A Time-of-Flight Range Sensor Using Four-Tap Lock-In Pixels with High near Infrared Sensitivity for LiDAR Applications

Abstract

1. Introduction

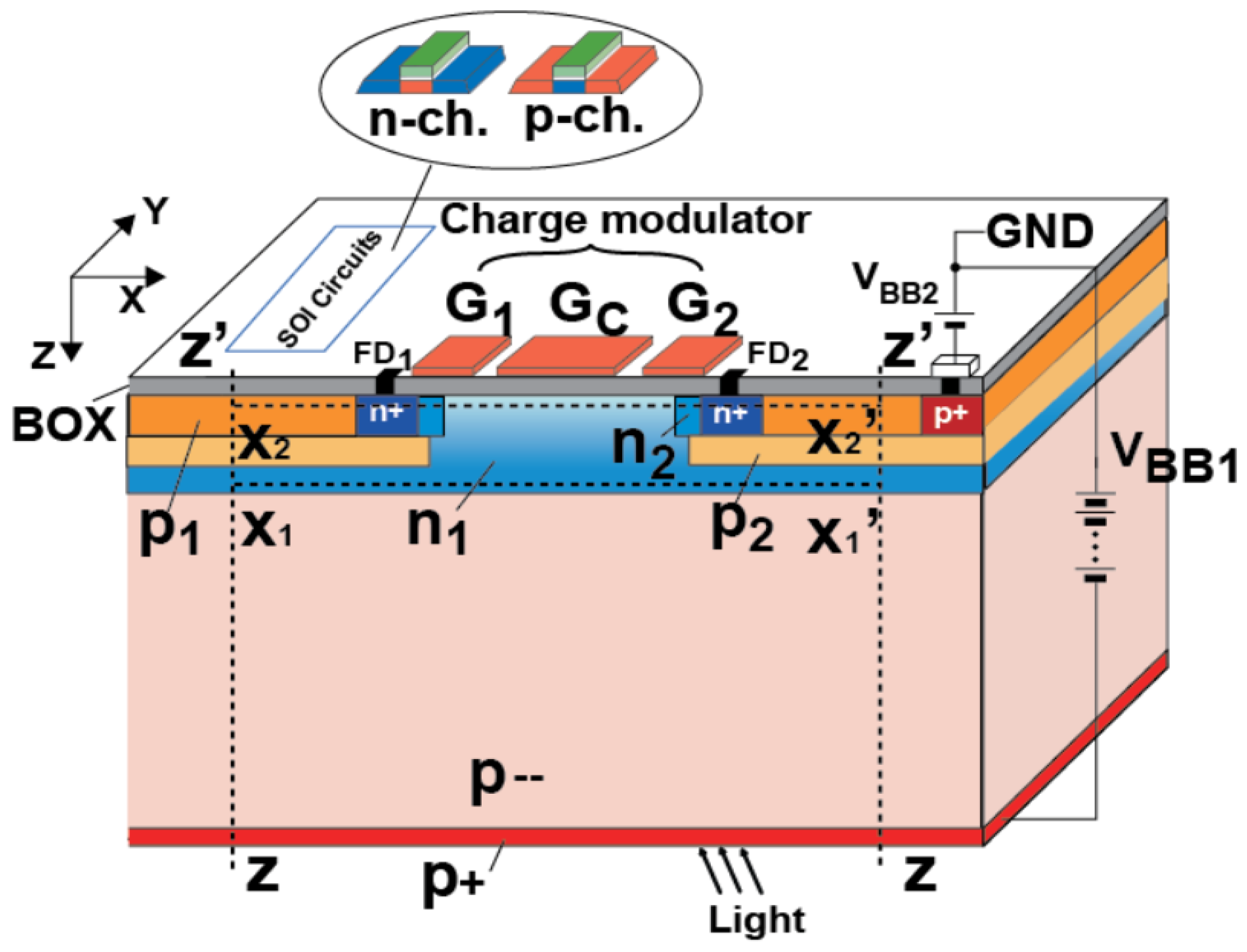

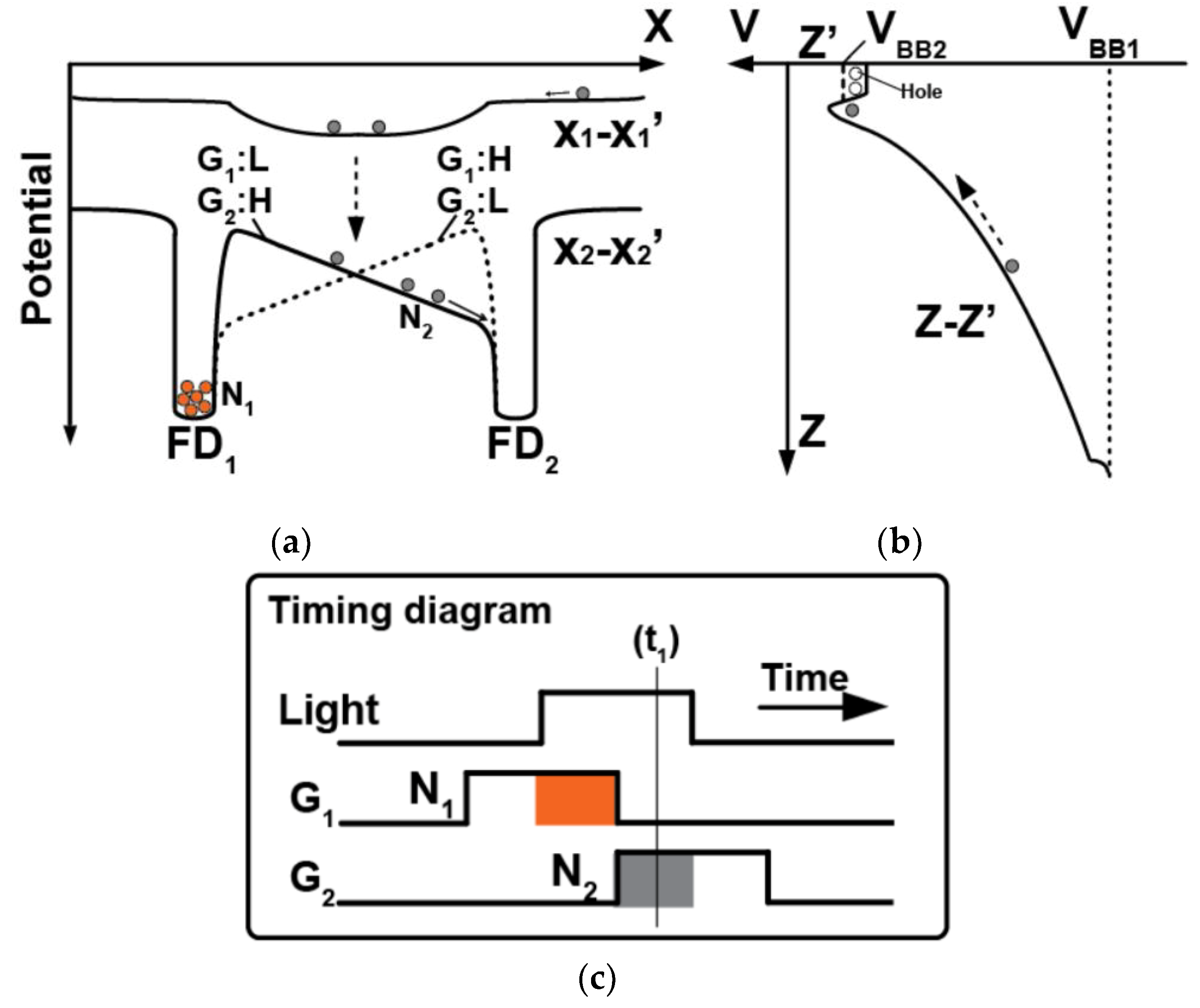

2. Lock-In Pixel Structure and Operation

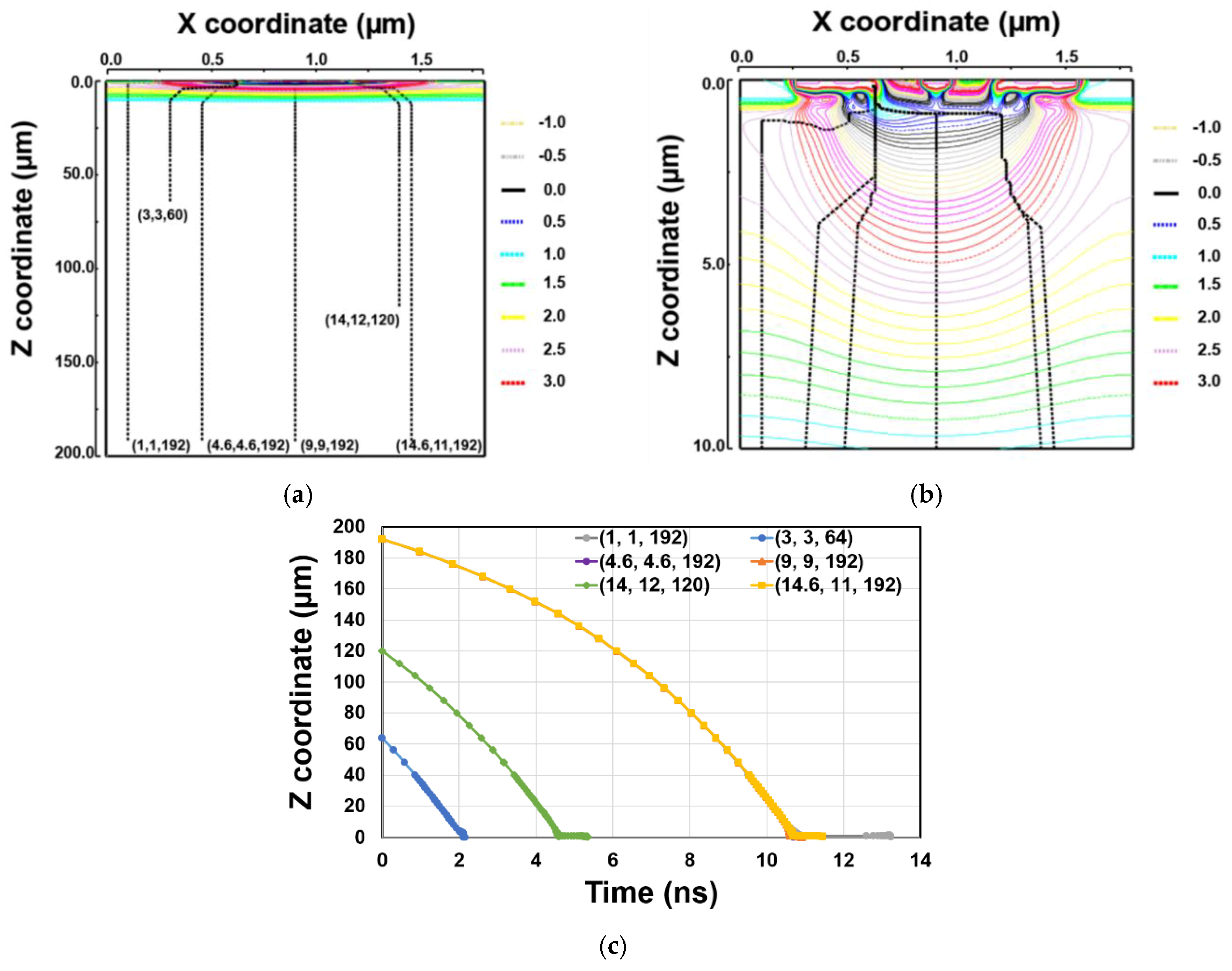

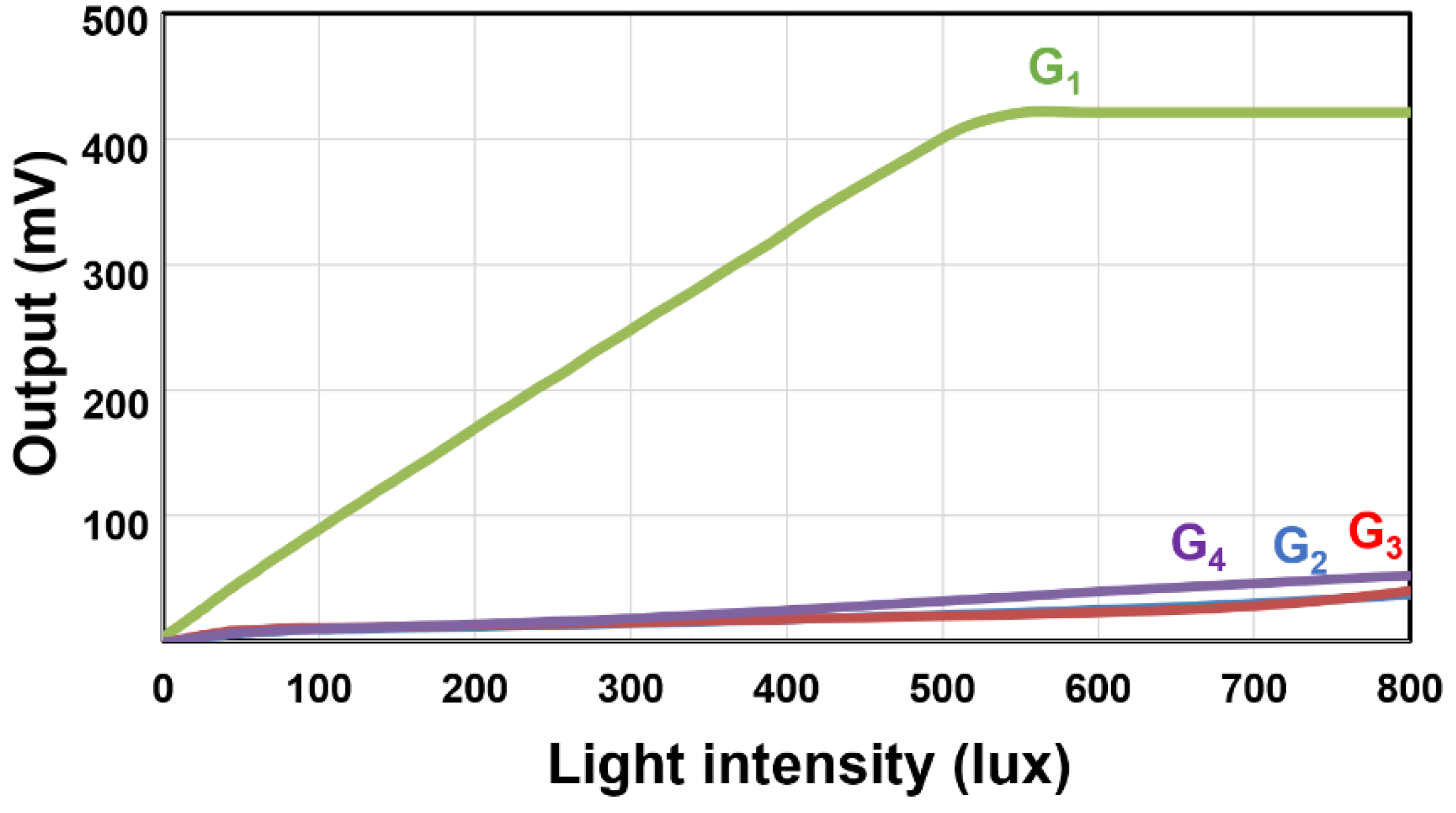

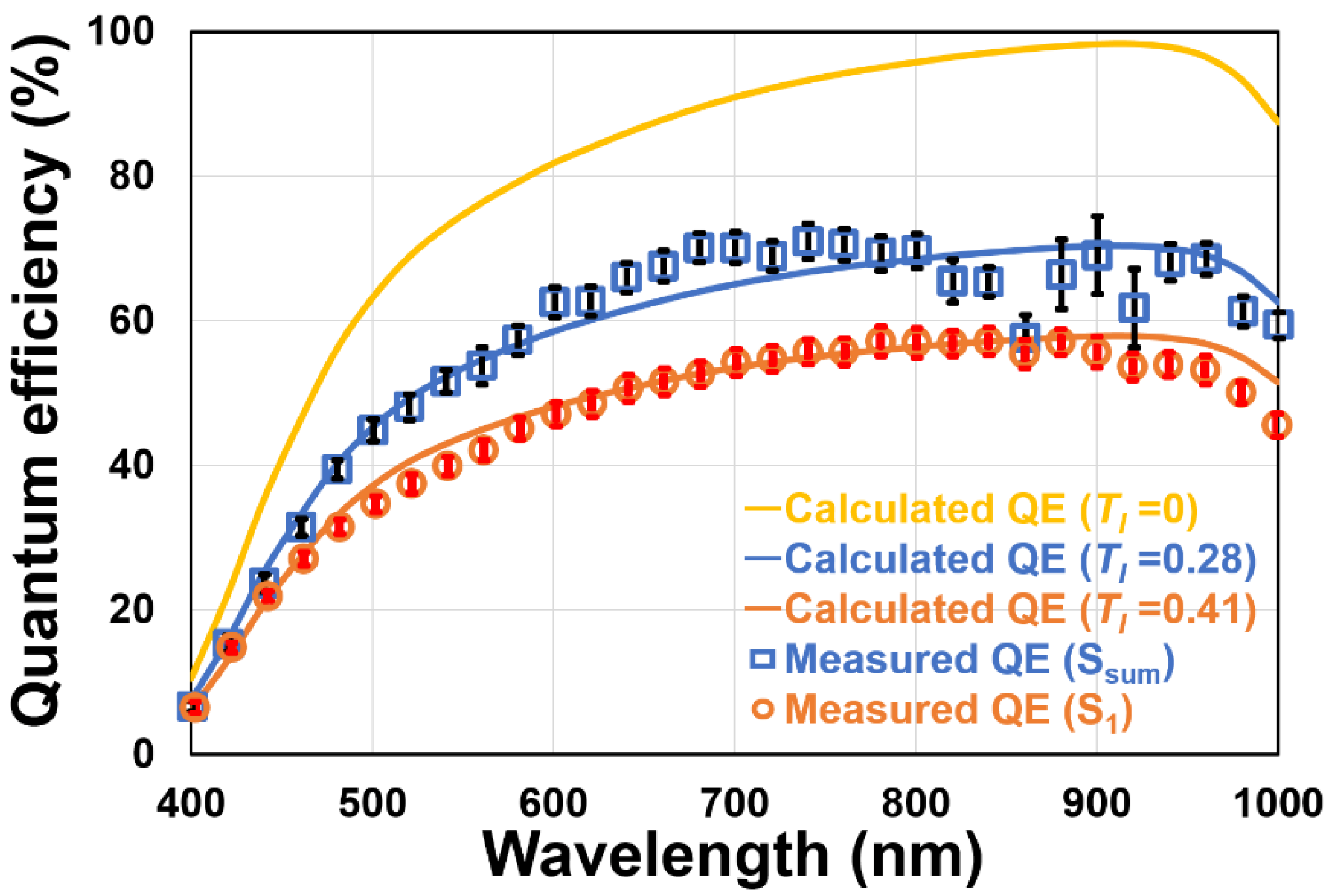

2.1. Silicon-On Insulator (SOI) Lock-In Pixel Detector

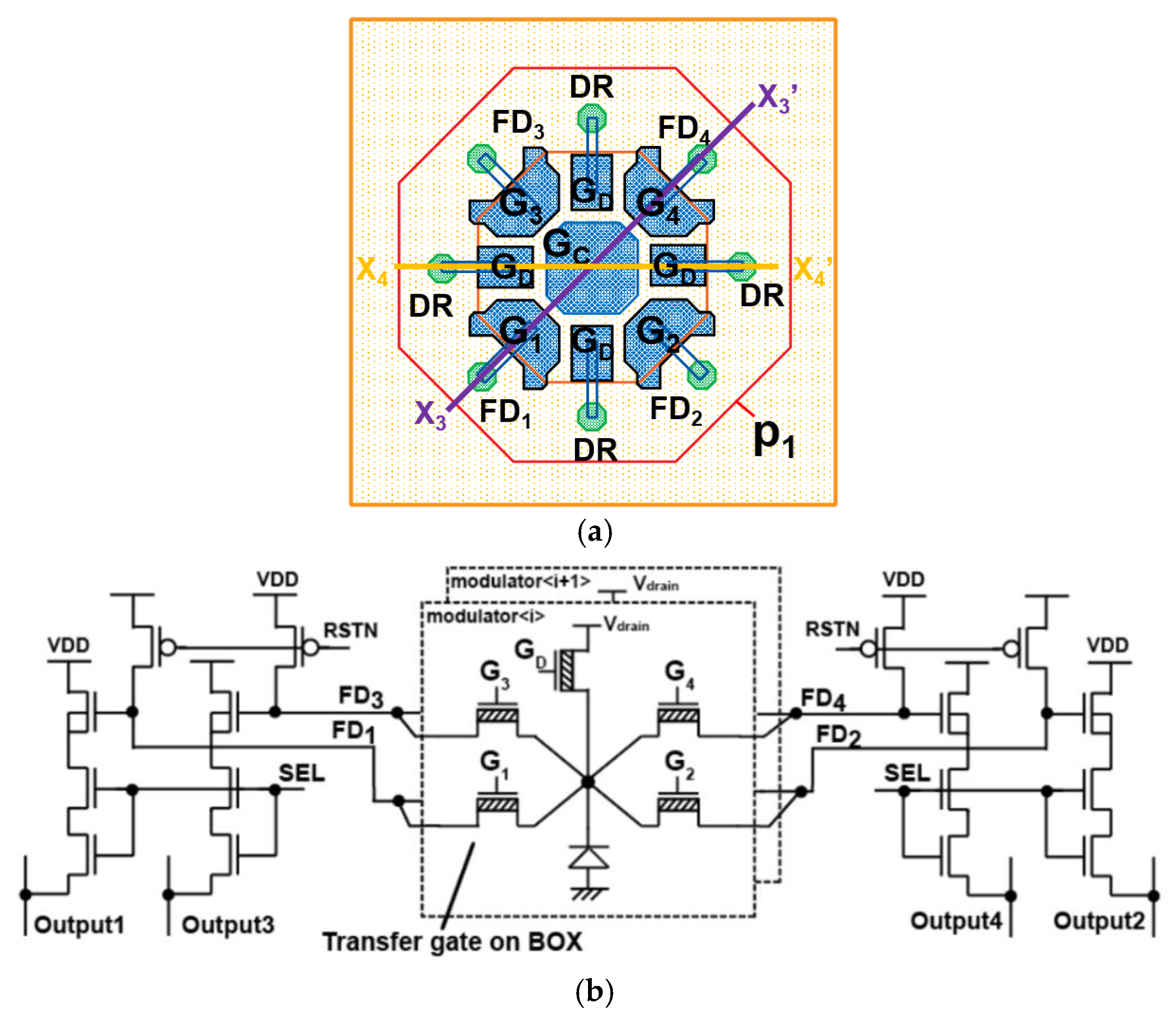

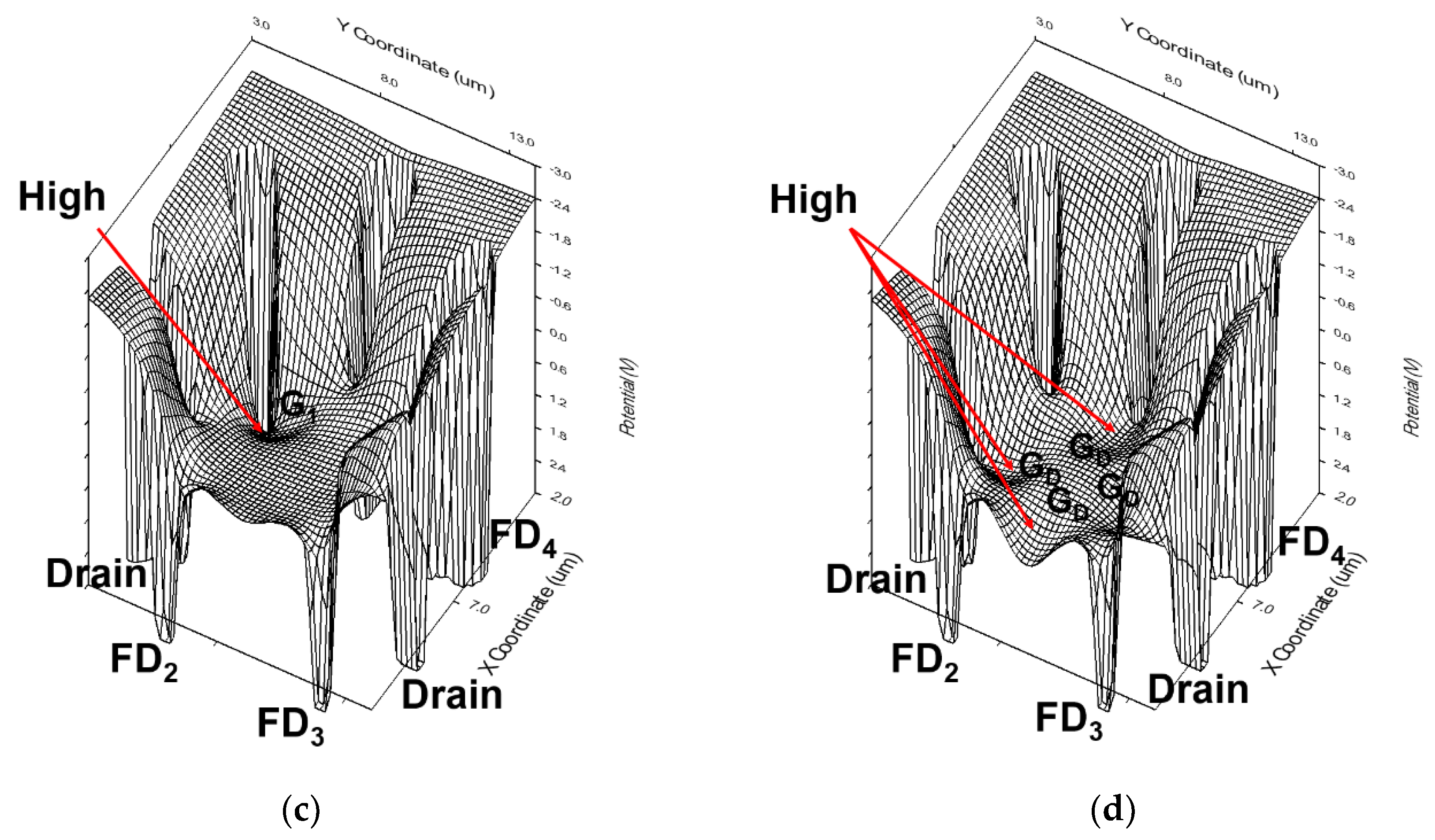

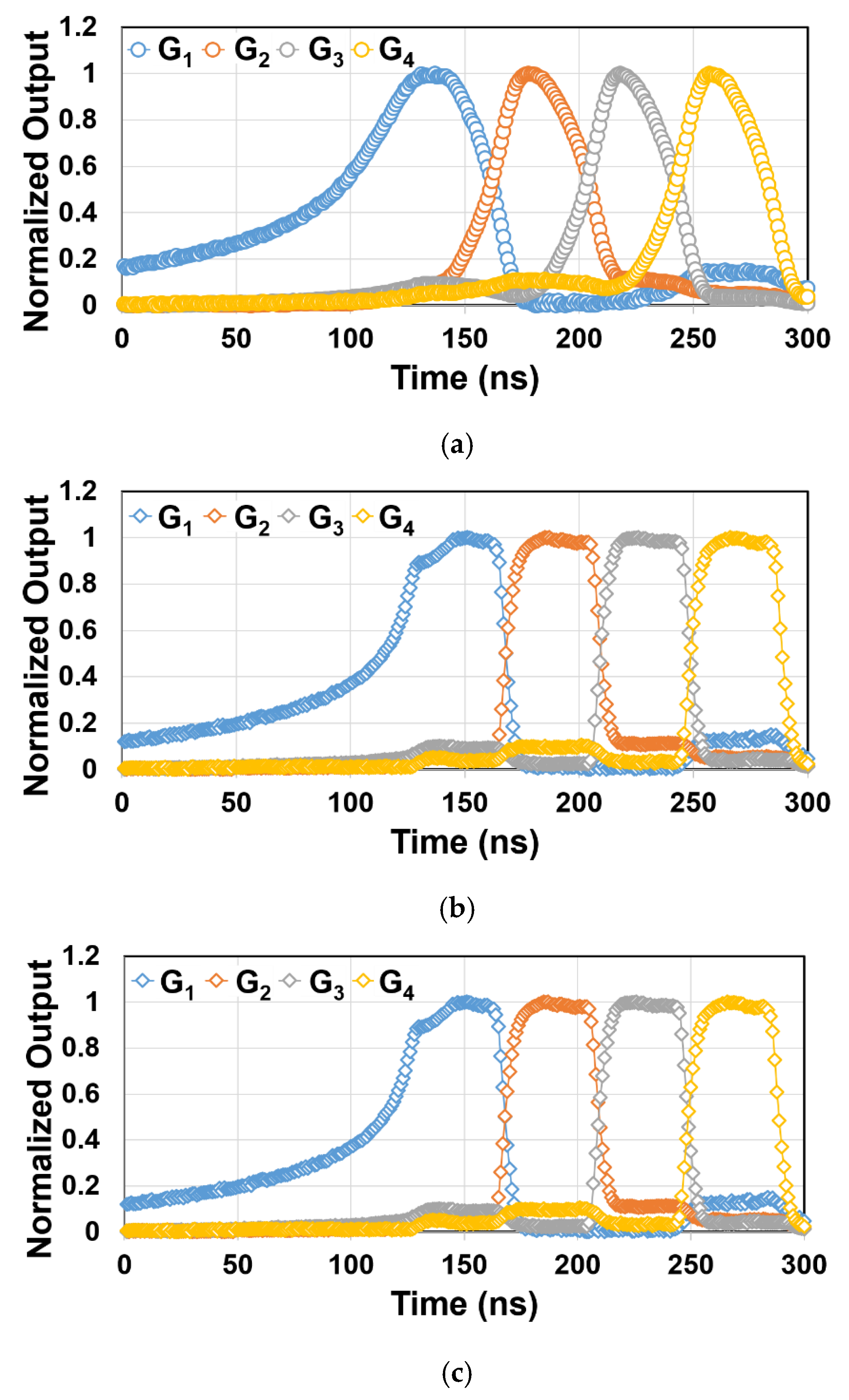

2.2. SOI-Based Four-Tap Lock-In Pixel for TOF Sensors

3. TOF Range Calculation and Resolution with Four-Tap Lock-On-Pixel and Short Pulse Modulation

4. Results and Discussion

4.1. Implemented TOF Sensor Chip

4.2. Measurement Results

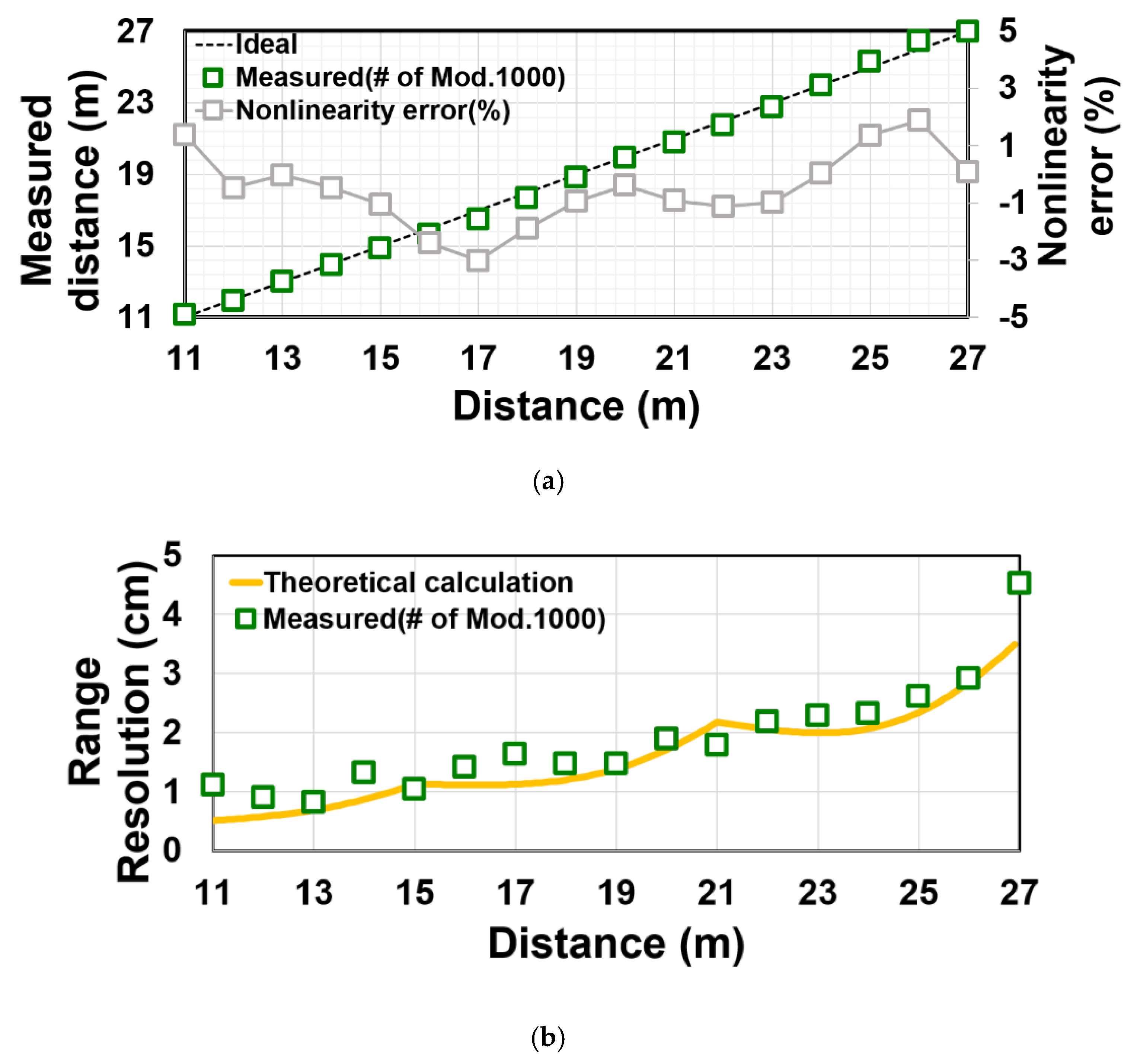

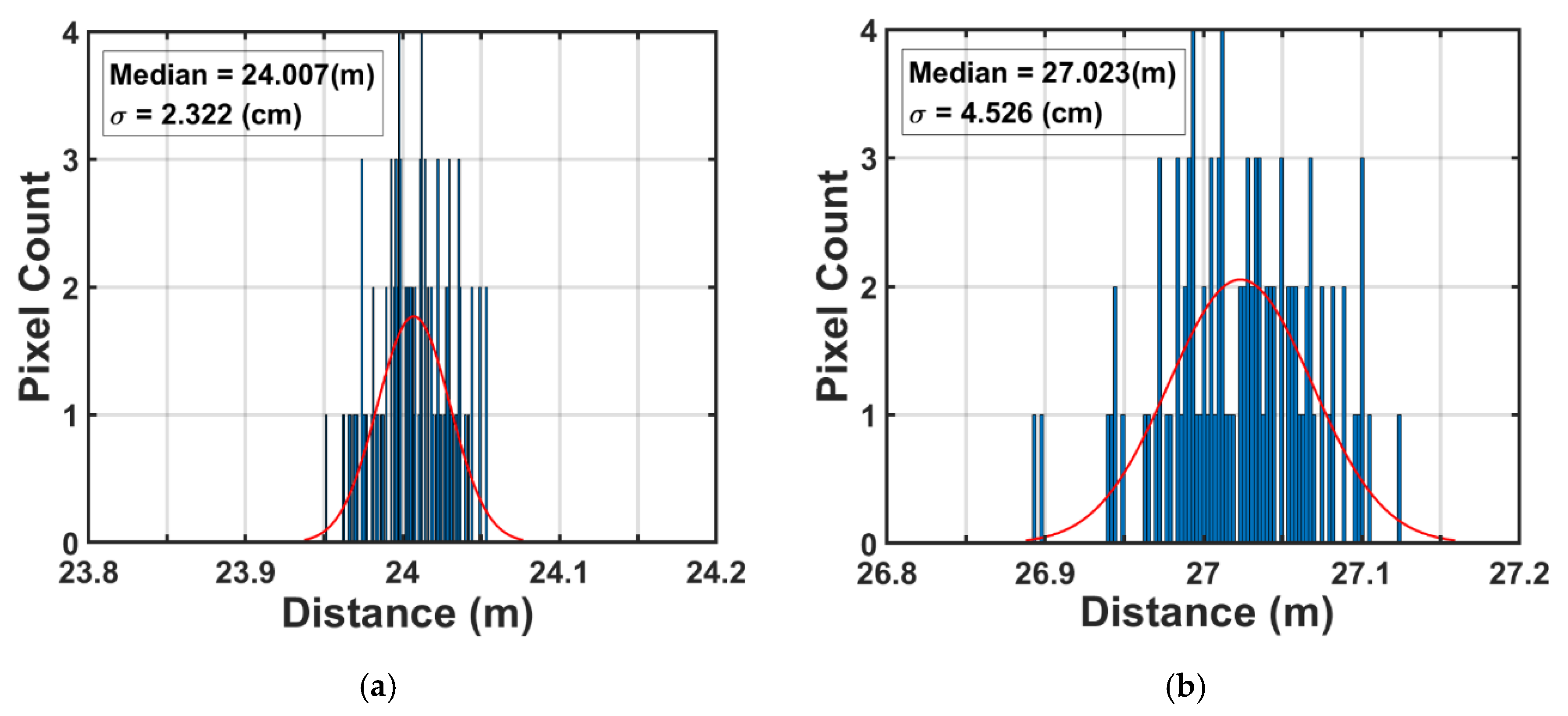

4.3. Distance Measurement

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Shcherbakova, O.; Pancheri, L.; Dalla Betta, G.-F.; Massari, N.; Stoppa, D. 3D camera based on linear-mode gain-modulated avalanche photodiodes. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 17–21 Februay 2013; pp. 490–491. [Google Scholar]

- Akita, H.; Takai, I.; Azuma, K.; Hata, T.; Ozaki, N. An Imager using 2-D Single-Photon Avalanche Diode Array in 0.18-μm CMOS for Automotive LIDAR Application. In Proceedings of the 2017 Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Kawahito, S.; Abdul Halin, I.; Ushinaga, T.; Sawada, T.; Homma, M.; Maeda, Y. A CMOS time-of-flight range image sensor with gates-on-field-oxide structure. IEEE Sens. J. 2007, 7, 1578–1586. [Google Scholar] [CrossRef]

- Lange, R.; Seitz, P. Solid-state time-of-flight range camera. IEEE J. Quantum Electron. 2001, 37, 390–397. [Google Scholar] [CrossRef]

- Niclass, C.; Soga, M.; Matsubara, H.; Ogawa, M.; Kagami, M. A 0.18-m CMOS SoC for a 100-M-range 10-frame/s 200 96-pixel time-of-flight depth sensor. IEEE J. Solid State Circuits 2014, 49, 315–330. [Google Scholar] [CrossRef]

- McCarthy, A.; Collins, R.J.; Krichel, N.J.; Fernández, V.; Wallace, A.M.; Buller, G.S. Long-range time-of flight scanning sensor based on high-speed time-correlated single-photon counting. Appl. Opt. 2009, 48, 6241–6251. [Google Scholar] [CrossRef] [PubMed]

- Ximenes, A.R.; Padmanabhan, P.; Lee, M.-J.; Yamashita, Y.; Yaung, D.N.; Charbon, E. A 256 × 256 45/65nm 3D-Stacked SPAD Based Direct TOF Image Sensor for LiDAR Applications with Optical Polar Modulation for up to 18.6dB Interference Suppression. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 Februay 2018; pp. 96–97. [Google Scholar]

- Takai, I.; Matsubara, H.; Soga, M.; Ohta, M.; Ogawa, M.; Yamashita, T. Single-Photon Avalanche Diode with Enhanced NIR-Sensitivity for Automotive LIDAR Systems. Sensors 2016, 16, 459. [Google Scholar] [CrossRef] [PubMed]

- Webster, E.A.G.; Richardson, J.A.; Grant, L.A.; Renshaw, D.; Henderson, R.K. A Single-Photon Avalanche Diode in 90-nm CMOS Imaging Technology with 44% Photon Detection Efficiency at 690 nm. IEEE Electron Device Lett. 2012, 33, 694–696. [Google Scholar] [CrossRef]

- Han, S.-M.; Takasawa, T.; Akahori, T.; Yasutomi, K.; Kagawa, K.; Kawahito, S. 7.4 A 413 × 240-pixel sub-centimeter resolution time-of-flight CMOS image sensor with in-pixel background canceling using lateral-electric-field charge modulators. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 Februay 2014; pp. 130–131. [Google Scholar]

- Stoppa, D.; Massari, N.; Pancheri, L.; Malfatti, M.; Perenzoni, M.; Gonzo, L. A range image sensor based on 10-μm lock-in pixels in 0.18-μm CMOS imaging technology. IEEE J. Solid State Circuits 2011, 46, 248–258. [Google Scholar] [CrossRef]

- Yasutomi, K.; Usui, T.; Han, S.-M.; Takasawa, T.; Kagawa, K.; Kawahito, K. A Submillimeter Range Resolution Time-of-Flight Range Imager with Column-wise Skew Calibration. IEEE Trans. Electron Devices 2015, 63, 82–188. [Google Scholar] [CrossRef]

- Bamji, C.S.; Mehta, S.; Thompson, B.; Elkhatib, T.; Wurster, S.; Akkaya, O.; Payne, A.; Godbaz, J.; Fenton, M.; Rajasekaran, V.; et al. 1Mpixel 65 nm BSI 320 MHz Demodulated TOF Image Sensor with 3.5 μm Global Shutter Pixels and Analog Binning. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 Februay 2018; pp. 94–95. [Google Scholar]

- Naik, N.; Kadambi, A.; Rhemann, C.; Izadi, S.; Raskar, R.; Bing Kang, S. A light transport model for mitigating multipath interference in time-of-flight sensors. In Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition (CVPR), Boston, MA, USA, 7–12 June 2015; pp. 73–81. [Google Scholar]

- Bhandari, A.; Kadambi, A.; Whyte, R.; Barsi, C.; Feigin, M.; Dorrington, A.; Raskar, R. Resolving multipath interference in time-of-flight imaging via modulation frequency diversity and sparse regularization. Opt. Lett. 2014, 39, 1705–1708. [Google Scholar] [CrossRef] [PubMed]

- Achar, S.; Bartels, J.R.; Whittaker, W.L.; Kutulakos, K.N.; Narasimhan, S.G. Epipolar time-of-flight imaging. ACM Trans. Gr. 2017, 36, 37. [Google Scholar] [CrossRef]

- Lee, S.; Yasutomi, K.; Nam, H.H.; Morita, M.; Kawahito, S. A Back-Illuminated Time-of-Flight Image Sensor with SOI-based Fully Depleted Detector Technology for LiDAR application. In Proceedings of the Eurosensors 2018 Conference, Graz, Austria, 9–12 September 2018. [Google Scholar]

- Sawada, T.; Ito, K.; Nakayama, M.; Kawahito, S. A range-shift technique for TOF range image sensors. IEEJ Trans. Sens. Micromach. 2009, 129, 421–425. [Google Scholar] [CrossRef]

- Kawahito, S.; Yasutomi, K.; Mars, K.; Kagawa, K.; Aoyama, S. Hybrid Time-of-Flight Range Image Sensors Using High-Speed Multiple-Tap Charge Modulation Pixels. In Proceedings of the International Display Workshops INP2-2, Nagoya, Japan, 12–14 December 2018. [Google Scholar]

- Stefanov, K.D.; Clarke, A.S.; Ivory, J.; Holland, A.D. Fully Depleted, Monolithic Pinned Photodiode CMOS Image Sensor Using Reverse Substrate Bias. In Proceedings of the 2017 International Image Sensor Society (IISW), Hiroshima, Japan, 30 May–2 June 2017; pp. P109–P112. [Google Scholar]

- Stefanov Konstantin, D.; Clarke Andrew, S.; Holland Andrew, D. Fully Depleted Pinned Photodiode CMOS Image Sensor with Reverse Substrate Bias. IEEE Electron Device Lett. 2017, 38, 64–66. [Google Scholar] [CrossRef]

- Lauxtermann, S.; Vangapally, V. A Fully Depleted Backside Illuminated CMOS Imager with VGA Resolution and 15-micron Pixel Pitch. In Proceedings of the International Image Sensor Workshop (IISW), Snowbird, UT, USA, 12–16 June 2013. [Google Scholar]

- Suss, A.; Wu, L.; Bacq, J.-L.; Spagnolo, A.; Coppejans, P.; Motsnyi, V.; Haspeslagh, L.; Borremeans, J.; Rosmeulen, M. A Fully Depleted 52 μm GS CIS Pixel with 6 ns Charge Transfer, 7 e–rms Read Noise, 80 μV/e–CG and >80% VIS-QE. In Proceedings of the International Image Sensor Workshop (IISW), Snowbird, UT, USA, 12–16 June 2013; pp. R402–R405. [Google Scholar]

- Popp, M.; Coi, B.D.; Huber, D.; Ferrat, P.; Ledergerber, M. High speed, backside illuminated 1024 × 1 line imager with charge domain frame store in Espros Photonic CMOSTM technology. In Proceedings of the International Image Sensor Workshop (IISW), Snowbird, UT, USA, 12–16 June 2013. [Google Scholar]

- Arai, Y.; Miyoshi, T.; Unno, Y.; Tsuboyama, T.; Terada, S.; Ikegami, Y.; Ichimiya, R.; Kohriki, T.; Tauchi, K.; Ikemoto, Y.; et al. Developments of SOI pixel process technology. Nucl. Instrum. Methods Phys. Res. A 2011, 636, S31–S36. [Google Scholar] [CrossRef]

- Kamehama, H.; Kawahito, S.; Shrestha, S.; Nakanishi, S.; Yasitomi, K.; Takeda, A.; Tsuru, T.G.; Arai, Y. A low-noise X-ray astronomical silicon-on-insulator pixel detector using a pinned depleted diode structure. Sensors 2018, 18, 27. [Google Scholar] [CrossRef] [PubMed]

- Miyoshi, T.; Arai, Y.; Chiba, T.; Fujita, Y.; Hara, K.; Honda, S.; Igarashi, Y.; Ikegami, Y.; Ikemoto, Y.; Kohriki, T.; et al. Monolithic pixel detectors with 0.2μm FD-SOI pixel process technology. Nucl. Instrum. Methods Phys. Res. A 2013, 732, 530–534. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Process | 0.2 µm SOI–CMOS technology |

| Pixel size | 36 µm × 18µm |

| Fill factor | 100% (Backside illumination) |

| Substrate thickness | 200 µm |

| Modulation | Light and Gate Pulse Width: 40 ns Cycle time of light pulse: 520 ns Duty ratio: 7.7% |

| Modulation contrast | 71% with 930 nm short-pulse laser |

| Light source | Wavelength: 940 nm Power density: 7.2 W/m2 @ 30 m |

| Integration time | 520 μs (1000 cycle) |

| Quantum efficiency | 55% (at 940 nm) |

| Linearity error | +1.8~−3.0% |

| Range resolution | 4.5 cm (at 27 m, outdoor (75klux)) |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.; Yasutomi, K.; Morita, M.; Kawanishi, H.; Kawahito, S. A Time-of-Flight Range Sensor Using Four-Tap Lock-In Pixels with High near Infrared Sensitivity for LiDAR Applications. Sensors 2020, 20, 116. https://doi.org/10.3390/s20010116

Lee S, Yasutomi K, Morita M, Kawanishi H, Kawahito S. A Time-of-Flight Range Sensor Using Four-Tap Lock-In Pixels with High near Infrared Sensitivity for LiDAR Applications. Sensors. 2020; 20(1):116. https://doi.org/10.3390/s20010116

Chicago/Turabian StyleLee, Sanggwon, Keita Yasutomi, Masato Morita, Hodaka Kawanishi, and Shoji Kawahito. 2020. "A Time-of-Flight Range Sensor Using Four-Tap Lock-In Pixels with High near Infrared Sensitivity for LiDAR Applications" Sensors 20, no. 1: 116. https://doi.org/10.3390/s20010116

APA StyleLee, S., Yasutomi, K., Morita, M., Kawanishi, H., & Kawahito, S. (2020). A Time-of-Flight Range Sensor Using Four-Tap Lock-In Pixels with High near Infrared Sensitivity for LiDAR Applications. Sensors, 20(1), 116. https://doi.org/10.3390/s20010116