Research on a 3D Encapsulation Technique for Capacitive MEMS Sensors Based on Through Silicon Via †

Abstract

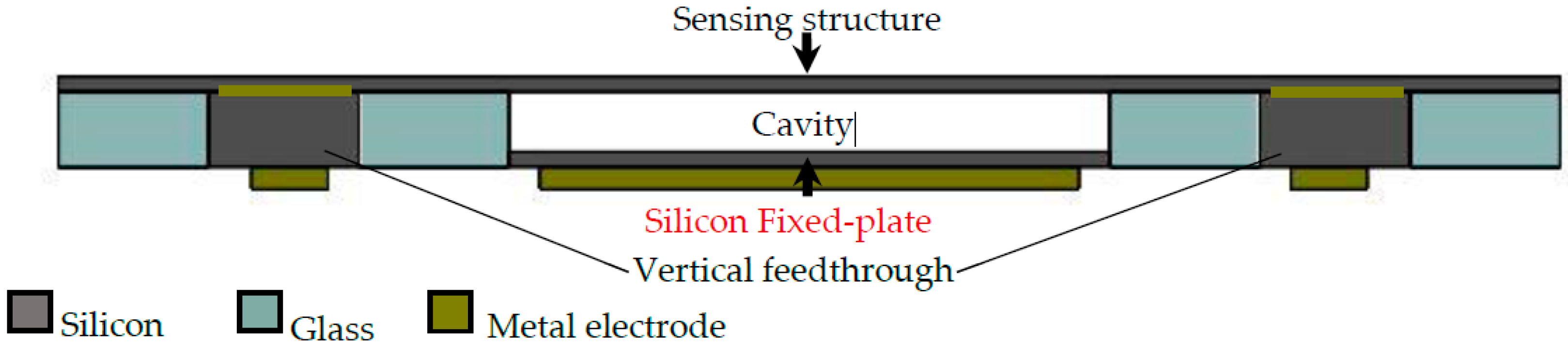

:1. Introduction

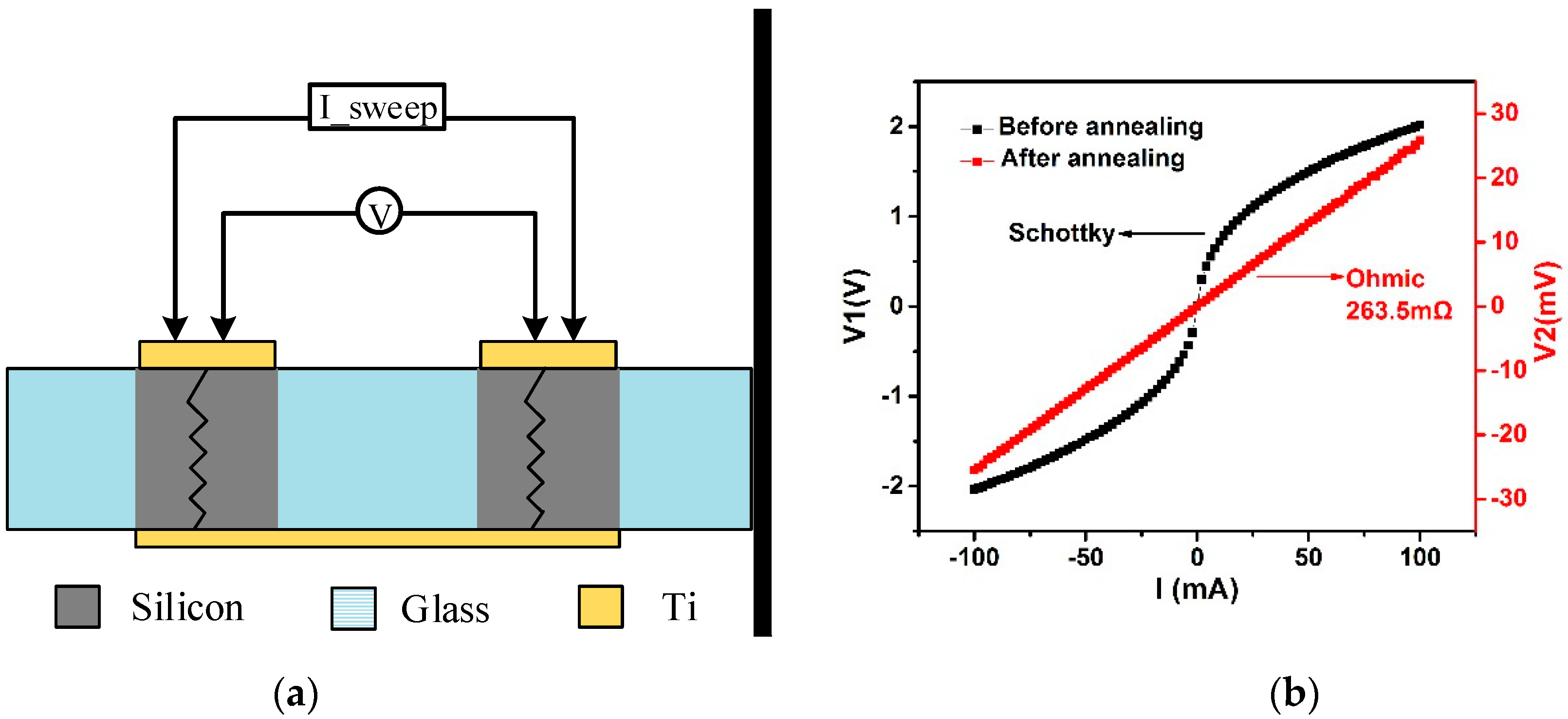

2. Fabrication of Encapsulation Cap

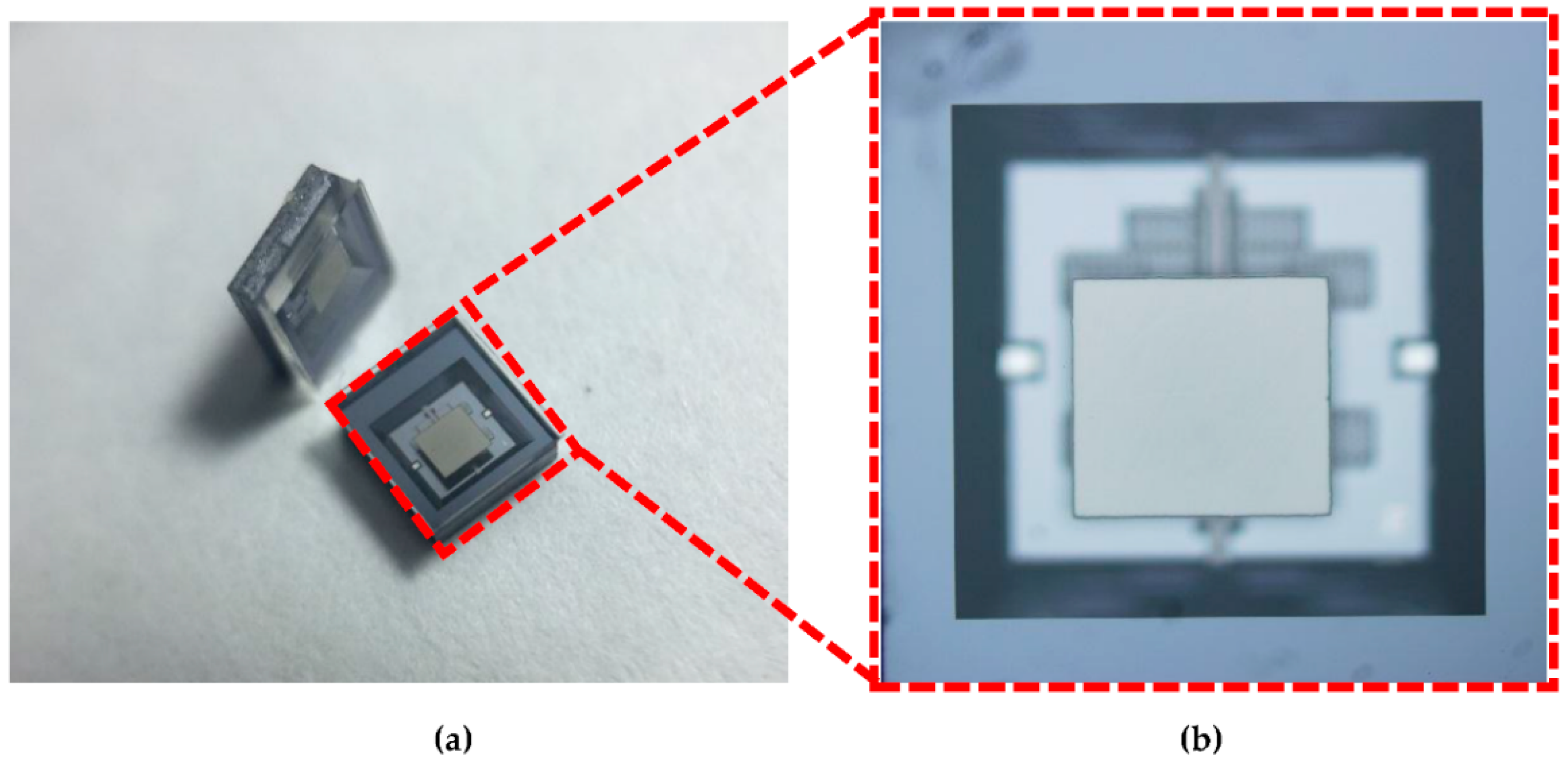

- (a)

- A 4-inch silicon wafer with a low resistivity (0.0009 Ω·cm) was used to realize a low loss electrical interconnection. The substrate was patterned by photolithography and an 8-μm thick photoresist acted as the mask for deep silicon etching.

- (b)

- The mature deep reactive ion etch (DRIE) process was utilized to etch silicon of 350 μm to form silicon molds for the glass reflow process. The photoresist was removed and the chemical cleaning of the wafer was carefully conducted for the following anodic bonding.

- (c)

- The silicon substrate was bonded to the Pyrex glass wafer in a vacuum environment. The silicon substrate and the glass wafer had the same thickness and a similar coefficient of thermal expansion (CTE) to minimize the warp and distortion of the bonded wafer. It should be noted that it is necessary to hold the vacuum conditions of 10−2 mTorr (1 Torr ≈ 133 Pa) for enough time to achieve vacuum outgassing, which can prevent generating voids during the glass reflow process.

- (d)

- The bonded wafer was then placed in the furnace at 1050 °C for 2 h to ensure that the silicon molds were fully filled with the fused glass. When the temperature was elevated above 750 °C, the fused glass started to be pushed into the silicon molds under the large pressure difference between inside and outside the hermetic cavity. Subsequently, the glass was cooled by a cooling process.

- (e)

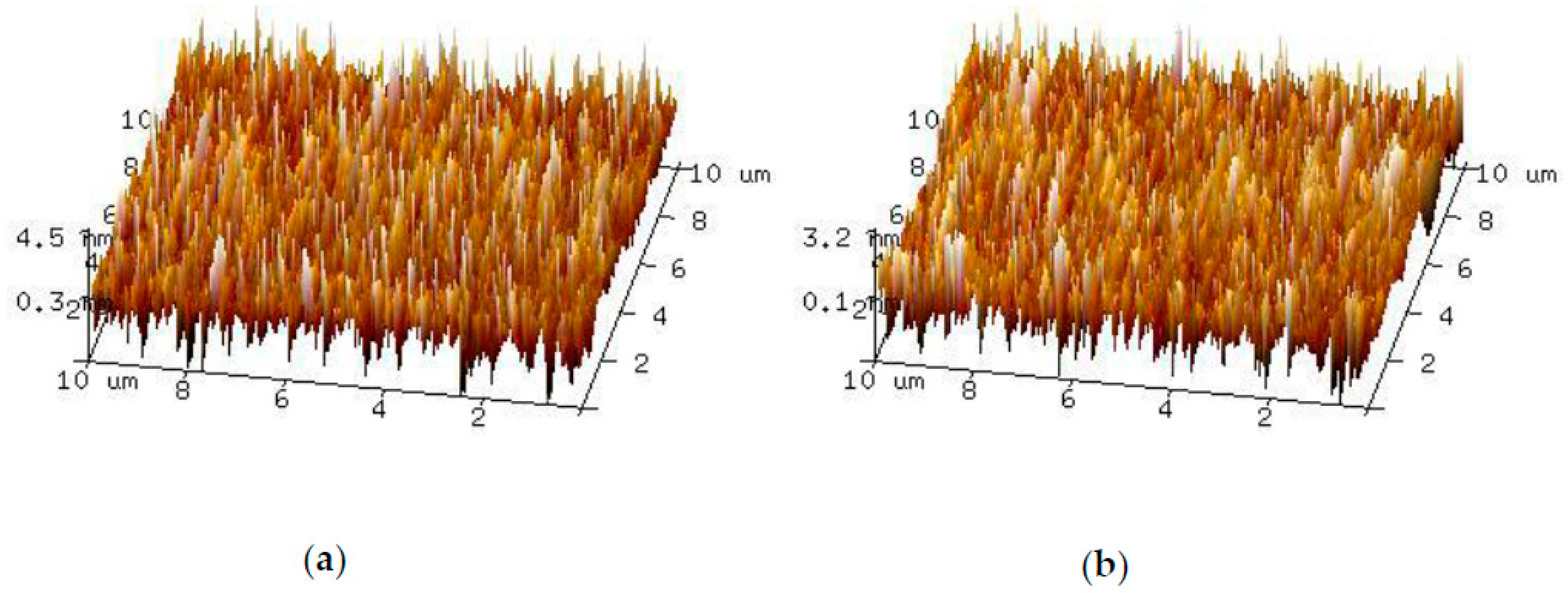

- The reflowed wafer was lapped and thinned on double sides until the formation of the silicon vertical feedthrough. A chemical mechanical polishing (CMP) process was exploited to provide good surface quality for later wafer bonding.

- (f)

- To form the encapsulation cavity, the silicon was etched by an Inductively Coupled Plasma (ICP) process to a certain depth according to design requirements. The cavity acted as the gap of the sensing capacitor when the following anodic bonding was accomplished.

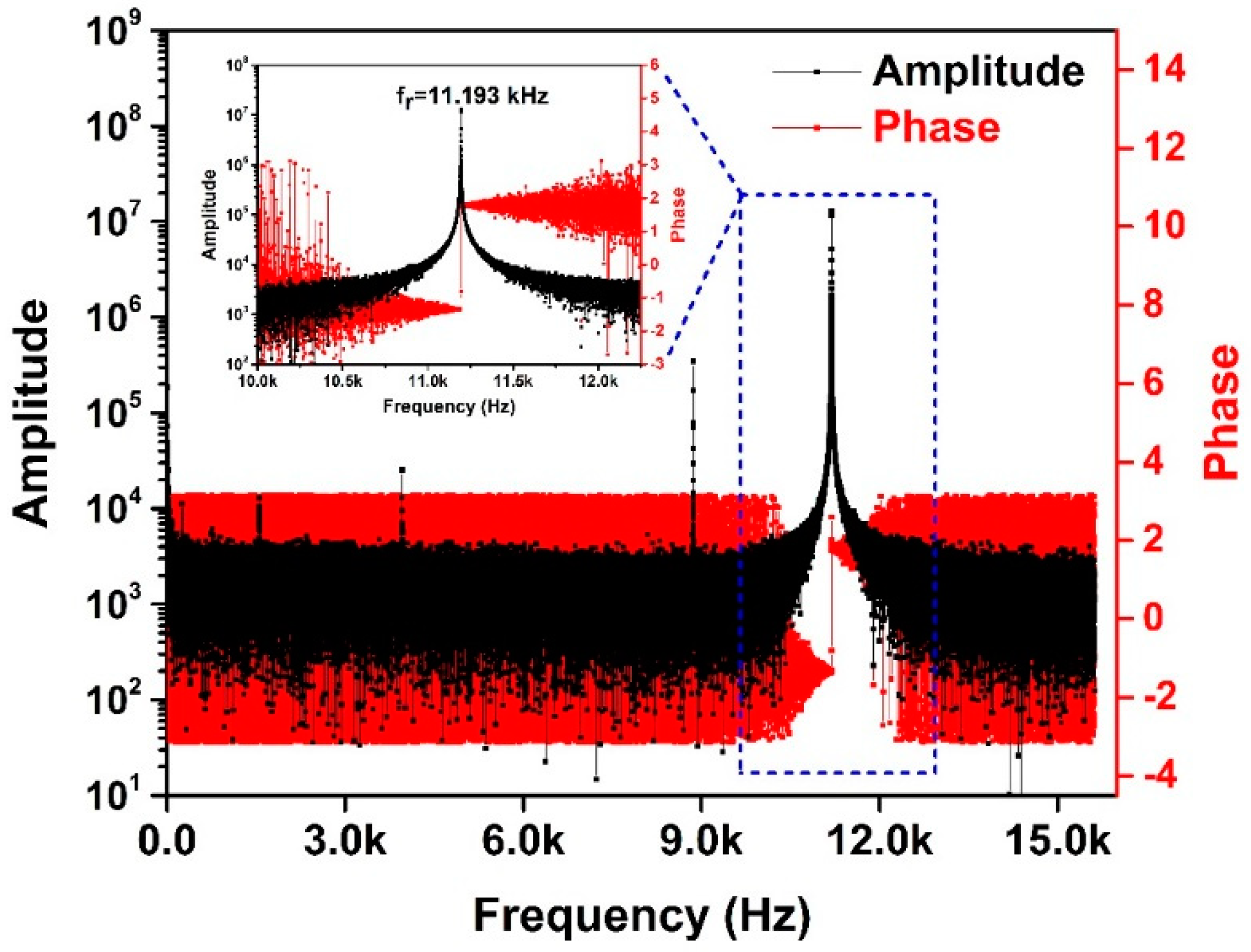

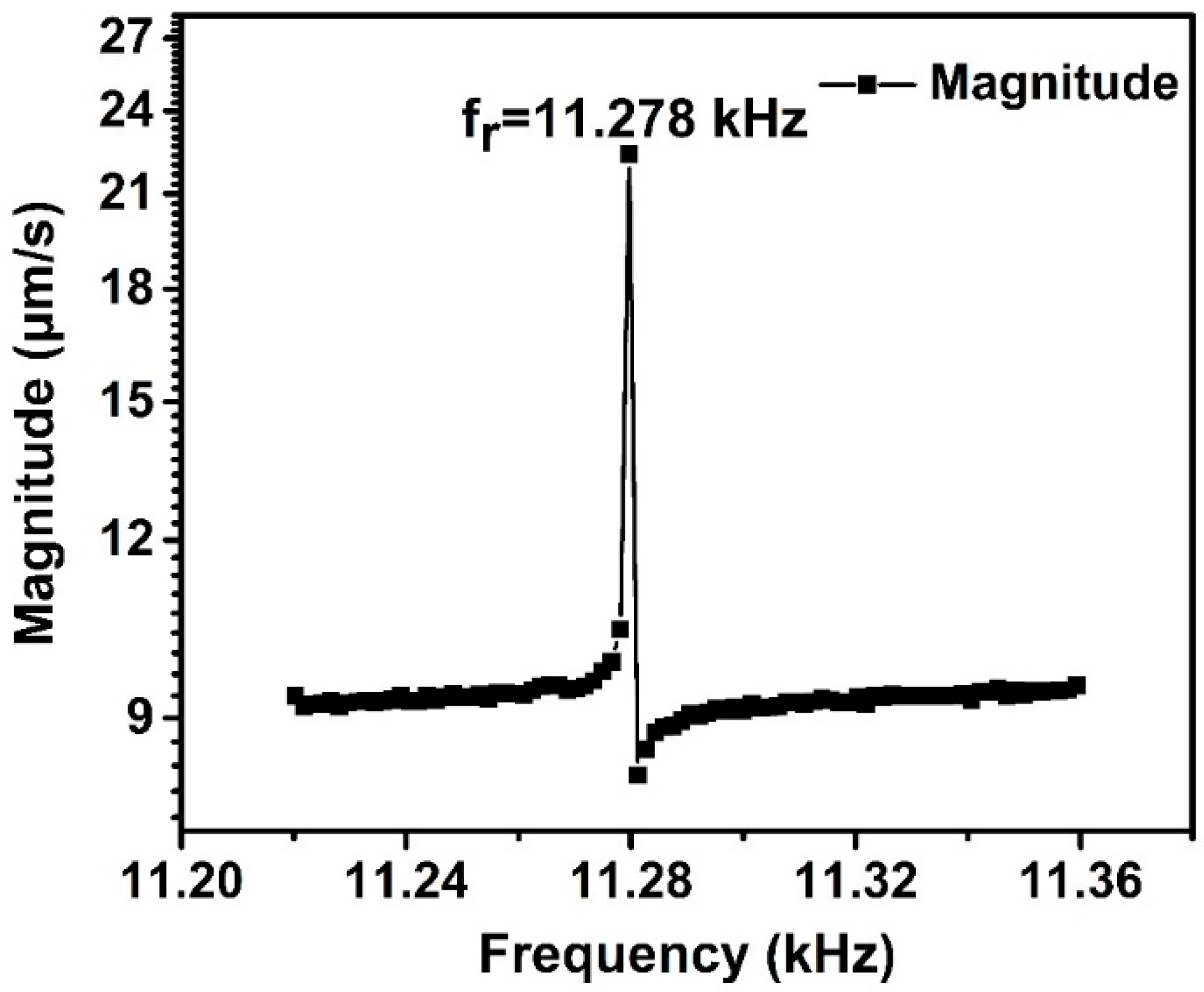

3. Characterization and Measurement

4. Application and Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hsu, T.-R. MEMS and Microsystems: Design, Manufacture, and Nanoscale Engineering; John Wiley & Sons: Hoboken, NJ, USA, 2004; pp. 91–360. ISBN 7-111-13226-2. [Google Scholar]

- Kühne, S.; Hierold, C. Wafer-level packaging and direct interconnection technology based on hybrid bonding and through silicon vias. J. Micromech. Microeng. 2011, 21, 085032. [Google Scholar] [CrossRef]

- Lee, S.W.; Lee, S.K.; Park, J.H. High-density through-wafer copper via array in insulating glass mold using reflow process. Jpn. J. Appl. Phys. 2015, 54, 4. [Google Scholar] [CrossRef]

- Kettner, P.; Kim, B.; Pargfrieder, S.; Zhu, S. In New Technologies for advanced high density 3D packaging by using TSV process. In Proceedings of the International Conference on Electronic Packaging Technology & High Density Packaging (ICEPT-HDP 2008), Shanghai, China, 28–31 July 2008; pp. 1–3. [Google Scholar]

- Wang, Z.Y. 3-D Integration and Through-Silicon Vias in MEMS and Microsensors. J. Microelectromech. Syst. 2015, 24, 1211–1244. [Google Scholar] [CrossRef]

- Zoschke, K.; Manier, C.A.; Wilke, M.; Oppermann, H.; Ruffieux, D.; Dekker, J.; Jaakkola, A.; Dalla Piazza, S.; Allegato, G.; Lang, K.D. Application of TSV Integration and Wafer Bonding Technologies for Hermetic Wafer Level Packaging of MEMS Components for Miniaturized Timing Devices. In Proceedings of the 2015 IEEE 65th Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2015; IEEE: New York, NY, USA, 2015; pp. 1343–1350. [Google Scholar]

- Tezcan, D.S.; Pham, N.; Majeed, B.; Moor, P.D. Sloped through Wafer Vias for 3D Wafer Level Packaging. In Proceedings of the Electronic Components & Technology Conference, Reno, NV, USA, 29 May–1 June 2007. [Google Scholar]

- Premachandran, C.S.; Nagarajan, R.; Yu, C.; Zhang, X.; Chong, S.C. A novel electrically conductive wafer through hole filled vias interconnect for 3D MEMS packaging. In Proceedings of the Electronic Components & Technology Conference, New Orleans, LA, USA, 27–30 May 2003. [Google Scholar]

- Esashi, M.; Ura, N.; Matsumoto, Y. Anodic bonding for integrated capacitive sensors. In Proceedings of the Micro Electro Mechanical Systems, MEMS’92, an Investigation of Micro Structures, Sensors, Actuators, Machines and Robot, Travemunde, Germany, 4–7 February 1992; pp. 43–48. [Google Scholar]

- Jin, J.Y.; Yoo, S.H.; Yoo, B.W.; Kim, Y.K. A Wafer-Level Vacuum Package Using Glass-Reflowed Silicon Through-Wafer Interconnection for Nano/Micro Devices. J. Nanosci. Nanotechnol. 2012, 12, 5252–5262. [Google Scholar] [CrossRef] [PubMed]

- Haque, R.; Wise, K. An intraocular pressure sensor based on a glass reflow process. In Proceedings of the Solid-State Sensors, Actuators, and Microsystems Workshop, Hilton Head Island, SC, USA, 6–10 June 2010; pp. 49–52. [Google Scholar]

- Haque, R.U.; Wise, K.D. A Glass-in-Silicon Reflow Process for Three-Dimensional Microsystems. J. Microelectromech. Syst. 2013, 22, 1470–1477. [Google Scholar] [CrossRef]

- Haque, R.M.; Serrano, D.E.; Gao, X.; N.-Shirazi, A.; Keesara, V.; Ayazi, F.; Wise, K.D. Hermetic packaging of resonators with vertical feedthroughs using a glass-in-silicon reflow process. In Proceedings of the Solid-State Sensors, Actuators and Microsystems Conference, Beijing, China, 5–9 June 2011; pp. 2303–2306. [Google Scholar]

- Zhao, J.C.; Yuan, Q.; Wang, F.X.; Kan, X.; Han, G.W.; Sun, L.; Sun, H.Y.; Yang, J.L.; Yang, F.H. Design and characterization of a 3D encapsulation with silicon vias for radio frequency micro-electromechanical system resonator. Chin. Phys. B 2017, 26, 5. [Google Scholar] [CrossRef]

- Kuang, Y.; Xiao, D.; Zhou, J.; Li, W.; Hou, Z.; Cui, H.; Wu, X. Theoretical model and experiments of glass reflow process in TGV for 3D wafer-level packaging. In Proceedings of the 2018 IEEE International Symposium on Inertial Sensors and Systems (INERTIAL), Moltrasio, Italy, 26–29 March 2018; pp. 1–4. [Google Scholar]

- Rödjegård, H.; Andersson, G.I.; Rusu, C.; Löfgren, M.; Billger, D. Capacitive slanted-beam three-axis accelerometer: I. Modelling and design. J. Micromech. Microeng. 2005, 15, 1989. [Google Scholar] [CrossRef]

- Benali, A.; Bouya, M.; Faqir, M.; El Amrani, A.; Ghogho, M.; Benali, A.; Benabdellah, A. Through Glass via Thermomechanical Analysis: Geometrical parameters effect on thermal stress. In Proceedings of the 2013 8th International Design and Test Symposium, Marrakesh, Morocco, 16–18 December 2013. [Google Scholar]

- Lee, J.-Y.; Lee, S.-W.; Lee, S.-K.; Park, J.-H. Through-glass copper via using the glass reflow and seedless electroplating processes for wafer-level RF MEMS packaging. J. Micromech. Microeng. 2013, 23, 085012. [Google Scholar] [CrossRef]

- Xiao, Z.; Yamaner, F.Y.; Oralkan, Ö. Fabrication of Vacuum-Sealed Capacitive Micromachined Ultrasonic Transducers with Through-Glass-Via Interconnects Using Anodic Bonding. J. Microelectromech. Syst. 2017, 26, 226–234. [Google Scholar]

- Yamaner, F.Y.; Zhang, X.; Oralkan, O.M. A three-mask process for fabricating vacuum-sealed capacitive micromachined ultrasonic transducers using anodic bonding. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2015, 62, 972–982. [Google Scholar] [CrossRef] [PubMed]

- Helfrick, A.D. Q Factor Measurement; CRC Press: Boca Raton, FL, USA, 2004; Volume 200, pp. 1–5. [Google Scholar]

- Bianco, S.; Cocuzza, M.; Ferrero, S.; Giuri, E.; Piacenza, G.; Pirri, C.F.; Ricci, A.; Scaltrito, L.; Bich, D.; Merialdo, A. Silicon resonant microcantilevers for absolute pressure measurement. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. 2006, 24, 1803–1809. [Google Scholar] [CrossRef]

- Chidambaram, V.; Ling, X.; Bangtao, C. Titanium-based getter solution for wafer-level MEMS vacuum packaging. J. Electron. Mater. 2013, 42, 485–491. [Google Scholar] [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, M.; Yang, J.; He, Y.; Yang, F.; Yang, F.; Han, G.; Si, C.; Ning, J. Research on a 3D Encapsulation Technique for Capacitive MEMS Sensors Based on Through Silicon Via. Sensors 2019, 19, 93. https://doi.org/10.3390/s19010093

Zhang M, Yang J, He Y, Yang F, Yang F, Han G, Si C, Ning J. Research on a 3D Encapsulation Technique for Capacitive MEMS Sensors Based on Through Silicon Via. Sensors. 2019; 19(1):93. https://doi.org/10.3390/s19010093

Chicago/Turabian StyleZhang, Meng, Jian Yang, Yurong He, Fan Yang, Fuhua Yang, Guowei Han, Chaowei Si, and Jin Ning. 2019. "Research on a 3D Encapsulation Technique for Capacitive MEMS Sensors Based on Through Silicon Via" Sensors 19, no. 1: 93. https://doi.org/10.3390/s19010093

APA StyleZhang, M., Yang, J., He, Y., Yang, F., Yang, F., Han, G., Si, C., & Ning, J. (2019). Research on a 3D Encapsulation Technique for Capacitive MEMS Sensors Based on Through Silicon Via. Sensors, 19(1), 93. https://doi.org/10.3390/s19010093