Study of CMOS-SOI Integrated Temperature Sensing Circuits for On-Chip Temperature Monitoring

Abstract

:1. Introduction

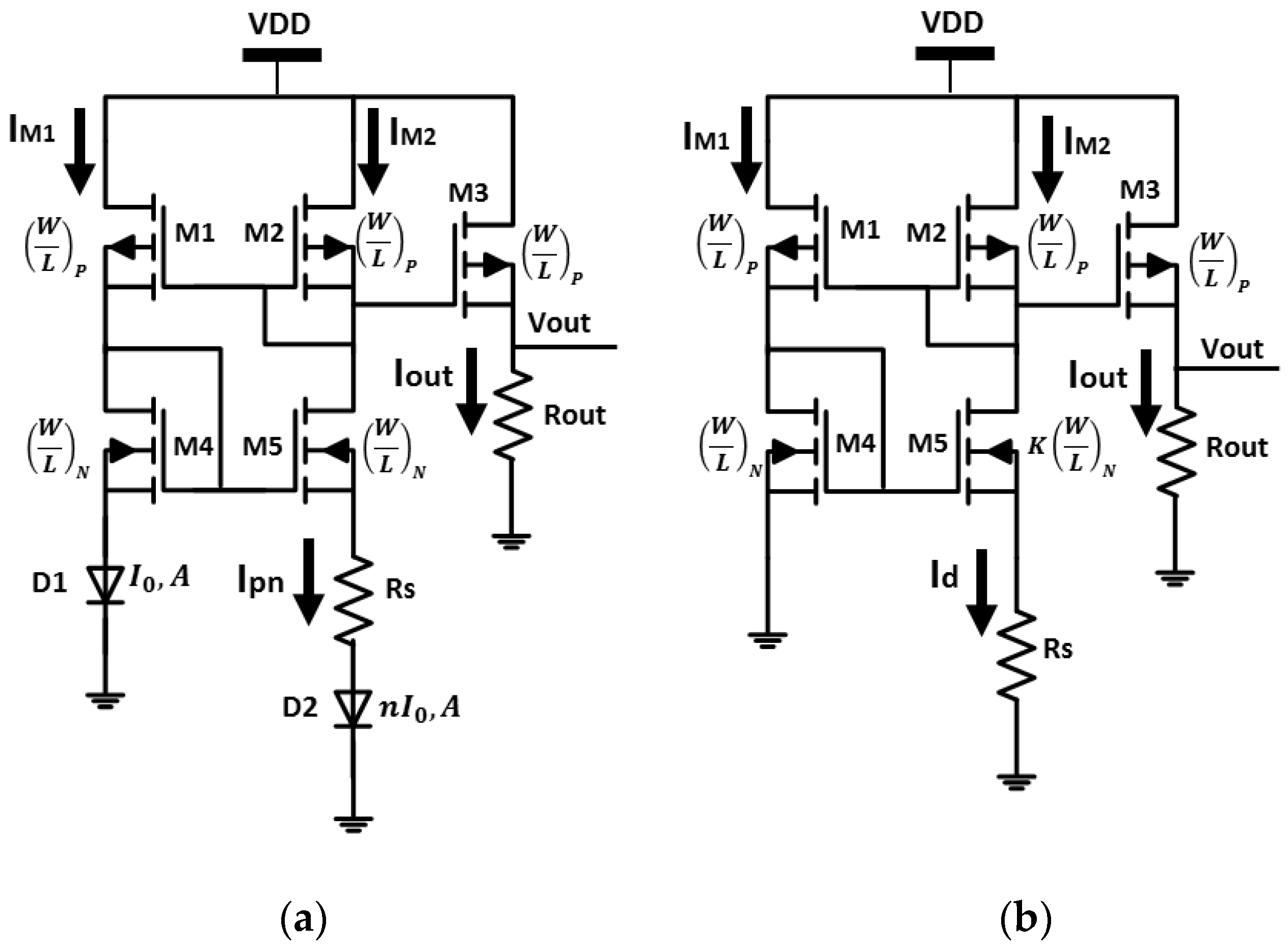

2. Proportional to Absolute Temperature (PTAT) Circuit

2.1. Principle of Operation

2.2. Implementation

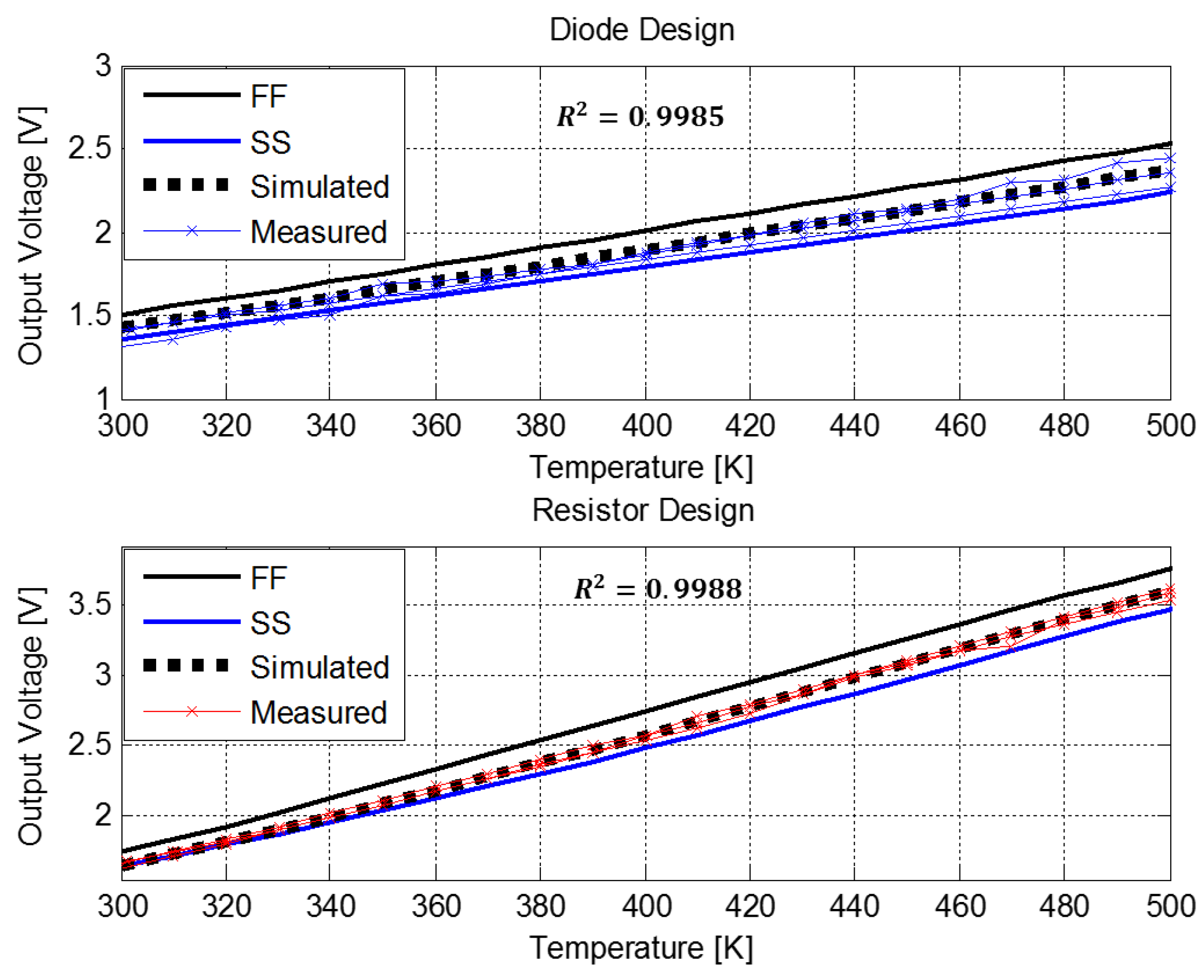

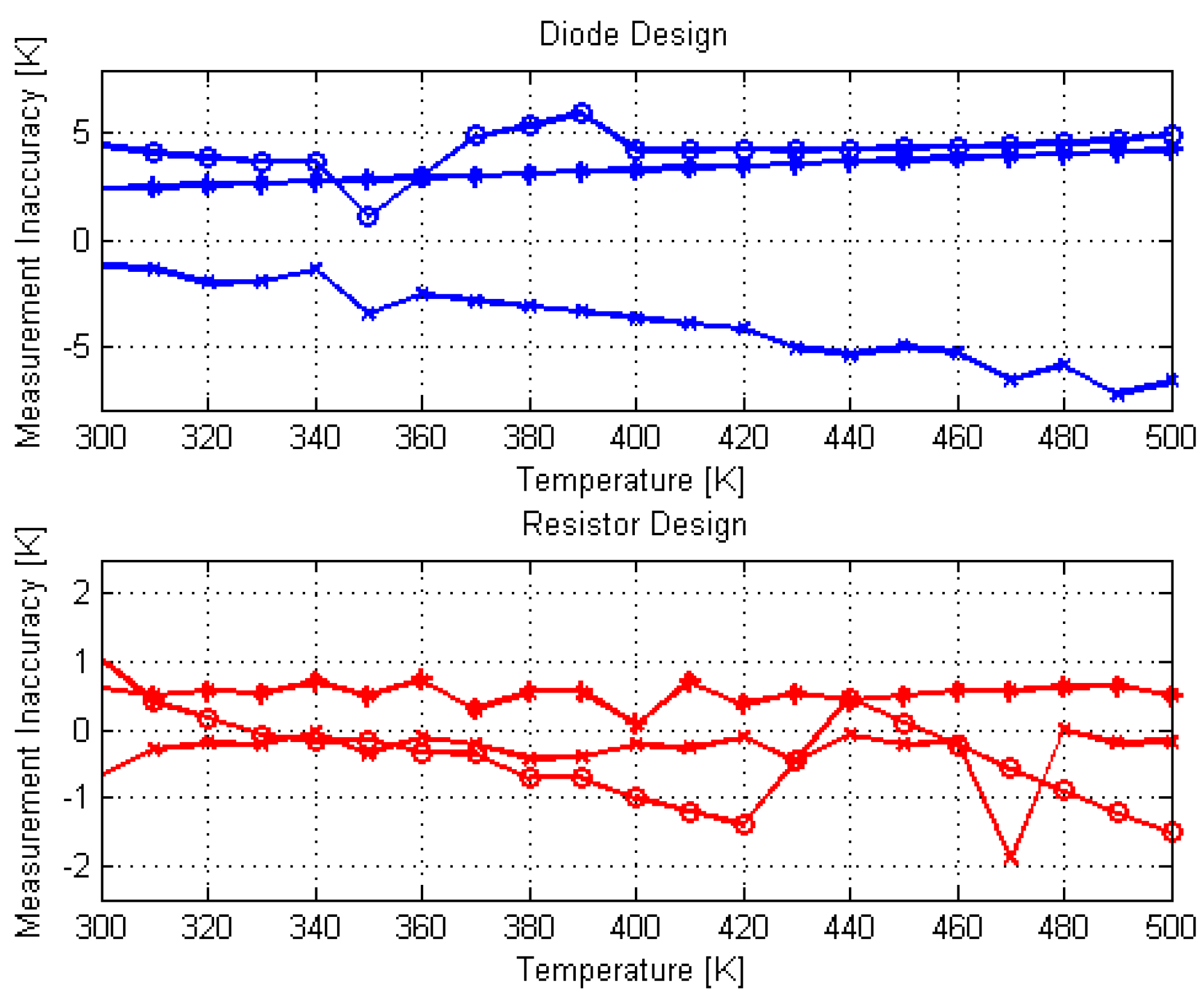

2.3. Measurements and Simulations

2.4. Time Response

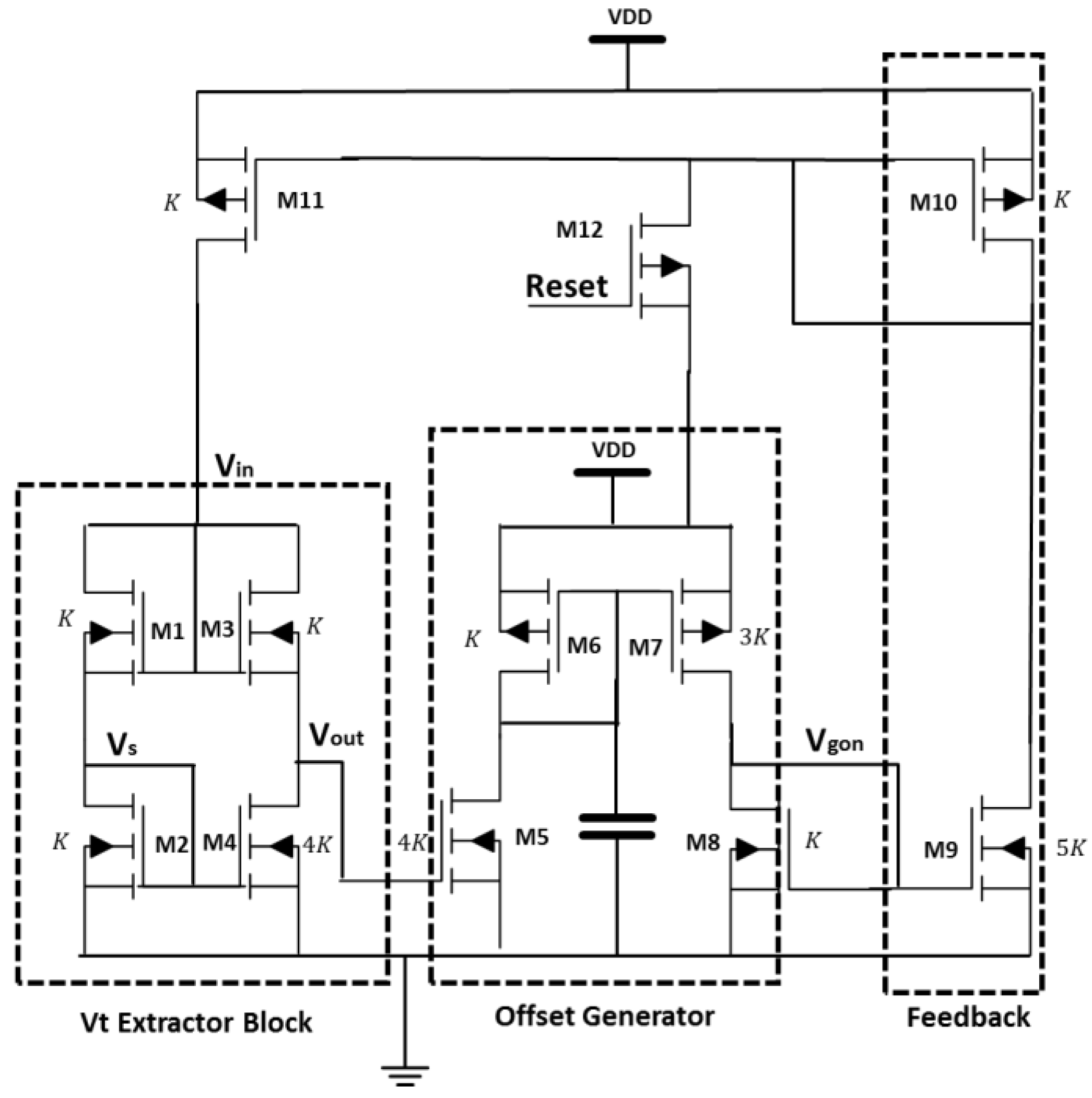

3. Vt Extractor Circuit

3.1. Principle of Operation

3.1.1. Analysis of Vt Extracting Block

3.1.2. Analysis of Offset Generator

3.1.3. Analysis of Feedback Block

3.2. Implementation

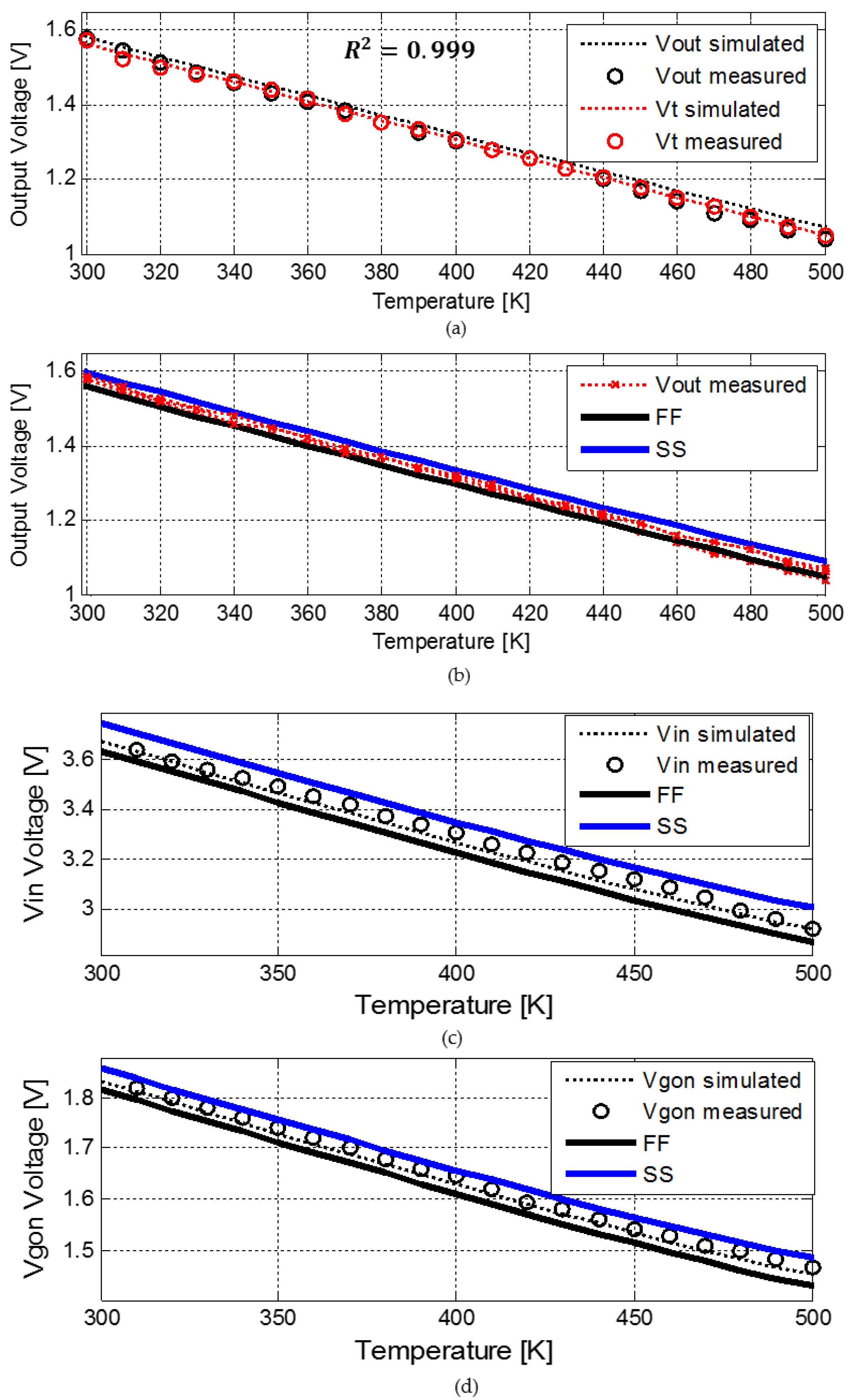

3.3. Measurements and Simulations

3.4. Time Response

4. Summary

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Poirier, C.; McGowen, R.; Bostak, C.; Naffziger, S. Power and temperature control on a 90 nm Itanium-family processor. In Proceedings of the IEEE ISSCC Digest of Technical Papers, San Francisco, CA, USA, 10 February 2005; pp. 304–305. [Google Scholar]

- Duarte, D.; Geannopoulos, G.; Muhgal, U.; Wong, K.; Taylor, G. Temperature sensor design in a high volume manufacturing 65 nm CMOS digital process. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 221–224. [Google Scholar]

- Li, Y.; Lakdawala, H. Smart integrated temperature sensor Mixed signal circuits and systems in 32-nm and beyond. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 19–21 September 2011; pp. 1–8. [Google Scholar]

- Pertijs, M.A.P.; Niederkorn, A.; Ma, X.; McKillop, B.; Bakker, A.; Huijsing, J.H. A CMOS smart temperature sensor with a 3σ inaccuracy of ±0.5 °C from −50 °C to 120 °C. IEEE J. Solid-State Circuits 2005, 40, 454–461. [Google Scholar] [CrossRef]

- Bakker, A.; Huijsing, J. Micropower CMOS temperature sensor with digital output. IEEE J. Solid-State Circuits 1996, 31, 933–937. [Google Scholar] [CrossRef]

- Zviagintsev, A.; Blank, T.; Brouk, I.; Bloom, I.; Nemirovsky, Y. Modeling the Performance of Nano Machined CMOS Transistors for Uncooled IR Sensing. IEEE Trans. Electron Devices 2017, 64, 4657–4663. [Google Scholar] [CrossRef]

- Souza, M.; Pavanello, M.A.; Flandre, D. Low power highly linear temperature sensor based on SOI lateral PIN diodes. In Proceedings of the IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 10–13 October 2016. [Google Scholar]

- De Souza, M.; Rue, B.; Flandre, D.; Pavanello, M.A. Thermal sensing performance of lateral SOI PIN diodes in the 90–400 K range. In Proceedings of the IEEE International SOI Conference, Foster City, CA, USA, 5–8 October 2009. [Google Scholar]

- De Souza, M.; Rue, B.; Flandre, D.; Pavanello, M.A. Thin-Film Lateral SOI PIN Diodes for Thermal Sensing Reaching the Cryogenic Regime. J. Integr. Circuits Syst. 2010, 5, 160–167. [Google Scholar]

- Santra, S.; Guha, P.K.; Ali, S.Z.; Haneef, I.; Udrea, F. Silicon on Insulator Diode Temperature Sensor—A Detailed Analysis for Ultra-High Temperature Operation. IEEE Sens. J. 2010, 10, 997–1003. [Google Scholar] [CrossRef]

- Santra, S.; Guha, P.K.; Haque, M.S.; Ali, S.Z.; Udrea, F. Si diode temperature sensor beyond 300 °C. In Proceedings of the 2007 International Semiconductor Conference, Sinaia, Romania, 15 October–17 September 2007; pp. 415–418. [Google Scholar]

- Chowdhury, G.; Hassibi, A. An On-Chip Temperature Sensor with a Self-Discharging Diode in 32-nm SOI CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 568–572. [Google Scholar] [CrossRef]

- Pathrose, J.; Zou, L.; Chai, K.T.C.; Je, M.; Xu, Y.P. A Time-Domain Smart Temperature Sensor without an Explicit Bandgap Reference in SOI CMOS Operating up to 225 °C. In Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC), Singapore, 11–13 November 2013. [Google Scholar]

- Malits, M.; Nemirovsky, Y. Nanometric Integrated Temperature and Thermal Sensors in CMOS-SOI Technology. Sensors 2017, 17, 1739. [Google Scholar] [CrossRef] [PubMed]

- XFAB CMOS-SOI 1 µm Process XI10. Available online: https://www.xfab.com/en/technology/soi/10-um-xi10/ (accessed on 18 March 2018).

- Gray, P.R.; Hurst, P.J.; Lewis, S.H.; Meyer, R.G. Analysis and Design of Analogue Integrated Circuits, 5th ed.; John Wiley & Sons: New York, NY, USA, 2009; pp. 321–324. [Google Scholar]

- Berkeley Short-Channel IGFET Model (BSIM). Available online: http://www-device.eecs.berkeley.edu/bsim/ (accessed on 8 March 2018).

- Nagelkerke, N.J.D. A note on the general definition of the coefficient of determination. Biometrika 1991, 78, 691–692. [Google Scholar] [CrossRef]

- Li, P.; Pileggi, L.T.; Asheghi, M.; Chandra, R. IC thermal simulation and modeling via efficient multigrid-based approaches. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2006, 25, 1763–1776. [Google Scholar]

- Cheng, Y.; Raha, P.; Teng, C.; Rosenbaum, E.; Kang, S. ILLIADS-T: An electro thermal timing simulator for temperature-sensitive reliability diagnosis of CMOS VLSI chips. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1998, 17, 668–680. [Google Scholar] [CrossRef]

- Yu, Z.; Yergeau, D.; Dutton, R.; Nakagawa, S.; Deeney, J. Fast placement-dependent full chip thermal simulation. In Proceedings of the 2001 International Symposium on VLSI Technology, Systems, and Applications, Hsinchu, Taiwan, 18–20 April 2001; pp. 249–252. [Google Scholar]

- Székely, V.; Rencz, M. Thermal Dynamics and the Time Constant Domain. IEEE Trans. Compon. Packag. Technol. 2000, 23, 587–594. [Google Scholar] [CrossRef]

- Allen, P.E.; Holberg, D.R. CMOS Analog Circuit Design, 3rd ed.; Holt, Rinehard and Winston: New York, NY, USA, 2011; pp. 153–160. [Google Scholar]

- Ueno, K.; Hirose, T.; Asai, T.; Amemiya, Y. A 300 nW, 15 ppm/C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs. IEEE J. Solid-State Circuits 2009, 44, 2047–2054. [Google Scholar] [CrossRef]

- Pathrose, J.; Zou, L.; Chai, K.T.C.; Je, M.; Xu, Y.P. Temperature Sensor Front End in SOI CMOS Operating up to 250 °C. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 496–500. [Google Scholar] [CrossRef]

- Nang, L.K.; Mok, P.K.T. A CMOS voltage reference based on weighted ΔVGS for CMOS low-dropout linear regulators. IEEE J. Solid-State Circuits 2003, 38, 146–150. [Google Scholar]

- Zhou, Z.; Zhu, P.; Shi, Y.; Wang, H.; Ma, Y.; Xu, X.; Tan, L.; Ming, X.; Zhang, B. A CMOS voltage reference based on mutual compensation of Vtn and Vtp. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 341–345. [Google Scholar] [CrossRef]

- Fikos, G.; Siskos, S. Low-Voltage Low-Power Accurate CMOS Vt Extractor. IEEE Trans. Circuit Syst. II Analog Digit. Signal Process. 2001, 48, 626–628. [Google Scholar] [CrossRef]

| Sensor | Process | Range (K) | Area (mm2) | Power (µW) | Maximum Sensitivity (mV/K) | Linearity (R2) | Accuracy (K) | Calibration Need |

|---|---|---|---|---|---|---|---|---|

| [7] | 150 nm CMOS SOI | 150–400 | - | - | 0.7 | 0.99 | - | Needed |

| [9] | FD CMOS SOI | 100–400 | 0.04 | - | −2.2 | - | 2 | Needed |

| [10] | 1 µm CMOS SOI | 300–1053 | - | 27 | −1.22 | - | - | - |

| [12] | 32 nm CMOS SOI | 270–370 | 0.001 | 100 | - | - | 1.95 (3ϭ) | Needed |

| [13] | 1 µm PD CMOS SOI | 300–500 | 0.45 | 112.5 | - | - | 2 | Needed |

| [24] | 0.35 µm CMOS | 250–350 | 0.055 | 0.3 | 15 (ppm/C) | - | - | - |

| [25] | 1 µm PD CMOS SOI | 250–520 | 0.23 | - | 27 (ppm/C) | - | 1.8 (%) | Needed |

| [27] | 0.35 µm CMOS | 270–400 | 0.011 | 24 | 11.8 (ppm/C) | - | 0.153 (%) | - |

| Resistor based PTAT(This work) | 1 µm PD CMOS SOI | 300–500 | 0.0085 | 250 | 9.8 | 0.9988 | 1.5 | Needed |

| Diode based PTAT(This work) | 1 µm PD CMOS SOI | 300–500 | 0.026 | 45 | 4.7 | 0.9985 | 6.5 | Needed |

| Vt Extractor Circuit(This work) | 1 µm PD CMOS SOI | 300–500 | 0.008 | 27.5 | 2.6 | 0.999 | 1.5 | Not Needed |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Malits, M.; Brouk, I.; Nemirovsky, Y. Study of CMOS-SOI Integrated Temperature Sensing Circuits for On-Chip Temperature Monitoring. Sensors 2018, 18, 1629. https://doi.org/10.3390/s18051629

Malits M, Brouk I, Nemirovsky Y. Study of CMOS-SOI Integrated Temperature Sensing Circuits for On-Chip Temperature Monitoring. Sensors. 2018; 18(5):1629. https://doi.org/10.3390/s18051629

Chicago/Turabian StyleMalits, Maria, Igor Brouk, and Yael Nemirovsky. 2018. "Study of CMOS-SOI Integrated Temperature Sensing Circuits for On-Chip Temperature Monitoring" Sensors 18, no. 5: 1629. https://doi.org/10.3390/s18051629

APA StyleMalits, M., Brouk, I., & Nemirovsky, Y. (2018). Study of CMOS-SOI Integrated Temperature Sensing Circuits for On-Chip Temperature Monitoring. Sensors, 18(5), 1629. https://doi.org/10.3390/s18051629