A Hybrid Readout Solution for GaN-Based Detectors Using CMOS Technology †

Abstract

:1. Introduction

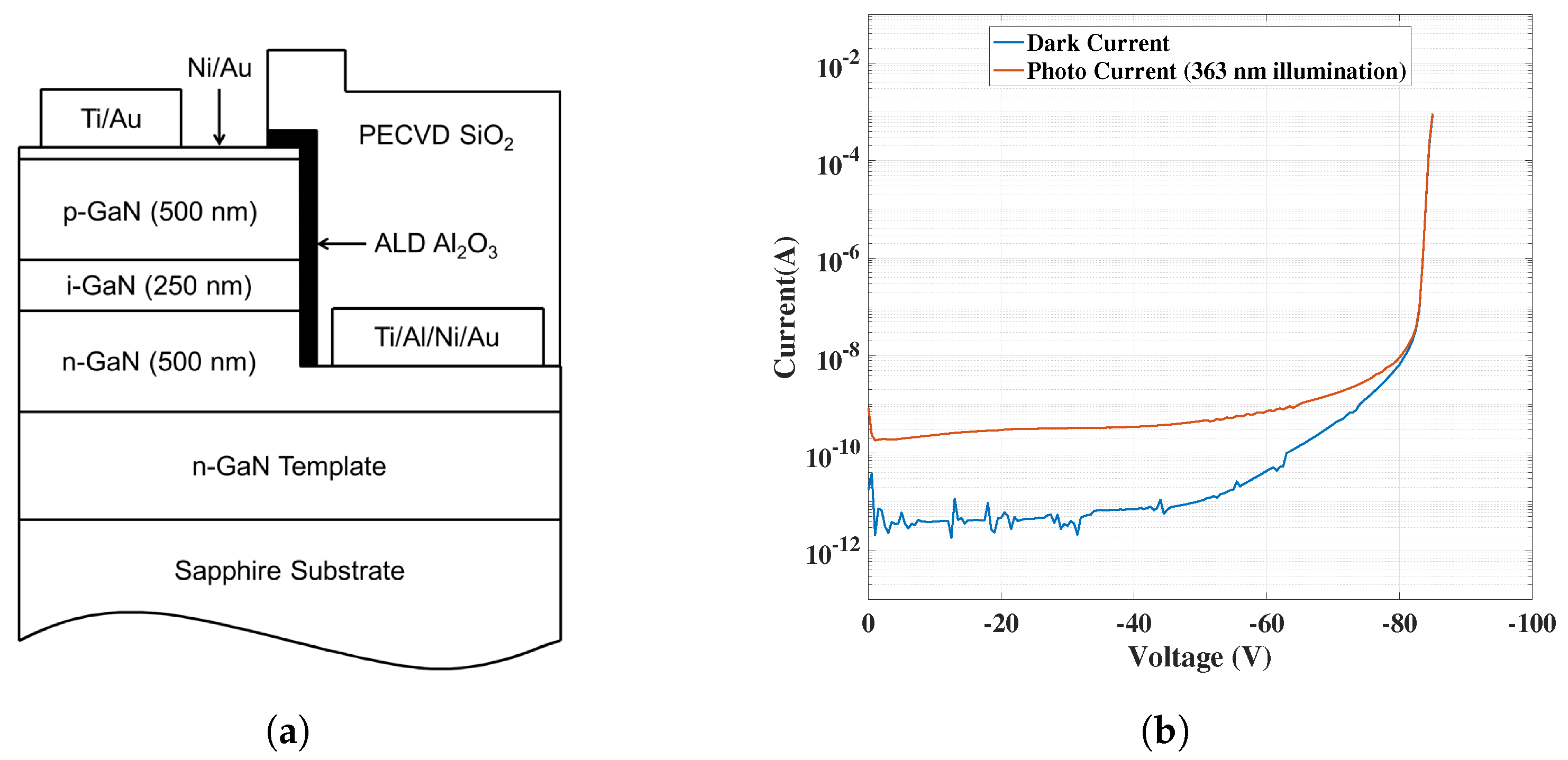

2. Gallium Nitride APDs

3. Design of CMOS Readout Integrated Circuit

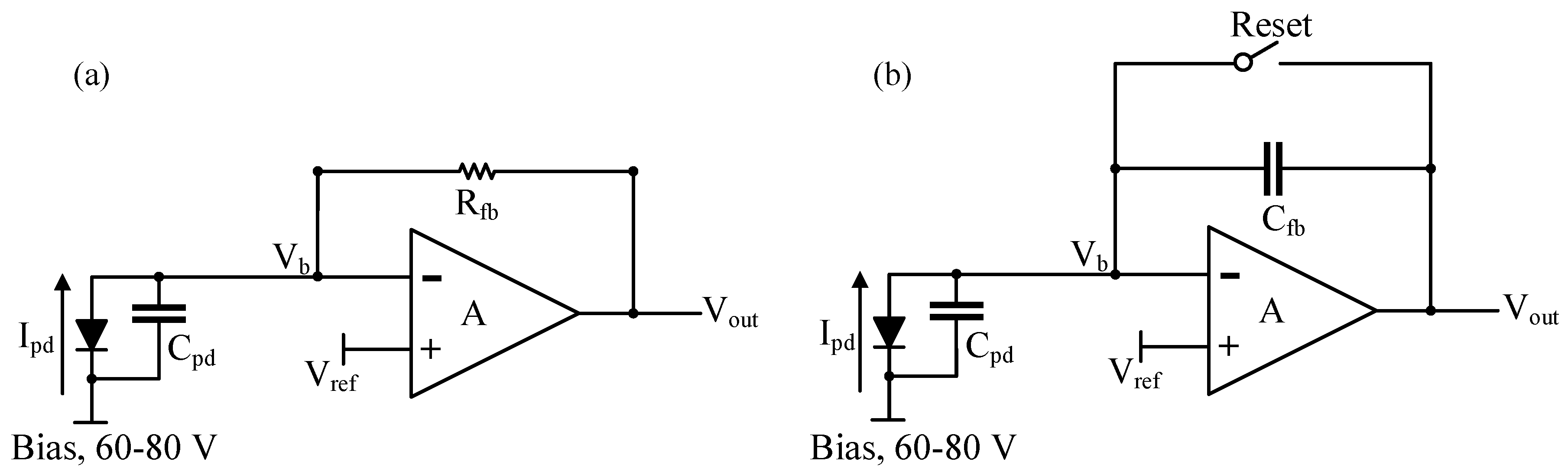

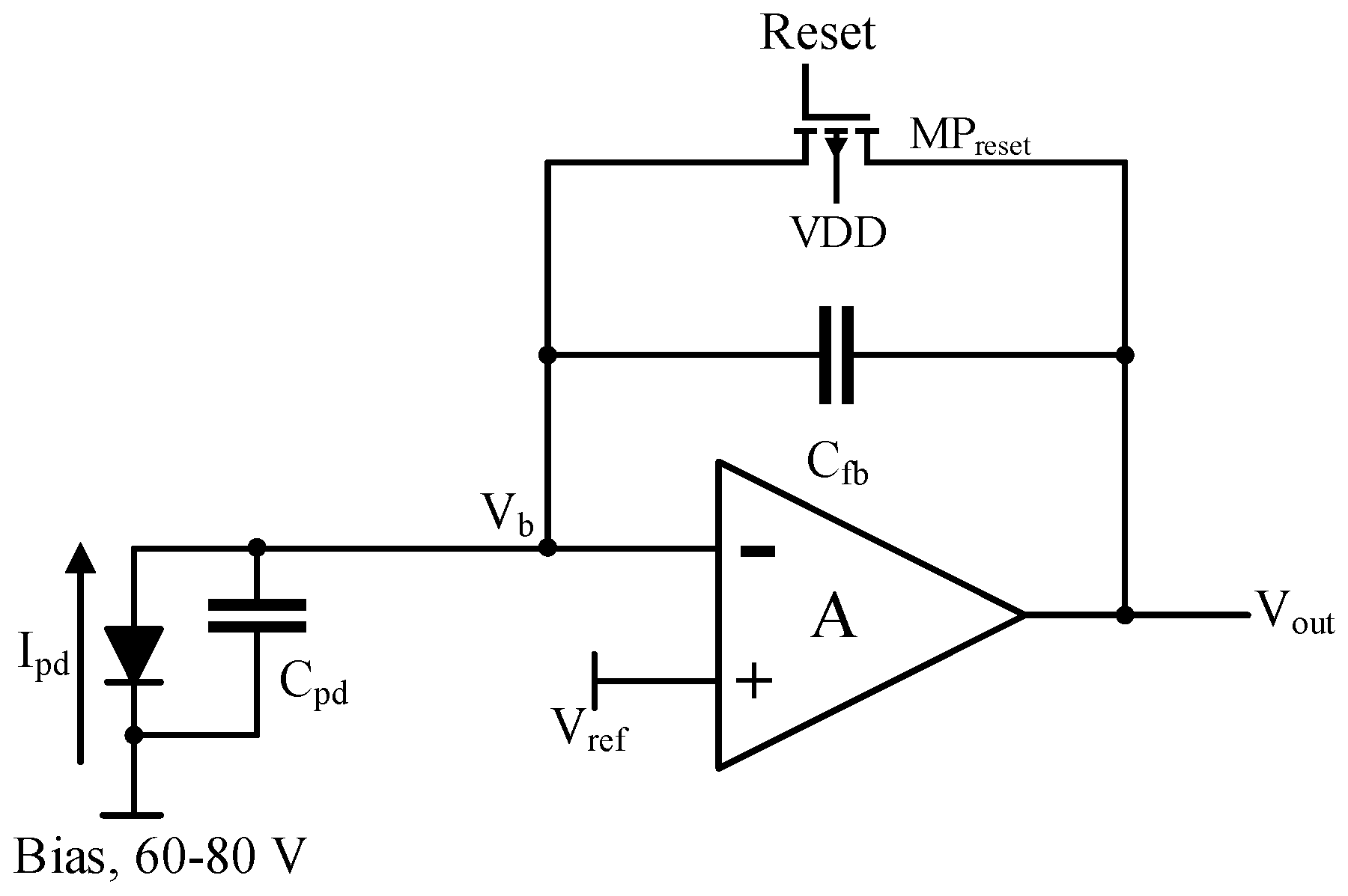

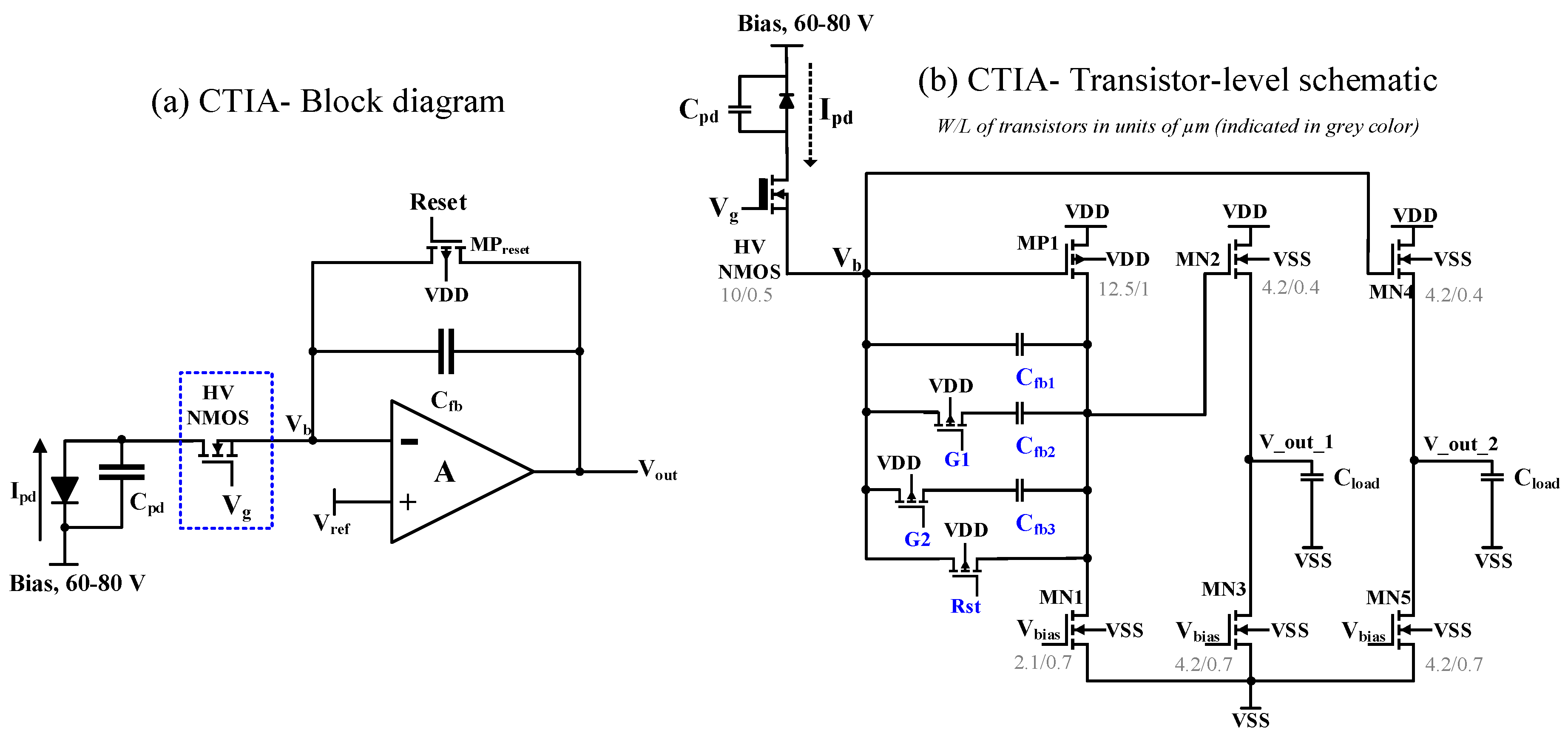

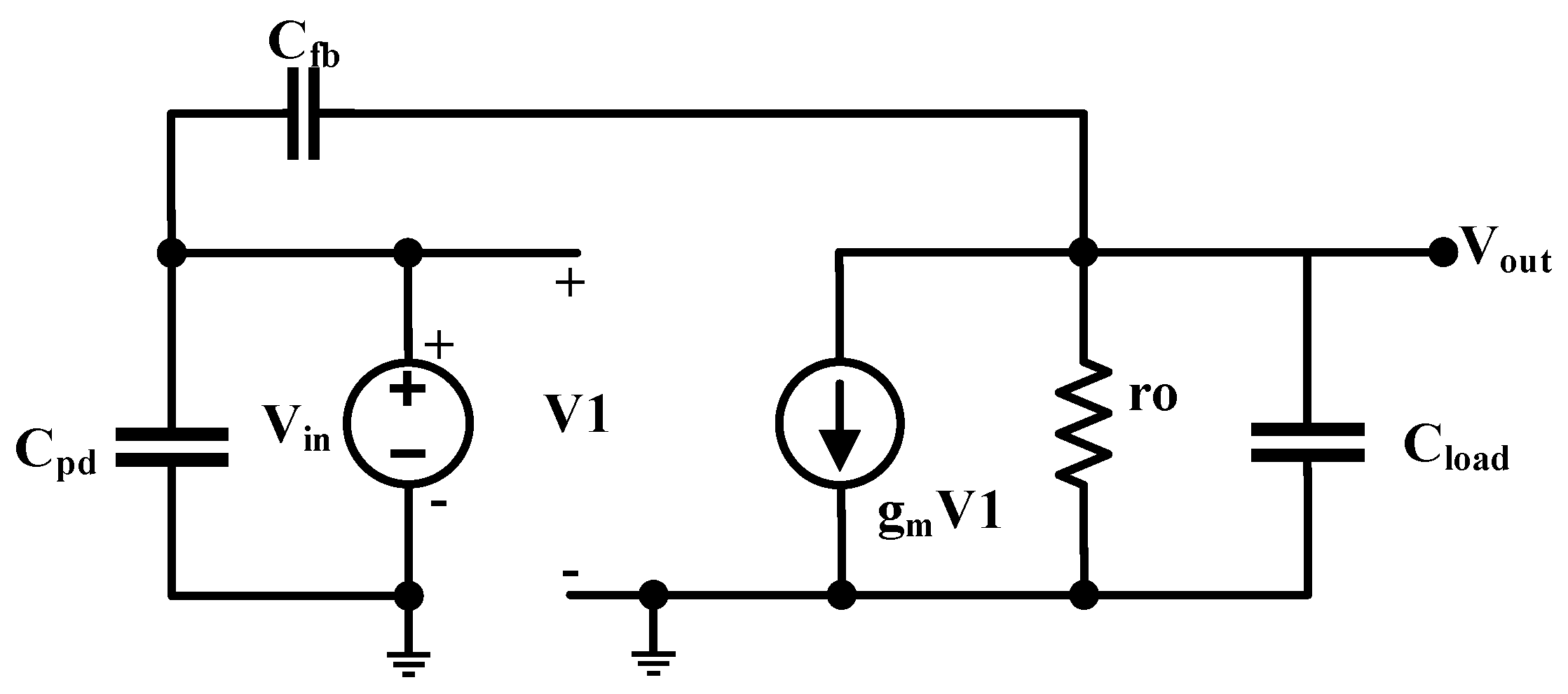

3.1. Capacitive Transimpedance Amplifier (CTIA)

3.1.1. Design Challenge- High Voltage Problem and Quenching

3.2. Noise Analysis

4. Measurement Results

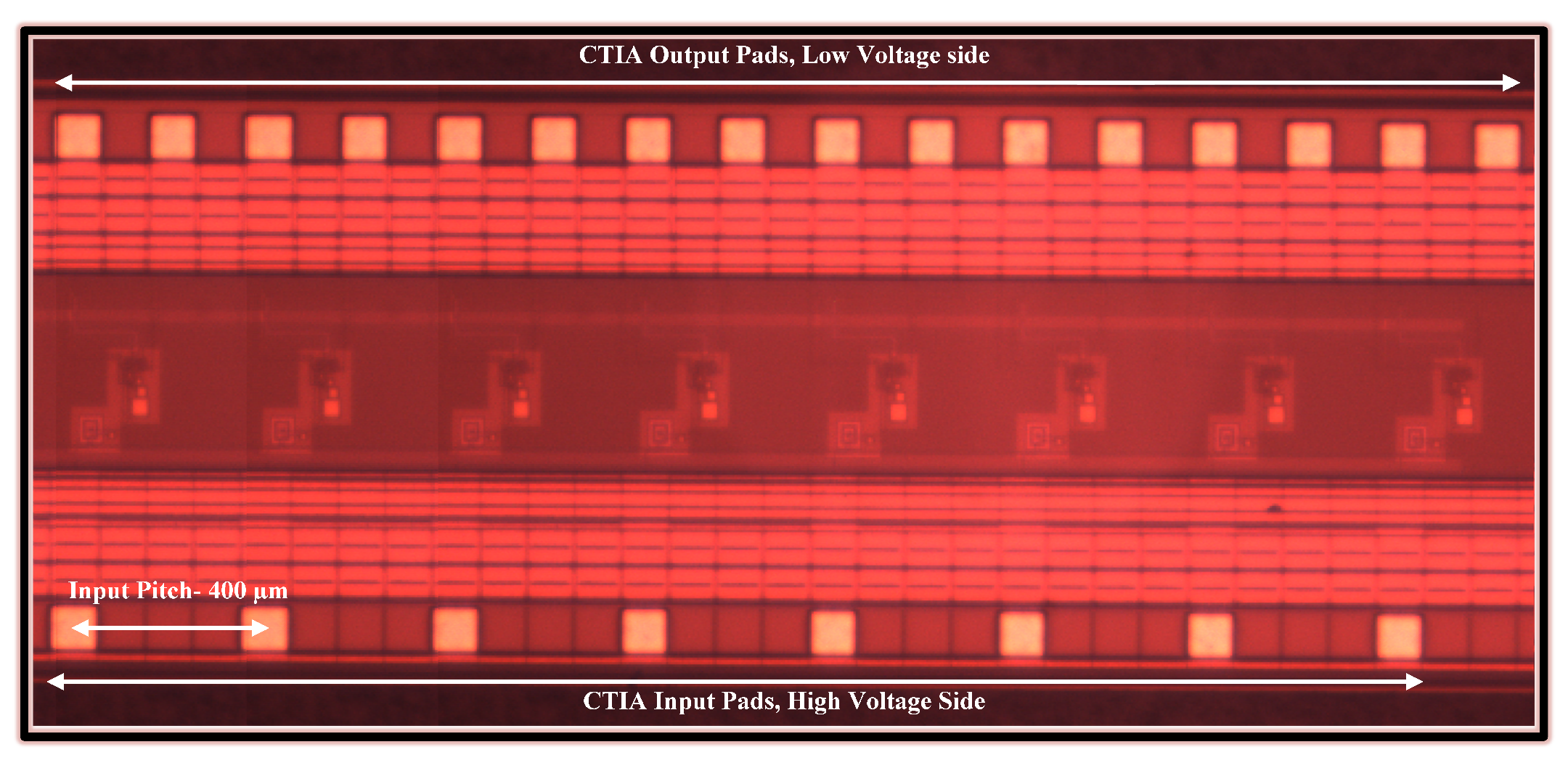

4.1. CTIA Characterization Results

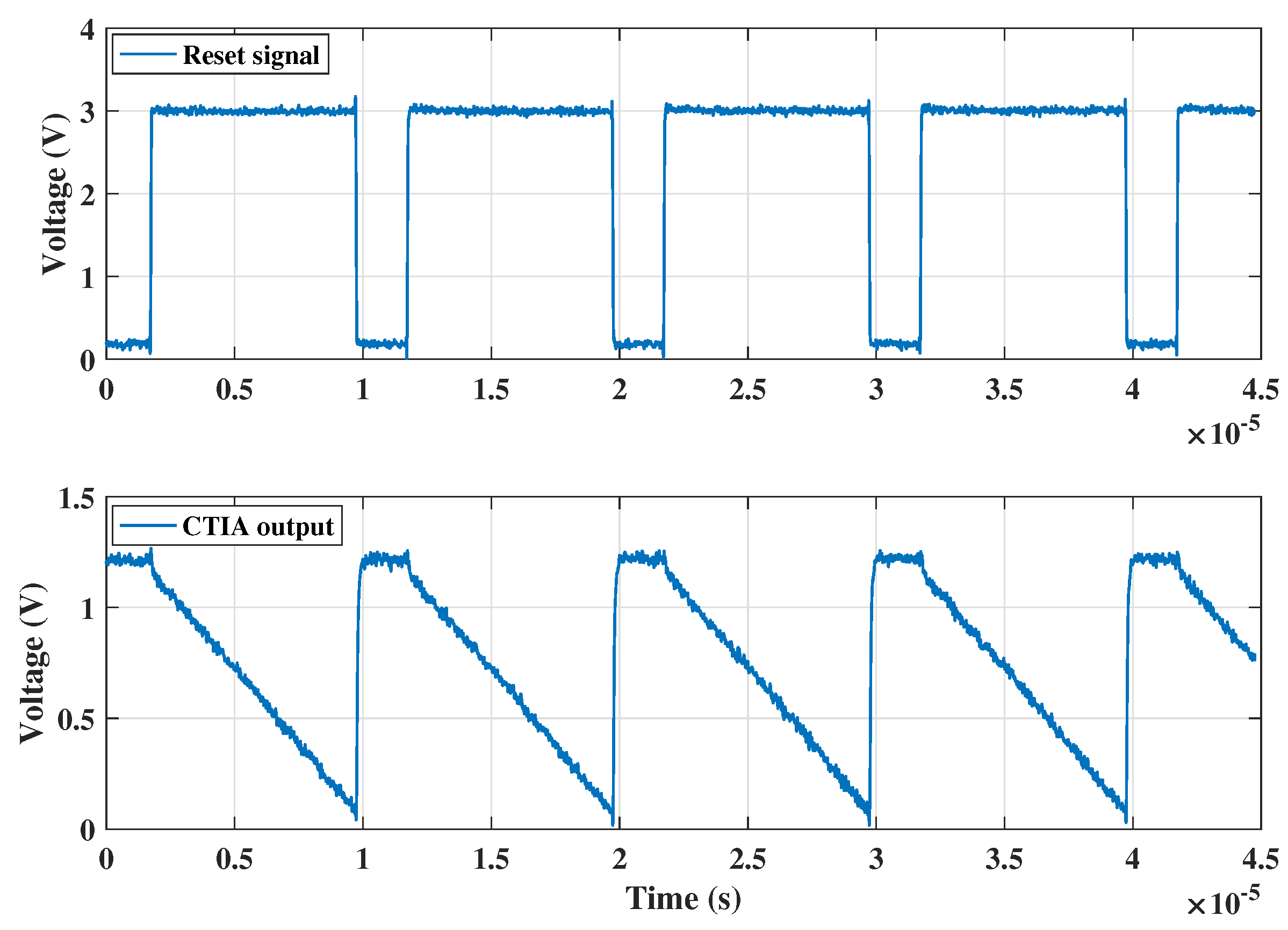

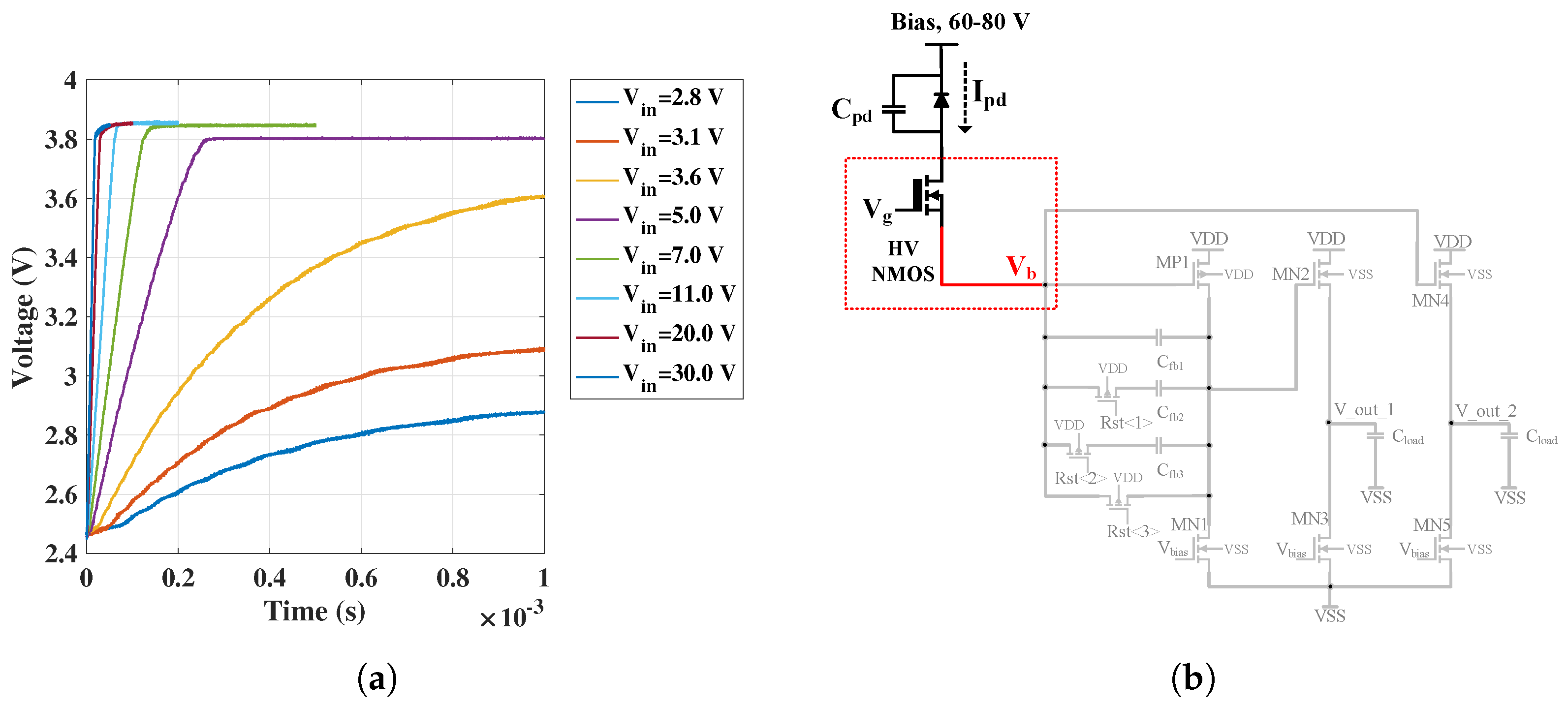

4.1.1. CTIA Transient Behavior

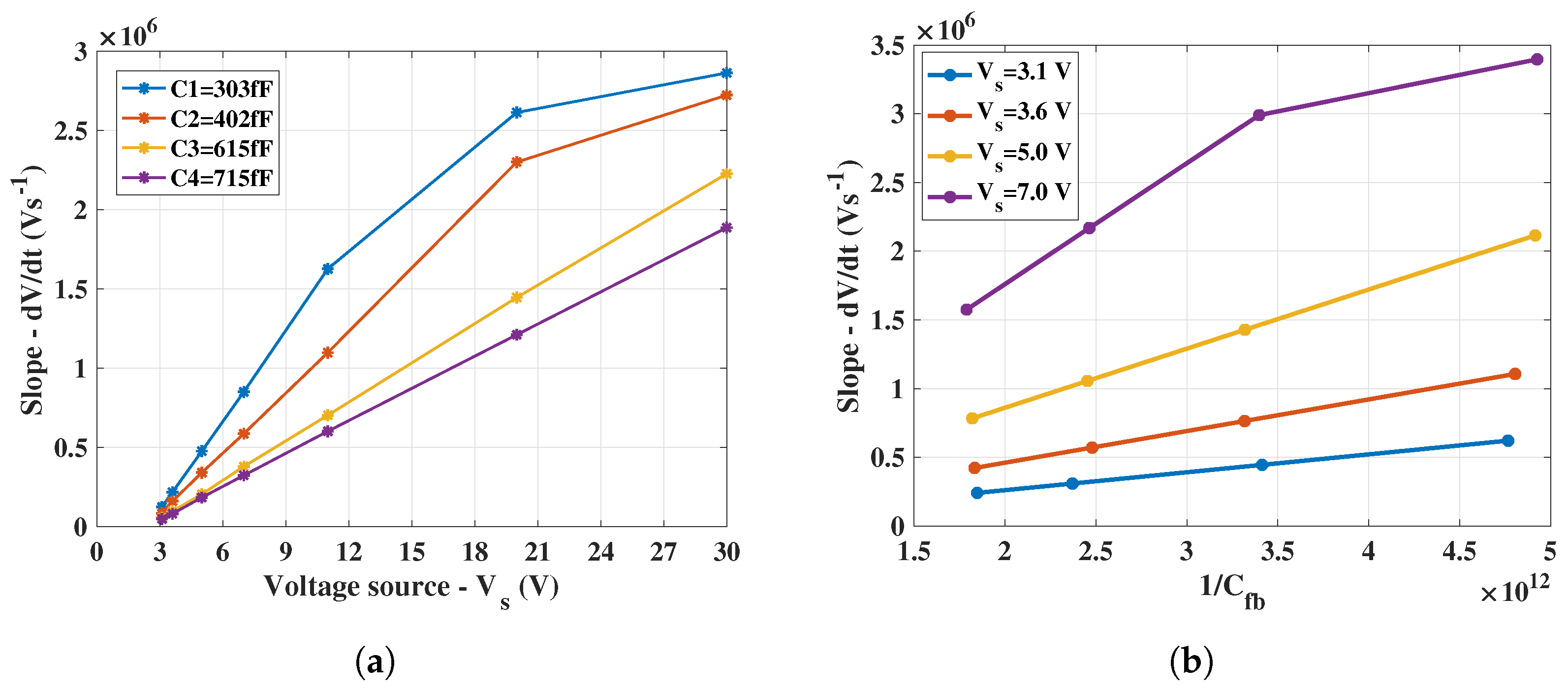

4.1.2. Slew Rate

4.1.3. Effective Feedback Capacitances

4.1.4. Charge-to-Voltage Conversion Factor

4.1.5. Voltage Limiter Functionality

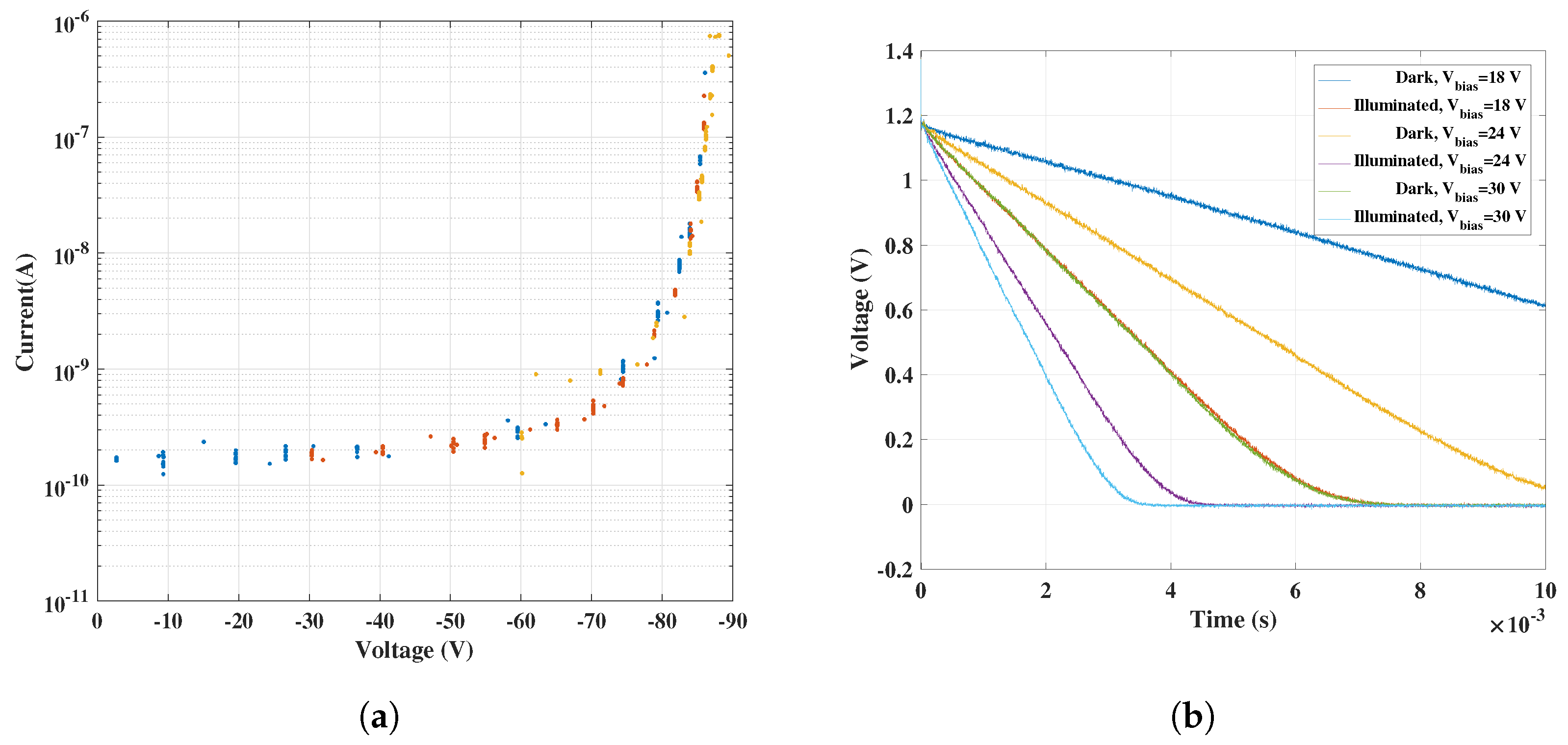

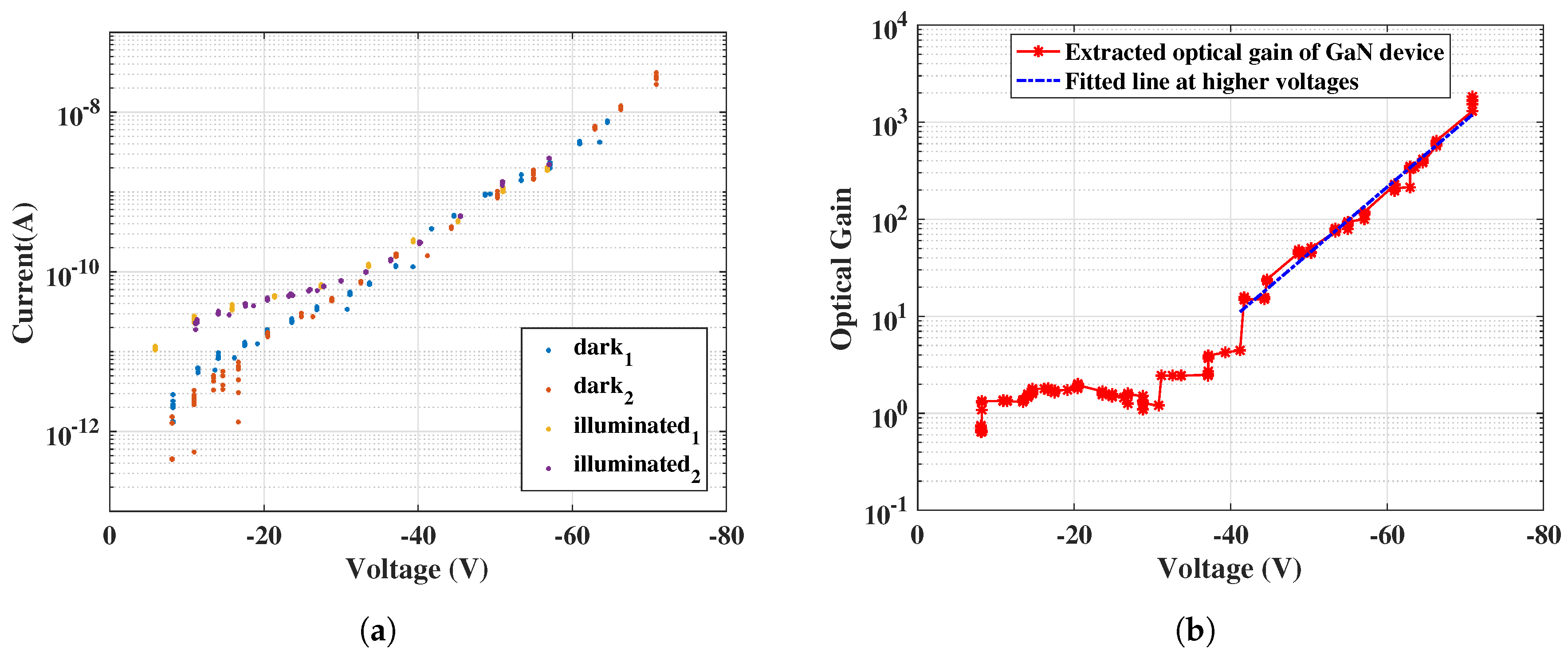

4.2. GaN + CMOS Measurement Results—Demonstration of UV Sensitivity

4.3. Noise Measurement

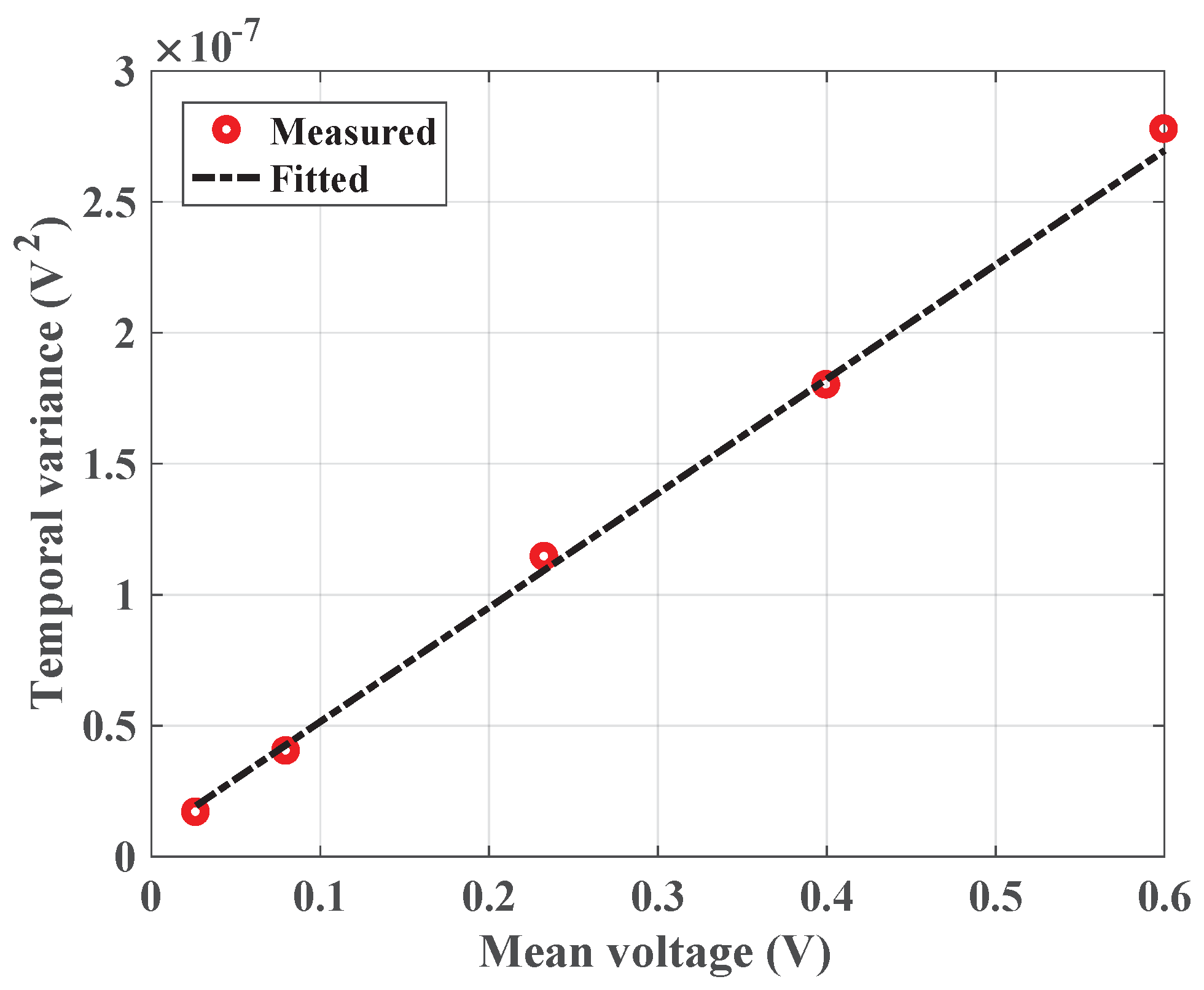

Conversion Gain and Read Noise

CTIA- Reset Noise

5. Next-Generation Readout Improvements

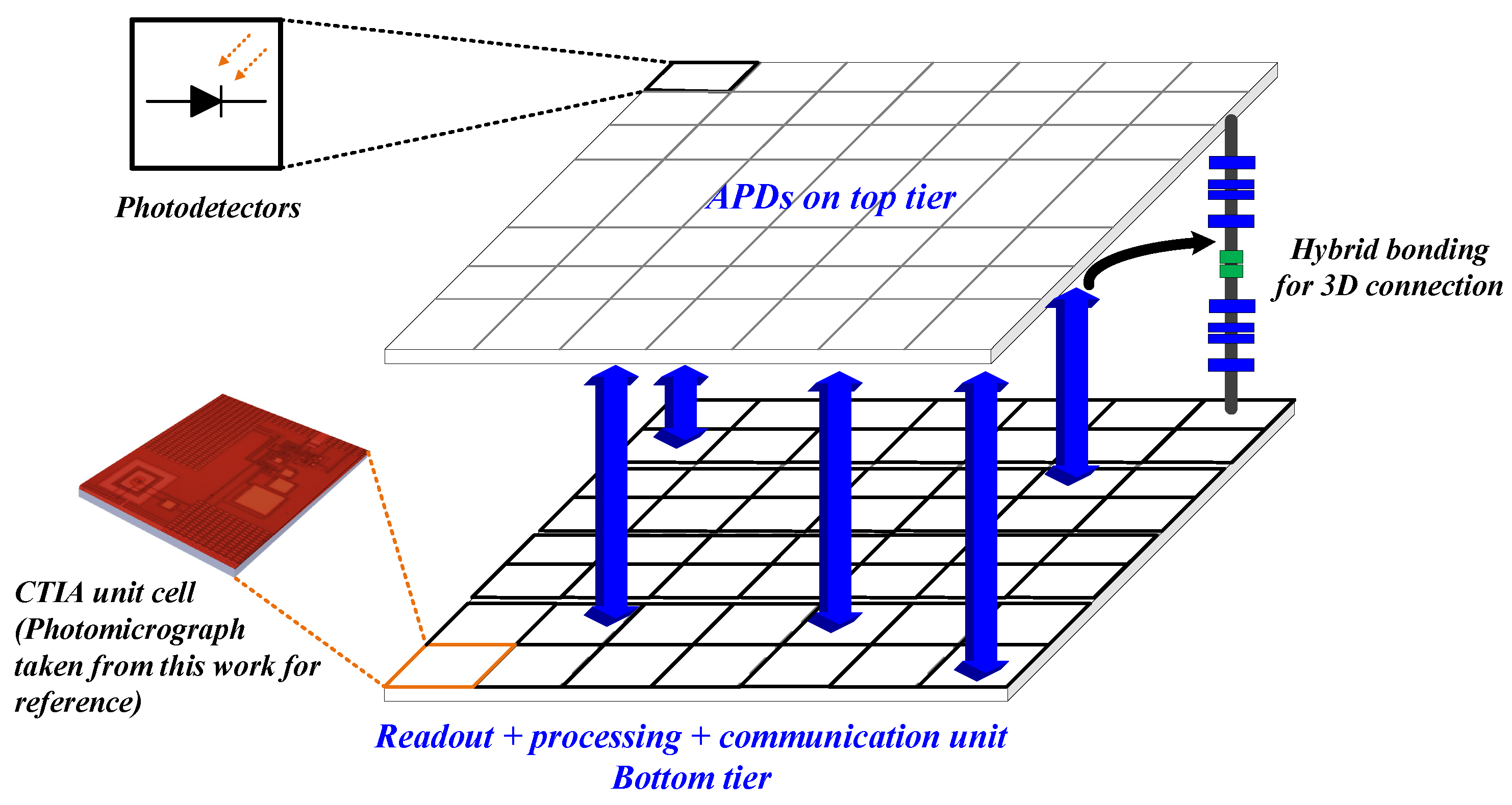

6. Hybridizing with 3D Stacked Technology—A Perspective

7. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Abbreviations

| UV | Ultraviolet |

| APDs | Avalanche photodiodes |

| GaN | Gallium nitride |

| CMOS | Complementary metal-oxide-semiconductor |

| SNR | Signal-to-noise ratio |

| TIA | Transimpedance amplifier |

| RTIA | Resistive transimpedance amplifier |

| CTIA | Capacitive transimpedance amplifier |

| HV | High voltage |

| CVF | Charge-to-voltage conversion factor |

| ADC | Analog-to-digital converter |

| CDS | correlated double sampling |

| IC | Integrated circuit |

References

- McGrath, M.; Feldman, P.; Strobel, D.; Retherford, K.; Wolven, B.; Moos, H. HST/STIS ultraviolet imaging of Europa. Bull. Am. Astron. Soc. 2000, 32, 1056. [Google Scholar]

- Feldman, P.D.; A’Hearn, M.F.; Bertaux, J.L.; Feaga, L.M.; Parker, J.W.; Schindhelm, E.; Steffl, A.J.; Stern, S.A.; Weaver, H.A.; Sierks, H.; et al. Measurements of the near-nucleus coma of comet 67P/Churyumov-Gerasimenko with the Alice far-ultraviolet spectrograph on Rosetta. Astron. Astrophys. 2015, 583, A8. [Google Scholar] [CrossRef]

- Feldman, P.D.; Steffl, A.J.; Parker, J.W.; A’Hearn, M.F.; Bertaux, J.L.; Stern, S.A.; Weaver, H.A.; Slater, D.C.; Versteeg, M.; Throop, H.B.; et al. Rosetta-Alice observations of exospheric hydrogen and oxygen on Mars. Icarus 2011, 214, 394–399. [Google Scholar] [CrossRef]

- Nikzad, S.; Hoenk, M.; Jewell, A.D.; Hennessy, J.J.; Carver, A.G.; Jones, T.J.; Goodsall, T.M.; Hamden, E.T.; Suvarna, P.; Bulmer, J.; et al. Single Photon Counting UV Solar-Blind Detectors Using Silicon and III-Nitride Materials. Sensors 2016, 16, 927. [Google Scholar] [CrossRef] [PubMed]

- Dries, J.C.; Miles, B.; Stettner, R. A 32 × 32 pixel FLASH laser radar system incorporating InGaAs PIN and APD detectors. Proc. SPIE 2004, 5412, 251. [Google Scholar] [CrossRef]

- Hsieh, C.C.; Wu, C.Y.; Jih, F.W.; Sun, T.P. Focal-plane-arrays and CMOS readout techniques of infrared imaging systems. IEEE Trans. Circuits Syst. Video Technol. 1997, 7, 594–605. [Google Scholar] [CrossRef]

- Bai, Y.; Bernd, S.G.; Hosack, J.R.; Farris, M.C.; Montroy, J.T.; Bajaj, J. Hybrid CMOS focal plane array with extended UV and NIR response for space applications. Proc. SPIE 2003, 5167, 83–93. [Google Scholar] [CrossRef]

- Kavusi, S.; Ghosh, K.; Fife, K.; El Gamal, A. A 0.18 μm CMOS 1000 frames/sec, 138 dB Dynamic Range Readout Circuit for 3D-IC IR Focal Plane Arrays. In Proceedings of the Custom Integrated Circuits Conference (CICC’06), San Jose, CA, USA, 10–13 September 2006; pp. 229–232. [Google Scholar] [CrossRef]

- Keast, C.L.; Aull, B.; Burns, J.; Chen, C.; Knecht, J.; Tyrrell, B.; Warner, K.; Wheeler, B.; Suntharaligam, V.; Wyatt, P.; et al. Three-dimensional integration technology for advanced focal planes. MRS Online Proc. Libr. Arch. 2008, 1112. [Google Scholar] [CrossRef]

- Henry, D.; Alozy, J.; Berthelot, A.; Cuchet, R.; Chantre, C.; Campbell, M. TSV last for hybrid pixel detectors: Application to particle physics and imaging experiments. In Proceedings of the 2013 IEEE 63rd Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013; pp. 568–575. [Google Scholar]

- Pavia, J.M.; Scandini, M.; Lindner, S.; Wolf, M.; Charbon, E. A 1 × 400 Backside-Illuminated SPAD Sensor With 49.7 ps Resolution, 30 pJ/Sample TDCs Fabricated in 3D CMOS Technology for Near-Infrared Optical Tomography. IEEE J. Solid-State Circuits 2015, 50, 2406–2418. [Google Scholar] [CrossRef]

- Padmanabhan, P.; Hancock, B.; Nikzad, S.; Bell, L.D.; Kroep, K.; Charbon, E. A CMOS Front-end for GaN-based UV Imaging. In Proceedings of the International Image Sensor Workshop, Hiroshima, Japan, 30 May–2 June 2017. [Google Scholar]

- Tian, H.; Fowler, B.; Gamal, A.E. Analysis of temporal noise in CMOS photodiode active pixel sensor. IEEE J. Solid-State Circuits 2001, 36, 92–101. [Google Scholar] [CrossRef]

- Fowler, B.A.; Balicki, J.; How, D.; Godfrey, M. Low-FPN high-gain capacitive transimpedance amplifier for low-noise CMOS image sensors. Proc. SPIE 2001, 4306, 68–78. [Google Scholar]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw-Hill Education: New York, NY, USA, 2001. [Google Scholar]

- Hynecek, J. Spectral analysis of reset noise observed in CCD charge-detection circuits. IEEE Trans. Electron Devices 1990, 37, 640–647. [Google Scholar] [CrossRef]

- Suvarna, P.; Tungare, M.; Leathersich, J.M.; Agnihotri, P.; Shahedipour-Sandvik, F.; Douglas Bell, L.; Nikzad, S. Design and Growth of Visible-Blind and Solar-Blind III-N APDs on Sapphire Substrates. J. Electron. Mater. 2013, 42, 854–858. [Google Scholar] [CrossRef]

- Theuwissen, A.J. CMOS image sensors: State-of-the-art. Solid-State Electron. 2008, 52, 1401–1406. [Google Scholar] [CrossRef]

- Janesick, J.; Klaasen, K.; Elliott, T. CCD Charge Collection Efficiency And The Photon Transfer Technique. Proc. SPIE 1985, 0570, 7–20. [Google Scholar] [CrossRef]

- McIntyre, R.J. Multiplication noise in uniform avalanche diodes. IEEE Trans. Electron Devices 1966, 13, 164–168. [Google Scholar] [CrossRef]

| Parameter | Results |

|---|---|

| Photodetector technology | GaN avalanche photodiode |

| APD bias voltage | 0–80 V, proportional-mode |

| Readout technology | 0.35 µm HV CMOS, Supply voltage = 3.3 V |

| Readout topology | Capacitive transimpedance amplifier (CTIA) |

| CTIA array size | 1 × 8 |

| CTIA area | ≈ 5 mm × 1 mm |

| Input current range | 150 pA–1.5 µA |

| Slew rate | 2.8 V/µs |

| Conversion gain | 0.43 µV/e− |

| CTIA read noise | 88 µV |

| CTIA reset noise | 121 µV |

| Power consumption | 1.5 mW |

| Avalanche Gain |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Padmanabhan, P.; Hancock, B.; Nikzad, S.; Bell, L.D.; Kroep, K.; Charbon, E. A Hybrid Readout Solution for GaN-Based Detectors Using CMOS Technology. Sensors 2018, 18, 449. https://doi.org/10.3390/s18020449

Padmanabhan P, Hancock B, Nikzad S, Bell LD, Kroep K, Charbon E. A Hybrid Readout Solution for GaN-Based Detectors Using CMOS Technology. Sensors. 2018; 18(2):449. https://doi.org/10.3390/s18020449

Chicago/Turabian StylePadmanabhan, Preethi, Bruce Hancock, Shouleh Nikzad, L. Douglas Bell, Kees Kroep, and Edoardo Charbon. 2018. "A Hybrid Readout Solution for GaN-Based Detectors Using CMOS Technology" Sensors 18, no. 2: 449. https://doi.org/10.3390/s18020449

APA StylePadmanabhan, P., Hancock, B., Nikzad, S., Bell, L. D., Kroep, K., & Charbon, E. (2018). A Hybrid Readout Solution for GaN-Based Detectors Using CMOS Technology. Sensors, 18(2), 449. https://doi.org/10.3390/s18020449