A CMOS SPAD Imager with Collision Detection and 128 Dynamically Reallocating TDCs for Single-Photon Counting and 3D Time-of-Flight Imaging

Abstract

:1. Introduction

2. Sensor Design

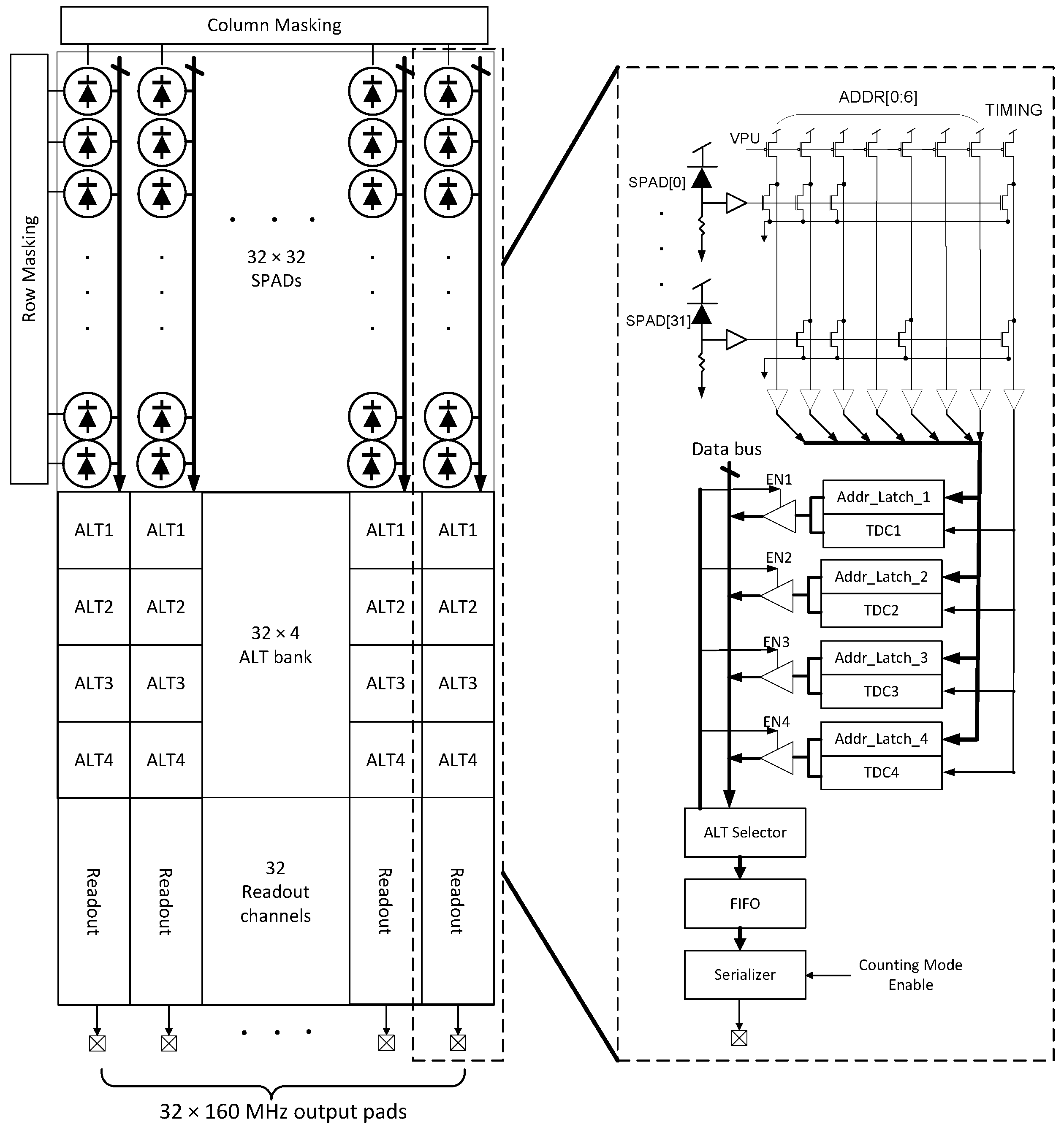

2.1. Sensor Architecture

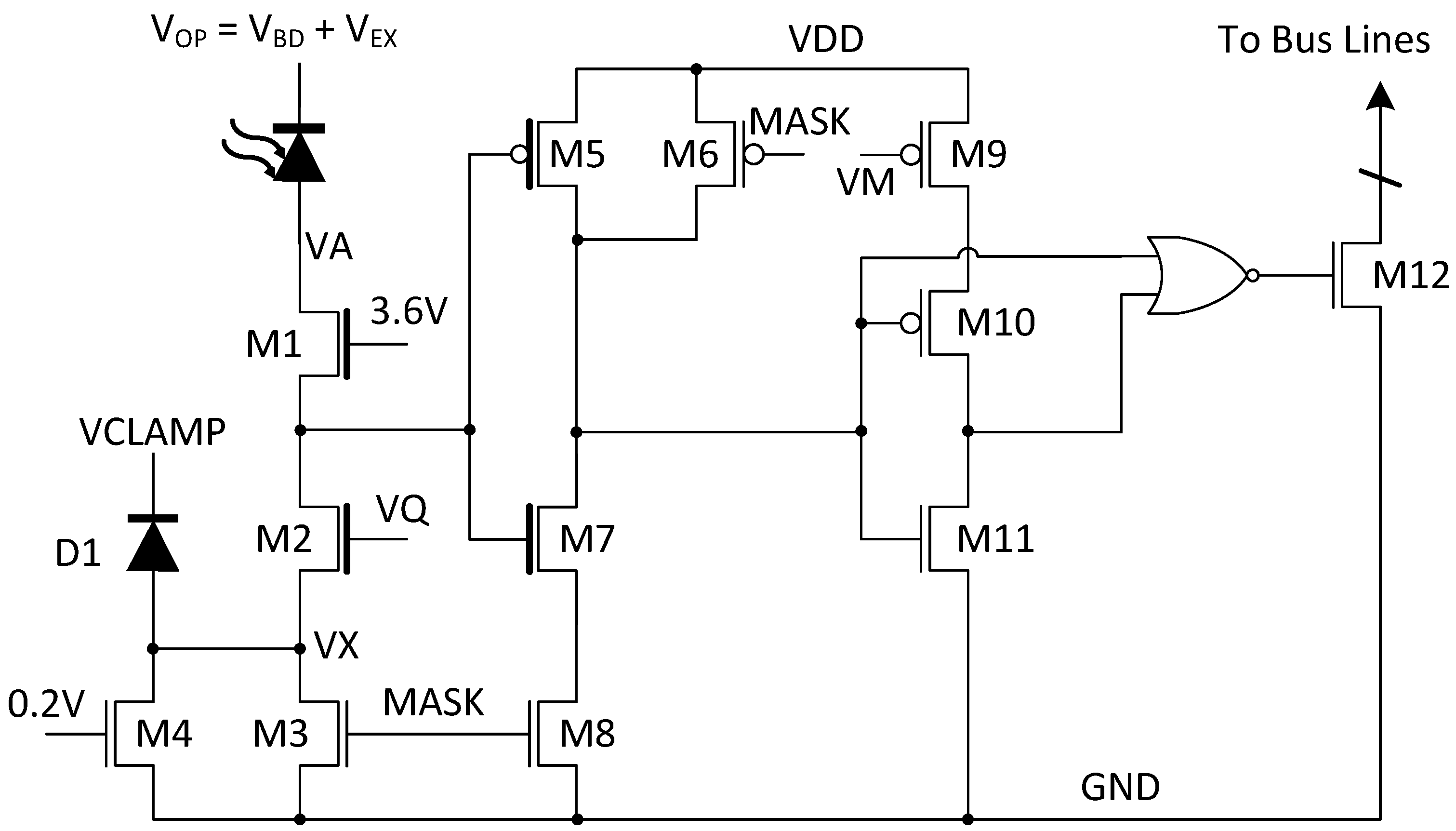

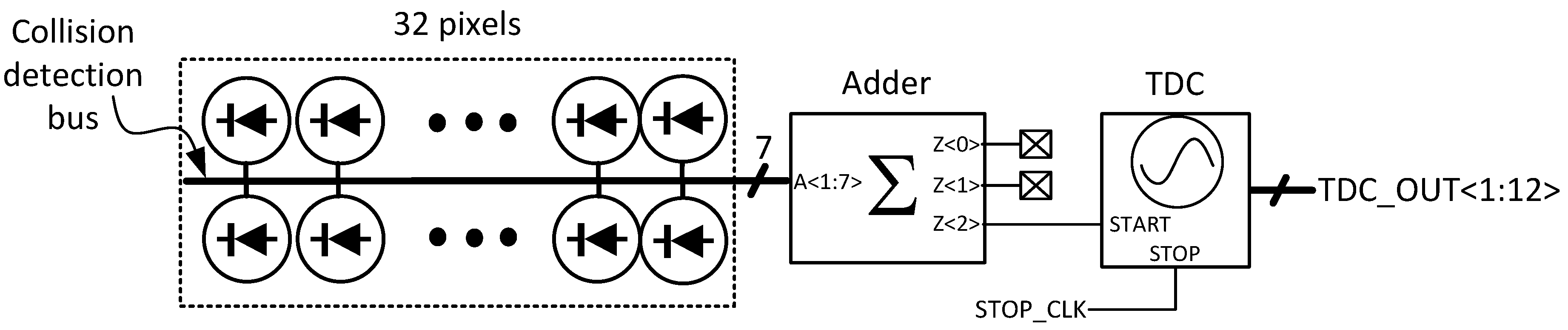

2.2. Pixel Schematic and Collision Detection Bus

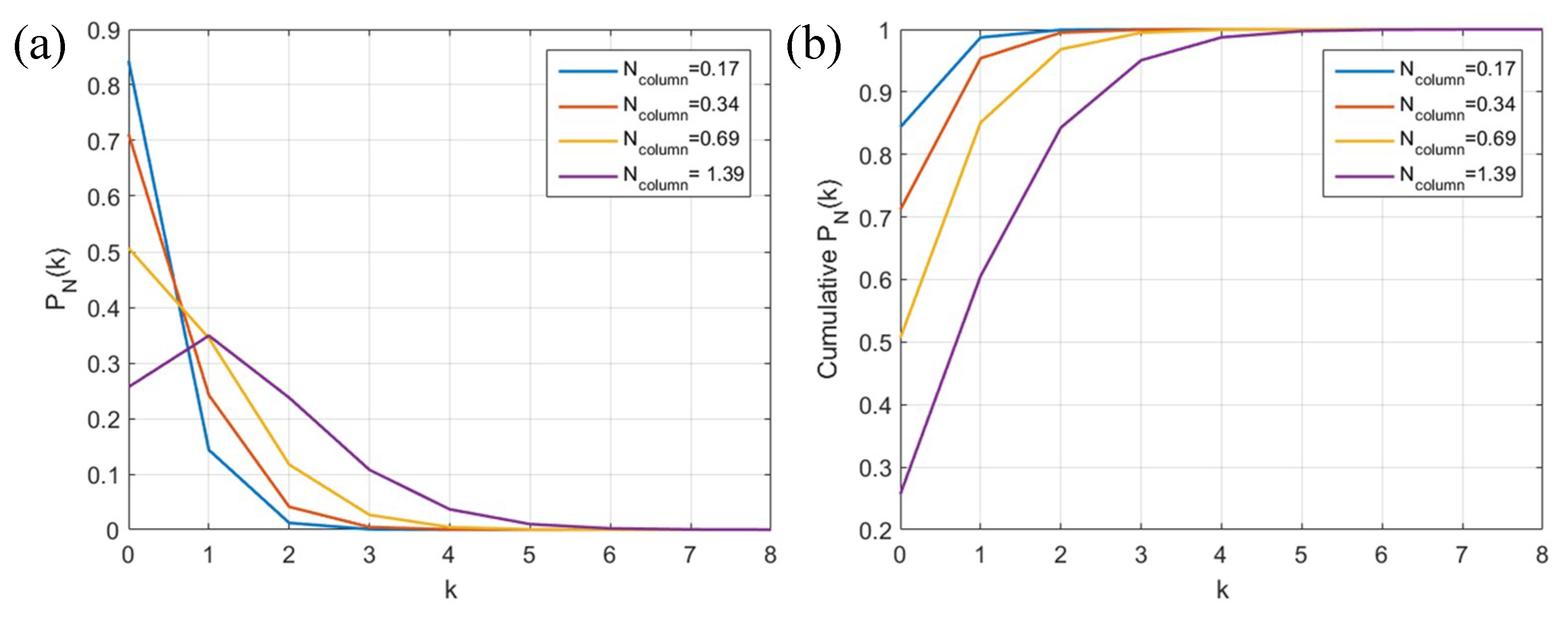

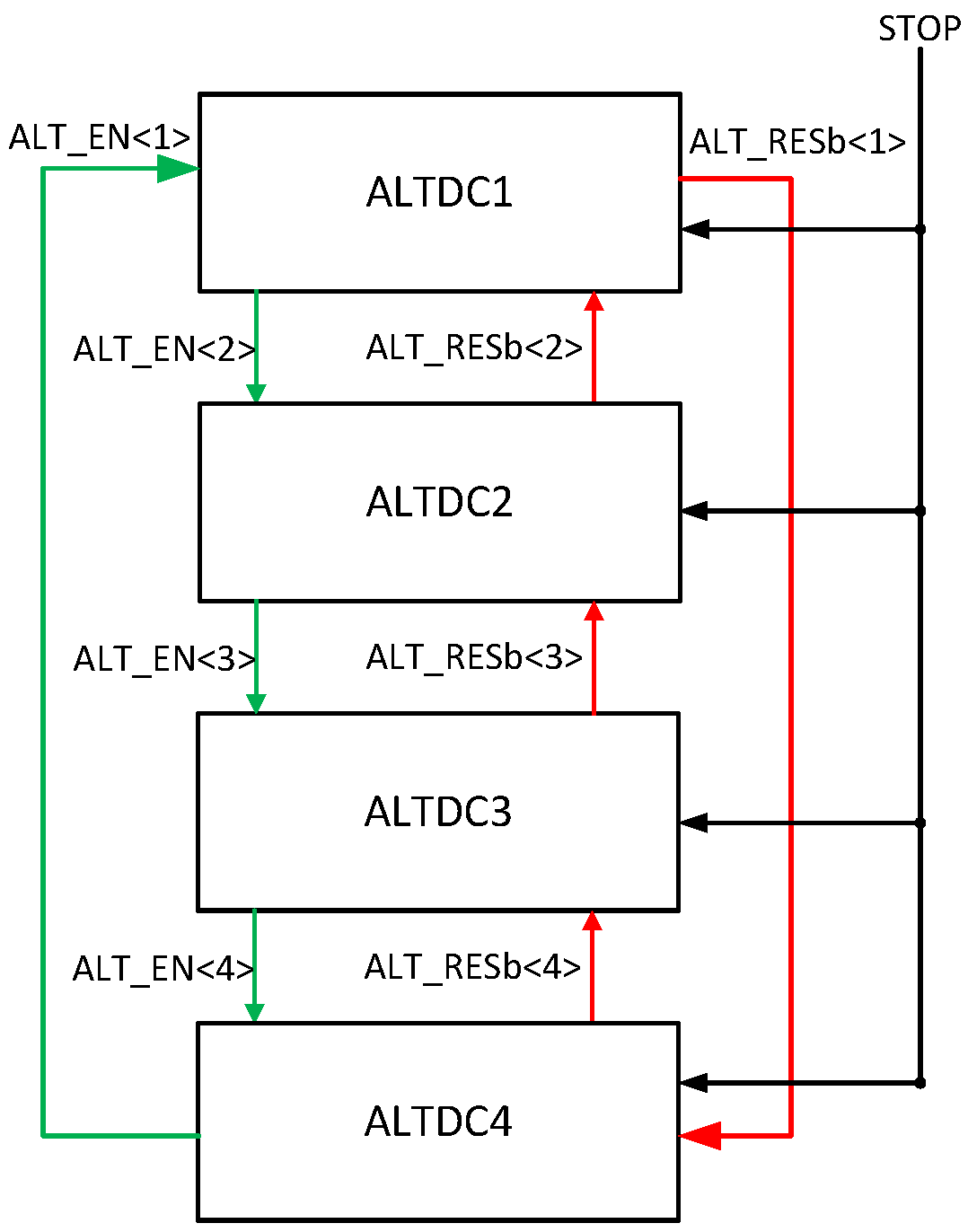

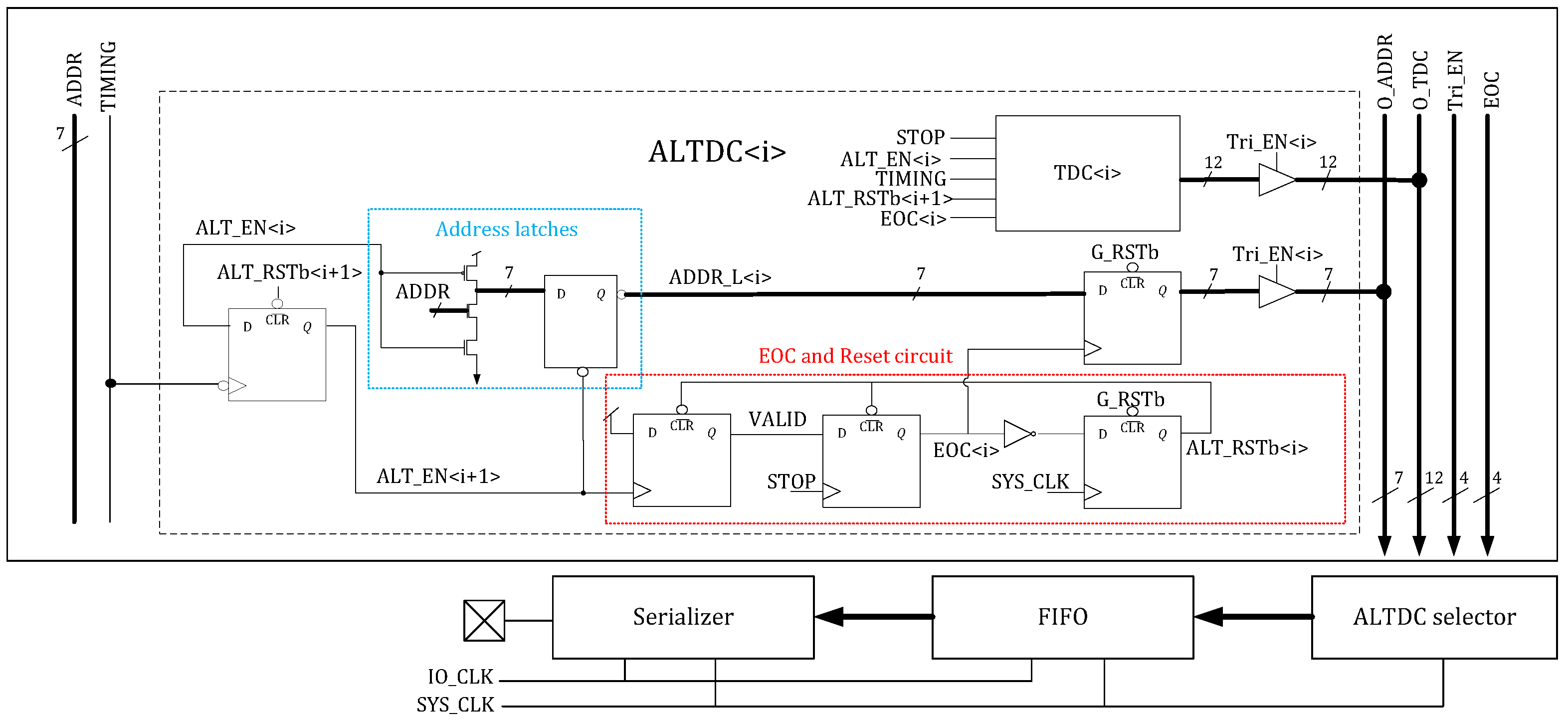

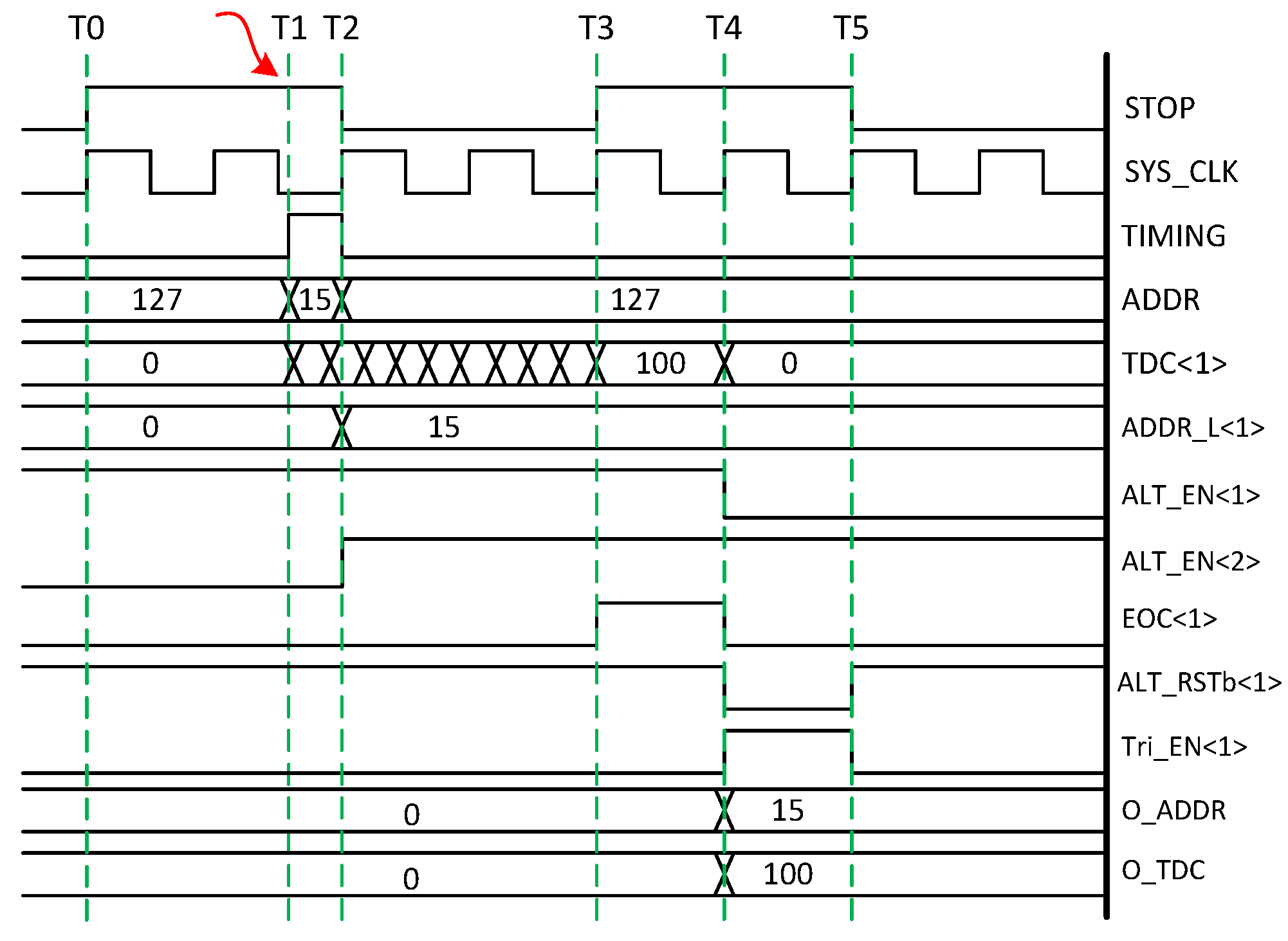

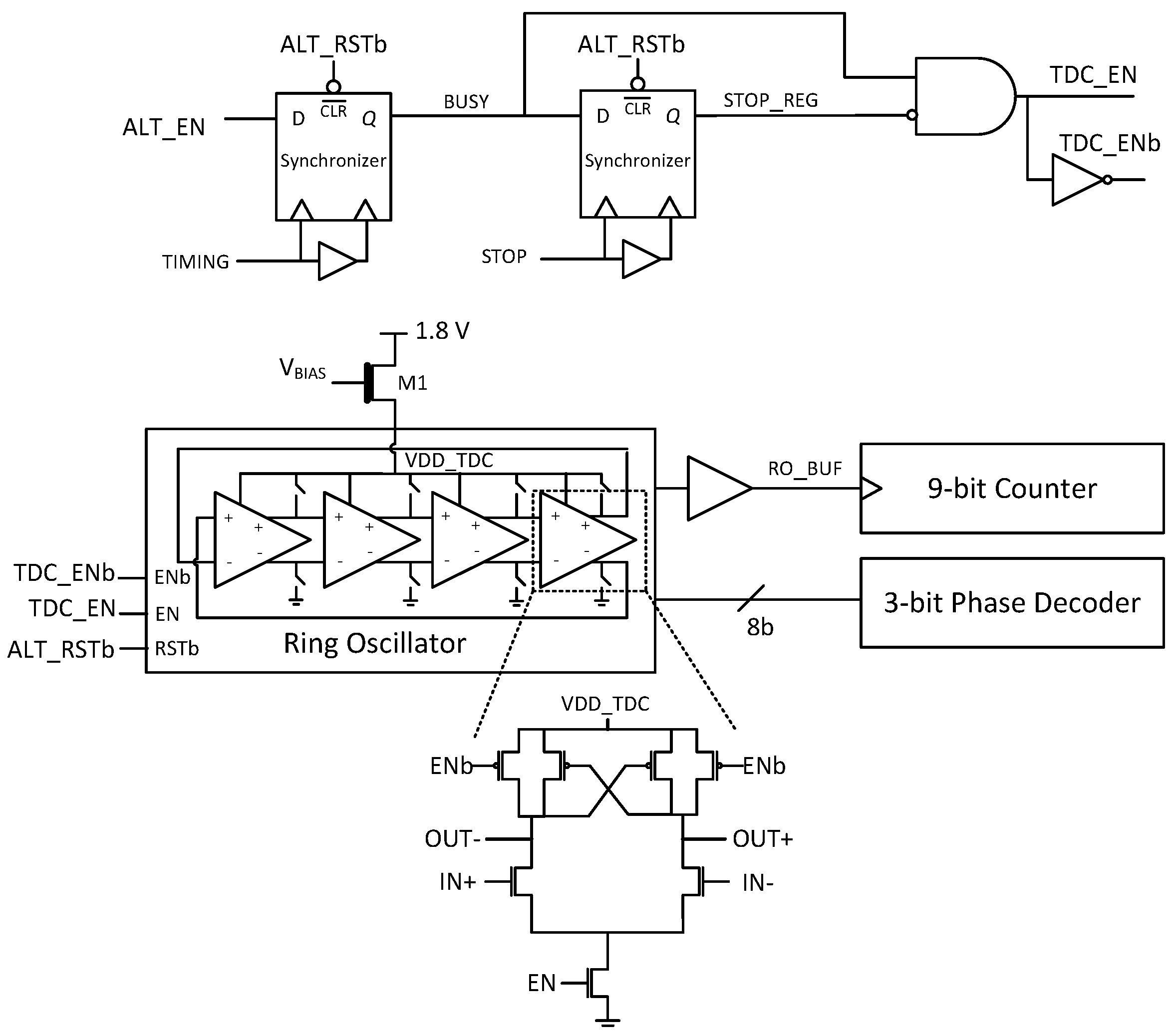

2.3. Dynamic Reallocation of Time-to-Digital Converters

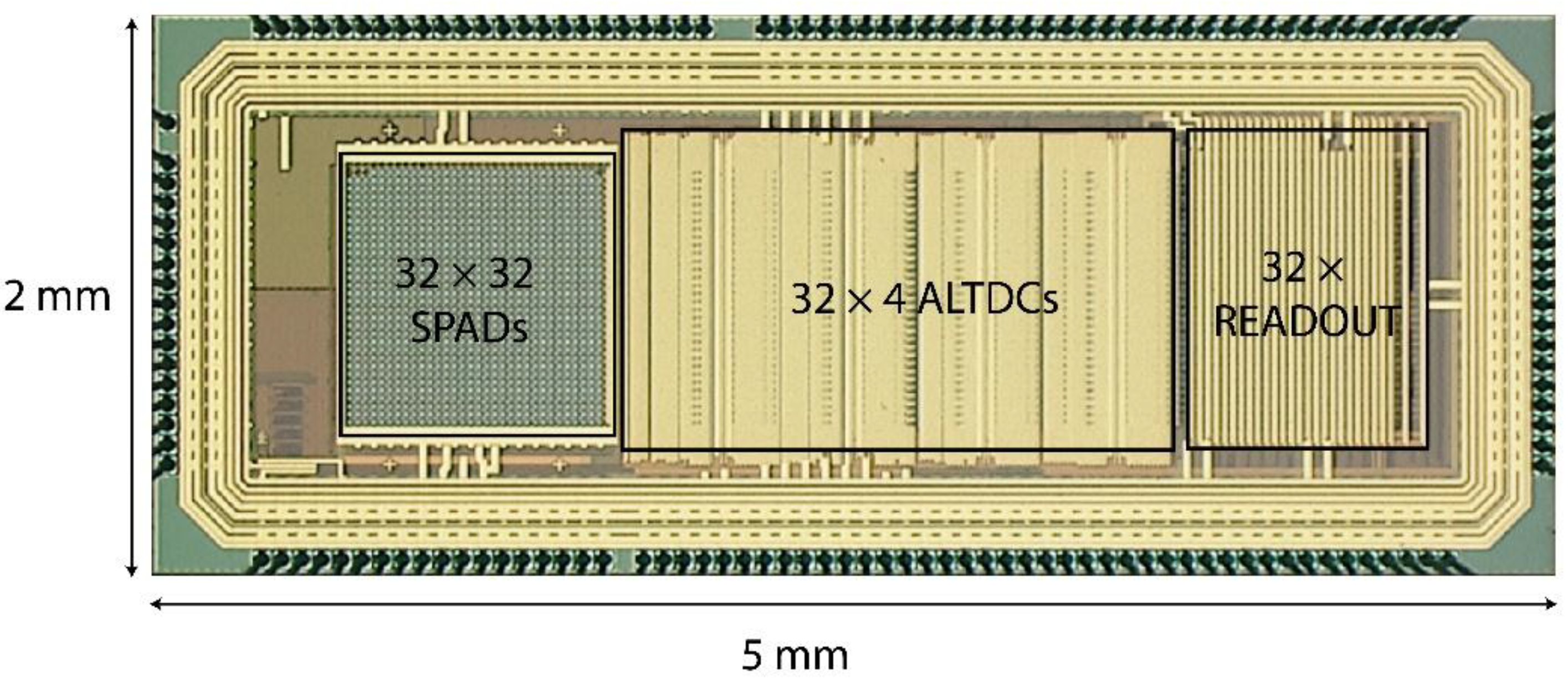

2.4. Chip Realization

3. Measurement Results

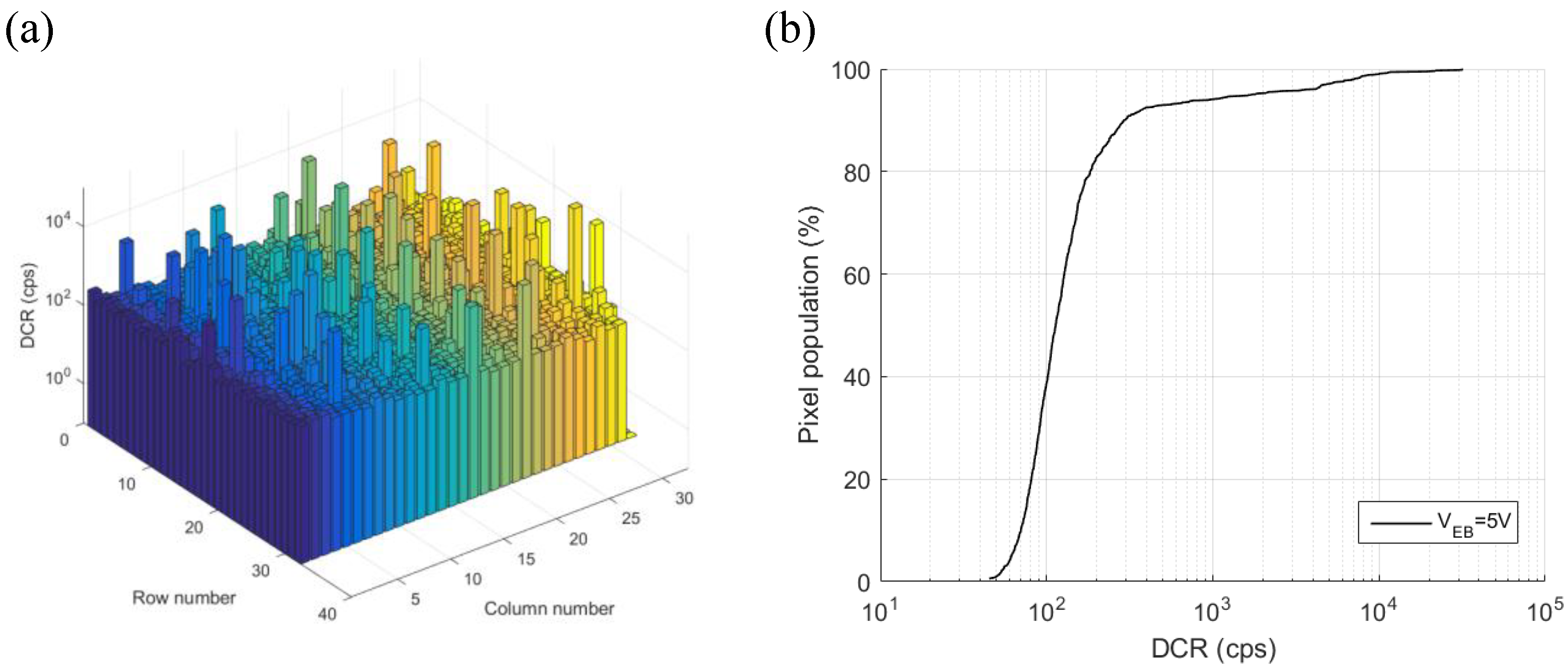

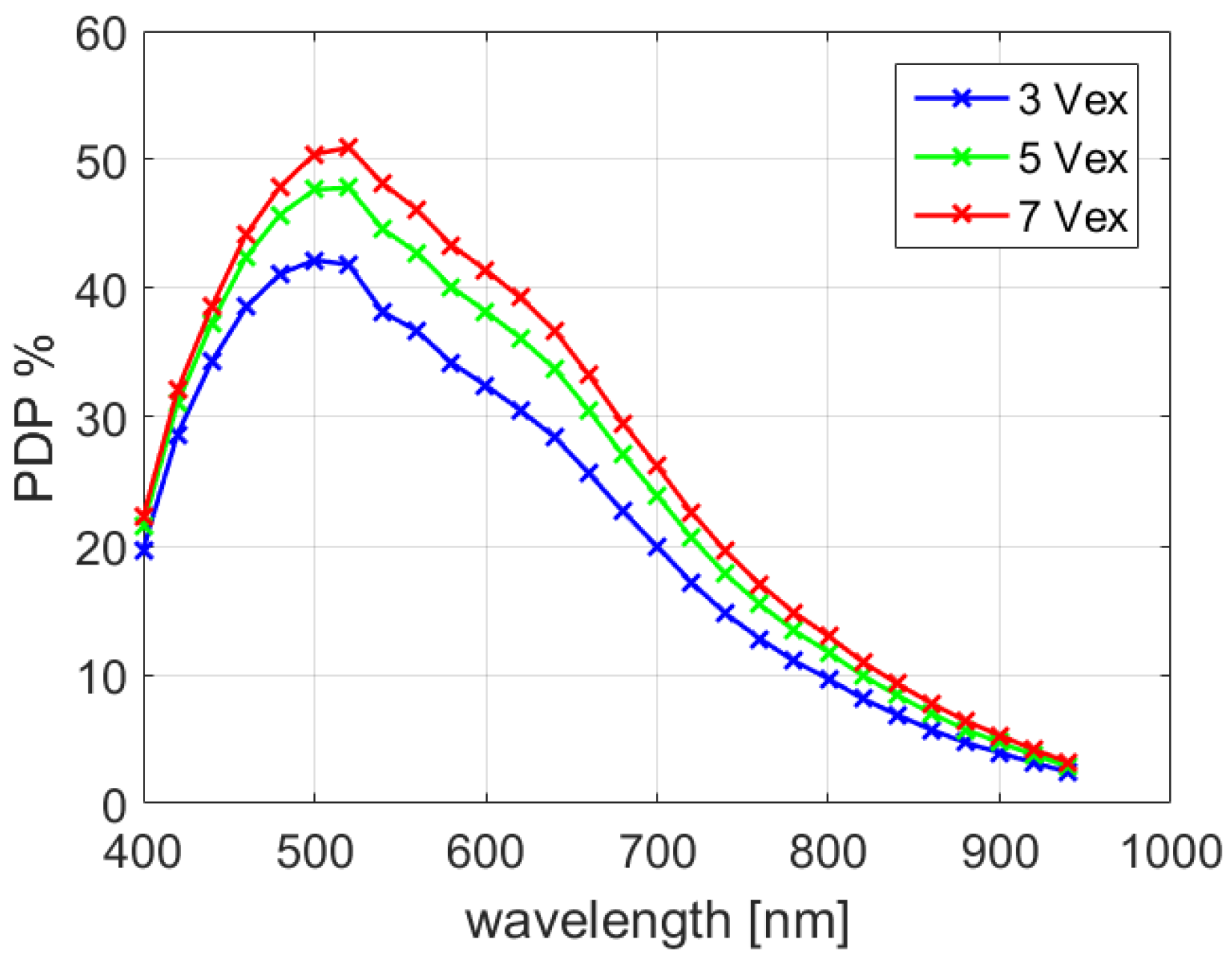

3.1. Chip Pixel Characterization

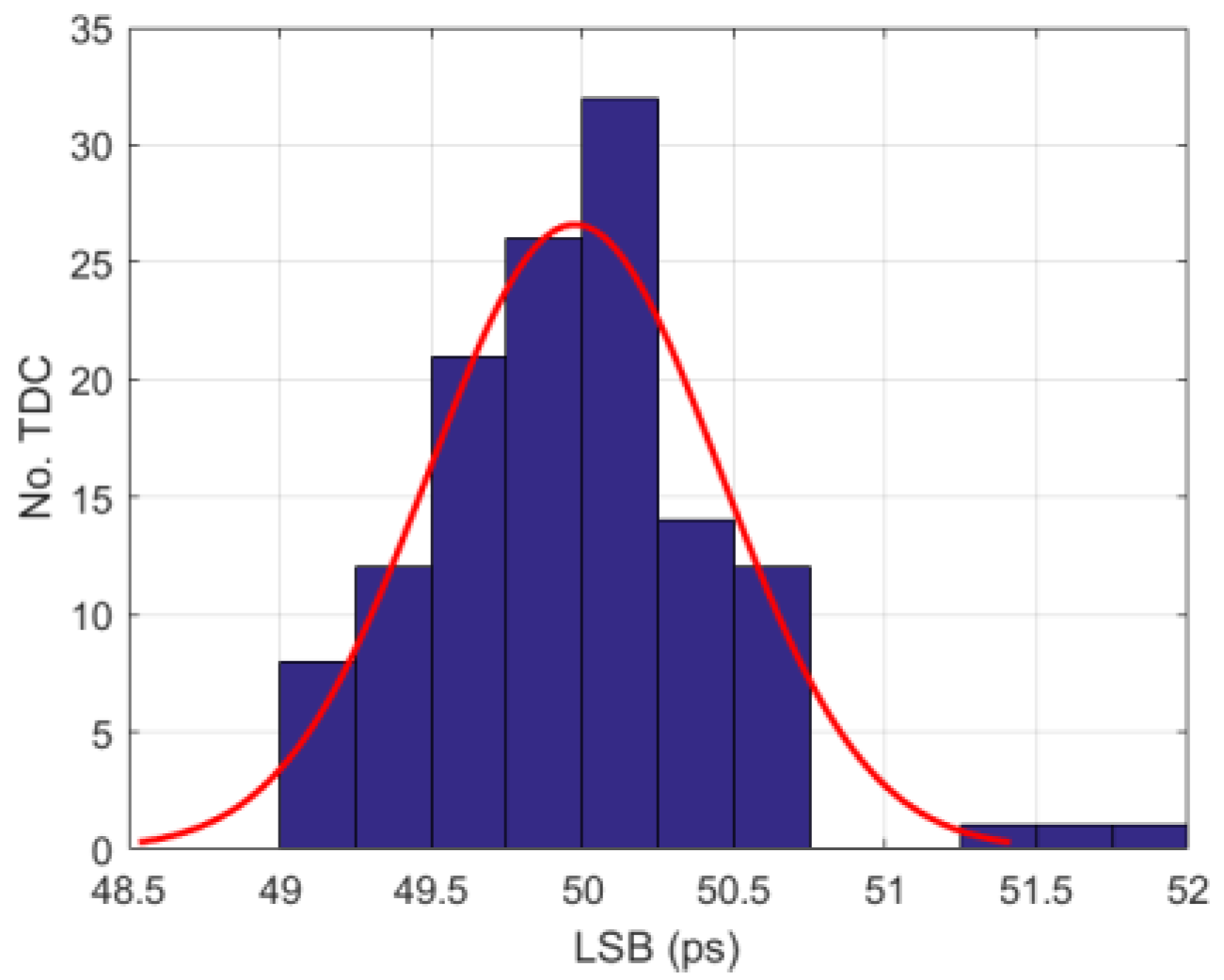

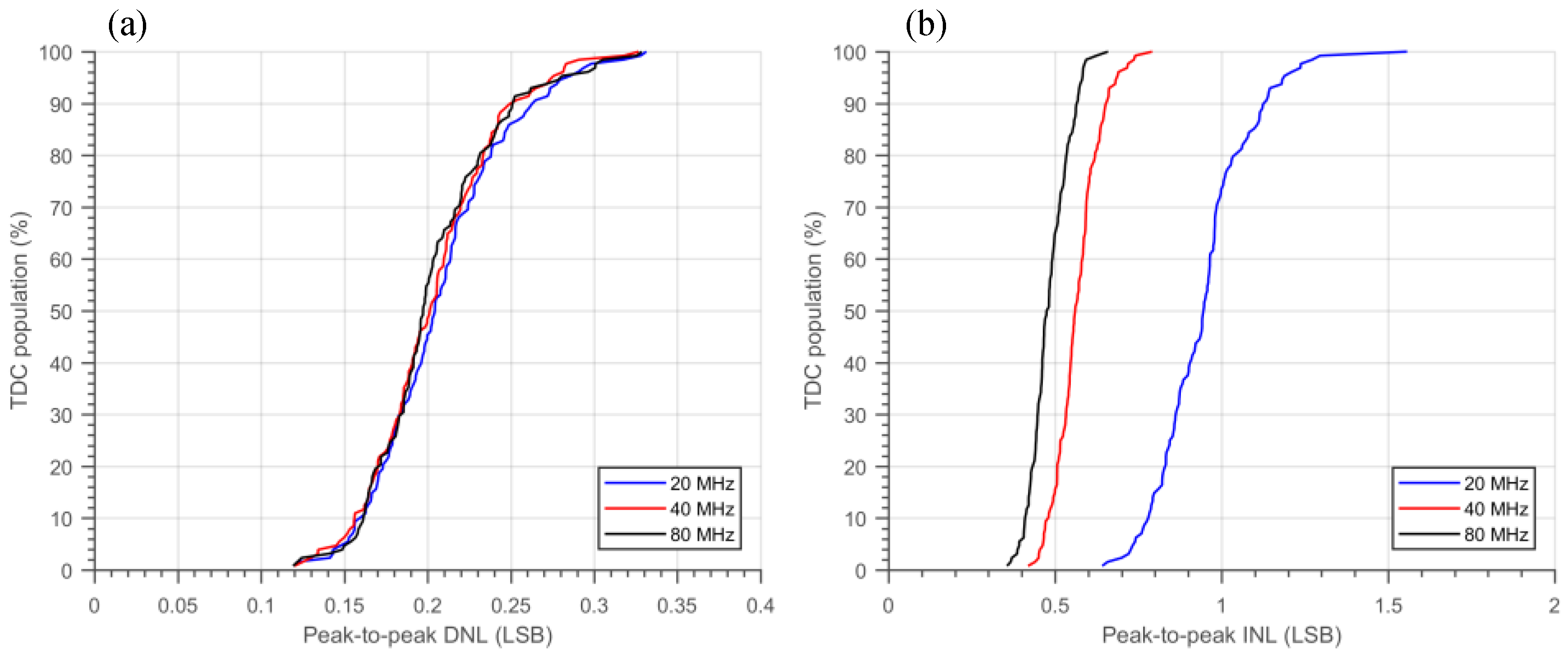

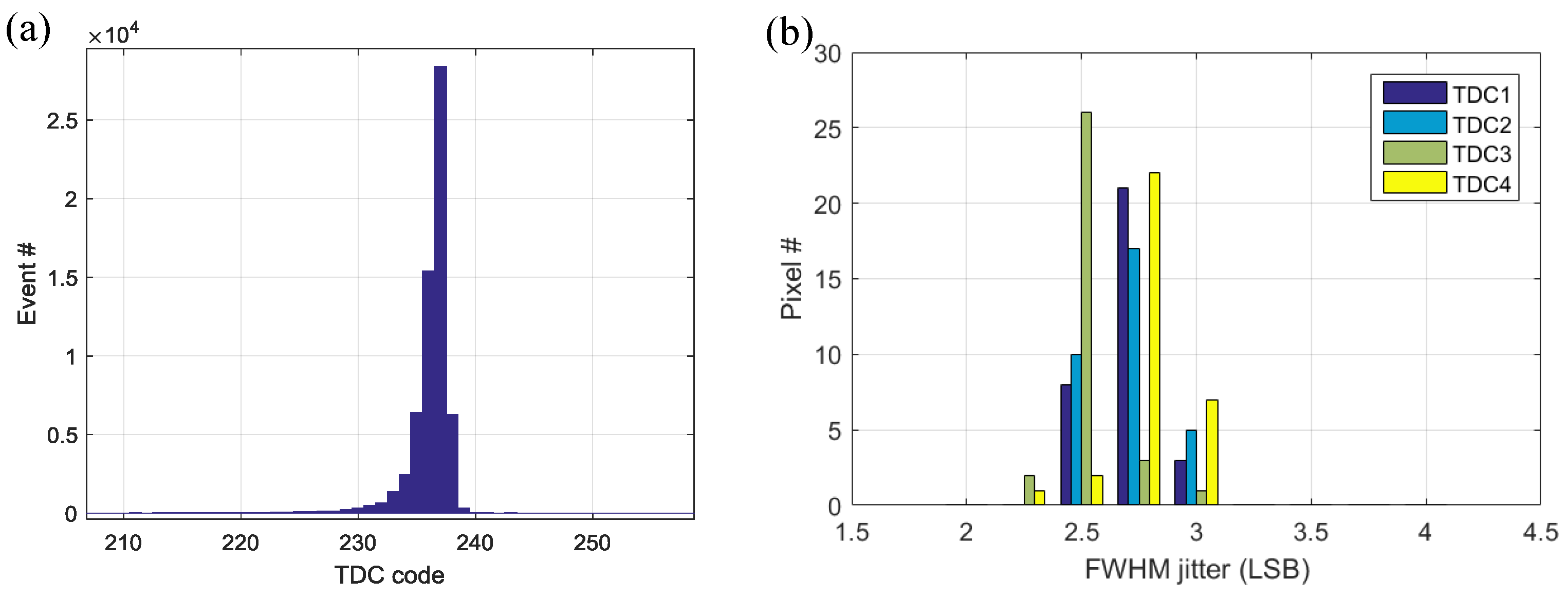

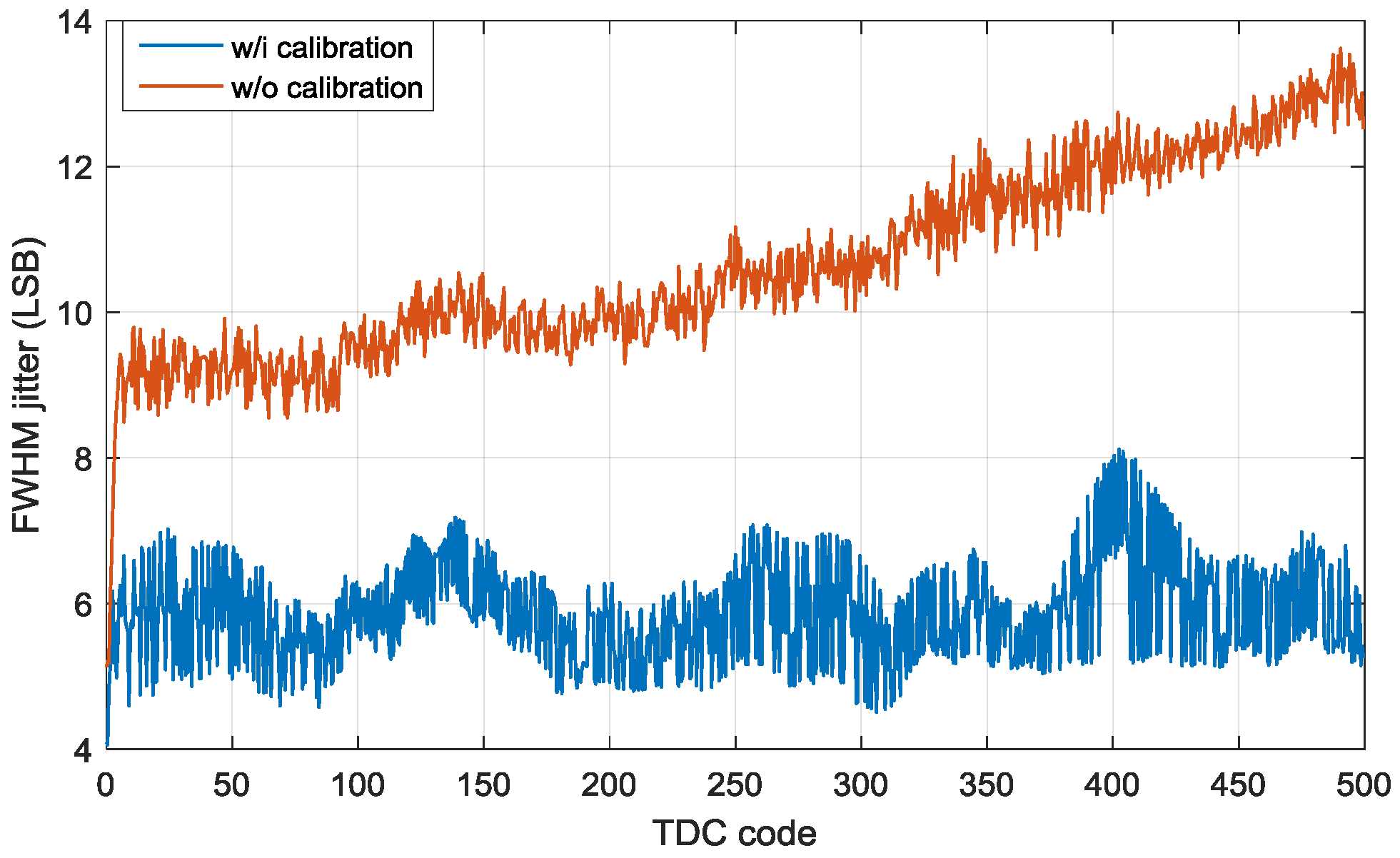

3.2. TDC Characterization

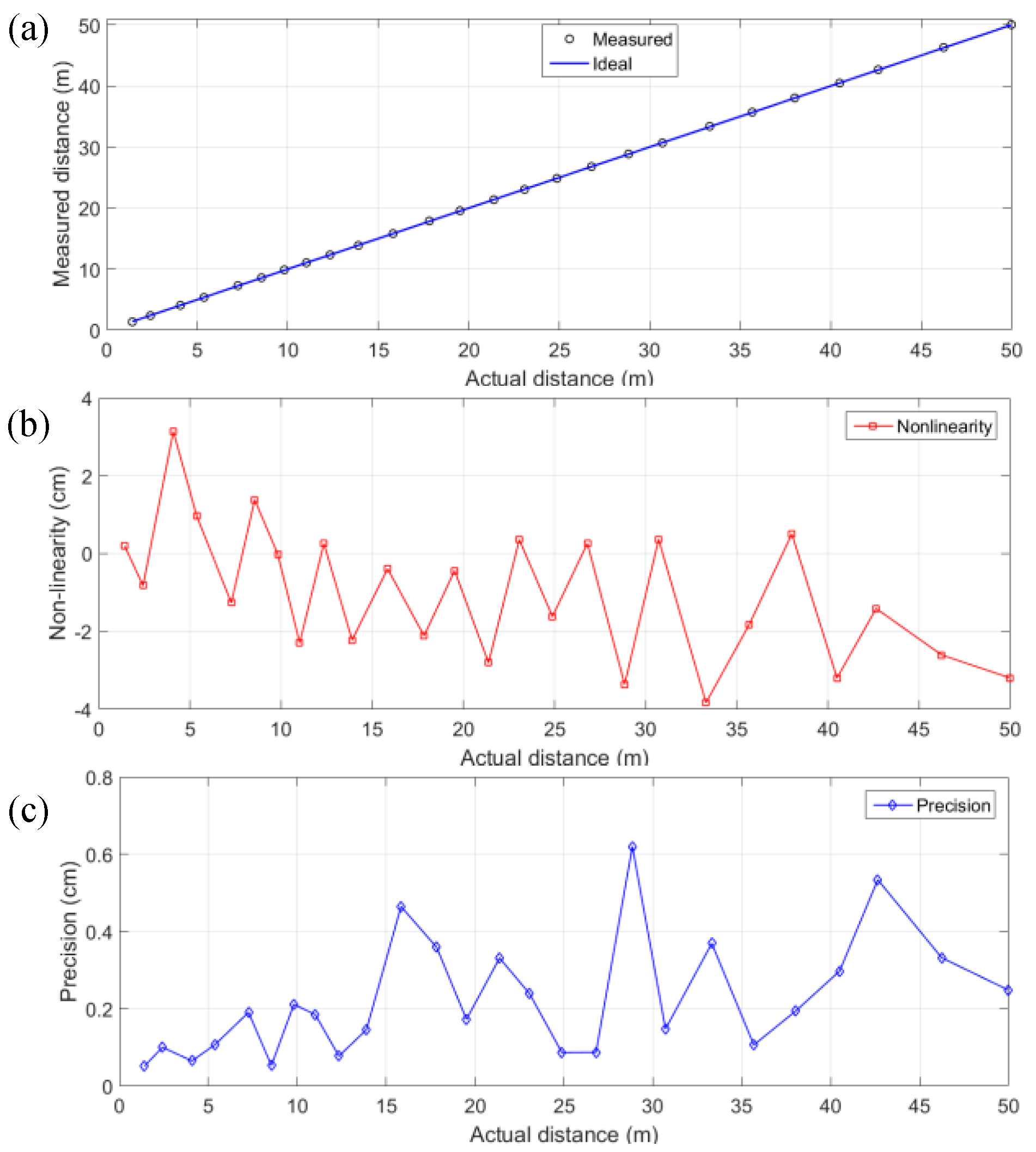

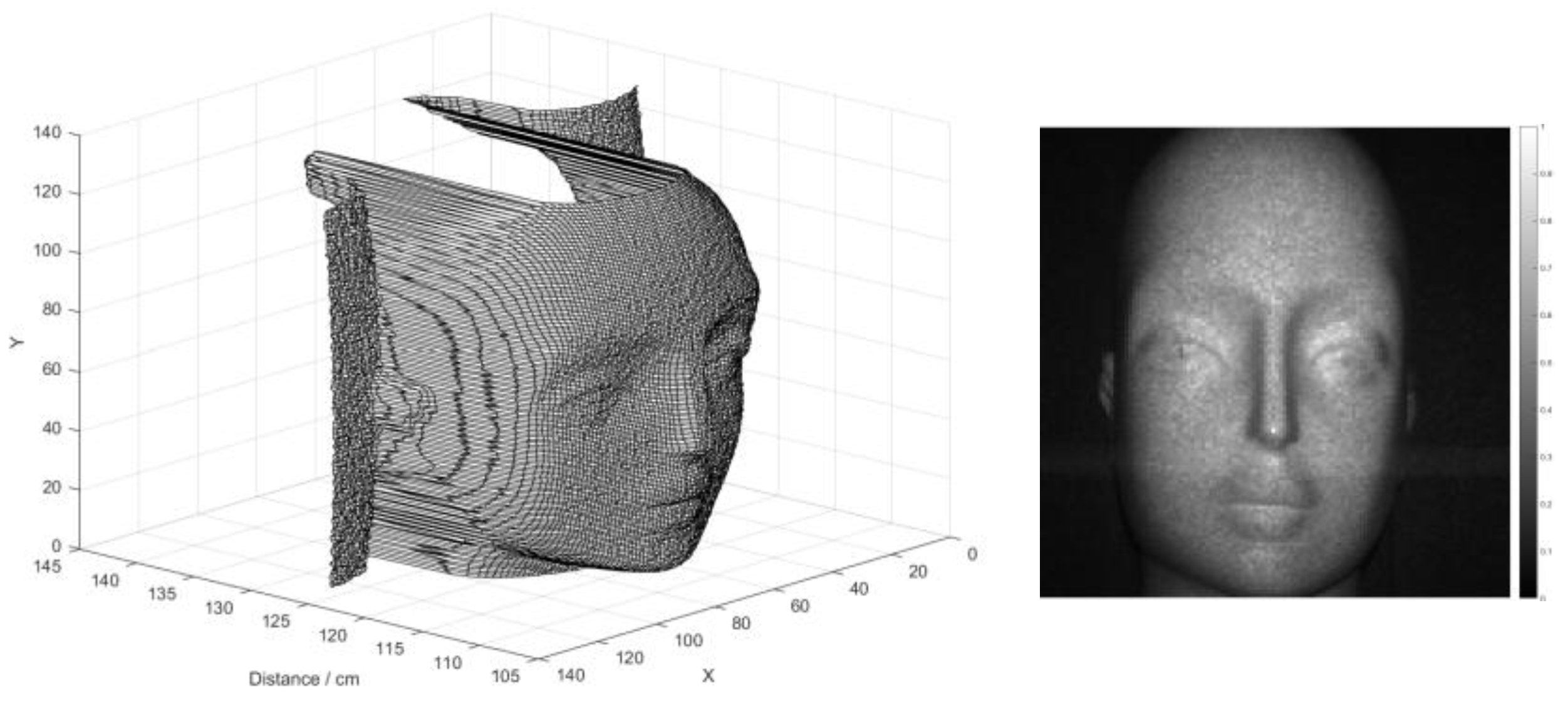

3.3. Flash 3D Imaging

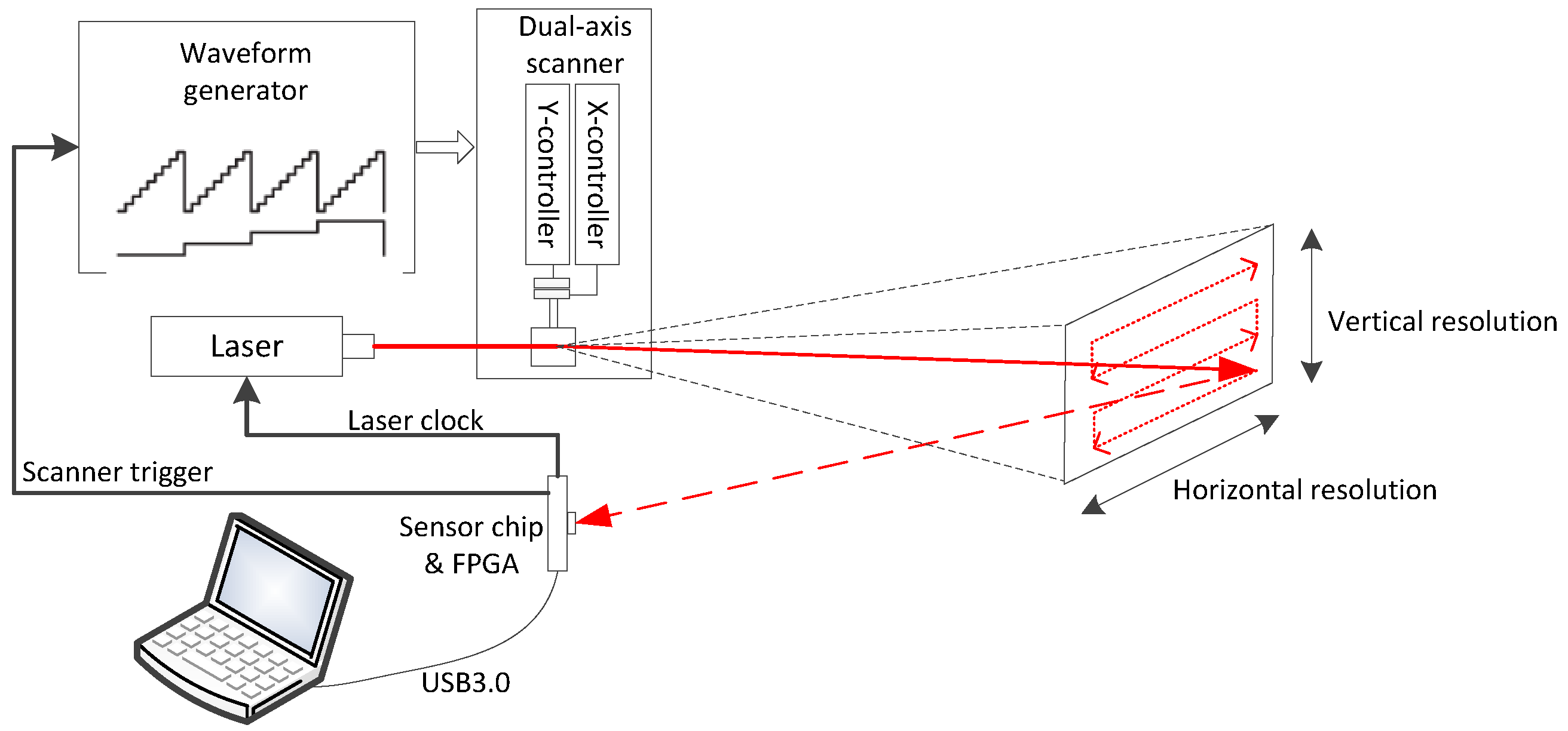

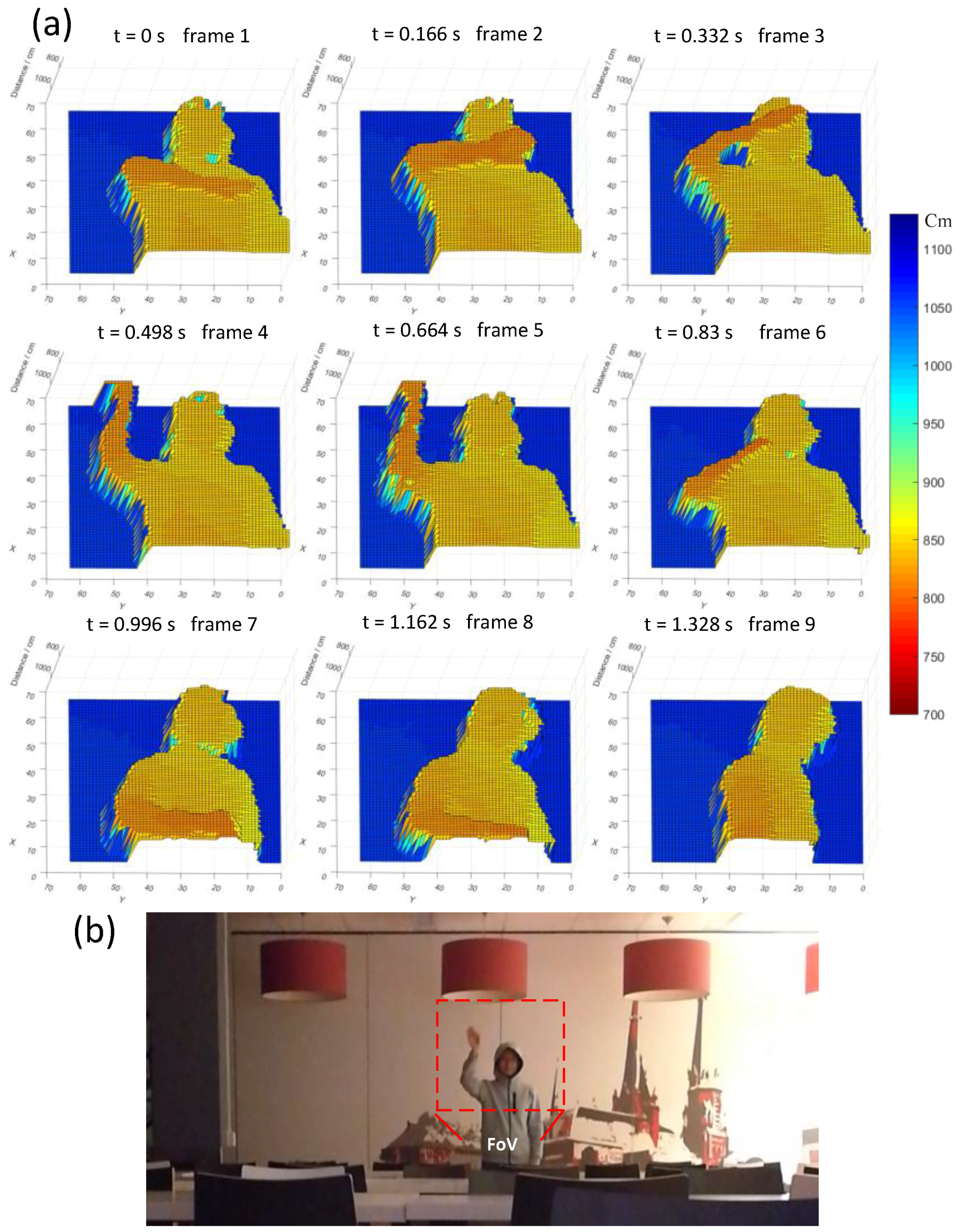

3.4. Scanning LiDAR Experiment

4. Proposed Background Light Suppression Architecture

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Oike, Y.; Ikeda, M.; Asada, K. A 375 × 365 high-speed 3-D range-finding image sensor using row-parallel search architecture and multisampling technique. IEEE J. Solid-State Circuits 2005, 40, 444–453. [Google Scholar] [CrossRef]

- Seo, M.W.; Shirakawa, Y.; Masuda, Y.; Kawata, Y.; Kagawa, K.; Yasutomi, K.; Kawahito, S. A programmable sub-nanosecond time-gated 4-tap lock-in pixel CMOS image sensor for real-time fluorescence lifetime imaging microscopy. In Proceedings of the ISSCC, San Francisco, CA, USA, 5–9 February 2017; pp. 70–71. [Google Scholar]

- Shcherbakova, O.; Pancheri, L.; Dalla Betta, G.F.; Massari, N.; Stoppa, D. 3D camera based on linear-mode gain-modulated avalanche photodiodes. In Proceedings of the ISSCC, San Francisco, CA, USA, 17–21 February 2013; pp. 490–491. [Google Scholar]

- Bronzi, D.; Villa, F.; Tisa, S.; Tosi, A.; Zappa, F.; Durini, D.; Weyers, S.; Brockherde, W. 100,000 Frames/s 64 × 32 Single-Photon Detector Array for 2-D Imaging and 3-D Ranging. IEEE J. Sel. Top. Quantum Electron. 2014, 20, 354–363. [Google Scholar] [CrossRef]

- Perenzoni, M.; Perenzoni, D.; Stoppa, D. A 64 × 64-Pixel Digital Silicon Photomultiplier Direct ToF Sensor with 100 MPhotons/s/pixel Background Rejection and Imaging/Altimeter Mode with 0.14% Precision up to 6 km for Spacecraft Navigation and Landing. IEEE J. Solid-State Circuits 2017, 52, 151–160. [Google Scholar] [CrossRef]

- Niclass, C.; Soga, M.; Matsubara, H.; Kato, S.; Kagami, M. A 100-m range 10-Frame/s 340×, 96-pixel time-of-flight depth sensor in 0.18-μm CMOS. IEEE J. Solid-State Circuits 2013, 48, 559–572. [Google Scholar] [CrossRef]

- Niclass, C.; Soga, M.; Matsubara, H.; Ogawa, M.; Kagami, M. A 0.18-m CMOS SoC for a 100-m-Range 10-Frame/s 200× 96-pixel Time-of-Flight Depth Sensor. IEEE J. Solid-State Circuits 2014, 49, 315–330. [Google Scholar] [CrossRef]

- Villa, F.; Lussana, R.; Bronzi, D.; Tisa, S.; Tosi, A.; Zappa, F.; Mora, A.D.; Contini, D.; Durini, D.; Weyers, S.; et al. CMOS imager with 1024 SPADs and TDCS for single-photon timing and 3-D time-of-flight. IEEE J. Sel. Top. Quantum Electron. 2014, 20, 364–373. [Google Scholar] [CrossRef]

- Ximenes, A.R.; Padmanabhan, P.; Lee, M.; Yamashita, Y.; Yaung, D.N.; Charbon, E. A 256 × 256 45/65 nm 3D-Stacked SPAD-Based Direct TOF Image Sensor for LiDAR Applications with Optical Polar Modulation for up to 18.6 dB Interference Suppression. In Proceedings of the ISSCC, San Francisco, CA, USA, 11–15 February 2018; pp. 27–29. [Google Scholar]

- Lindner, S.; Zhang, C.; Antolovic, I.M.; Pavia, J.M.; Wolf, M.; Charbon, E. Column-Parallel Dynamic TDC Reallocation in SPAD Sensor Module Fabricated in 180 nm CMOS for Near Infrared Optical Tomography. In Proceedings of the 2017 International Image Sensor Workshop, Hiroshima, Japan, 30 May–2 June 2017; pp. 86–89. [Google Scholar]

- Veerappan, C.; Richardson, J.; Walker, R.; Li, D.; Fishburn, M.W.; Maruyama, Y.; Stoppa, D.; Borghetti, F.; Gersbach, M.; Henderson, R.K.; et al. A 160 × 128 Single-Photon Image Sensor with On-Pixel 55ps 10b Time-to-Digital Converter. In Proceedings of the ISSCC, San Francisco, CA, USA, 20–24 February 2011; pp. 312–314. [Google Scholar]

- Field, R.M.; Realov, S.; Shepard, K.L. A 100 fps, time-correlated single-photon-counting-based fluorescence-lifetime imager in 130 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 867–880. [Google Scholar] [CrossRef]

- Acconcia, G.; Cominelli, A.; Rech, I.; Ghioni, M. High-efficiency integrated readout circuit for single photon avalanche diode arrays in fluorescence lifetime imaging. Rev. Sci. Instrum. 2016, 87, 113110. [Google Scholar] [CrossRef] [PubMed]

- Lindner, S.; Zhang, C.; Antolovic, I.M.; Wolf, M.; Charbon, E. A 252 × 144 SPAD pixel FLASH LiDAR with 1728 Dual-clock 48.8 ps TDCs, Integrated Histogramming and 14.9-to-1 Compression in 180 nm CMOS Technology. In Proceedings of the IEEE VLSI Symposium, Honolulu, HI, USA, 18–22 June 2018. [Google Scholar]

- Pavia, J.M.; Scandini, M.; Lindner, S.; Wolf, M.; Charbon, E. A 1 × 400 Backside-Illuminated SPAD Sensor with 49.7 ps Resolution, 30 pJ/Sample TDCs Fabricated in 3D CMOS Technology for Near-Infrared Optical Tomography. IEEE J. Solid-State Circuits 2015, 50, 2406–2418. [Google Scholar] [CrossRef]

- Niclass, C.; Sergio, M.; Charbon, E. A CMOS 64 × 48 Single Photon Avalanche Diode Array with Event-Driven Readout. In Proceedings of the ESSCIRC, Montreux, Switzerland, 19–21 September 2006; pp. 556–559. [Google Scholar]

- Veerappan, C. Single-Photon Avalanche Diodes for Cancer Diagnosis. Ph.D. Thesis, Delft University of Technology, Delft, The Netherlands, March 2016. [Google Scholar]

- Lindner, S.; Pellegrini, S.; Henrion, Y.; Rae, B.; Wolf, M.; Charbon, E. A High-PDE, Backside-Illuminated SPAD in 65/40-nm 3D IC CMOS Pixel with Cascoded Passive Quenching and Active Recharge. IEEE Electron Device Lett. 2017, 38, 1547–1550. [Google Scholar] [CrossRef]

- Xu, H.; Pancheri, L.G.; Betta, D.; Stoppa, D. Design and characterization of a p+/n-well SPAD array in 150 nm CMOS process. Opt. Express 2017, 25, 12765–12778. [Google Scholar] [CrossRef] [PubMed]

- Gyongy, I.; Calder, N.; Davies, A.; Dutton, N.A.W.; Dalgarno, P.; Duncan, R.; Rickman, C.; Henderson, R.K. 256 × 256, 100 kfps, 61% Fill-factor time-resolved SPAD image sensor for time-resolved microscopy applications. IEEE Trans. Electron Devices 2018, 65, 547–554. [Google Scholar] [CrossRef]

- Lee, M.; Ximenes, A.R.; Member, S.; Padmanabhan, P.; Member, S.; Wang, T.; Huang, K.; Yamashita, Y.; Yaung, D.; Charbon, E. High-Performance Back-Illuminated Three-Dimensional Stacked Single-Photon Avalanche Diode Implemented in 45-nm CMOS Technology. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 1–9. [Google Scholar] [CrossRef]

- Bronzi, D.; Villa, F.; Bellisai, S.; Markovic, B.; Tisa, S.; Tosi, A.; Zappa, F.; Weyers, S.; Durini, D.; Brockherde, W.; et al. Low-noise and large-area CMOS SPADs with Timing Response free from Slow Tails. In Proceedings of the IEEE ESSDERC, Bordeaux, France, 17–21 September 2012; pp. 230–233. [Google Scholar]

- Sanzaro, M.; Gattari, P.; Villa, F.; Tosi, A.; Croce, G.; Zappa, F. Single-Photon Avalanche Diodes in a 0.16 μm BCD Technology with Sharp Timing Response and Red-Enhanced Sensitivity. IEEE. J. Sel. Top. Quantum Electron. 2018, 24, 1–9. [Google Scholar] [CrossRef]

- Cova, S.; Ghioni, M.; Lacaita, A.; Samori, C.; Zappa, F. Avalanche photodiodes and quenching circuits for single-photon detection. Appl. Opt. 1996, 35, 1956–1976. [Google Scholar] [CrossRef] [PubMed]

| SPAD | ADDR | SPAD | ADDR | SPAD | ADDR | SPAD | ADDR |

|---|---|---|---|---|---|---|---|

| 0 | 1110000 | 8 | 1000011 | 16 | 0011001 | 24 | 0001110 |

| 1 | 1100100 | 9 | 1000101 | 17 | 0011010 | 25 | 0101100 |

| 2 | 1100001 | 10 | 1000110 | 18 | 0010011 | 26 | 0101001 |

| 3 | 1100010 | 11 | 1010100 | 19 | 0010101 | 27 | 0101010 |

| 4 | 1101000 | 12 | 1010001 | 20 | 0010110 | 28 | 0100011 |

| 5 | 1001100 | 12 | 1010010 | 21 | 0000111 | 29 | 0100101 |

| 6 | 1001001 | 14 | 1011000 | 22 | 0001011 | 30 | 0100110 |

| 7 | 1001010 | 15 | 0011100 | 23 | 0001101 | 31 | 0110100 |

| Parameter | Value | Unit |

|---|---|---|

| Chip characteristics | ||

| Array resolution | 32 × 32 | |

| Technology | 180 nm CMOS | |

| Chip size | 5 × 2 | mm2 |

| Pixel pitch | 28.5 | μm |

| Pixel fill-factor | 28 | % |

| SPAD break down voltage | 22 | V |

| SPAD median DCR | 113 (Vex = 5 V, 20 °C) | cps |

| SPAD jitter | 106 (Vex = 5 V) | ps |

| SPAD PDP | 47.8 (Vex = 5 V @520 nm) | % |

| TDC LSB | 50 | ps |

| TDC resolution | 12 | bit |

| No. TDC | 128 | |

| TDC area | 4200 | μm2 |

| Readout bandwidth | 5.12 | Gbps |

| Maximum photon throughput | 222 (PT mode) | Mcps |

| 465 (PC mode) | Mcps | |

| Distance measurement | ||

| Measurement range | 50 | m |

| Non-linearity (Accuracy) | 6.9 (0.14%) | cm |

| Precision (σ) (Repeatability) | 0.62 (0.01%) | cm |

| LiDAR experiment | ||

| Illumination wavelength | 637 | nm |

| Illumination power | 2 (average) | mW |

| 500 (peak) | mW | |

| Frame rate | 6 | fps |

| Image resolution | 64 × 64 | |

| Field of view (H × V) | 5 × 5 | degree |

| Target reflectivity | 40 | % |

| Distance range (LiDAR) | 10 | m |

| Background light | 50 | lux |

| Chip power consumption | 0.31 (@ 35.5 Mcps photon throughput) | W |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, C.; Lindner, S.; Antolovic, I.M.; Wolf, M.; Charbon, E. A CMOS SPAD Imager with Collision Detection and 128 Dynamically Reallocating TDCs for Single-Photon Counting and 3D Time-of-Flight Imaging. Sensors 2018, 18, 4016. https://doi.org/10.3390/s18114016

Zhang C, Lindner S, Antolovic IM, Wolf M, Charbon E. A CMOS SPAD Imager with Collision Detection and 128 Dynamically Reallocating TDCs for Single-Photon Counting and 3D Time-of-Flight Imaging. Sensors. 2018; 18(11):4016. https://doi.org/10.3390/s18114016

Chicago/Turabian StyleZhang, Chao, Scott Lindner, Ivan Michel Antolovic, Martin Wolf, and Edoardo Charbon. 2018. "A CMOS SPAD Imager with Collision Detection and 128 Dynamically Reallocating TDCs for Single-Photon Counting and 3D Time-of-Flight Imaging" Sensors 18, no. 11: 4016. https://doi.org/10.3390/s18114016

APA StyleZhang, C., Lindner, S., Antolovic, I. M., Wolf, M., & Charbon, E. (2018). A CMOS SPAD Imager with Collision Detection and 128 Dynamically Reallocating TDCs for Single-Photon Counting and 3D Time-of-Flight Imaging. Sensors, 18(11), 4016. https://doi.org/10.3390/s18114016