3D Defect Localization on Exothermic Faults within Multi-Layered Structures Using Lock-In Thermography: An Experimental and Numerical Approach

Abstract

:1. Introduction

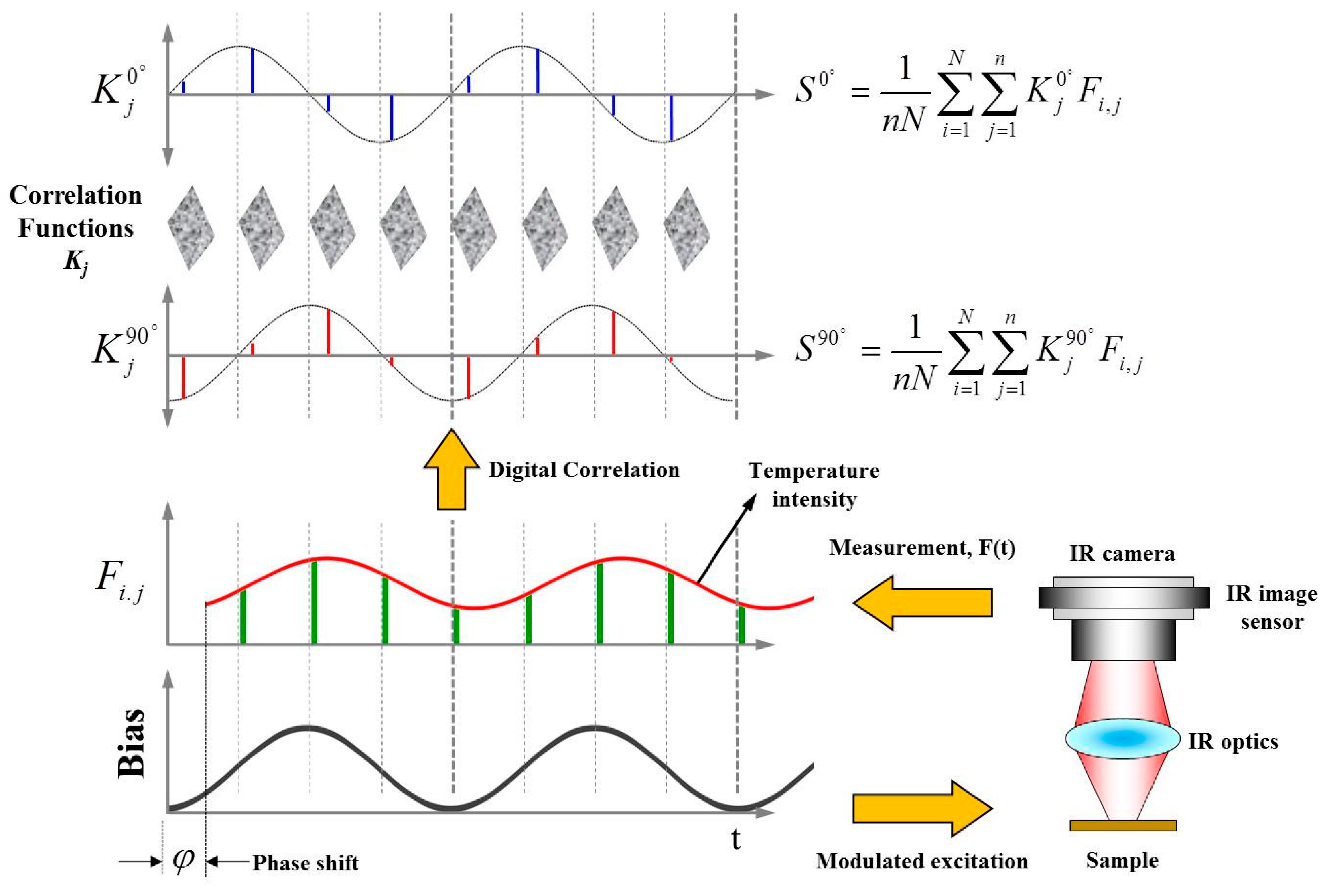

2. Lock-In Principle

3. Experiment

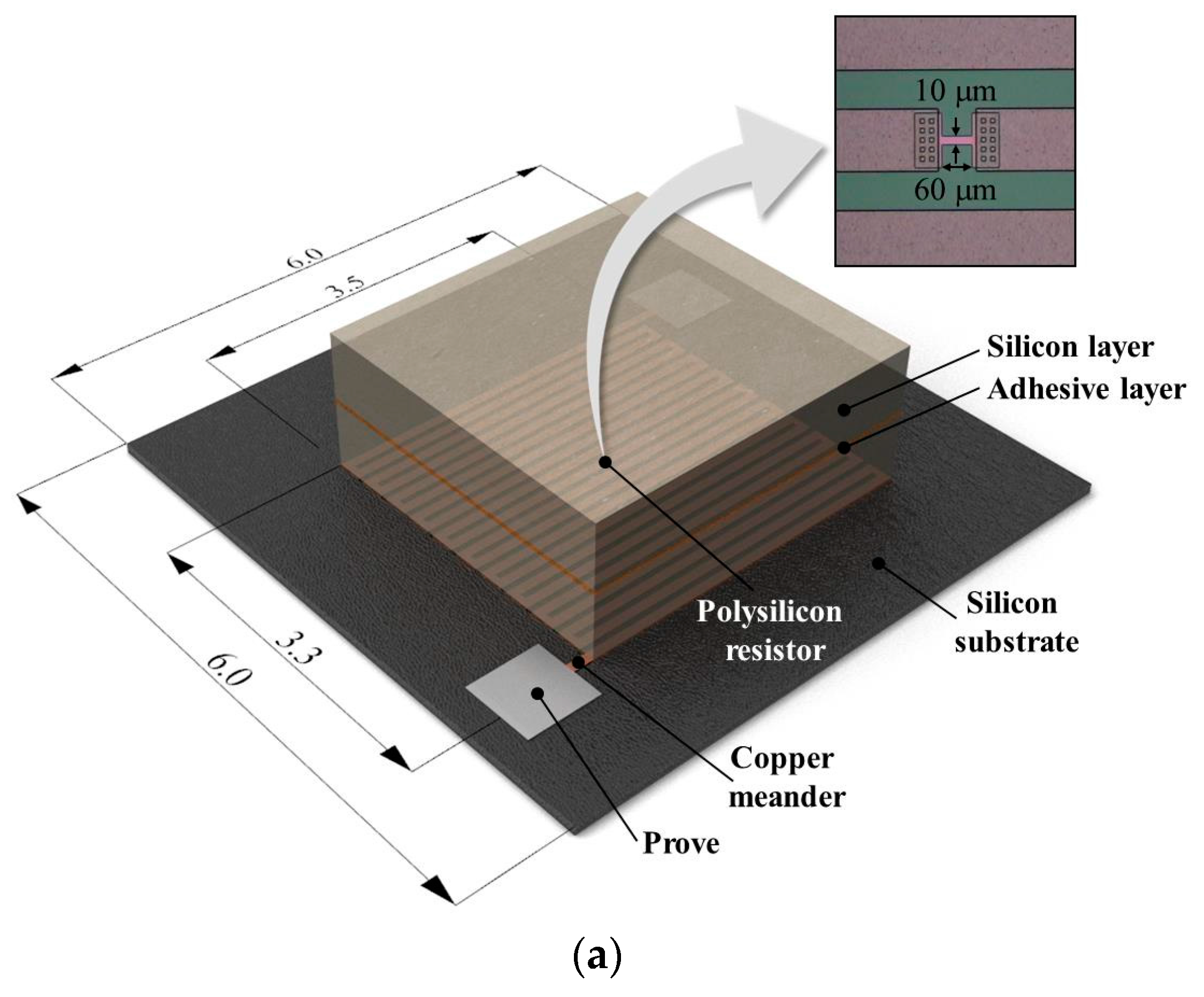

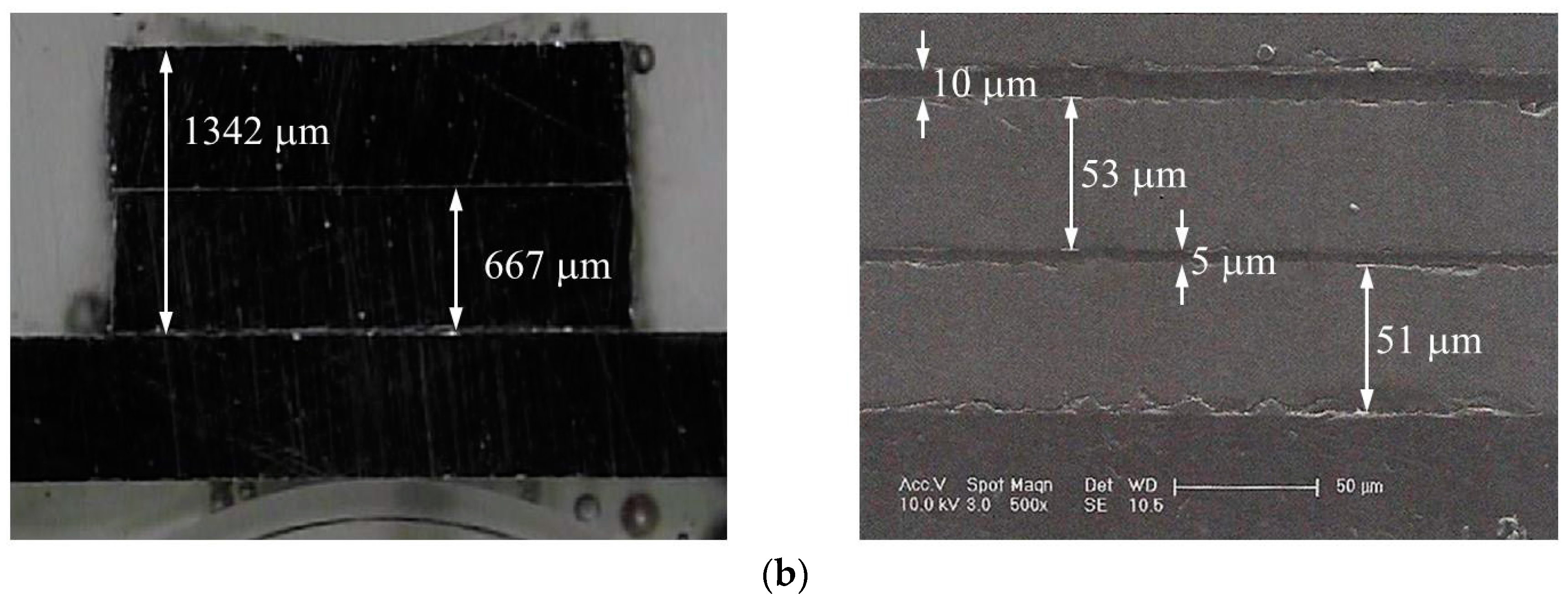

3.1. Silicon Wafer Stacked Heat Source Chip

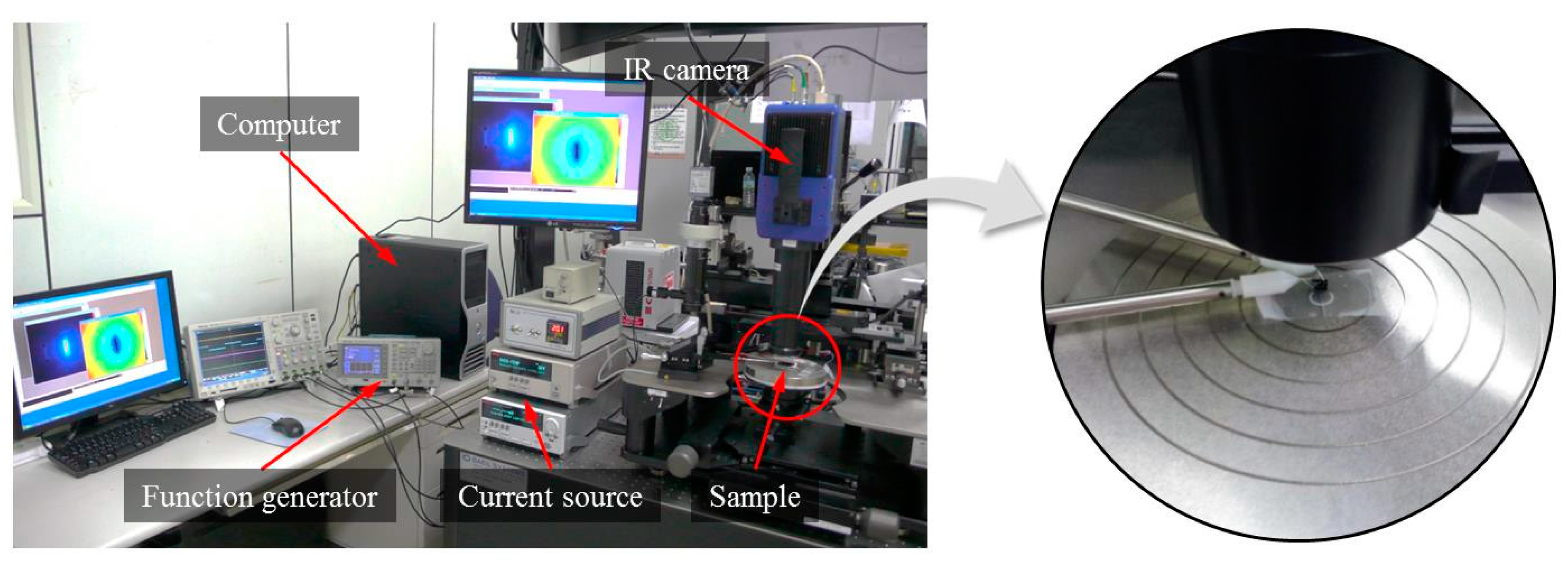

3.2. Lock-In Thermography

3.3. Depth Estimation

4. Numerical Simulations

4.1. Finite Element Modeling

4.2. Boundary Conditions and Finite Element Analysis

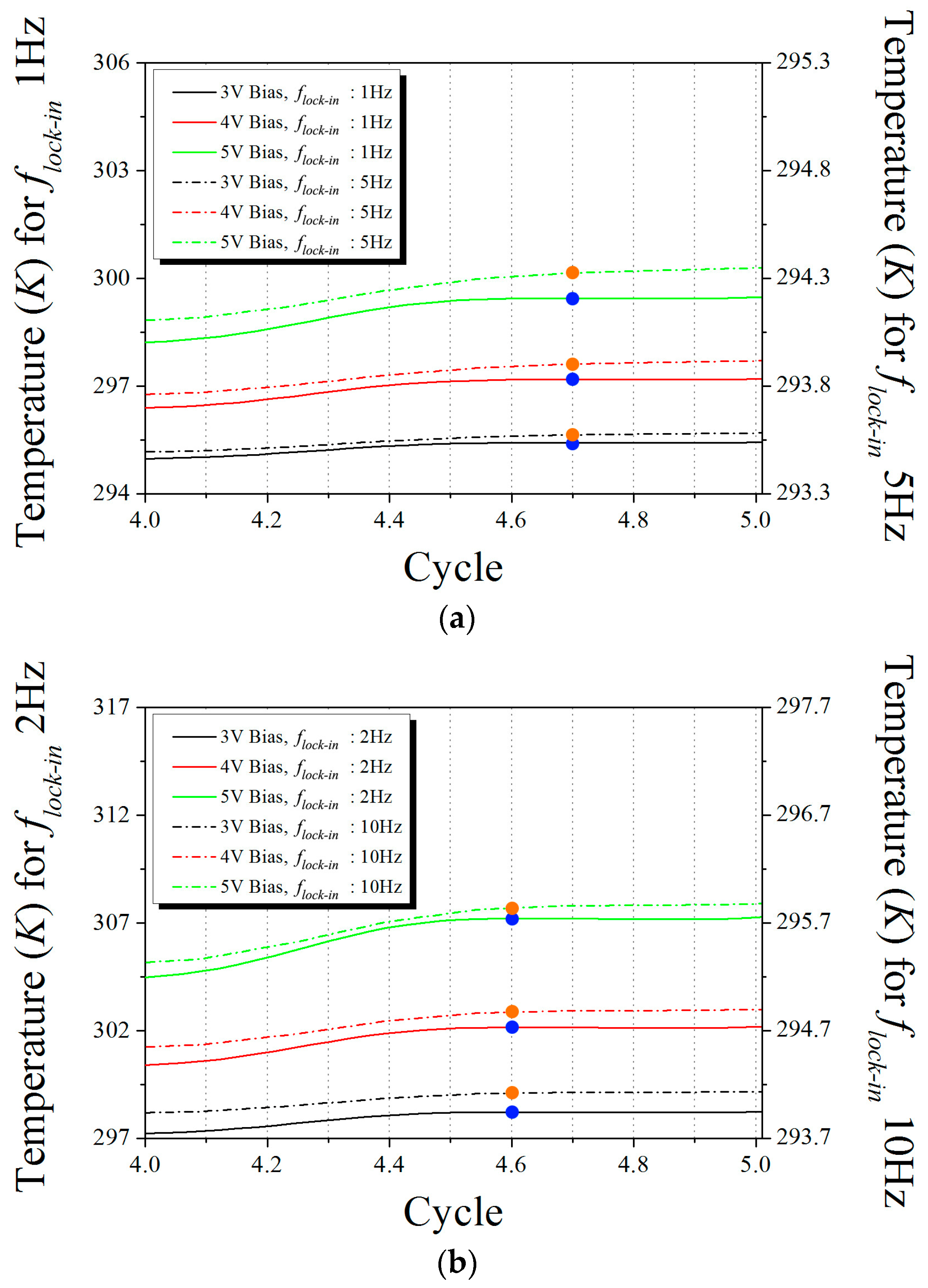

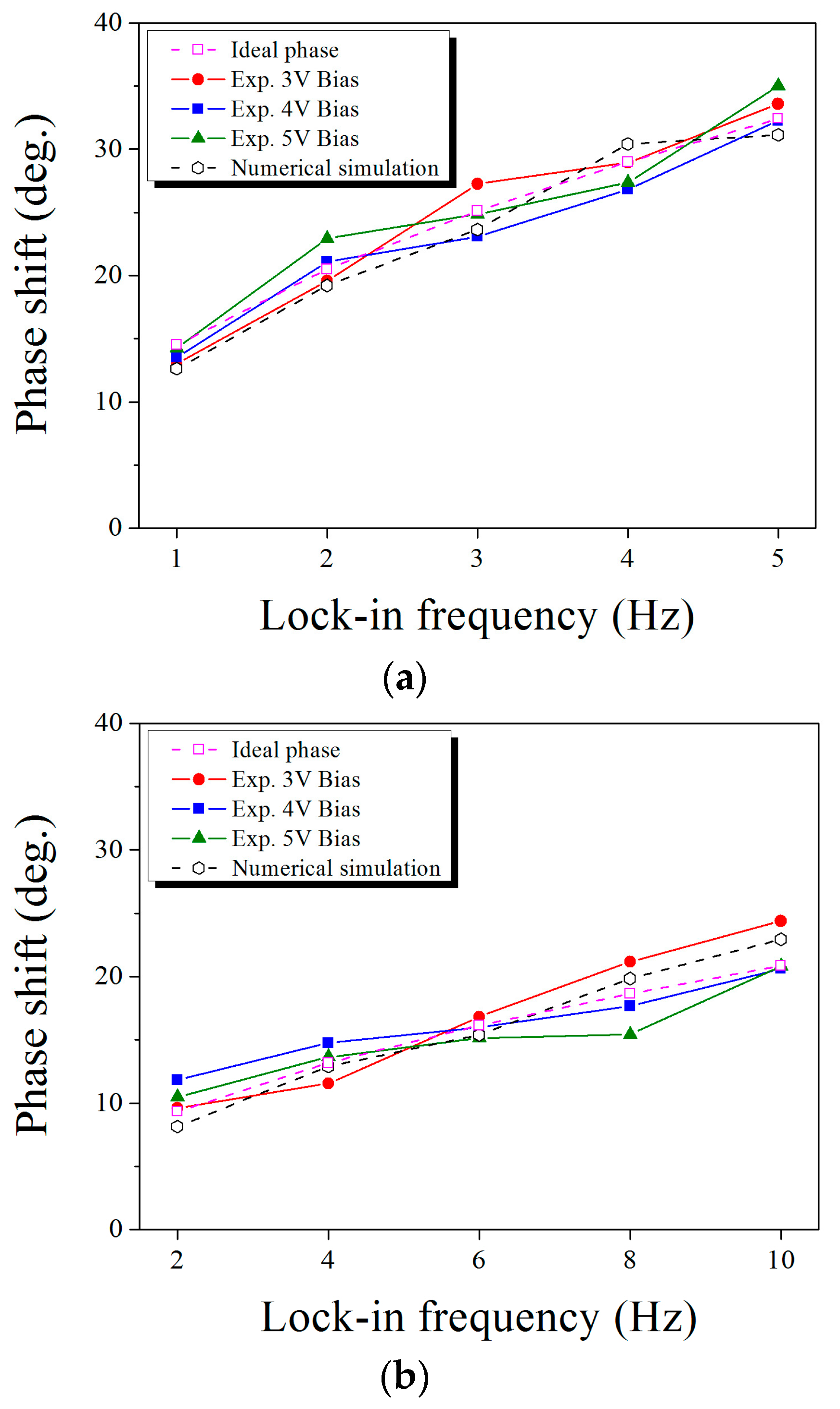

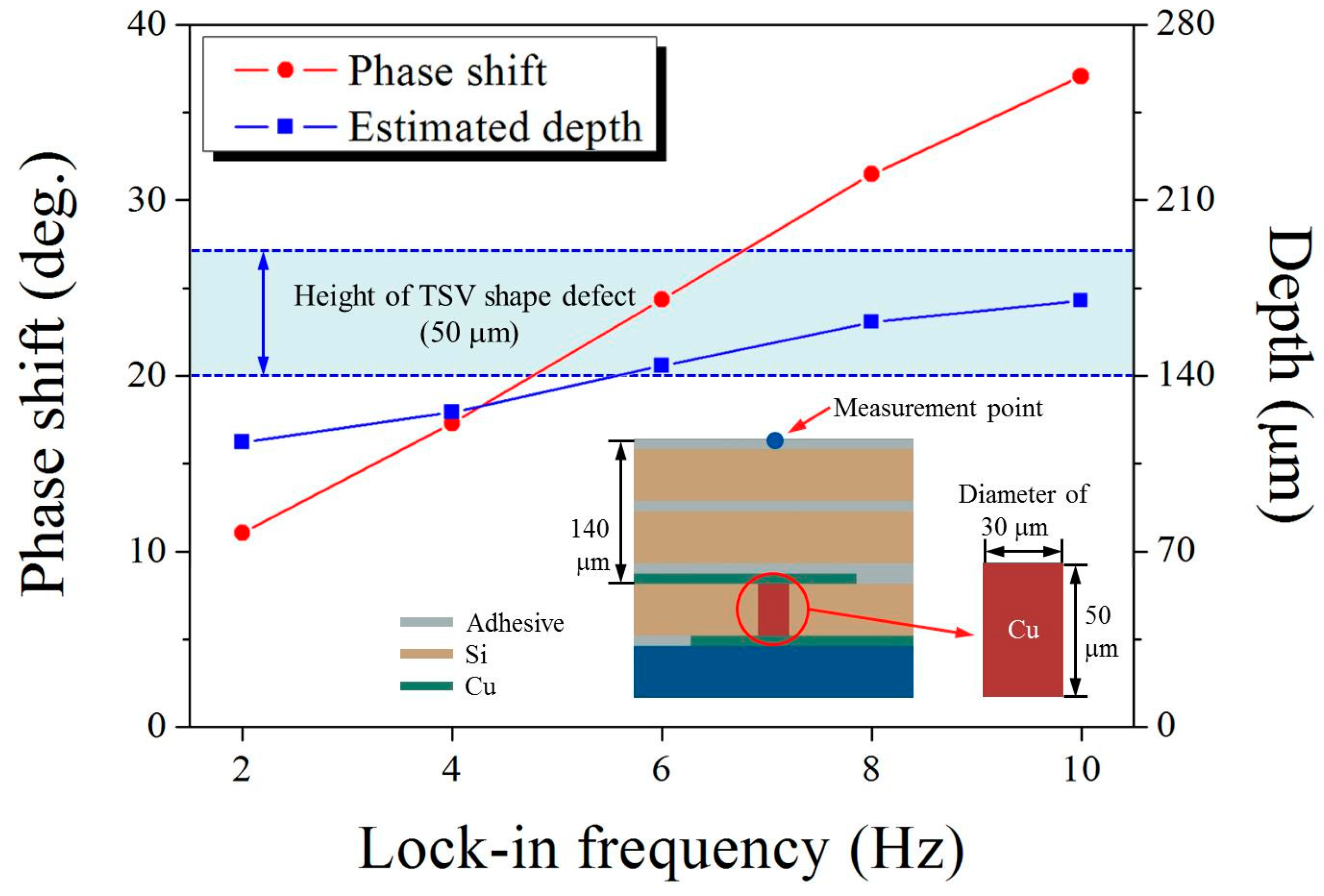

5. Results and Discussion

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Davis, W.R.; Wilson, J.; Mick, S.; Xu, J.; Hua, H.; Mineo, C.; Sule, A.; Steer, M.; Franzon, P.D. Demystifying 3D ICs: The Pros and Cons of Going Vertical. IEEE Des. Test Comput. 2005, 22, 498–510. [Google Scholar] [CrossRef]

- Rakotoniaina, J.P.; Breitenstein, O.; Langenkamp, M. Localization of weak heat sources in electronic devices using highly sensitive lock-in thermography. Mater. Sci. Eng. B 2002, 91, 481–485. [Google Scholar] [CrossRef]

- Schmidt, C.H.; Altmann, F.; Breitenstein, O. Application of lock-in thermography for failure analysis in integrated circuits using quantitative phase shift analysis. Mater. Sci. Eng. B 2012, 177, 1261–1267. [Google Scholar] [CrossRef]

- Phang, J.C.H.; Chan, D.S.H.; Tan, S.L.; Len, W.B.; Yim, K.H.; Koh, L.S.; Chua, C.M.; Balk, L.J. A review of near infrared photon emission microscopy and spectroscopy. In Proceedings of the 12th International Symposium on the Physical and Failure Analysis of Integrated Circuits, Singapore, 27 June–1 July 2005. [Google Scholar]

- Csendes, A.; Szekely, V.; Rencz, M. Thermal mapping with liquid crystal method. Microelectron. Eng. 1996, 31, 281–290. [Google Scholar] [CrossRef]

- Kolodner, P.; Tyson, J.A. Microscopic fluorescent imaging of surface temperature profiles with 0.01 °C resolution. Appl. Phys. Lett. 1982, 40, 782–784. [Google Scholar] [CrossRef]

- Shi, L.; Kwon, O.; Miner, A.C.; Majumdar, A. Design and batch fabrication of probes for sub-100 nm scanning thermal microscopy. J. Microelectromech. Syst. 2001, 10, 370–378. [Google Scholar] [CrossRef]

- Vellvehi, M.; Perpiñà, X.; Lauro, G.L.; Perillo, F.; Jordà, X. Irradiance-based emissivity correction in infrared thermography for electronic applications. Rev. Sci. Instrum. 2011, 82, 114901. [Google Scholar] [CrossRef] [PubMed]

- Chang, K.S.; Yang, S.C.; Kim, J.-Y.; Kook, M.H.; Ryu, S.Y.; Choi, H.Y.; Kim, G.H. Precise temperature mapping of GaN-based LEDs by quantitative infrared micro-thermography. Sensors 2012, 12, 4648–4660. [Google Scholar] [CrossRef] [PubMed]

- Busse, G.; Wu, D.; Karpen, W. Thermal wave imaging with phase sensitive modulated thermography. J. Appl. Phys. 1992, 71, 3962–3965. [Google Scholar] [CrossRef]

- Wu, D.; Salerno, A.; Schonbach, B.; Hallin, H.; Busse, G. Phase-sensitive modulation thermography and its applications for NDE. In Proceedings of the International Conference on Thermal Sensing and Imaging Diagnostic Applications, Orlando, FL, USA, 21 April 1997. [Google Scholar]

- Breitenstein, O.; Langenkamp, M. Lock-in contact thermography investigation of lateral electronic inhomogeneities in semiconductor devices. Sens. Actuators A Phys. 1998, 71, 46–50. [Google Scholar] [CrossRef]

- Wu, D.; Busse, G. Lock-in thermography for nondestructive evaluation of materials. Rev. Gén. Therm. 1998, 37, 693–703. [Google Scholar] [CrossRef]

- Kim, G.S.; Kim, G.-H.; Park, J.M.; Kim, D.-Y.; Cho, B.-K. Application of infrared lock-in thermography for the quantitative evaluation of bruises on pears. Infrared Phys. Technol. 2014, 63, 133–139. [Google Scholar] [CrossRef]

- Kim, G.S.; Lee, K.-S.; Kim, G.-H.; Hur, H.; Kim, D.-I.; Chang, K.S. Thermal Resolution Analysis of Lock-In Infrared Microscope. J. Korean Soc. Nondestruct. Test. 2015, 35, 12–17. [Google Scholar] [CrossRef]

- Christian, S.; Frank, A.; Rudolf, S.; Herve, D. Non-destructive defect depth determination at fully packaged and stacked die devices using Lock-in Thermography. In Proceedings of the 17th IEEE International Symposium Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 5–9 July 2010. [Google Scholar]

- Schlangen, R.; Motegi, S.; Nagatomo, T.; Schmidt, C.; Altmann, F.; Murakami, H.; Hollingshead, S.; West, J. Use of Lock-in thermography for nondestructive 3D defect localization on system in package and stacked-die technology. In Proceedings of the 37th International Symposium for Testing and Failure Analysis, San Jose, CA, USA, 13–17 November 2011; pp. 68–73. [Google Scholar]

- Schmidt, C.; Altmann, F. Quantitative phase shift analysis for 3D defect localization using lock-in thermography. In Proceedings of the 37th International Symposium for Testing and Failure Analysis American Society for Metals, San Jose, CA, USA, 13–17 November 2011; p. 34. [Google Scholar]

- Kijkanjanapaiboon, K.; Xie, M.; Zhou, J.; Fan, X. Investigation of dimensional and heat source effects in Lock-In Thermography applications in semiconductor packages. Appl. Therm. Eng. 2017, 113, 673–683. [Google Scholar] [CrossRef]

- Breitenstein, O.; Warta, W.; Langenkamp, M. Lock-In Thermography: Basics and Use for Evaluating Electronic Devices and Materials, 2nd ed.; Springer: Berlin, Germany, 2010. [Google Scholar]

- Giorleo, G.; Meola, C. Comparison between pulsed and modulated thermography in glass-epoxy laminates. NDT E Int. 2002, 35, 287–292. [Google Scholar] [CrossRef]

- Suter, P.; Graf, T. Photothermal thickness measurement of multilayered structures: An experimental and numerical analysis. J. Appl. Phys. 2008, 103, 033509. [Google Scholar] [CrossRef]

- Usamentiaga, R.; Venegas, P.; Guerediaga, J.; Vega, L.; Molleda, J.; Bulnes, F.G. Infrared thermography for temperature measurement and non-destructive testing-Review. Sensors 2014, 14, 12305–12348. [Google Scholar] [CrossRef] [PubMed]

- Chou, Y.C.; Yao, L. Automatic diagnostic system of electrical equipment using infrared thermography. In Proceedings of the International Conference of IEEE Soft Computing and Pattern Recognition, Malacca, Malaysia, 4–7 December 2009; pp. 155–160. [Google Scholar]

| Thermo-Physical Properties of Each Layer | |||||

|---|---|---|---|---|---|

| Silicon Layer | Adhesive Layer | Poly-Silicon Resistor | Cu Meander | Silicon Substrate | |

| Density, , (kg/m3) | 2329 | 1250 | 2320 | 8960 | 2329 |

| Specific heat capacity, , (J/kg·K) | 710 | 1110 | 678 | 384 | 700 |

| Thermal conductivity, , (W/m·K) | 149 | 0.14 | 34 | 401 | 130 |

| Electric conductivity, , (S/m) | 1 × 10−12 | 1.776 × 10−13 | 2.4045 × 103 | 5.81 × 107 | 1 × 10−12 |

| Dielectric constant | 1 | 8.32 | 4.5 | 1 | 1 |

| Depth Estimation for Two-Layer SSHSC (µm) | |||||

| Lock-In Frequency (flock-in) | Experiment | Numerical Simulation | Actual Depth | ||

| 3 V | 4 V | 5 V | |||

| 1 | 1203.25 | 1252.77 | 1319.87 | 1169.12 | 1342 |

| 2 | 1280.82 | 1380.63 | 1500.40 | 1257.51 | |

| 3 | 1456.73 | 1233.09 | 1328.74 | 1263.36 | |

| 4 | 1338.62 | 1240.74 | 1266.88 | 1408.15 | |

| 5 | 1390.19 | 1335.55 | 1448.55 | 1289.02 | |

| Depth Estimation for Three-Layer SSHSC (µm) | |||||

| Lock-In Frequency (flock-in) | Experiment | Numerical Simulation | Actual Depth | ||

| 3 V | 4 V | 5 V | |||

| 2 | 175.01 | 215.85 | 190.77 | 148.50 | 170 |

| 4 | 149.06 | 190.13 | 175.92 | 166.29 | |

| 6 | 177.09 | 168.36 | 159.40 | 161.98 | |

| 8 | 192.96 | 161.07 | 140.57 | 180.96 | |

| 10 | 198.83 | 168.07 | 169.73 | 187.09 | |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bae, J.Y.; Lee, K.-S.; Hur, H.; Nam, K.-H.; Hong, S.-J.; Lee, A.-Y.; Chang, K.S.; Kim, G.-H.; Kim, G. 3D Defect Localization on Exothermic Faults within Multi-Layered Structures Using Lock-In Thermography: An Experimental and Numerical Approach. Sensors 2017, 17, 2331. https://doi.org/10.3390/s17102331

Bae JY, Lee K-S, Hur H, Nam K-H, Hong S-J, Lee A-Y, Chang KS, Kim G-H, Kim G. 3D Defect Localization on Exothermic Faults within Multi-Layered Structures Using Lock-In Thermography: An Experimental and Numerical Approach. Sensors. 2017; 17(10):2331. https://doi.org/10.3390/s17102331

Chicago/Turabian StyleBae, Ji Yong, Kye-Sung Lee, Hwan Hur, Ki-Hwan Nam, Suk-Ju Hong, Ah-Yeong Lee, Ki Soo Chang, Geon-Hee Kim, and Ghiseok Kim. 2017. "3D Defect Localization on Exothermic Faults within Multi-Layered Structures Using Lock-In Thermography: An Experimental and Numerical Approach" Sensors 17, no. 10: 2331. https://doi.org/10.3390/s17102331

APA StyleBae, J. Y., Lee, K.-S., Hur, H., Nam, K.-H., Hong, S.-J., Lee, A.-Y., Chang, K. S., Kim, G.-H., & Kim, G. (2017). 3D Defect Localization on Exothermic Faults within Multi-Layered Structures Using Lock-In Thermography: An Experimental and Numerical Approach. Sensors, 17(10), 2331. https://doi.org/10.3390/s17102331