Biocompatible Potato-Starch Electrolyte-Based Coplanar Gate-Type Artificial Synaptic Transistors on Paper Substrates

Abstract

1. Introduction

2. Results and Discussion

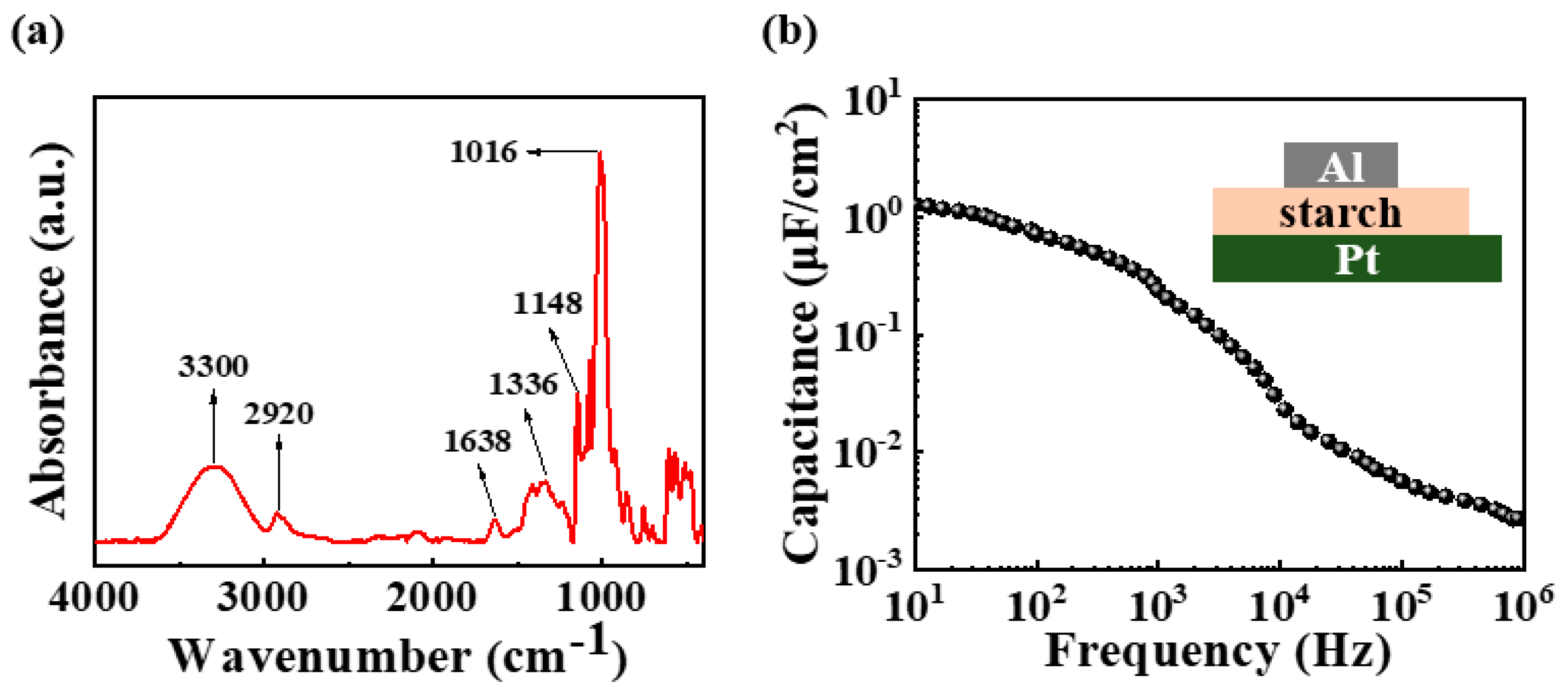

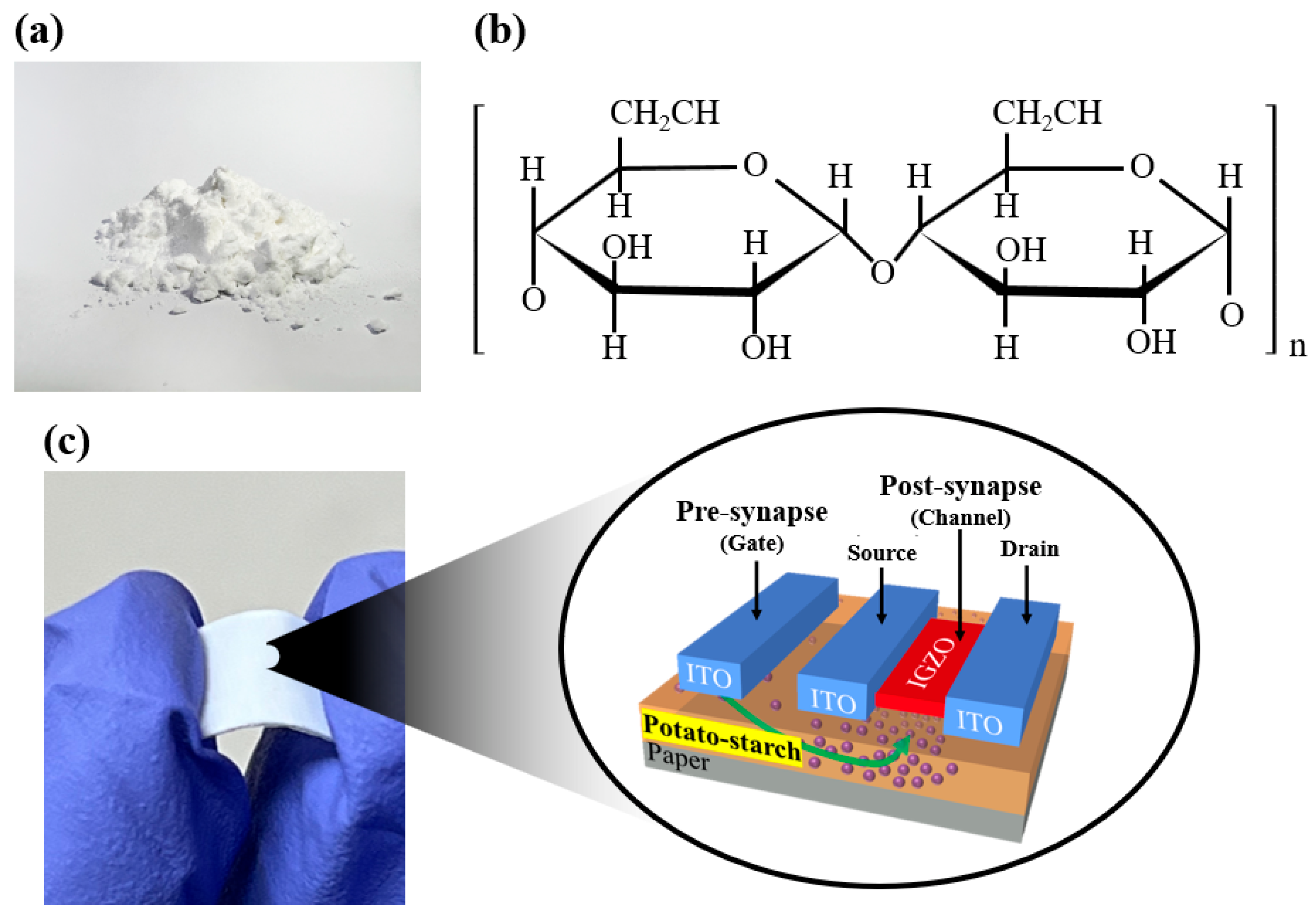

2.1. Characteristics Verification of Potato Starch

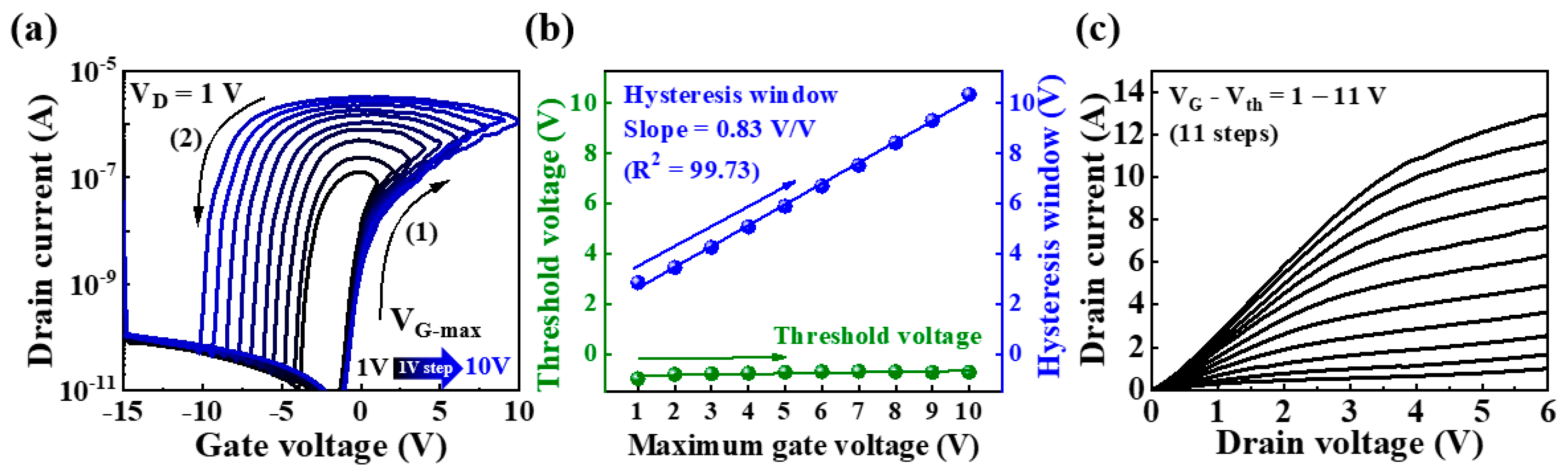

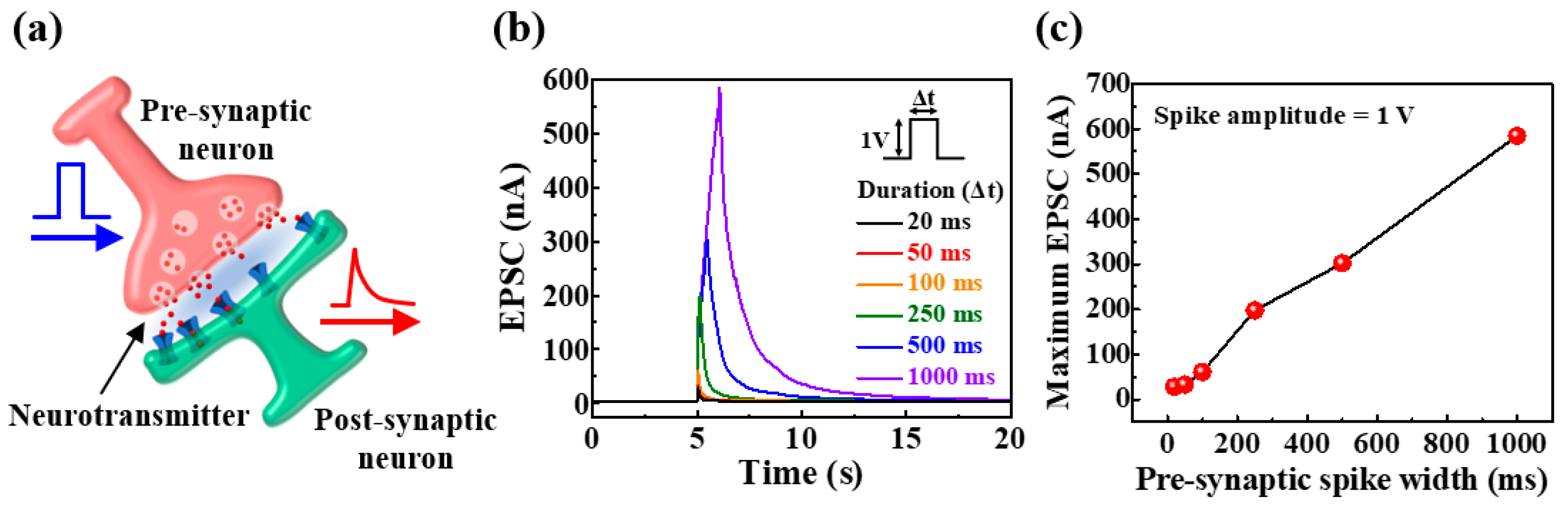

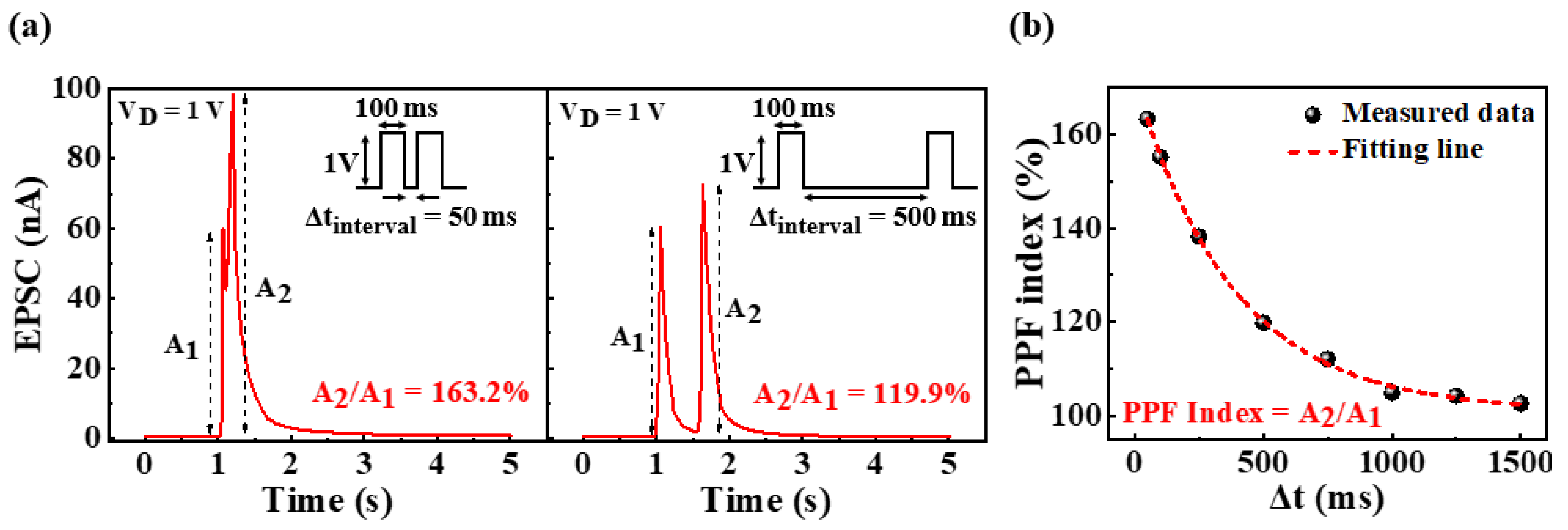

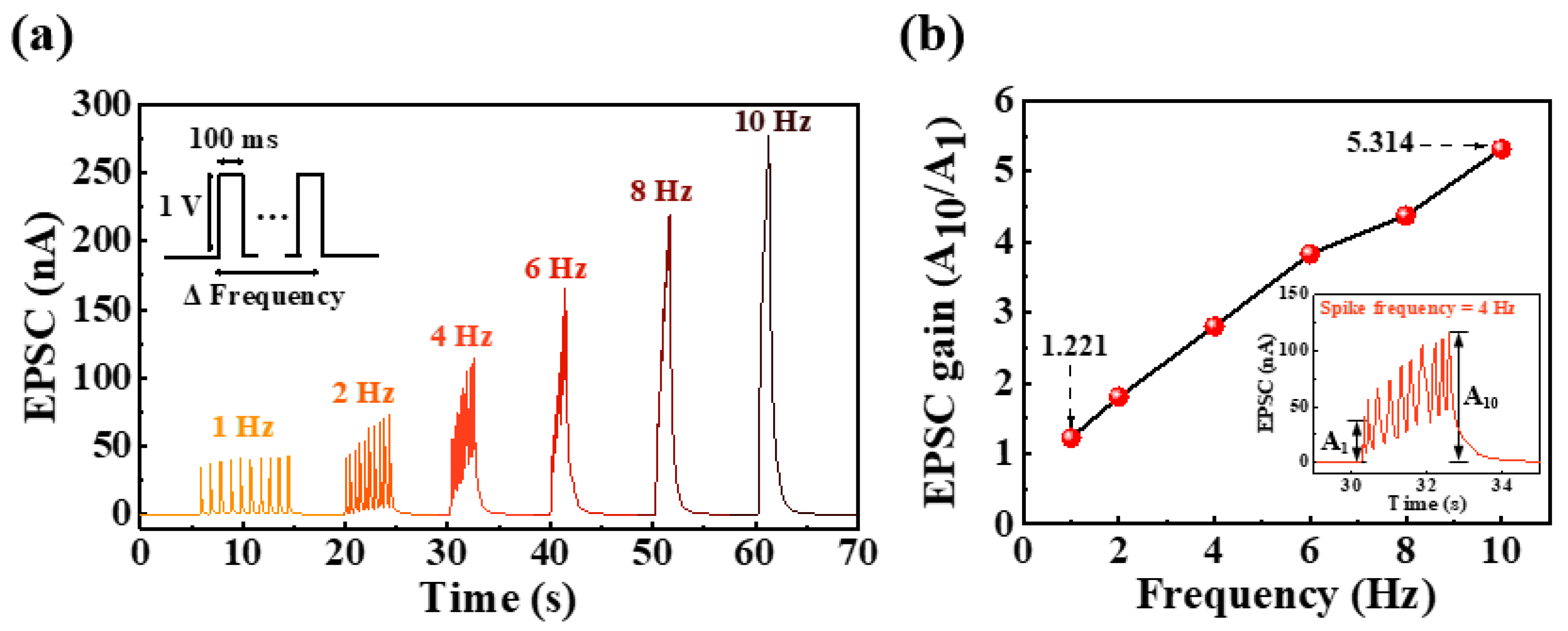

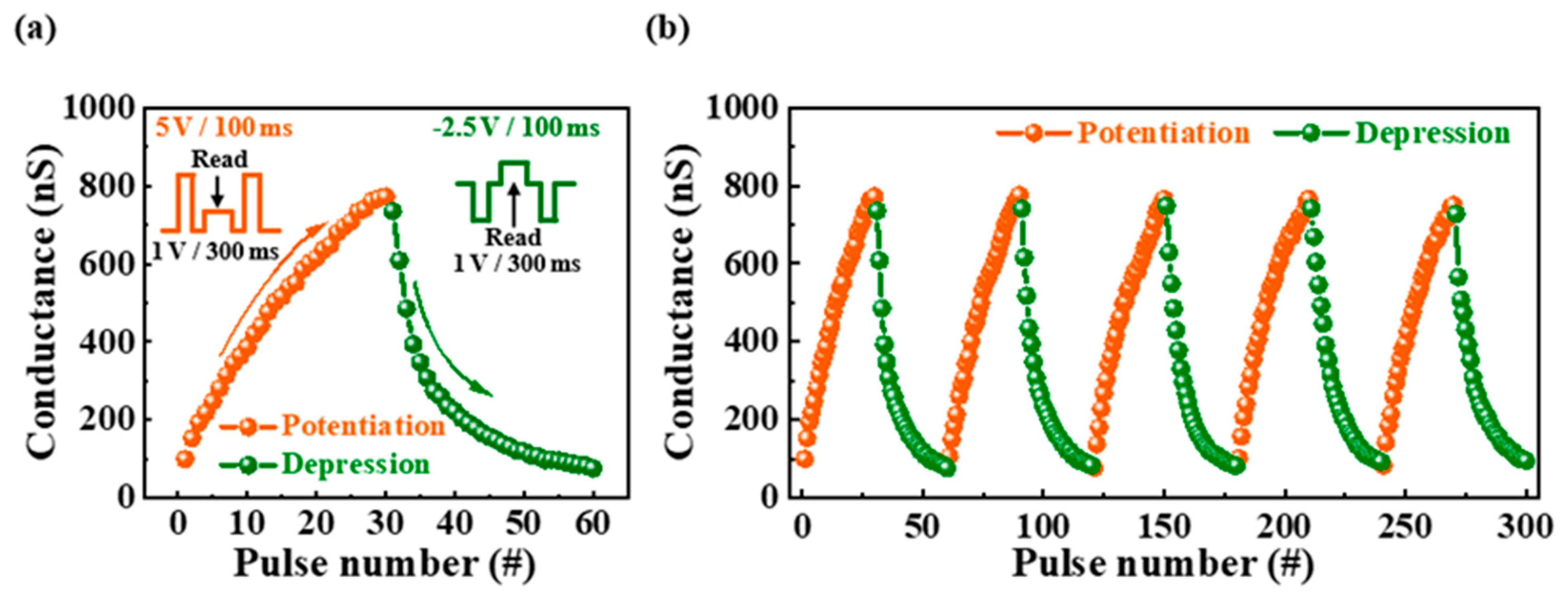

2.2. Electrical Properties and Synaptic Operation of Potato-Starch EDL Transistors

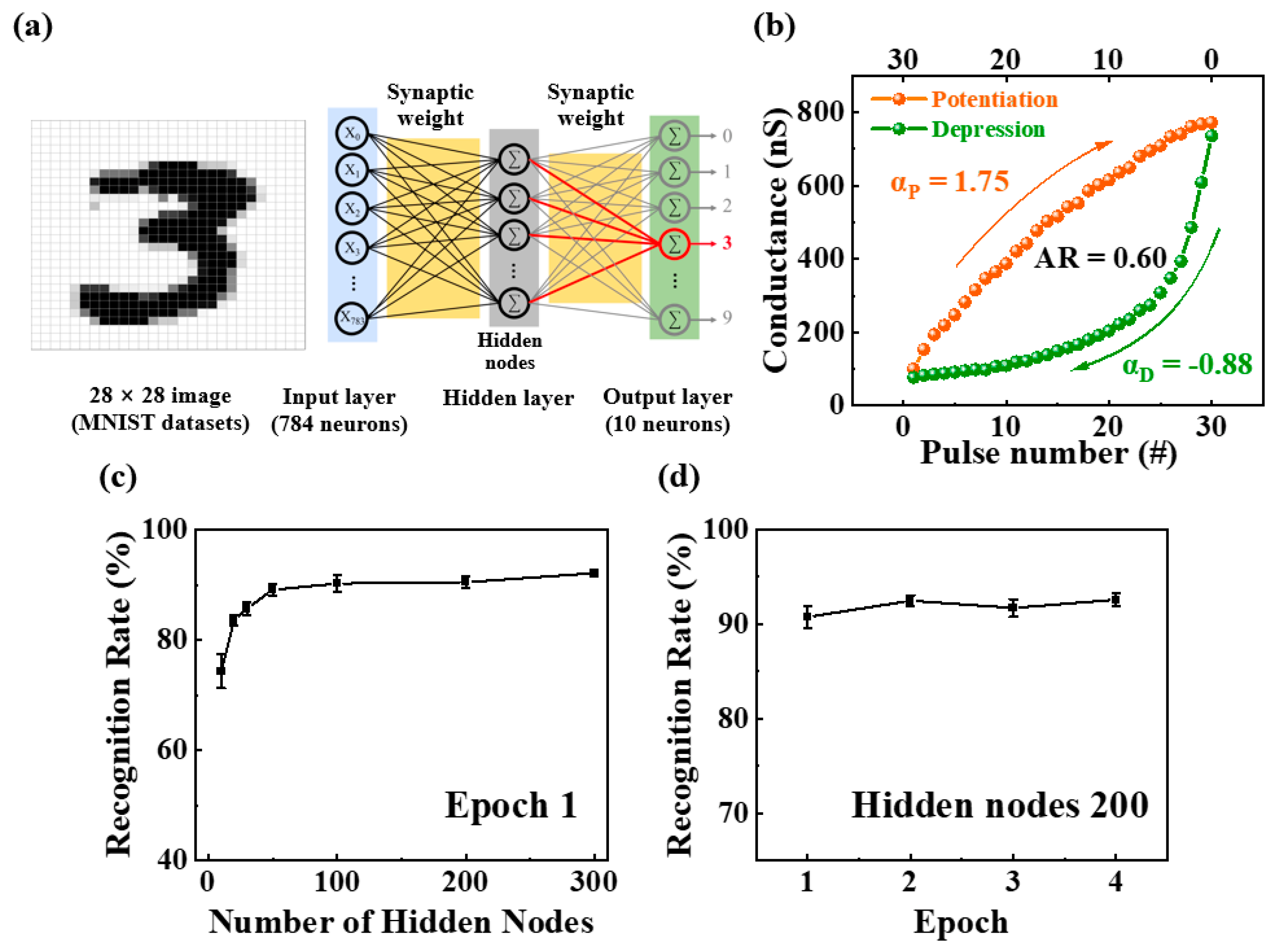

2.3. MNIST ANN Simulation

3. Methods and Materials

3.1. Materials

3.2. Fabrication Details of Potato-Starch EDL-Based Synaptic Transistors

3.3. Characterization

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Slavakis, K.; Giannakis, G.B.; Mateos, G. Modeling and optimization for big data analytics:(Statistical) learning tools for our era of data deluge. IEEE Signal Process. Mag. 2014, 31, 18–31. [Google Scholar] [CrossRef]

- Huang, P.; Kang, J.; Zhao, Y.; Chen, S.; Han, R.; Zhou, Z.; Chen, Z.; Ma, W.; Li, M.; Liu, L.; et al. Reconfigurable nonvolatile logic operations in resistance switching crossbar array for large-scale circuits. Adv. Mater. 2016, 28, 9758–9764. [Google Scholar] [CrossRef] [PubMed]

- Huang, W.; Xia, X.; Zhu, C.; Steichen, P.; Quan, W.; Mao, W.; Yang, J.; Chu, L.; Li, X.A. Memristive artificial synapses for neuromorphic computing. Nano-Micro Lett. 2021, 13, 85. [Google Scholar] [CrossRef] [PubMed]

- Boybat, I.; Le Gallo, M.; Nandakumar, S.R.; Moraitis, T.; Parnell, T.; Tuma, T.; Rajendran, B.; Leblebici, Y.; Sebastian, A.; Eleftheriou, E. Neuromorphic computing with multi-memristive synapses. Nat. Commun. 2018, 9, 2514. [Google Scholar] [CrossRef]

- Upadhyay, N.K.; Jiang, H.; Wang, Z.; Asapu, S.; Xia, Q.; Joshua Yang, J. Emerging memory devices for neuromorphic computing. Adv. Mater. Technol. 2019, 4, 1800589. [Google Scholar] [CrossRef]

- Indiveri, G.; Liu, S.C. Memory and information processing in neuromorphic systems. Proc. IEEE 2018, 103, 1379–1397. [Google Scholar] [CrossRef]

- Furber, S. Large-scale neuromorphic computing systems. J. Neural Eng. 2016, 13, 051001. [Google Scholar] [CrossRef]

- Zhu, L.Q.; Wan, C.J.; Guo, L.Q.; Shi, Y.; Wan, Q. Artificial synapse network on inorganic proton conductor for neuromorphic systems. Nat. Commun. 2014, 5, 3158. [Google Scholar] [CrossRef]

- Han, H.; Yu, H.; Wei, H.; Gong, J.; Xu, W. Recent progress in three-terminal artificial synapses: From device to system. Small 2019, 15, 1900695. [Google Scholar] [CrossRef]

- Yu, Y.; Ma, Q.; Ling, H.; Li, W.; Ju, R.; Bian, L.; Shi, N.; Qian, Y.; Yi, M.; Xie, L.; et al. Small-molecule-based organic field-effect transistor for nonvolatile memory and artificial synapse. Adv. Funct. Mater. 2019, 29, 1904602. [Google Scholar] [CrossRef]

- Åkerman, J. Toward a universal memory. Science 2005, 308, 508–510. [Google Scholar] [CrossRef]

- Jo, S.H.; Chang, T.; Ebong, I.; Bhadviya, B.B.; Mazumder, P.; Lu, W. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 2010, 10, 1297–1301. [Google Scholar] [CrossRef]

- Indiveri, G.; Linares-Barranco, B.; Legenstein, R.; Deligeorgis, G.; Prodromakis, T. Integration of nanoscale memristor synapses in neuromorphic computing architectures. Nanotechnology 2013, 24, 384010. [Google Scholar] [CrossRef]

- Fuller, E.J.; Gabaly, F.E.; Léonard, F.; Agarwal, S.; Plimpton, S.J.; Jacobs-Gedrim, R.B.; James, C.D.; Marinella, M.J.; Talin, A.A. Li-ion synaptic transistor for low power analog computing. Adv. Mater. 2017, 29, 1604310. [Google Scholar] [CrossRef]

- Kaneko, Y.; Nishitani, Y.; Ueda, M. Ferroelectric artificial synapses for recognition of a multishaded image. IEEE Trans. Electron Devices 2017, 61, 2827–2833. [Google Scholar] [CrossRef]

- Jiang, S.; Nie, S.; He, Y.; Liu, R.; Chen, C.; Wan, Q. Emerging synaptic devices: From two-terminal memristors to multiterminal neuromorphic transistors. Mater. Today Nano 2019, 8, 100059. [Google Scholar] [CrossRef]

- Huang, H.Y.; Ge, C.; Zhang, Q.H.; Liu, C.X.; Du, J.Y.; Li, J.K.; Wang, C.; Gu, L.; Yang, G.Z.; Jin, K.J. Electrolyte-gated synaptic transistor with oxygen ions. Adv. Funct. Mater. 2019, 29, 1902702. [Google Scholar] [CrossRef]

- Lee, C.; Choi, W.; Kwak, M.; Kim, S.; Hwang, H. Impact of electrolyte density on synaptic characteristics of oxygen-based ionic synaptic transistor. Appl. Phys. Lett. 2021, 119, 103503. [Google Scholar] [CrossRef]

- Dai, S.; Wang, Y.; Zhang, J.; Zhao, Y.; Xiao, F.; Liu, D.; Wang, T.; Huang, J. Wood-derived nanopaper dielectrics for organic synaptic transistors. ACS Appl. Mater. Interfaces 2018, 10, 39983–39991. [Google Scholar] [CrossRef]

- Fujimoto, T.; Awaga, K. Electric-double-layer field-effect transistors with ionic liquids. Phys. Chem. Chem. Phys. 2013, 15, 8983–9006. [Google Scholar] [CrossRef]

- Shao, F.; Yang, Y.; Zhu, L.Q.; Feng, P.; Wan, Q. Oxide-based synaptic transistors gated by sol–gel silica electrolytes. ACS Appl. Mater. Interfaces 2016, 8, 3050–3055. [Google Scholar] [CrossRef] [PubMed]

- Yu, F.; Zhu, L.Q.; Gao, W.T.; Fu, Y.M.; Xiao, H.; Tao, J.; Zhou, J.M. Chitosan-based polysaccharide-gated flexible indium tin oxide synaptic transistor with learning abilities. ACS Appl. Mater. Interfaces 2018, 10, 16881–16886. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.H.; Cho, W.J. Artificial Synapses Based on Bovine Milk Biopolymer Electric-Double-Layer Transistors. Polymers 2022, 14, 1372. [Google Scholar] [CrossRef] [PubMed]

- Gao, W.T.; Zhu, L.Q.; Tao, J.; Wan, D.Y.; Xiao, H.; Yu, F. Dendrite integration mimicked on starch-based electrolyte-gated oxide dendrite transistors. ACS Appl. Mater. Interfaces 2018, 10, 40008–40013. [Google Scholar] [CrossRef] [PubMed]

- Wu, G.; Zhang, J.; Wan, X.; Yang, Y.; Jiang, S. Chitosan-based biopolysaccharide proton conductors for synaptic transistors on paper substrates. J. Mater. Chem. C 2014, 2, 6249–6255. [Google Scholar] [CrossRef]

- Wu, G.; Wan, C.; Zhou, J.; Zhu, L.; Wan, Q. Low-voltage protonic/electronic hybrid indium zinc oxide synaptic transistors on paper substrates. Nanotechnology 2014, 25, 094001. [Google Scholar] [CrossRef]

- Shao, F.; Cai, M.L.; Gu, X.F.; Wu, G.D. Starch as ion-based gate dielectric for oxide thin film transistors. Org. Electron. 2017, 45, 203–208. [Google Scholar] [CrossRef]

- Liang, X.; Li, Z.; Liu, L.; Chen, S.; Wang, X.; Pei, Y. Artificial synaptic transistor with solution processed InOx channel and AlOx solid electrolyte gate. Appl. Phys. Lett. 2020, 116, 012102. [Google Scholar] [CrossRef]

- Pereda, A.E. Electrical synapses and their functional interactions with chemical synapses. Nat. Rev. Neurosci. 2014, 15, 250–263. [Google Scholar] [CrossRef]

- Lee, G.; Baek, J.H.; Ren, F.; Pearton, S.J.; Lee, G.H.; Kim, J. Artificial neuron and synapse devices based on 2D materials. Small 2021, 17, 2100640. [Google Scholar] [CrossRef]

- Abbott, L.F.; Nelson, S.B. Synaptic plasticity: Taming the beast. Nat. Neurosci. 2000, 3, 1178–1183. [Google Scholar] [CrossRef]

- Han, C.; Han, X.; Han, J.; He, M.; Peng, S.; Zhang, C.; Liu, X.; Gou, J.; Wang, J. Light-Stimulated Synaptic Transistor with High PPF Feature for Artificial Visual Perception System Application. Adv. Funct. Mater. 2022, 32, 2113053. [Google Scholar] [CrossRef]

- Buonomano, D.V. Decoding temporal information: A model based on short-term synaptic plasticity. J. Neurosci. 2000, 20, 1129–1141. [Google Scholar] [CrossRef]

- Hu, S.G.; Liu, Y.; Chen, T.P.; Liu, Z.; Yu, Q.; Deng, L.J.; Yin, Y.; Hosaka, S. Emulating the paired-pulse facilitation of a biological synapse with a NiOx-based memristor. Appl. Phys. Lett. 2013, 102, 183510. [Google Scholar] [CrossRef]

- Hu, W.; Jiang, J.; Xie, D.; Liu, B.; Yang, J.; He, J. Proton–electron-coupled MoS 2 synaptic transistors with a natural renewable biopolymer neurotransmitter for brain-inspired neuromorphic learning. J. Mater. Chem. C 2019, 7, 682–691. [Google Scholar] [CrossRef]

- Abbott, L.F.; Regehr, W.G. Synaptic computation. Nature 2004, 431, 796–803. [Google Scholar] [CrossRef]

- Zucker, R.S.; Regehr, W.G. Short-term synaptic plasticity. Ann. Rev. Physiol. 2002, 64, 355–405. [Google Scholar] [CrossRef]

- Fortune, E.S.; Rose, G.J. Roles for short-term synaptic plasticity in behavior. J. Physiol. Paris 2002, 96, 539–545. [Google Scholar] [CrossRef]

- Ding, G.; Yang, B.; Zhou, K.; Zhang, C.; Wang, Y.; Yang, J.Q.; Han, S.T.; Zhai, Y.; Roy, V.A.; Zhou, Y. Synaptic plasticity and filtering emulated in metal–organic frameworks nanosheets based transistors. Adv. Electron. Mater. 2020, 6, 1900978. [Google Scholar] [CrossRef]

- Yang, C.S.; Shang, D.S.; Liu, N.; Fuller, E.J.; Agrawal, S.; Talin, A.A.; Li, Y.Q.; Shen, B.G.; Sun, Y. All-solid-state synaptic transistor with ultralow conductance for neuromorphic computing. Adv. Funct. Mater. 2018, 28, 1804170. [Google Scholar] [CrossRef]

- Jang, J.W.; Park, S.; Jeong, Y.H.; Hwang, H. ReRAM-based synaptic device for neuromorphic computing. In Proceedings of the IEEE International Symposium on Circuits and Systems, Melbourne, Australia, 1–5 June 2014; pp. 1054–1057. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, H.-S.; Lee, Y.-J.; Park, H.; Cho, W.-J. Biocompatible Potato-Starch Electrolyte-Based Coplanar Gate-Type Artificial Synaptic Transistors on Paper Substrates. Int. J. Mol. Sci. 2022, 23, 15901. https://doi.org/10.3390/ijms232415901

Choi H-S, Lee Y-J, Park H, Cho W-J. Biocompatible Potato-Starch Electrolyte-Based Coplanar Gate-Type Artificial Synaptic Transistors on Paper Substrates. International Journal of Molecular Sciences. 2022; 23(24):15901. https://doi.org/10.3390/ijms232415901

Chicago/Turabian StyleChoi, Hyun-Sik, Young-Jun Lee, Hamin Park, and Won-Ju Cho. 2022. "Biocompatible Potato-Starch Electrolyte-Based Coplanar Gate-Type Artificial Synaptic Transistors on Paper Substrates" International Journal of Molecular Sciences 23, no. 24: 15901. https://doi.org/10.3390/ijms232415901

APA StyleChoi, H.-S., Lee, Y.-J., Park, H., & Cho, W.-J. (2022). Biocompatible Potato-Starch Electrolyte-Based Coplanar Gate-Type Artificial Synaptic Transistors on Paper Substrates. International Journal of Molecular Sciences, 23(24), 15901. https://doi.org/10.3390/ijms232415901