Generalized Adaptive Diversity Gradient Descent Bit-Flipping with a Finite State Machine

Abstract

1. Introduction

1.1. Related Works

1.2. Summary and Organization

- We propose a finite state machine for updates of potential, which defines which update values should be used based on the previous highlighting activity of the VN. A VN is assumed to be highlighted if its energy function in the current iteration is higher than the predefined threshold. In contrast to the idea presented in Paper [32], the potentials are no longer dependent on iteration but the state of a finite state machine.

- For the proposed algorithm, we present the numerical results for regular LDPC codes, both on the AWGN channel and on the BSC. In [31], the authors presented numerical results for the LDPC codes and the BSC, but the concept of potential was not used in that paper. In [32], numerical results for the simplified algorithm that uses the concept of potential for the BCH codes and the AWGN channel were presented. In that paper, no finite state machine was used to determine the update of potential.

- A new rule that helps in the decoding process of the BSC is introduced. This rule is called the rule and it helps the algorithm to overcome the problem related to the formal definition of the function. The importance of this rule will be shown later.

2. Preliminaries

- If the AWGN channel is used, at the output of the channel the vector , is received. The channel quality is determined by the received signal-to-noise ratio (SNR).

- If the BSC is used, at the output of the channel the vector , where . This can be considered as the special case of the AWGN channel, where a hard decision is applied prior to the decoding. The channel quality is determined by the crossover probability, denoted by .

3. Framework

3.1. Description of One Component Decoder

| Algorithm 1 gAD-GDBFwM with Finite State Machine in one component decoder |

| Input: , , , , Output: , , , |

| Initialization: , , , |

| , , while ( or () do for do end for update accordingly to update accordingly to and state machine , apply rule if necessary and update , , , end while , , |

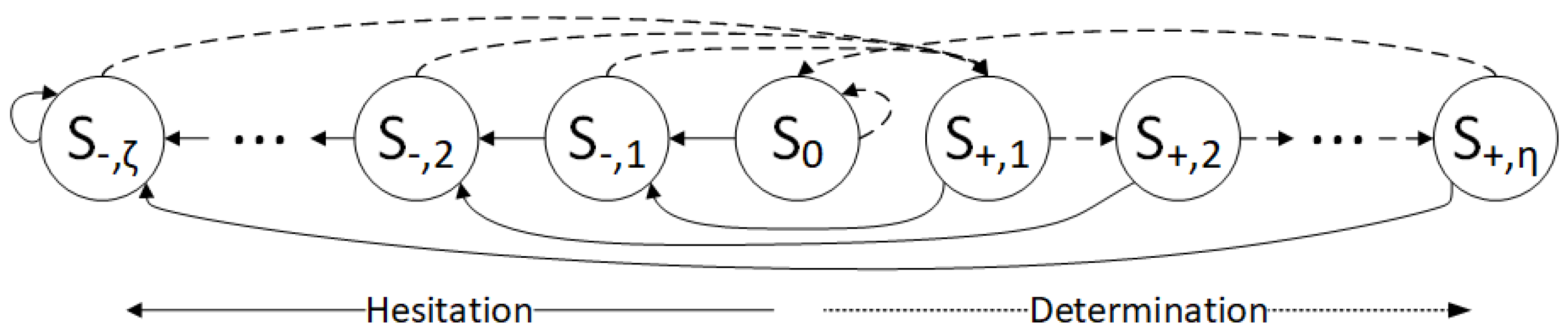

3.2. Description of the Finite State Machine

3.3. Finite State Machine and Trapping Set Example

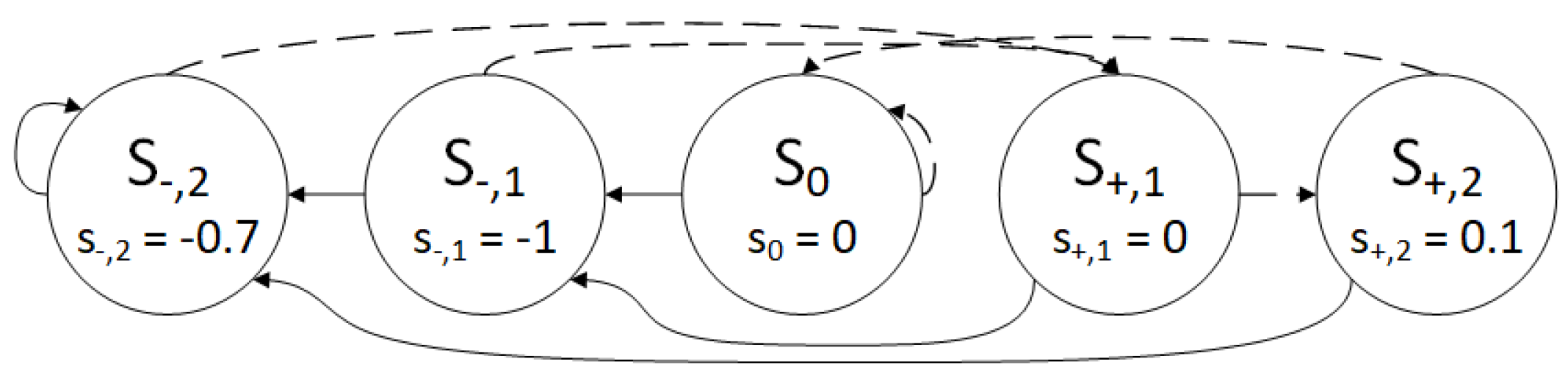

- If the variable is not highlighted in the first iteration, it will reach the state , according to the diagram shown in Figure 3 following the dashed lines. The updated potentials for these VNs are , , , and .

- If the VN is highlighted in the first decoding iteration, then it will go from the state to the state , according to the diagram shown in Figure 3 following the full lines. The corresponding update is , and therefore, for all highlighted VNs. In this case, the rule has to be applied to enable a correct codeword estimation. As an example, if the potential for the variable node after the update would be equal to , it is not clear how to calculate . When this scenario occurs, the parameter is used to push it a bit more to the opposite side when compared to the potential from the previous iteration, and the potential will be equal to . The modification according to the rule is denoted as in Figure 4. We set the value in this example, and therefore , , , , , , and .

3.4. Concatenation of the Component Decoders

- For the first decoder (), the input vector of the potentials is equal to the received word, i.e., . Furthermore, momentum states and potential states are equal for all variables, , and .

- If and , the inputs are also defined with the expressions: , , and .

- If and , the input vector of the potentials is equal to the output vector of potentials from the previous decoder: , and using the similar approach , and .

3.5. Learnable Framework

- The parameters which are heuristically chosen for the t-th component decoder, such as the starting state , the maximum number of iterations , and the margin . These are parameters which are known before the machine learning optimization procedure.

- The basic parameters of the t-th decoder are the number of states for the finite state machine , the length of the momentum vector , the maximum value which momentum can take I, and the value of the flag restart . For one combination of these parameters, one GA optimization has to be run.

- The parameters obtained as a result of the GA optimization are learnable weights and , state values s for states in the finite state machine, and momentum vector .

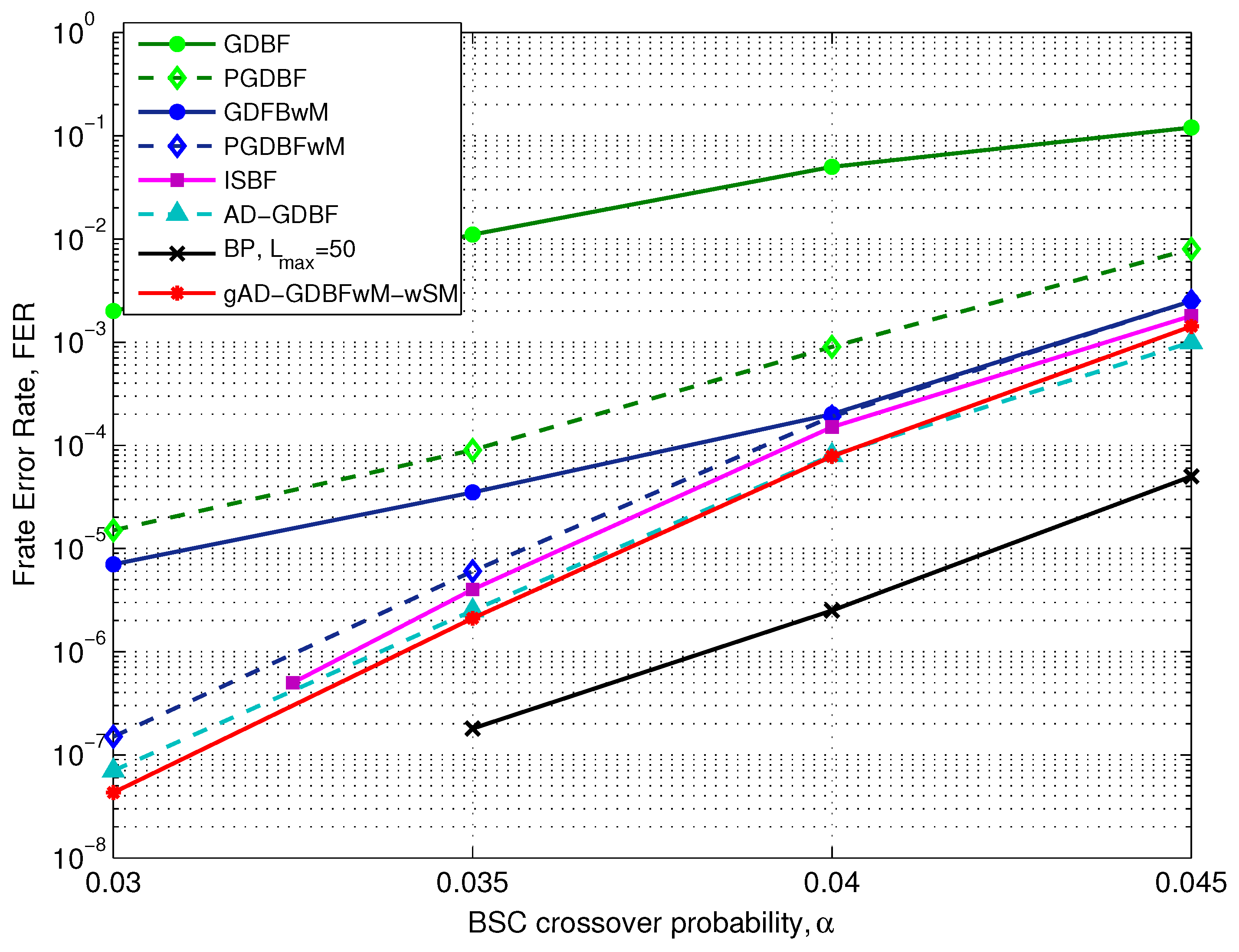

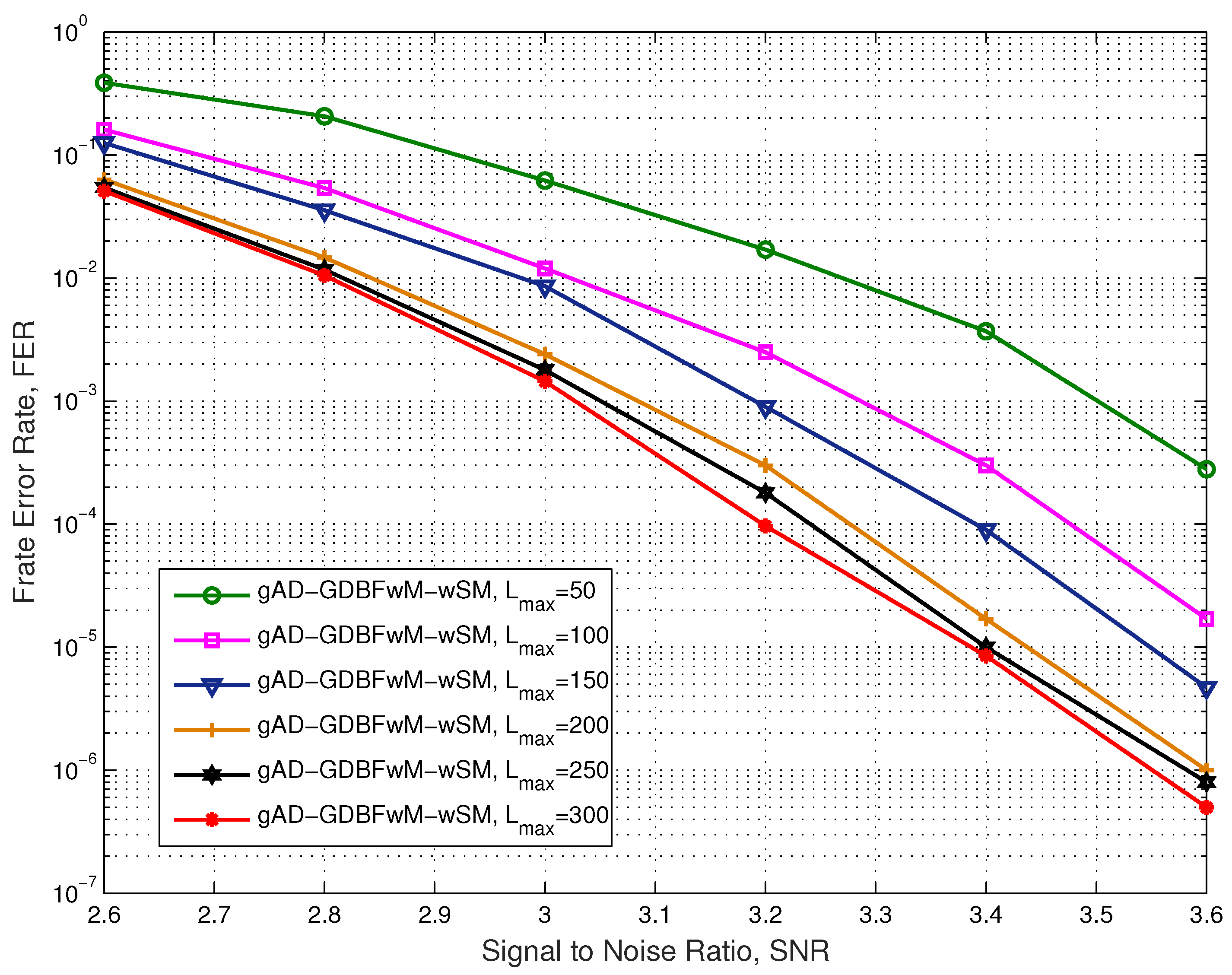

4. Numerical Results

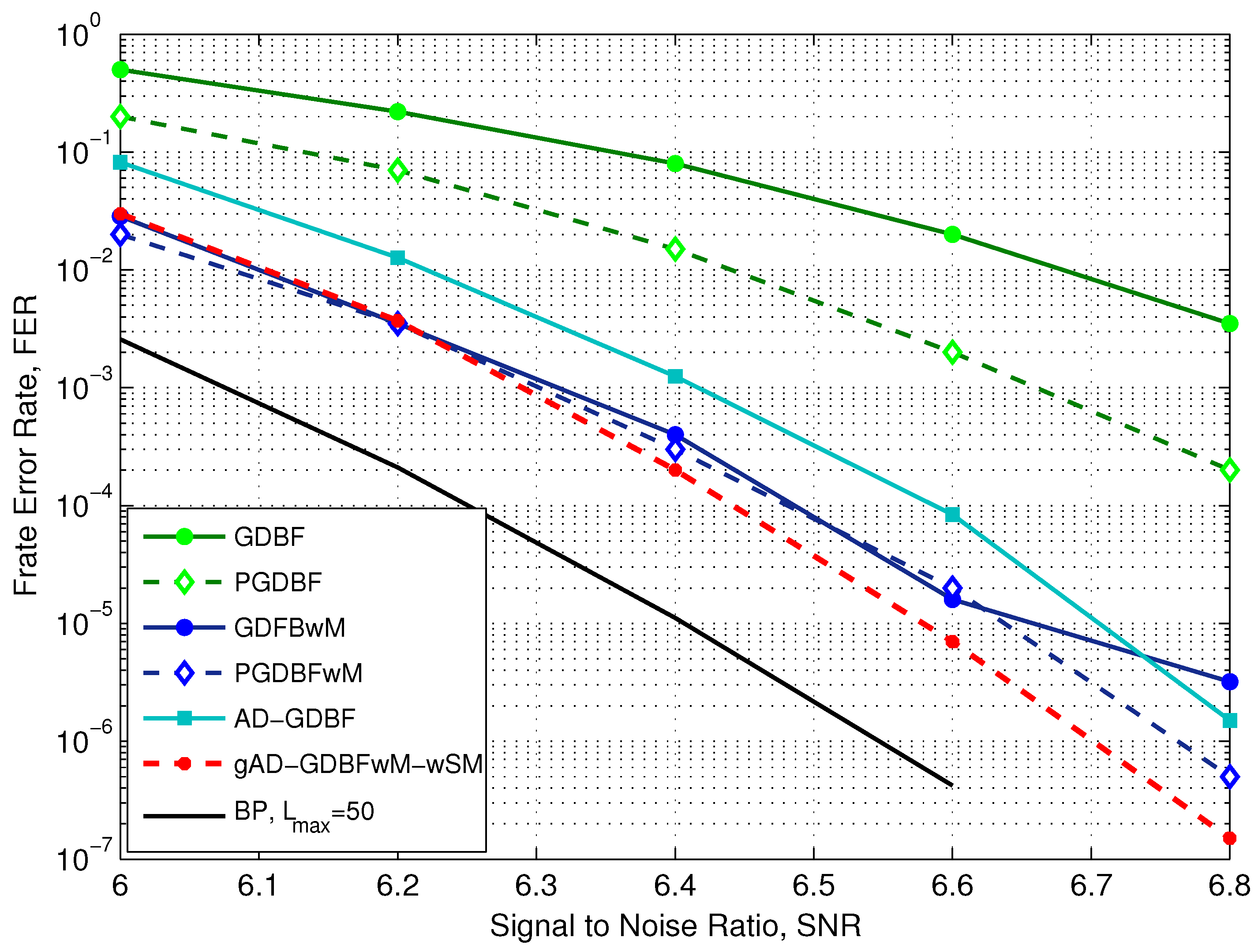

4.1. Tanner Code

4.2. i-RISC Code

4.3. IEEE 802.3an Code

5. Complexity Analysis

- One floating-point register;

- One floating-point adder;

- One register for the state of that variable;

- One comparator.

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lin, S.; Costello, D.J. Error Control Coding, Fundamentals and Applications, 2nd ed.; Prentice Hall: Upper Saddle River, NJ, USA, 2004. [Google Scholar]

- Gallager, R.G. Low Density Parity Check Codes. Ph.D. Thesis, Harvard University, Cambridge, MA, USA, 1963. [Google Scholar]

- Richardson, T.; Shokrollahi, M.; Urbanke, R. Design of capacity-approaching irregular low-density parity-check codes. IEEE Trans. Inf. Theory 2002, 47, 619–637. [Google Scholar] [CrossRef]

- Standard ETSI TS 138 101-1 V16.5.0 (2020-11); 5G; NR; User Equipment (UE) Radio Transmission and Reception; Part 1: Range 1 Standalone (3GPP TS 38.101-1 Version 16.5.0 Release 16). European Telecommunications Standards Institute: Sophia Antipolis, France, 2020.

- Standard ETSI EN 302 307-2 V1.2.1 (2020-05); Digital Video Broadcasting (DVB); Second Generation Framing Structure, Channel Coding and Modulation Systems for Broadcasting, Interactive Services, News Gathering and Other Broadband Satellite Applications; Part 2: DVB-S2 Extensions (DVB-S2X). European Telecommunications Standards Institute: Sophia Antipolis, France, 2020.

- IEEE. IEEE SA—IEEE 802.11ax-2021. Available online: https://standards.ieee.org/ieee/802.11ax/7180/ (accessed on 12 November 2024).

- Zhao, K.; Zhao, W.; Sun, H.; Zhang, T.; Zhang, X.; Zheng, N. LDPC-in-SSD: Making Advanced Error Correction Codes Work Effectively in Solid State Drives. In Proceedings of the 11th USENIX Conference on File and Storage Technologies (FAST 13), San Jose, CA, USA, 12–15 February 2013; pp. 243–256. [Google Scholar]

- Tanner, R. A recursive approach to low complexity codes. IEEE Trans. Inf. Theory 1981, 27, 533–547. [Google Scholar] [CrossRef]

- Pearl, J. Reverend Bayes on Inference Engines: A Distributed Hierarchical Approach. In Proceedings of the AAAI National Conference on AI, Pittsburgh, PA, USA, 18–20 August 1982; pp. 133–136. [Google Scholar]

- Chen, J.; Fossorier, M. Near optimum universal belief propagation based decoding of low-density parity check codes. IEEE Trans. Commun. 2002, 50, 406–414. [Google Scholar] [CrossRef]

- Planjery, S.K.; Declercq, D.; Danjean, L.; Vasic, B. Finite Alphabet Iterative Decoders—Part I: Decoding Beyond Belief Propagation on the Binary Symmetric Channel. IEEE Trans. Commun. 2013, 61, 4033–4045. [Google Scholar] [CrossRef]

- Declercq, D.; Vasic, B.; Planjery, S.K.; Li, E. Finite Alphabet Iterative Decoders—Part II: Towards Guaranteed Error Correction of LDPC Codes via Iterative Decoder Diversity. IEEE Trans. Commun. 2013, 61, 4046–4057. [Google Scholar] [CrossRef]

- Zhang, J.; Fossorier, M. A modified weighted bit-flipping decoding of low-density Parity-check codes. IEEE Commun. Lett. 2004, 8, 165–167. [Google Scholar] [CrossRef]

- Chang, T.C.Y.; Su, Y.T. Dynamic Weighted Bit-Flipping Decoding Algorithms for LDPC Codes. IEEE Trans. Commun. 2015, 63, 3950–3963. [Google Scholar] [CrossRef]

- Wadayama, T.; Nakamura, K.; Yagita, M.; Funahashi, Y.; Usami, S.; Takumi, I. Gradient descent bit flipping algorithms for decoding LDPC codes. IEEE Trans. Commun. 2010, 58, 1610–1614. [Google Scholar] [CrossRef]

- Sundararajan, G.; Winstead, C.; Boutillon, E. Noisy Gradient Descent Bit-Flip Decoding for LDPC Codes. IEEE Trans. Commun. 2014, 62, 3385–3400. [Google Scholar] [CrossRef]

- Rasheed, O.A.; Ivaniš, P.; Vasić, B. Fault-Tolerant Probabilistic Gradient-Descent Bit Flipping Decoder. IEEE Commun. Lett. 2014, 18, 1487–1490. [Google Scholar] [CrossRef]

- Cui, H.; Lin, J.; Song, S.; Wang, Z. A New Probabilistic Gradient Descent Bit Flipping Decoder for LDPC Codes. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019. [Google Scholar] [CrossRef]

- Cui, H.; Lin, J.; Wang, Z. An Improved Gradient Descent Bit-Flipping Decoder for LDPC Codes. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 3188–3200. [Google Scholar] [CrossRef]

- Cui, H.; Lin, J.; Wang, Z. Information Storage Bit-Flipping Decoder for LDPC Codes. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 2464–2468. [Google Scholar] [CrossRef]

- Jiang, M.; Fan, D. A Low-Latency BF Decoding of LDPC Codes with Dynamic Thresholds. IEEE Commun. Lett. 2021, 25, 2781–2785. [Google Scholar] [CrossRef]

- Chen, Y.; Cui, H.; Lin, J.; Wang, Z. Fine-Grained Bit-Flipping Decoding for LDPC Codes. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 896–900. [Google Scholar] [CrossRef]

- He, C.; Deng, K.; Song, S.; Wang, Z. Column-Weighted Probabilistic GDBF Decoder for Irregular LDPC Codes. In Proceedings of the 2023 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Foz do Iguacu, Brazil, 20–23 June 2023. [Google Scholar] [CrossRef]

- Dai, B.; Liu, R.; Gao, C.; Mei, Z. Noisy Gradient Descent Bit-Flipping Decoder Based on Adjustment Factor for LDPC Codes. IEEE Commun. Lett. 2018, 22, 1152–1155. [Google Scholar] [CrossRef]

- Deng, K.; Chen, Y.; Song, S.; Wang, Z. Sign Aided Adaptive Noisy Gradient Descent Bit-Flipping Algorithm for LDPC Codes. In Proceedings of the 2022 IEEE 8th International Conference on Computer and Communications (ICCC), Chengdu, China, 9–12 December 2022. [Google Scholar] [CrossRef]

- Savin, V. Gradient Descent Bit-Flipping Decoding with Momentum. In Proceedings of the 2021 11th International Symposium on Topics in Coding (ISTC), Montreal, QC, Canada, 30 August–3 September 2021. [Google Scholar] [CrossRef]

- Ivanis, P.; Al Rasheed, O.; Vasić, B. MUDRI: A fault-tolerant decoding algorithm. In Proceedings of the 2015 IEEE International Conference on Communications (ICC), London, UK, 8–12 June 2015; pp. 4291–4296. [Google Scholar] [CrossRef]

- Vasić, B.; Ivaniš, P.; Declercq, D.; LeTrung, K. Approaching maximum likelihood performance of LDPC codes by stochastic resonance in noisy iterative decoders. In Proceedings of the 2016 Information Theory and Applications Workshop (ITA), La Jolla, CA, USA, 31 January–5 February 2016; pp. 1–9. [Google Scholar] [CrossRef]

- Chang, T.C.Y.; Wang, P.H.; Su, Y.T. Multi-Stage Bit-Flipping Decoding Algorithms for LDPC Codes. IEEE Commun. Lett. 2019, 23, 1524–1528. [Google Scholar] [CrossRef]

- Ivaniš, P.; Brkić, S.; Vasić, B. Suspicion Distillation Gradient Descent Bit-Flipping Algorithm. Entropy 2022, 24, 558. [Google Scholar] [CrossRef]

- Brkic, S.; Ivanis, P.; Vasić, B. Adaptive Gradient Descent Bit-Flipping Diversity Decoding. IEEE Commun. Lett. 2022, 26, 2257–2261. [Google Scholar] [CrossRef]

- Milojković, J.; Brkic, S.; Ivanis, P.; Vasić, B. Learning to Decode Linear Block Codes using Adaptive Gradient-Descent Bit-Flipping. In Proceedings of the 2023 12th International Symposium on Topics in Coding (ISTC), Brest, France, 4–8 September 2023. [Google Scholar] [CrossRef]

- Mirjalili, S. Evolutionary Algorithms and Neural Networks Theory and Applications; Springer: Cham, Switzerland, 2019. [Google Scholar]

- Jeruchim, M.C.; Balaban, P.; Shanmugan, K.S. Simulation of Communication Systems: Modeling, Methodology and Techniques; Springer Science & Business Media: New York, NY, USA, 2006. [Google Scholar]

- Decoders and Matrices for the Given Numerical Results. Available online: https://github.com/jovan94/MDPI_StateMachineForPotentials (accessed on 21 November 2024).

- Tanner, R.; Sridhara, D.; Sridharan, A.; Fuja, T.; Costello, D. LDPC block and convolutional codes based on circulant matrices. IEEE Trans. Inf. Theory 2004, 50, 2966–2984. [Google Scholar] [CrossRef]

- Le, K.; Declercq, D.; Ghaffari, F.; Kessal, L.; Boncalo, O.; Savin, V. Variable-Node-Shift Based Architecture for Probabilistic Gradient Descent Bit Flipping on QC-LDPC Codes. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 2183–2195. [Google Scholar] [CrossRef]

- IEEE. IEEE Standard for Information Technology—Telecommunications and Information Exchange Between Systems—LAN/MAN—Specific Requirements Part 3: CSMA/CD Access Method and Physical Layer Specifications—Amendment: Physical Layer and Management Parameters for 10 Gb/s Operation, Type 10GBASE-T. Available online: https://standards.ieee.org/ieee/802.3an/3560/ (accessed on 9 November 2024).

| Symbol | Meaning |

|---|---|

| n | codeword length |

| k | number of information bits |

| R | code rate |

| parity-check matrix | |

| element of a parity-check matrix | |

| variable node associated to i-th column | |

| parity-check equation related to the j-th row | |

| set of indices for | |

| set of indices for | |

| regular LDPC code, degree of | |

| regular LDPC code, degree of | |

| transmitted codeword | |

| received codeword | |

| estimated codeword | |

| maximum no. iterations for t-th decoder | |

| maximum no. iterations for chained decoder | |

| restart flag of the t-th decoder | |

| Energy function for i-th VN in the ℓ-th iteration | |

| , | learnable weights |

| value of momentum for variable i | |

| momentum state of the i-th variable | |

| momentum vector | |

| number of values in momentum vector | |

| I | maximum value in momentum vector |

| set of highlighted variables in ℓ-th iteration | |

| margin (threshold) parameter | |

| potential for variable in ℓ-th iteration | |

| value for rule | |

| vector of potentials for t-th decoder | |

| vector of momentum states for t-th decoder | |

| vector of states for finite state machine | |

| finite state machine | |

| S | state in the finite state machine |

| s | value of state in the finite state machine |

| set of + states in the finite state machine | |

| number of states in | |

| set of − states in the finite state machine | |

| number of states in | |

| neutral state | |

| starting state | |

| function which converts finite state machines |

| Momentum Set Name | I | |

|---|---|---|

| 2 | 3 | |

| 3 | 2 | |

| 4 | 2 | |

| 3 | 3 |

| Finite State Machine Name | No. State | ||

|---|---|---|---|

| 5 | 2 | 2 | |

| 3 | 1 | 1 | |

| 2 | 1 | 0 | |

| 4 | 2 | 1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Milojković, J.; Brkić, S.; Ivaniš, P.; Vasić, B. Generalized Adaptive Diversity Gradient Descent Bit-Flipping with a Finite State Machine. Entropy 2025, 27, 49. https://doi.org/10.3390/e27010049

Milojković J, Brkić S, Ivaniš P, Vasić B. Generalized Adaptive Diversity Gradient Descent Bit-Flipping with a Finite State Machine. Entropy. 2025; 27(1):49. https://doi.org/10.3390/e27010049

Chicago/Turabian StyleMilojković, Jovan, Srdjan Brkić, Predrag Ivaniš, and Bane Vasić. 2025. "Generalized Adaptive Diversity Gradient Descent Bit-Flipping with a Finite State Machine" Entropy 27, no. 1: 49. https://doi.org/10.3390/e27010049

APA StyleMilojković, J., Brkić, S., Ivaniš, P., & Vasić, B. (2025). Generalized Adaptive Diversity Gradient Descent Bit-Flipping with a Finite State Machine. Entropy, 27(1), 49. https://doi.org/10.3390/e27010049