FPGA Design Integration of a 32-Microelectrodes Low-Latency Spike Detector in a Commercial System for Intracortical Recordings

Abstract

:1. Introduction

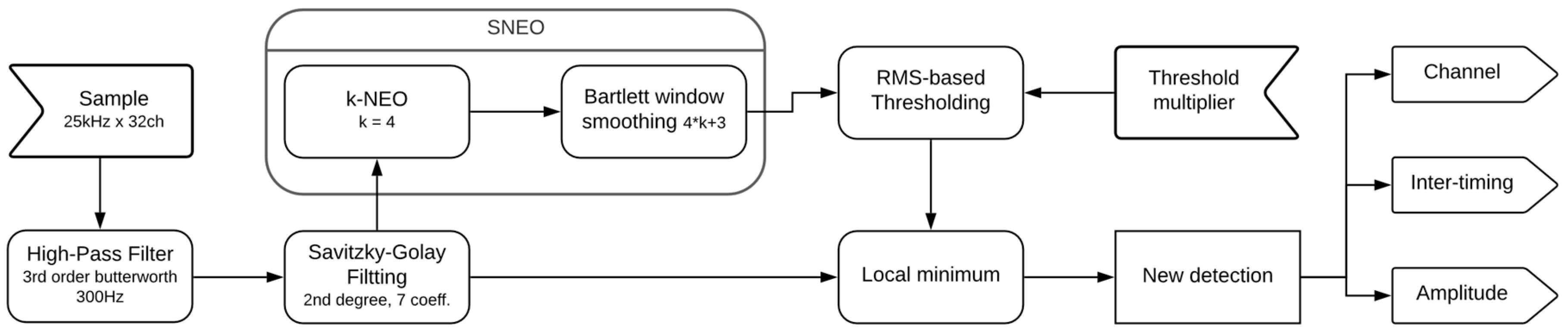

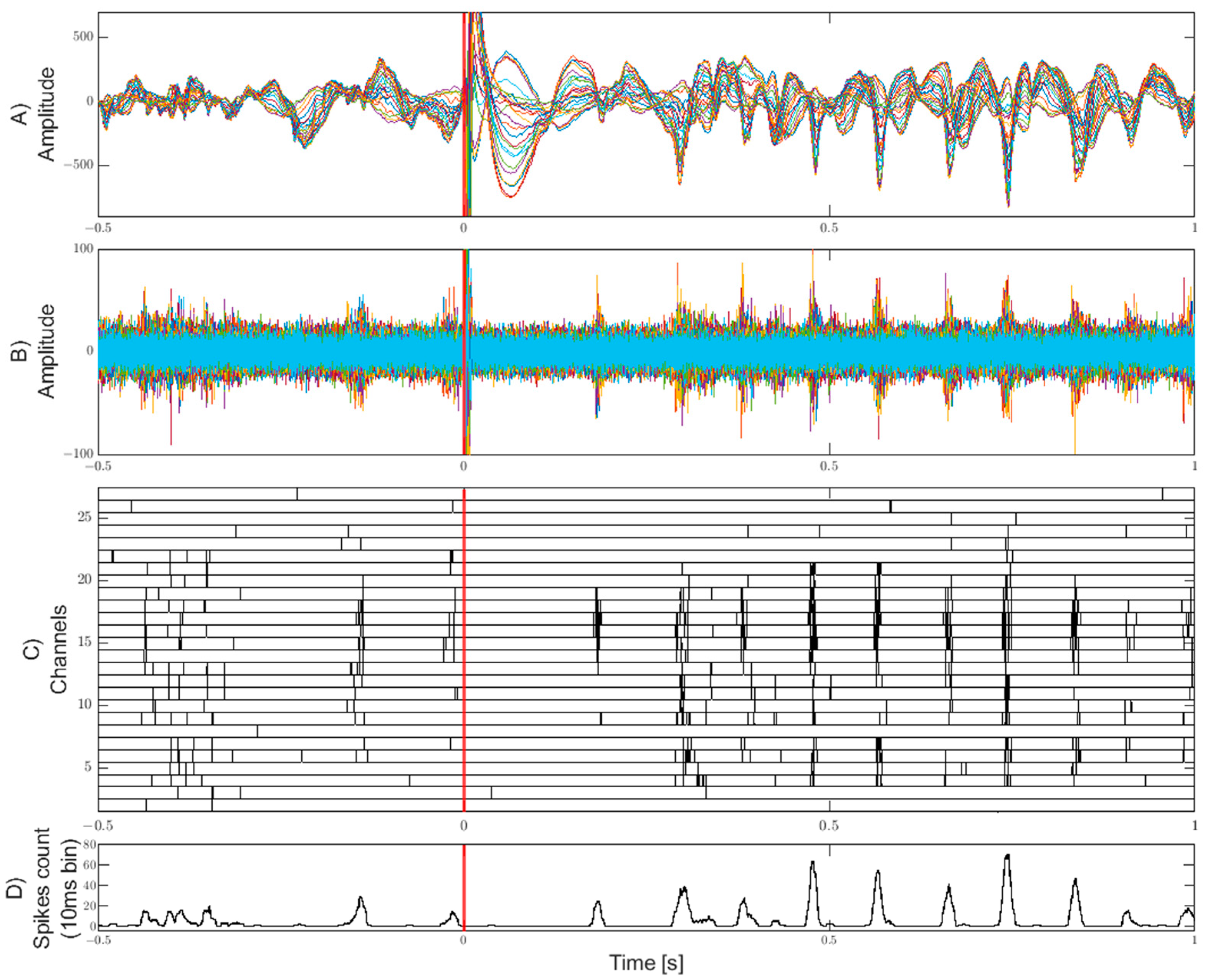

- A third order Butterworth high-pass Infinite Input Response (IIR) filter with a cutoff frequency of 300 Hz and a Savitzky-Golay smoothing filter [18], fitting the high-pass filtered signal with a second degree polynomial.

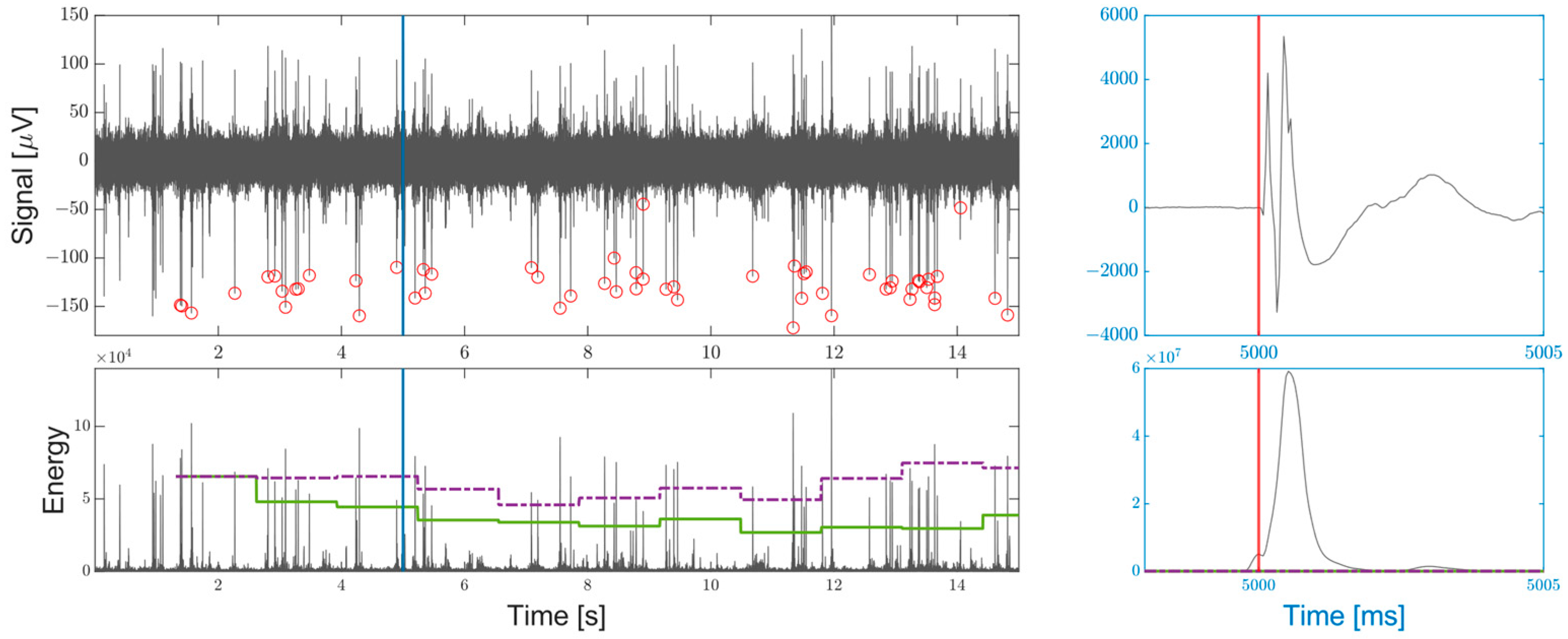

- A point-by-point signal energy estimation using the SNEO [19], that aggregates both the frequency and the amplitude of the voltage fluctuations in a series of samples that can be compared with a threshold.

- A novel dynamic threshold per-channel estimation based on the Root Mean Square (RMS) of the SNEO output that accommodates any drift of the probe or changes in the signal quality, that rapidly converges to a firing-independent value close to an ideal threshold based only on the noise energy. The threshold can be adjusted by the user, to open the detection of both the single AP and MUA.

- A post-ICMS blind window of a user-defined duration, to prevent the detection of false positives following the high increase in the signal power due to the artifact induced by the injection of a current.

- The capability to stream the amplitude, the channel, and the timing of each detected spikes via the USB to the host computer, and, simultaneously, via the UART protocol to any other connected device with sub-milliseconds latency. By the UART command, it is also possible to trigger the ICMS set from the host application.

2. Materials and Methods

2.1. Design Algorithms

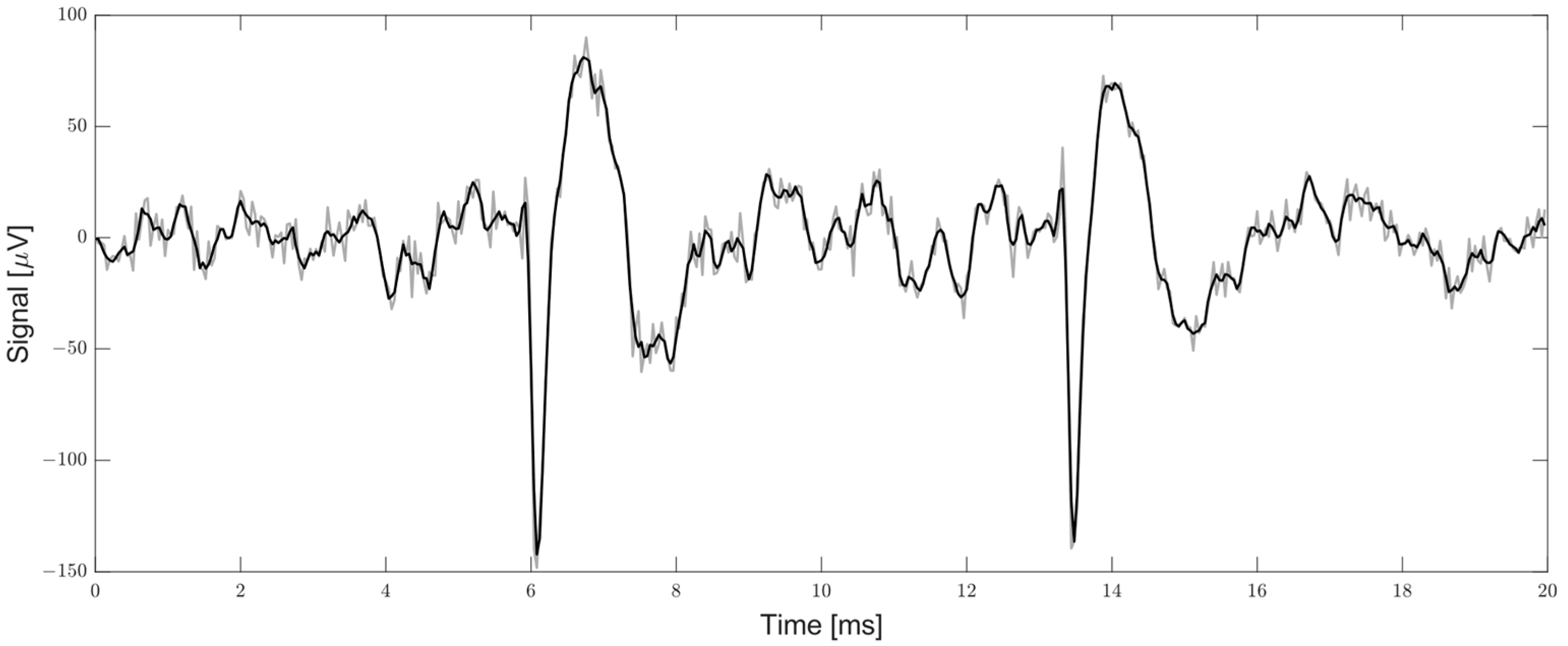

2.1.1. High-Pass and Savitzky-Golay Filtering

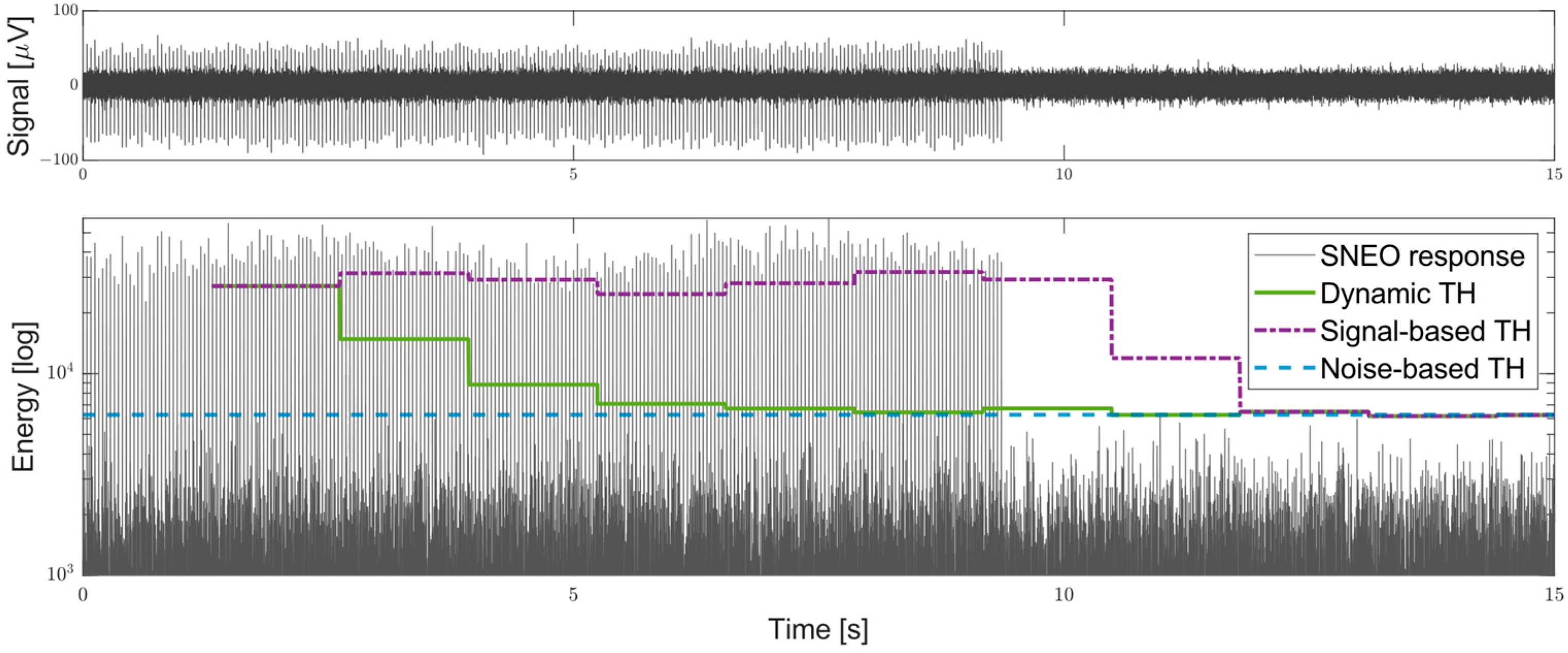

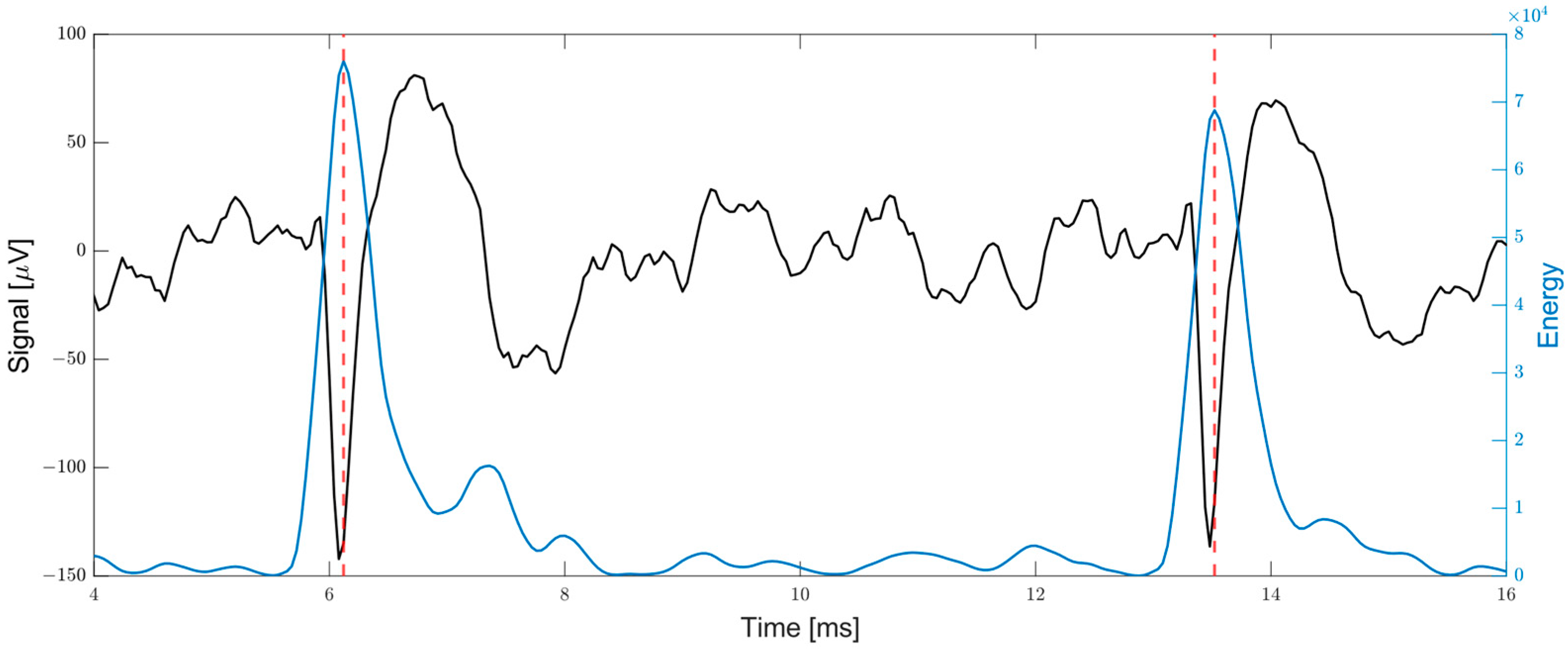

2.1.2. Smoothed Nonlinear Energy Operator and Threshold

2.1.3. Spike Detection and Local Minimum Finder

2.2. Design Implementation

2.2.1. Filter

2.2.2. Savitzky-Golay Fitting

2.2.3. Smoothed Nonlinear Energy Operator

2.2.4. Energy RMS and Threshold

2.2.5. Local Minimum Finder and Spike Output

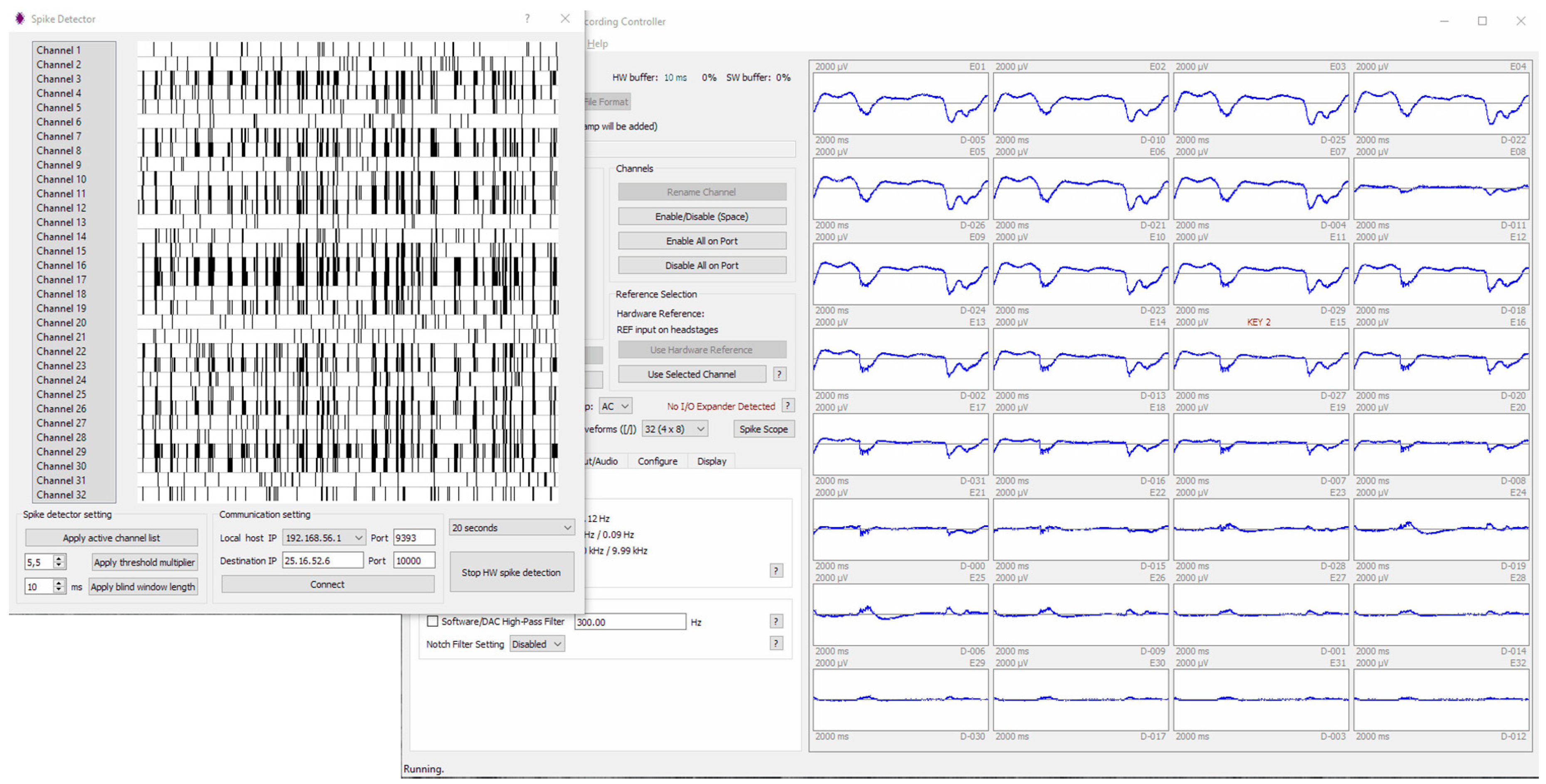

2.2.6. Software Integration

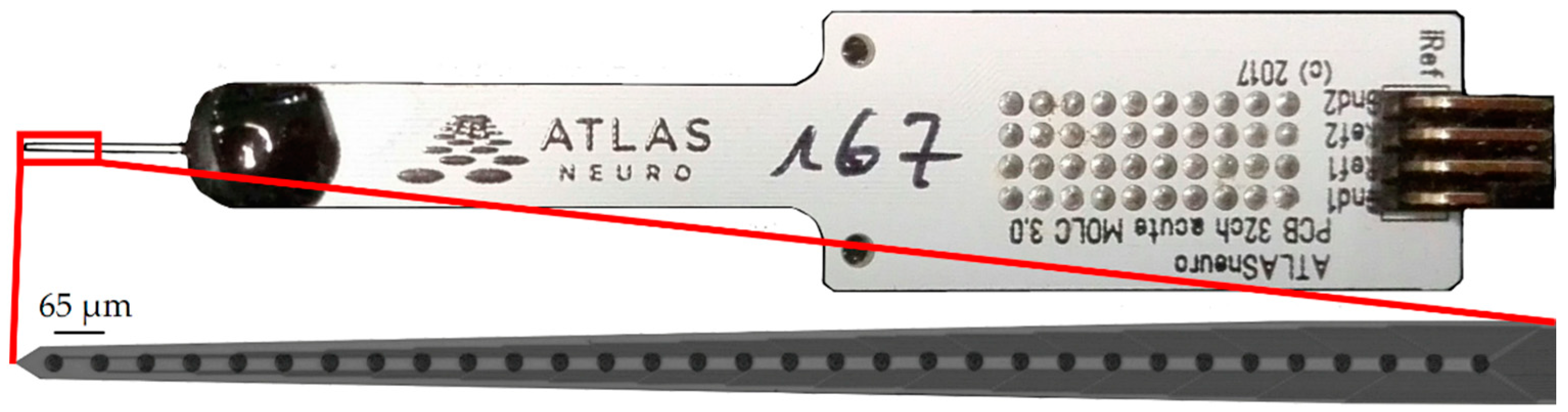

2.3. Animals and Surgical Procedure

3. Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A

References

- Kim, G.H.; Kim, K.; Lee, E.; An, T.; Choi, W.; Lim, G.; Shin, J.H. Recent Progress on Microelectrodes in Neural Interfaces. Materials 2018, 11, 1995. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Obien, M.E.J.; Frey, U. Large-Scale, High-Resolution Microelectrode Arrays for Interrogation of Neurons and Networks. In In Vitro Neuronal Networks; Advances in Neurobiology; Chiappalone, M., Pasquale, V., Frega, M., Eds.; Springer: Cham, Switzerland, 2019; Volume 22. [Google Scholar] [CrossRef]

- Spira, M.E.; Hai, A. Multi-electrode array technologies for neuroscience and cardiology. Nat. Nanotechnol. 2013, 8, 83–94. [Google Scholar] [CrossRef] [PubMed]

- Nam, Y.; Wheeler, B.C. In vitro microelectrode array technology and neural recordings. Crit. Rev. Biomed. Eng. 2011, 39, 45–61. [Google Scholar] [CrossRef] [PubMed]

- Jun, J.J.; Steinmetz, N.A.; Siegle, J.H.; Denman, D.J.; Bauza, M.; Barbarits, B.; Lee, A.K.; Anastassiou, C.A.; Andrei, A.; Aydın, Ç.; et al. Fully integrated silicon probes for high-density recording of neural activity. Nature 2017, 551, 232–236. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Scholvin, J.; Kinney, J.P.; Bernstein, J.G.; Moore-Kochlacs, C.; Kopell, N.; Fonstad, C.G.; Boyden, E.S. Close-Packed Silicon Microelectrodes for Scalable Spatially Oversampled Neural Recording. IEEE Trans. Biomed. Eng. 2016, 63, 120–130. [Google Scholar] [CrossRef] [Green Version]

- Berényi, A.; Somogyvári, Z.; Nagy, A.J.; Roux, L.; Long, J.D.; Fujisawa, S.; Stark, E.; Leonardo, A.; Harris, T.D.; Buzsáki, G. Large-scale, high-density (up to 512 channels) recording of local circuits in behaving animals. J. Neurophysiol. 2014, 111, 1132–1149. [Google Scholar] [CrossRef] [Green Version]

- Butovas, S.; Schwarz, C. Spatiotemporal effects of microstimulation in rat neocortex: A parametric study using multielectrode recordings. J. Neurophysiol. 2003, 90, 3024–3039. [Google Scholar] [CrossRef]

- Tehovnik, E.J. Electrical stimulation of neural tissue to evoke behavioral responses. J. Neurosci. Methods 1996, 65, 1–17. [Google Scholar] [CrossRef]

- Harrison, B.J.; Pantelis, C. Multiunit Activity. In Encyclopedia of Psychopharmacology; Stolerman, I.P., Ed.; Springer: Berlin/Heidelberg, Germany, 2010. [Google Scholar] [CrossRef]

- Angotzi, G.N.; Boi, F.; Lecomte, A.; Miele, E.; Malerba, M.; Zucca, S.; Casile, A.; Berdondini, L. SiNAPS: An implantable active pixel sensor CMOS-probe for simultaneous large-scale neural recordings. Biosens. Bioelectron. 2019, 126, 355–364. [Google Scholar] [CrossRef]

- Raducanu, B.C.; Yazicioglu, R.F.; Lopez, C.M.; Ballini, M.; Putzeys, J.; Wang, S.; Andrei, A.; Rochus, V.; Welkenhuysen, M.; Helleputte, N.V.; et al. Time Multiplexed Active Neural Probe with 1356 Parallel Recording Sites. Sensors 2017, 17, 2388. [Google Scholar] [CrossRef] [Green Version]

- Rolston, J.D.; Gross, R.E.; Potter, S.M. A low-cost multielectrode system for data acquisition enabling real-time closed-loop processing with rapid recovery from stimulation artifacts. Front. Neuroeng. 2009, 2, 12. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Venkatraman, S.; Elkabany, K.; Long, J.D.; Yao, Y.; Carmena, J.M. A System for Neural Recording and Closed-Loop Intracortical Microstimulation in Awake Rodents. IEEE Trans. Biomed. Eng. 2009, 56, 15–22. [Google Scholar] [CrossRef] [PubMed]

- Bi, G.Q.; Poo, M.M. Synaptic modifications in cultured hippocampal neurons: Dependence on spike timing, synaptic strength, and postsynaptic cell type. J. Neurosci. 1998, 18, 10464–10472. [Google Scholar] [CrossRef] [PubMed]

- Grosenick, L.; Marshel, J.H.; Deisseroth, K. Closed-loop and activity-guided optogenetic control. Neuron 2015, 86, 106–139. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Newman, J.P.; Fong, M.F.; Millard, D.C.; Whitmire, C.J.; Stanley, G.B.; Potter, S.M. Optogenetic feedback control of neural activity. Elife 2015. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Savitzky, A.; Golay, M.J.E. Smoothing and Differentiation of Data by Simplified Least Squares Procedures. Anal. Chem. 1964, 36, 1627–1639. [Google Scholar] [CrossRef]

- Mukhopadhyay, S.; Ray, G.C. A new interpretation of nonlinear energy operator and its efficacy in spike detection. IEEE Trans. Biomed. Eng. 1998, 45, 180–187. [Google Scholar] [CrossRef]

- Tambaro, M.; Vallicelli, E.A.; Saggese, G.; Strollo, A.; Baschirotto, A.; Vassanelli, S. Evaluation of In Vivo Spike Detection Algorithms for Implantable MTA Brain—Silicon Interfaces. J. Low Power Electron. Appl. 2020, 10, 26. [Google Scholar] [CrossRef]

- Azami, H.; Sanei, S. Spike detection approaches for noisy neuronal data: Assessment and comparison. Neurocomputing 2014, 133, 491–506. [Google Scholar] [CrossRef]

- Yu, B.; Mak, T.; Li, X.; Xia, F.; Yakovlev, A.; Sun, Y.; Poon, C.S. Real-Time FPGA-Based Multichannel Spike Sorting Using Hebbian Eigenfilters. IEEE J. Emerg. Sel. Top. Circuits Syst. 2011, 1, 502–515. [Google Scholar] [CrossRef] [Green Version]

- Tariq, T.; Satti, M.H.; Saeed, M.; Kamboh, A.M. Low SNR neural spike detection using scaled energy operators for implantable brain circuits. Annu. Int. Conf. IEEE Eng. Med. Biol. Soc. 2017, 1074–1077. [Google Scholar] [CrossRef]

- Wang, P.K.; Pun, S.H.; Chen, C.H.; McCullagh, E.A.; Klug, A.; Li, A.; Vai, M.I.; Mak, P.U.; Lei, T.C. Low-latency single channel real-time neural spike sorting system based on template matching. PLoS ONE 2019, 14. [Google Scholar] [CrossRef] [PubMed]

- Valencia, D.; Alimohammad, A. A Real-Time Spike Sorting System Using Parallel OSort Clustering. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 1700–1713. [Google Scholar] [CrossRef] [PubMed]

- Yael, D.; Bar-Gad, I. Filter based phase distortions in extracellular spikes. PLoS ONE 2017, 12. [Google Scholar] [CrossRef] [PubMed]

- Shimegi, S.; Akasaki, T.; Ichikawa, T.; Sato, H. Physiological and anatomical organization of multiwhisker response interactions in the barrel cortex of rats. J. Neurosci. 2000, 20, 6241–6248. [Google Scholar] [CrossRef]

- Swanson, L.W. Brain maps 4.0-Structure of the rat brain: An open access atlas with global nervous system nomenclature ontology and flatmaps. J. Comp. Neurol. 2018, 526, 935–943. [Google Scholar] [CrossRef] [Green Version]

- Murphy, M.; Buccelli, S.; Bornat, Y.; Bundy, D.; Nudo, R.; Guggenmos, D.; Chiappalone, M. Improving an open-source commercial system to reliably perform activity-dependent stimulation. J. Neural Eng. 2019, 16. [Google Scholar] [CrossRef]

- Luan, S.; Williams, I.; Maslik, M.; Liu, Y.; De Carvalho, F.; Jackson, A.; Quiroga, R.Q.; Constandinou, T.G. Compact standalone platform for neural recording with real-time spike sorting and data logging. J. Neural Eng. 2018, 15. [Google Scholar] [CrossRef]

| Mask | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

|---|---|---|---|---|---|---|---|

| a | 0.9274 | −2.7821 | 2.7821 | −0.9274 | \ | \ | \ |

| b | 1 | −2.8492 | 2.7096 | −0.8600 | \ | \ | \ |

| SG | −0.0952 | 0.1429 | 0.2857 | 0.3333 | 0.2857 | 0.1429 | −0.0952 |

| Coefficients | Rounding Error (%) | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 | ||

| a | 30.388 | −91.163 | 91.163 | −30.388 | 0.0021 | 0.0010 | 0.0010 | 0.0021 | |

| b | 32.768 | −93.364 | 88.789 | −28.180 | 0 | 0.0009 | 0.0001 | 0.0008 | |

| Component | Clock Cycles to Output | Notes |

|---|---|---|

| Samples preprocessing | 7 | cross-clock and samples format |

| High-pass filter | 11 | complete the filter state after 17 |

| Savitzky-Golay fitting | 15 | 8 + mask length |

| SNEO | 34 | 18 + 4 * k (k = 4) |

| Thresholding | 5 | |

| Local minimum | 20 | 4 k + 4 (k = 4) |

| Samples postprocessing | 4 | writing to output FIFOs |

| Threshold estimation 1 | 11 | the square root and eight more cycles are required every samples |

| Total | 96 | One hundred and twenty-five cycles are available between the two samples |

| Logic | Default | Custom | Increment | Available |

|---|---|---|---|---|

| Slice register | 8883 | 13,770 | 4887 | 54,576 |

| Slice LUT | 17,775 | 23,065 | 5290 | 27,288 |

| BRAM16 | 69 | 76 | 7 | 116 |

| BRAM8 | 0 | 15 | 15 | 232 |

| DSP48A1 | 8 | 19 | 11 | 58 |

| This Work | Default | [29] | [24] | [30] | |

|---|---|---|---|---|---|

| AP detection accuracy (%) | 92 | N/A | 90.7 | 80–96 1 | N/A |

| Latency (ms) | ~0.5 | 0.2 | 0.3–0.8 | 1.96 | 0.1 |

| Supported channels | 32 | 8 | 8 | 1 | 32 |

| Automatic threshold | ✓ | ✗ | ✗ | ✓ | ✓ |

| Stimulation artifact dealing | ✓ | ✗ | ✓ | ✗ | ✗ |

| MUA detection | ✓ | ~ | ✓ | ✗ | ✗ |

| Sorting | ✗ | ✗ | ✗ | ✓ 2 | ✓ 2 |

| UDP spike communication | ✓ | ✗ | ✗ | ✗ | ✗ |

| Use Intan RHS | ✓ | ✓ | ✓ | ✓ 3 | ✓ 3 |

| Code availability | ✓ | ✓ | ✓ | ✗ | ✓ |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tambaro, M.; Bisio, M.; Maschietto, M.; Leparulo, A.; Vassanelli, S. FPGA Design Integration of a 32-Microelectrodes Low-Latency Spike Detector in a Commercial System for Intracortical Recordings. Digital 2021, 1, 34-53. https://doi.org/10.3390/digital1010003

Tambaro M, Bisio M, Maschietto M, Leparulo A, Vassanelli S. FPGA Design Integration of a 32-Microelectrodes Low-Latency Spike Detector in a Commercial System for Intracortical Recordings. Digital. 2021; 1(1):34-53. https://doi.org/10.3390/digital1010003

Chicago/Turabian StyleTambaro, Mattia, Marta Bisio, Marta Maschietto, Alessandro Leparulo, and Stefano Vassanelli. 2021. "FPGA Design Integration of a 32-Microelectrodes Low-Latency Spike Detector in a Commercial System for Intracortical Recordings" Digital 1, no. 1: 34-53. https://doi.org/10.3390/digital1010003

APA StyleTambaro, M., Bisio, M., Maschietto, M., Leparulo, A., & Vassanelli, S. (2021). FPGA Design Integration of a 32-Microelectrodes Low-Latency Spike Detector in a Commercial System for Intracortical Recordings. Digital, 1(1), 34-53. https://doi.org/10.3390/digital1010003