Design and Experimental Verification of Electric Vehicle Battery Charger Using Kelvin-Connected Discrete MOSFETs and IGBTs for Energy Efficiency Improvement

Abstract

1. Introduction

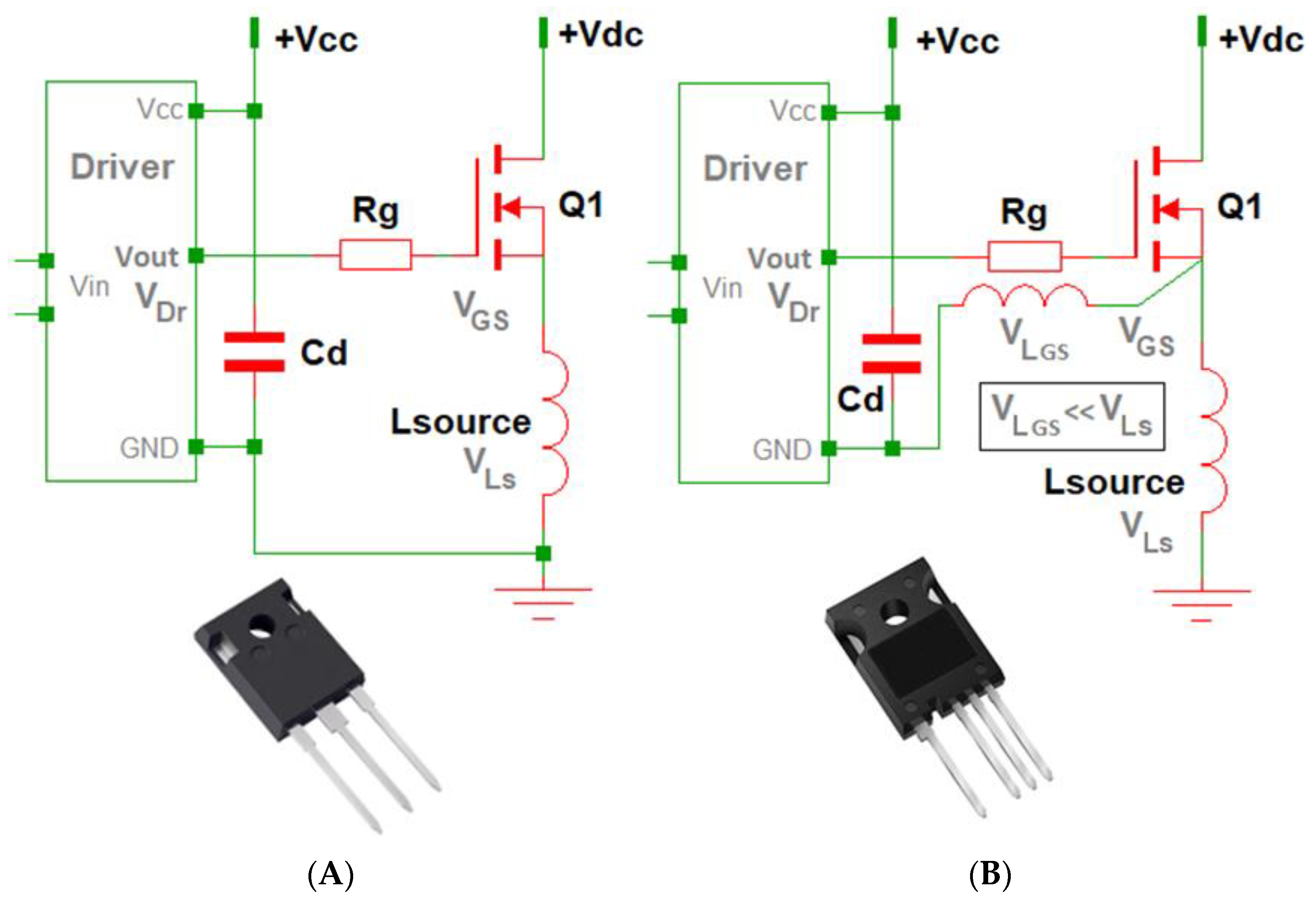

- The advantages of the 4-pin discrete Kelvin-connected MOSFETs [1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18,19,20] and IGBT [21,22,23,24,25,26,27,28,29,30] are well demonstrated with models and simulations and supported with experiments. The switches were studied individually and are not associated with a specific converter topology. Therefore, their potential contribution to power loss and temperature reduction in a particular topology requires additional study.

- Most battery charger converters are based on a PFC-Boost circuit [42,43,44,45,46,47,48,49,50,51,52,53,54,55,56,57], offering a good quality/price ratio and a subsequent LLC [31,32,33,34,35,36,37,38,39,40,41] stage, which is highly efficient due to the ZVS operation. Published results suggest that further improvement could be achieved with Kelvin-connected transistors, but this requires further analytical and experimental investigation. However, no complete study has demonstrated the application of Kelvin-connected discrete IGBTs and MOSFETs in automotive battery chargers.

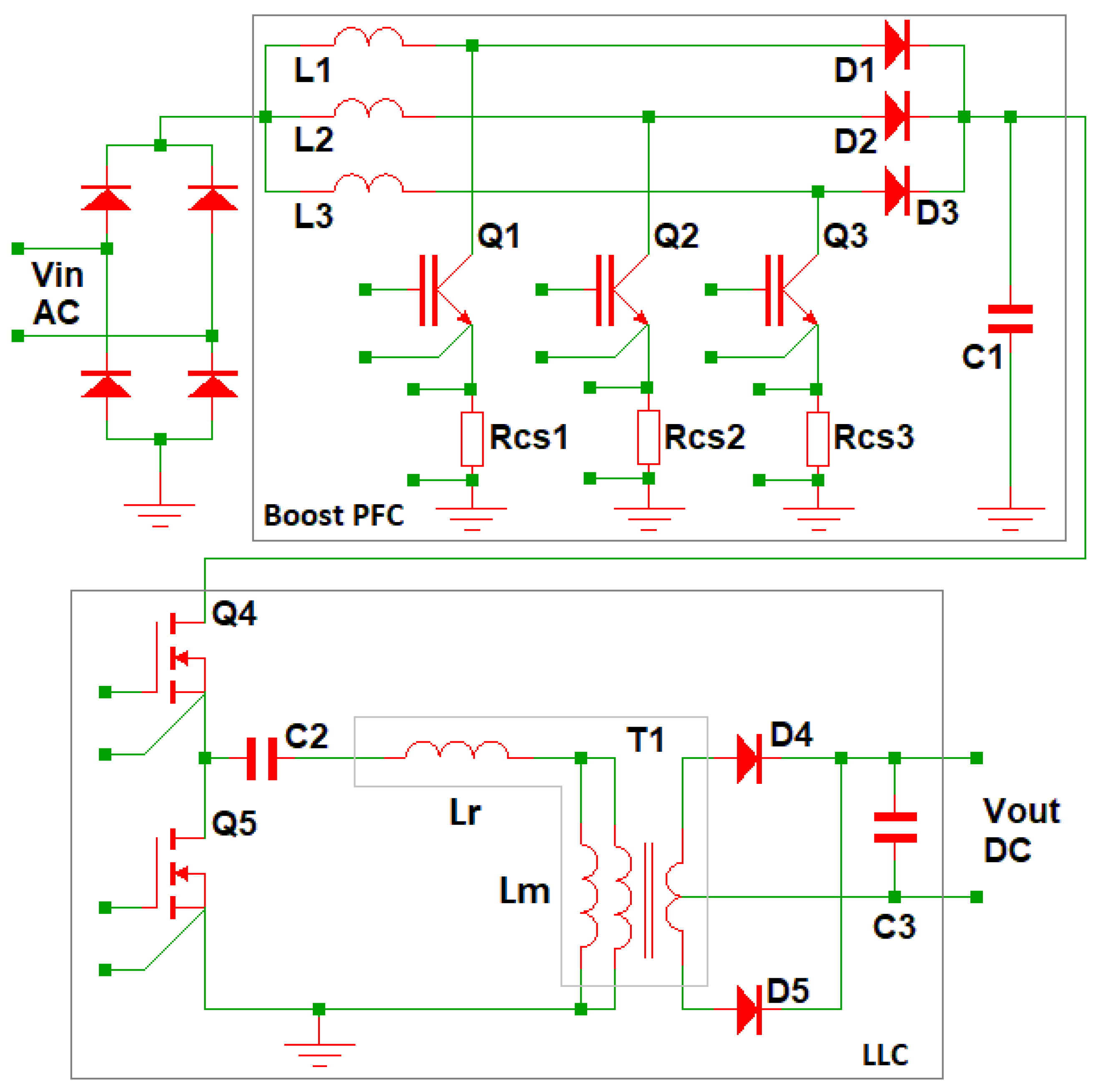

2. The Architecture of the Proposed Battery Charger

2.1. The Central Topology of the Proposed Charger

- Single-phase input rectifier (not part of this research).

- Boost-PFC converter with three channels. Channel 1: Kelvin-connected IGBT Q1, inductor L1, ultra-fast diode D1, and current sense resistor Rcs1. Channel 2: Q2, L2, D2, Rcs2. Channel 3: Q3, L3, D3, and Rcs3. The Boost capacitor C1 is common for all three parallel channels.

- LLC DC-DC half-bridge converter with Kelvin-connected MOSFETs Q4 and Q5, resonant circuit capacitor C2, transformer with integrated resonant inductor T1, output rectifier ultra-fast diodes D4 and D5, and output filter capacitor C3. The transformer integrates the resonant inductance and magnetised inductance .

2.2. Investigation of the Application of Kelvin-Connected Discrete MOSFETs and IGBTs in the Suggested Battery Charger

| Package | Equivalent Circuit | Equation | ||

|---|---|---|---|---|

|  | —total power at the junction | (20) | |

| —junction temperature | ||||

| —junction-to-case thermal resistance | ||||

| —case temperature | (21) | |||

| —case-to-heat-sink th. resistance | ||||

| —heat sink temperature | ||||

| —heat-sink-to-ambient th. resistance | (22) | |||

| —ambient temperature | ||||

| Total thermal balance | (23) | |||

| MOSFET | IGBTs | |||

|---|---|---|---|---|

| IMW65R015M2H TO-247 3-pin | IMZA65R015M2H TO-247 4-pin | STGW80H65DFB TO-247 3-pin | STGW80H65DFB-4 TO-247 4-pin | |

| Datasheet data | ||||

|

(°C/W) (datasheet) | 0.44 | 0.32 | ||

|

(°C/W) (estimated) | 1 | 1 | ||

|

(°C/W) (heat sink selected) | 1.5 | 1.5 | ||

| Calculated results according to Table 2 | ||||

| (W) | 27.5 | 18.4 | 36.4 | 27.4 |

| (°C) | 120.9 | 94.2 | 142.8 | 117.4 |

| (°C) | 81.2 | 67.6 | 94.7 | 81.2 |

3. Design of LLC Converter

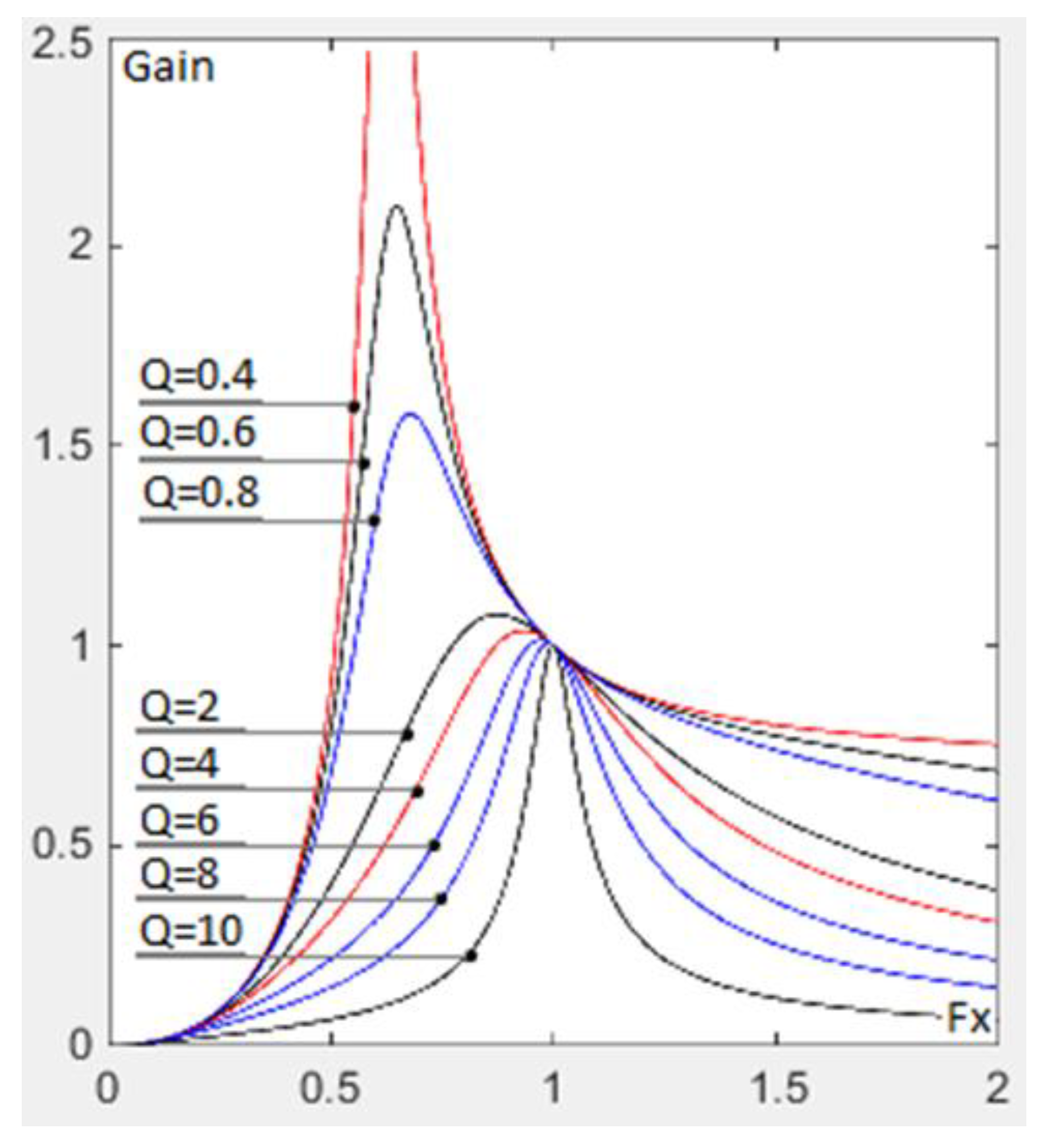

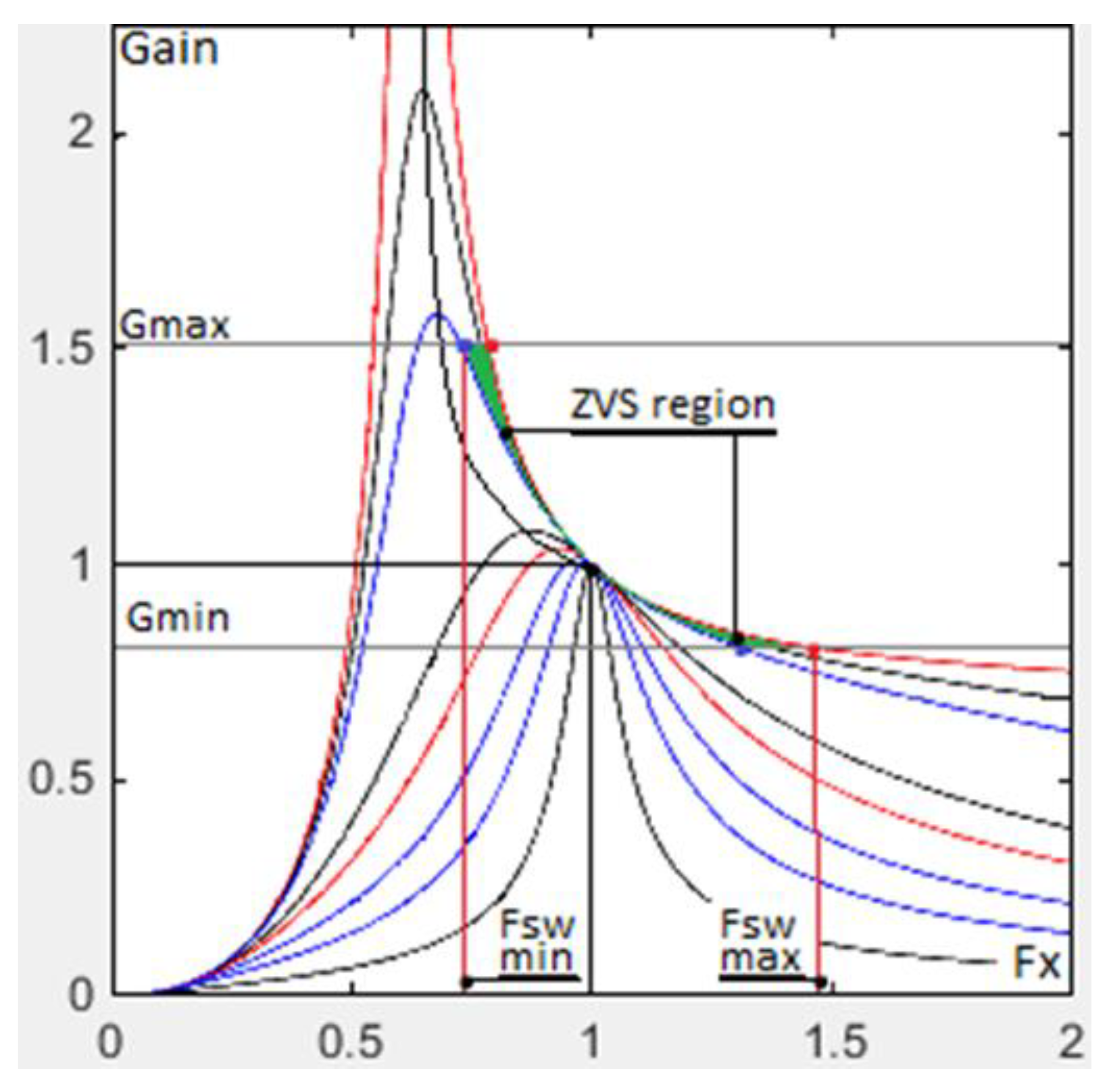

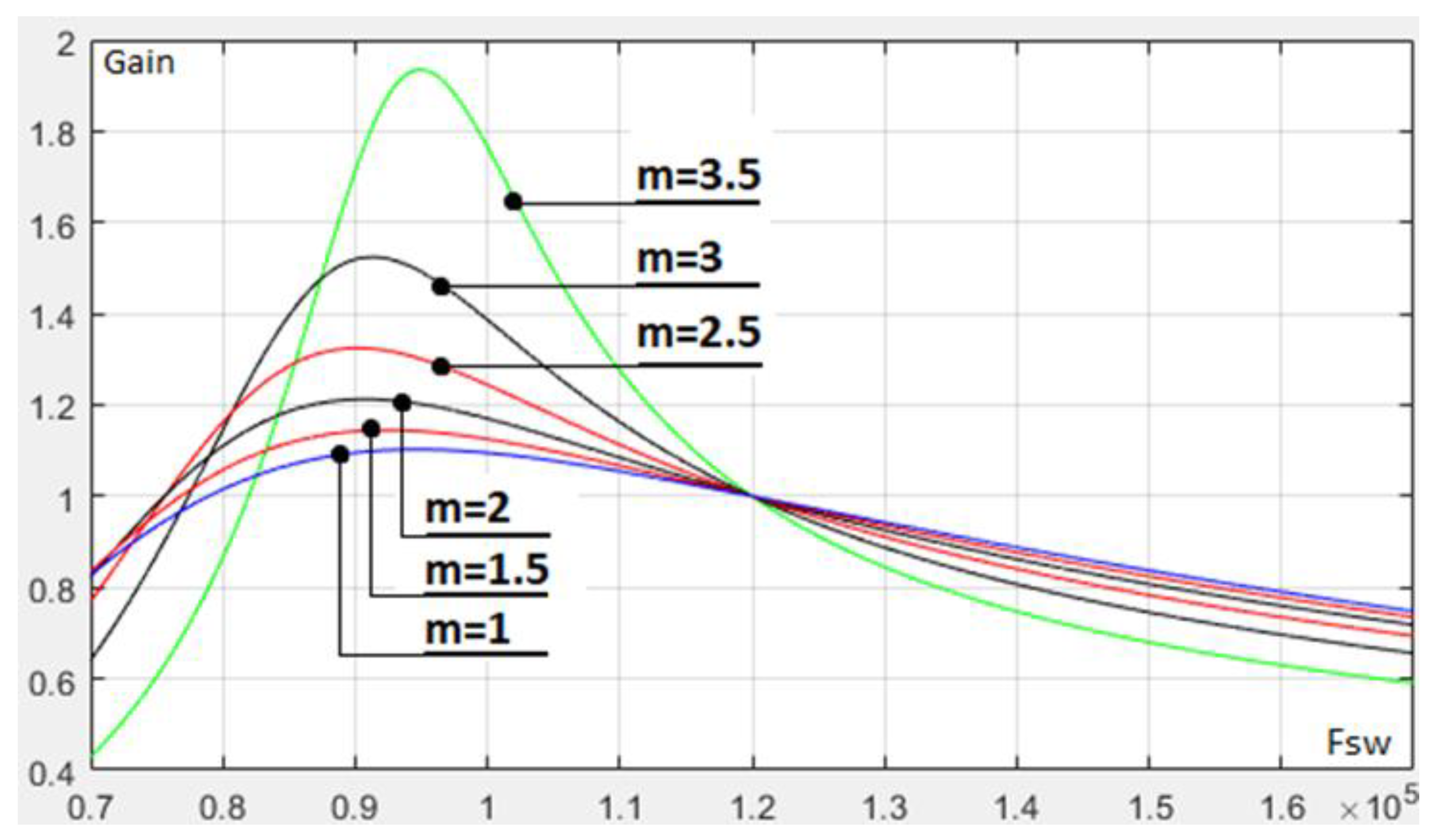

3.1. Methodology for LLC Converter Design Based on FHA

| Description | Equation | Number |

|---|---|---|

| Gain () | (24) | |

| Quality factor (Q) | (25) | |

| Normalised frequency ( ) | (26) | |

| Resonant factor () | where is the primary inductance, and is the resonant inductance | (27) |

| Reflected load resistance | (28) | |

| Resonant capacitor | (29) | |

| Resonant inductance | (30) | |

| Transient function | (31) | |

| Gain including | where ; | (32) |

| ZVS condition | (33) | |

| Required minimum gain | (34) | |

| Required maximum gain | where is the voltage drop over the diodes and | (35) |

| Input LLC power () | (36) | |

| Minimum input voltage | (37) | |

| Primary-side turns | (38) | |

| Transformer turns ratio () | (39) | |

| RMS primary side | (40) | |

| RMS current through each MOSFET | (41) |

3.2. LLC DC-DC Converter Design Case Study

4. The Design of the PFC-Boost Converter

4.1. Methodology for PFC-Boost Design

4.2. PFC-Boost Converter Design Case Study

5. Experimental Setup

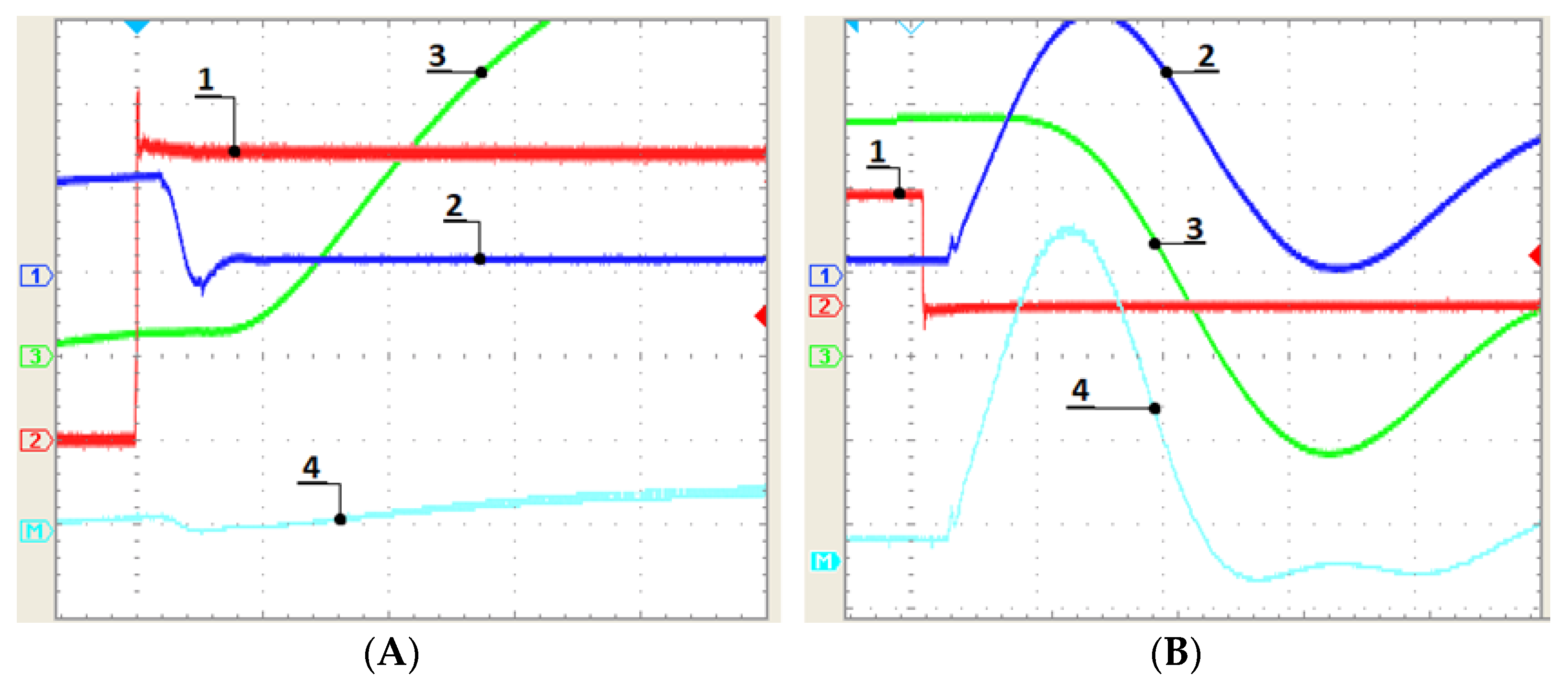

- Figure 17 shows a single channel of the interleaved PFC-Boost converter implemented with three IGBTs, as suggested in the initial design (Table 6). The gate PWM (1) controls the switch with the collector-to-emitter voltage (2) and the collector current (3). The diode conducts the current in the OFF switch state (4).

- Figure 18 shows the input PFC-Boost rectified DC voltage (1) without filtering. The PFC operates by varying the PWM (3) signal according to the input voltage variation and the collector-to-emitter voltage (2), leading to a stable output DC current (4).

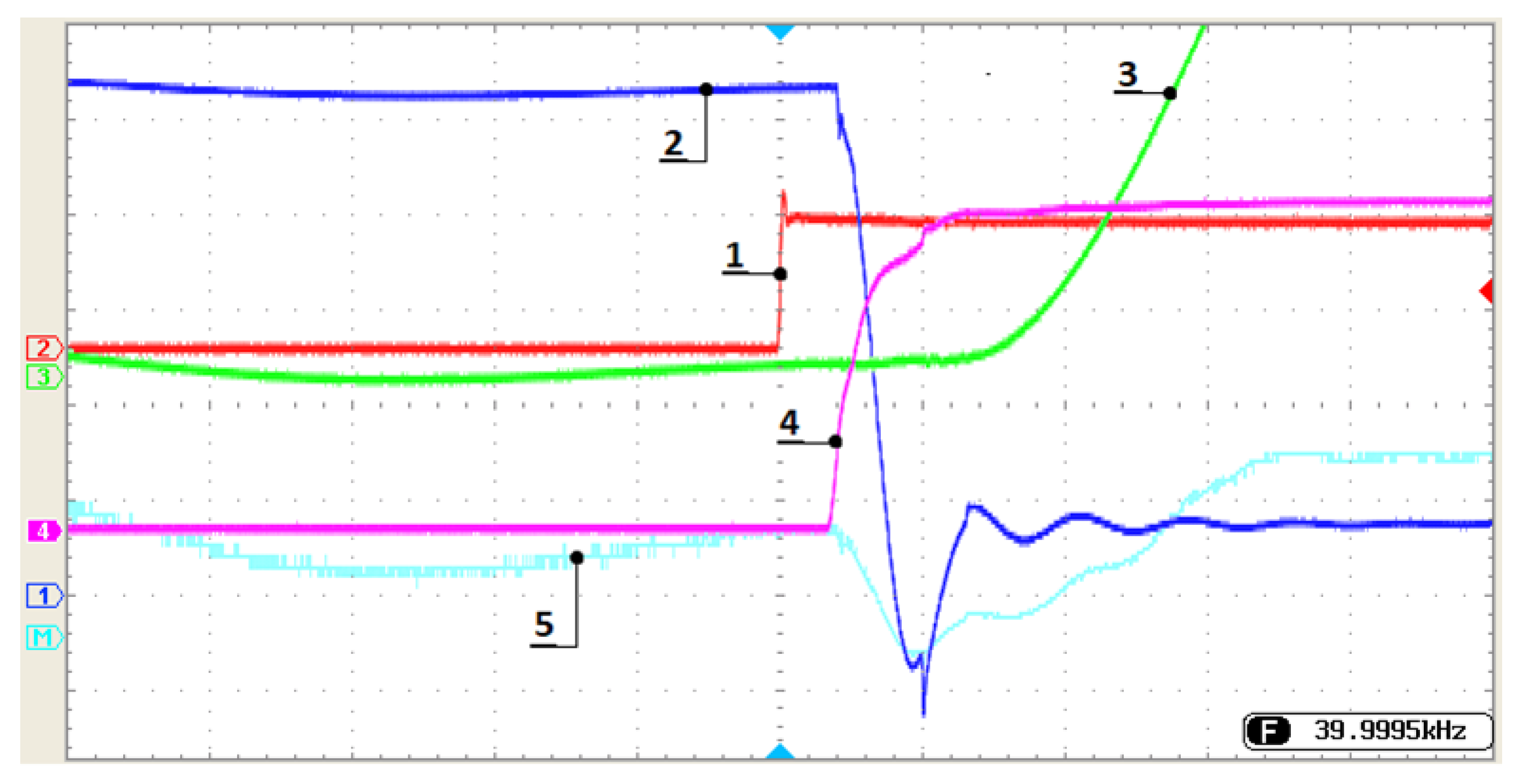

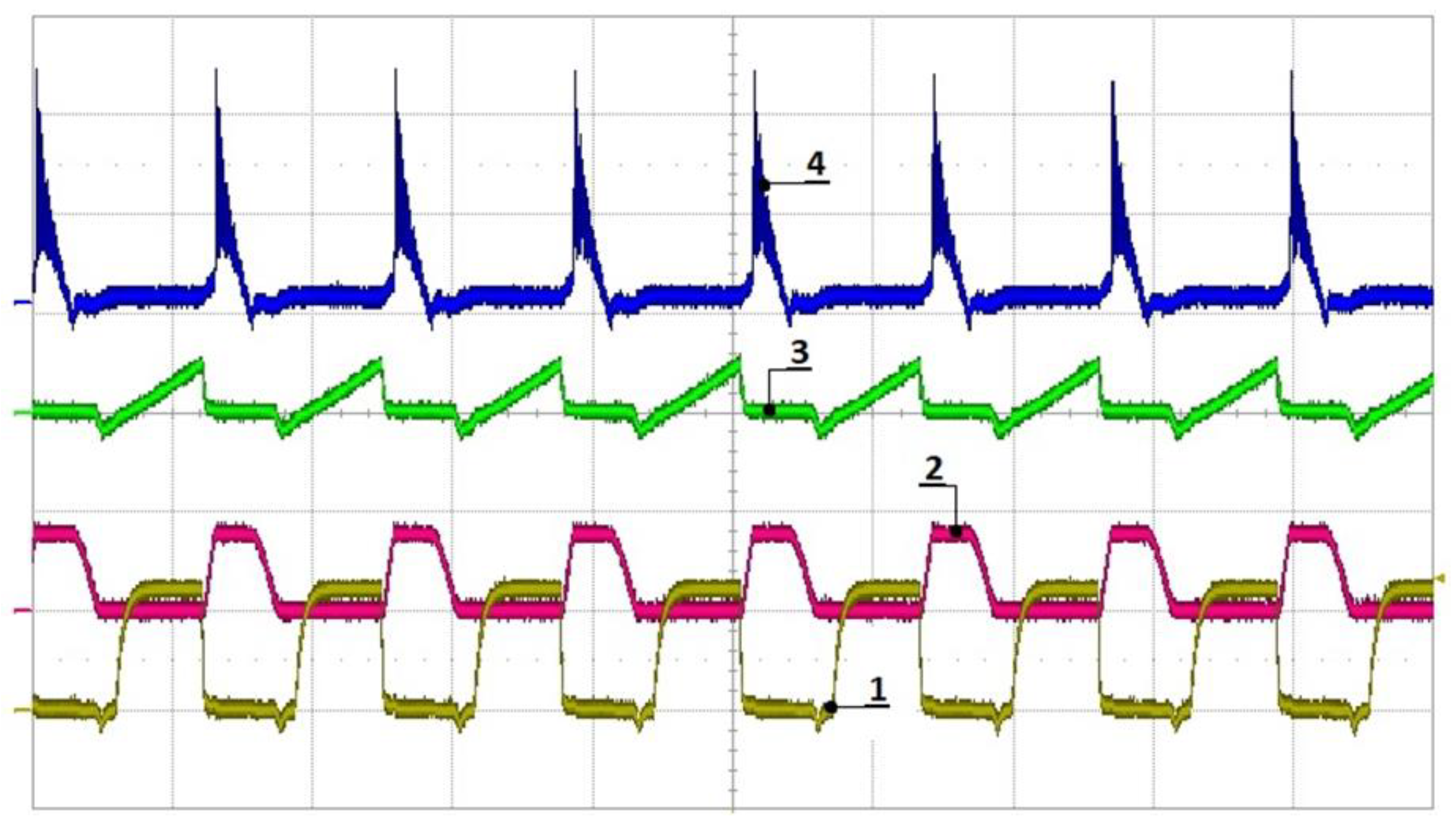

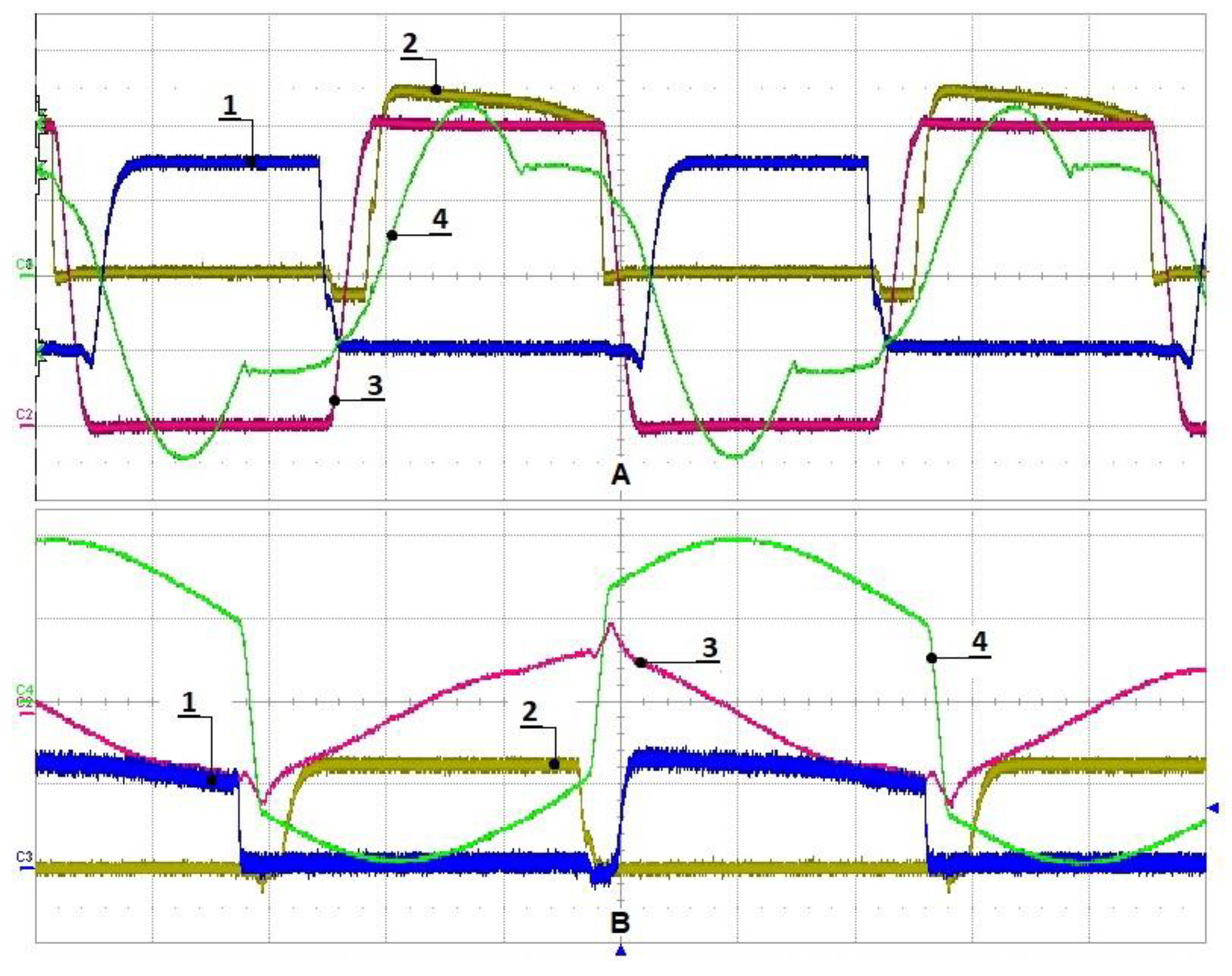

- Figure 20A shows the ZVS operation in which the voltage at the middle point of the half-bridge (3) switches in the dead time between the two transistors’ PWM (1, 2). The current through the resonant capacitor and transformer (4) is depicted under the resonant frequency under output power control. Figure 20B shows the magnetising current (3) on the primary side. Both oscillograms depict the accurate operation of the LLC converter completed with 4-pin Kelvin-connected MOSFETs.

- Figure 21A shows the ZVS in greater resolution, depicting the voltage switching at the zero point (3) between the drain-to-source voltages over the two MOSFETs (1, 2) in the half-bridge. The output DC current is shown in diagram 4. Figure 21B shows the output voltage (1) and current (2) in better resolution as part of the switching process. The output ripples are according to those accepted in the design procedure.

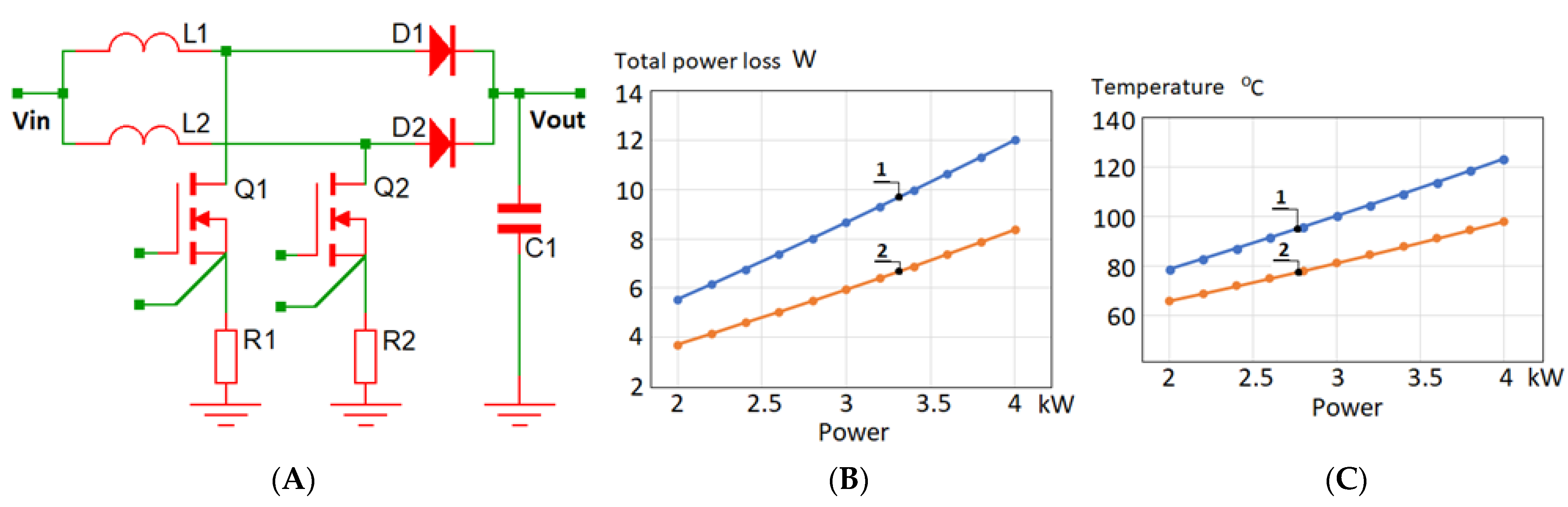

6. Results and Discussion

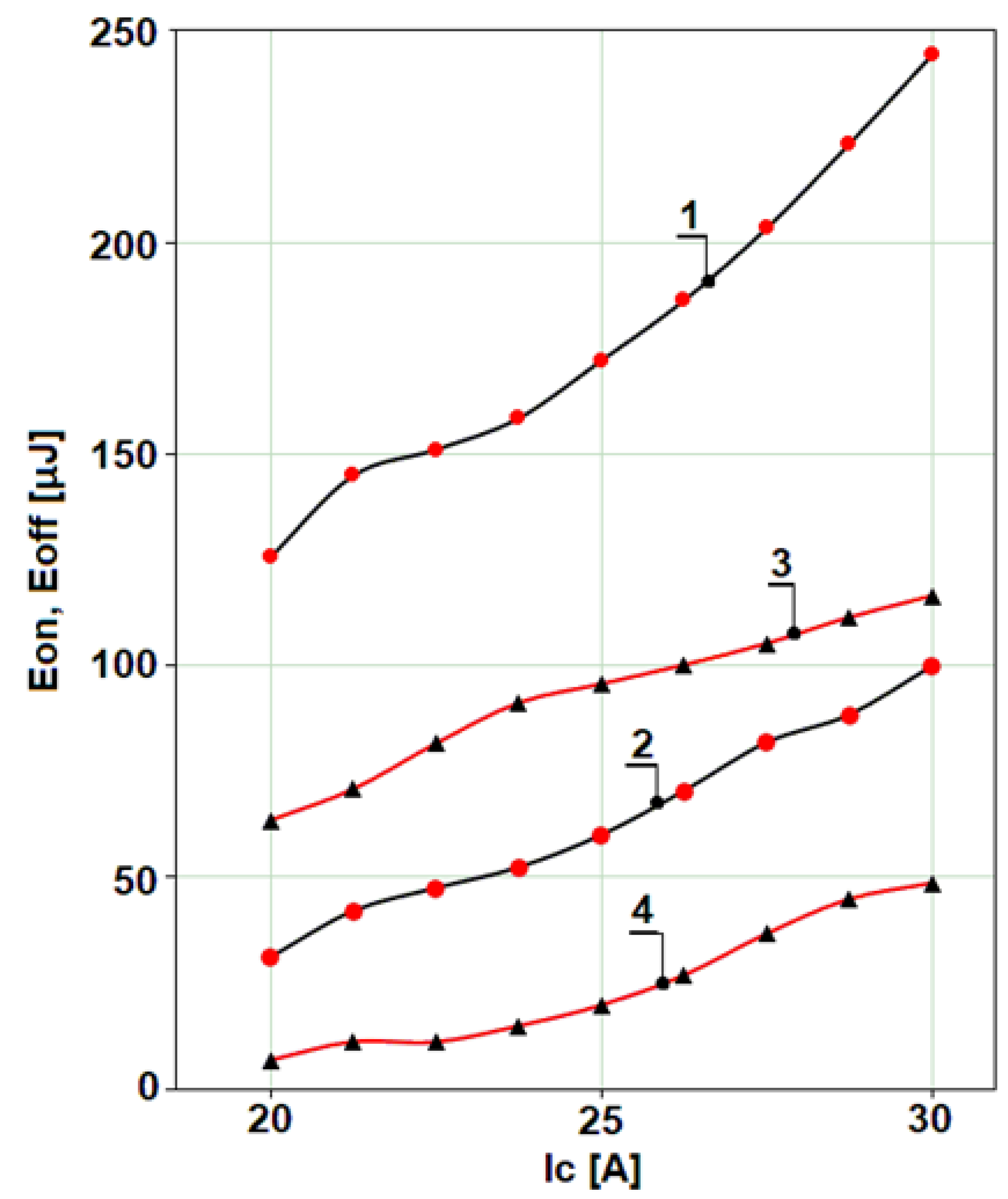

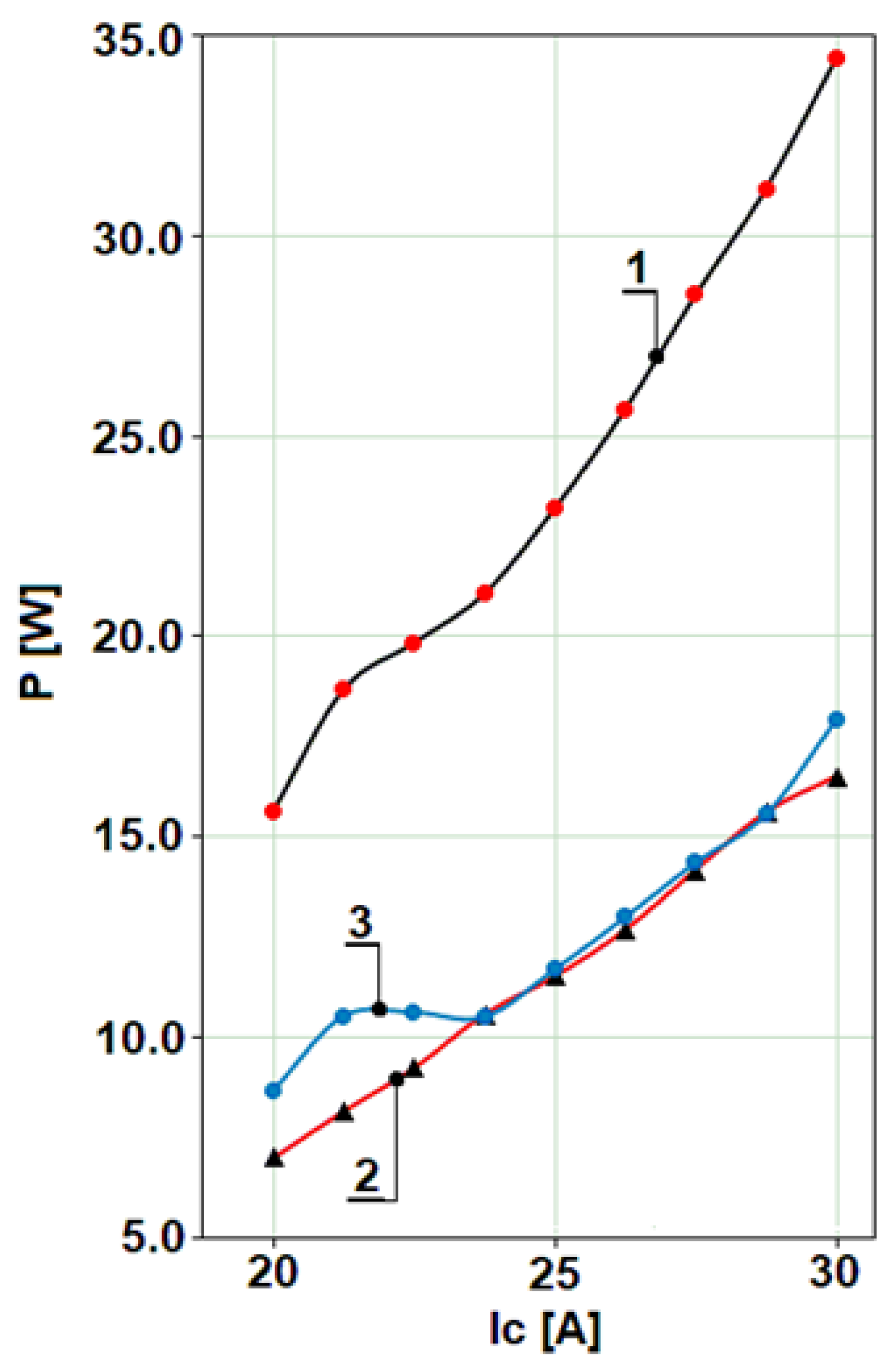

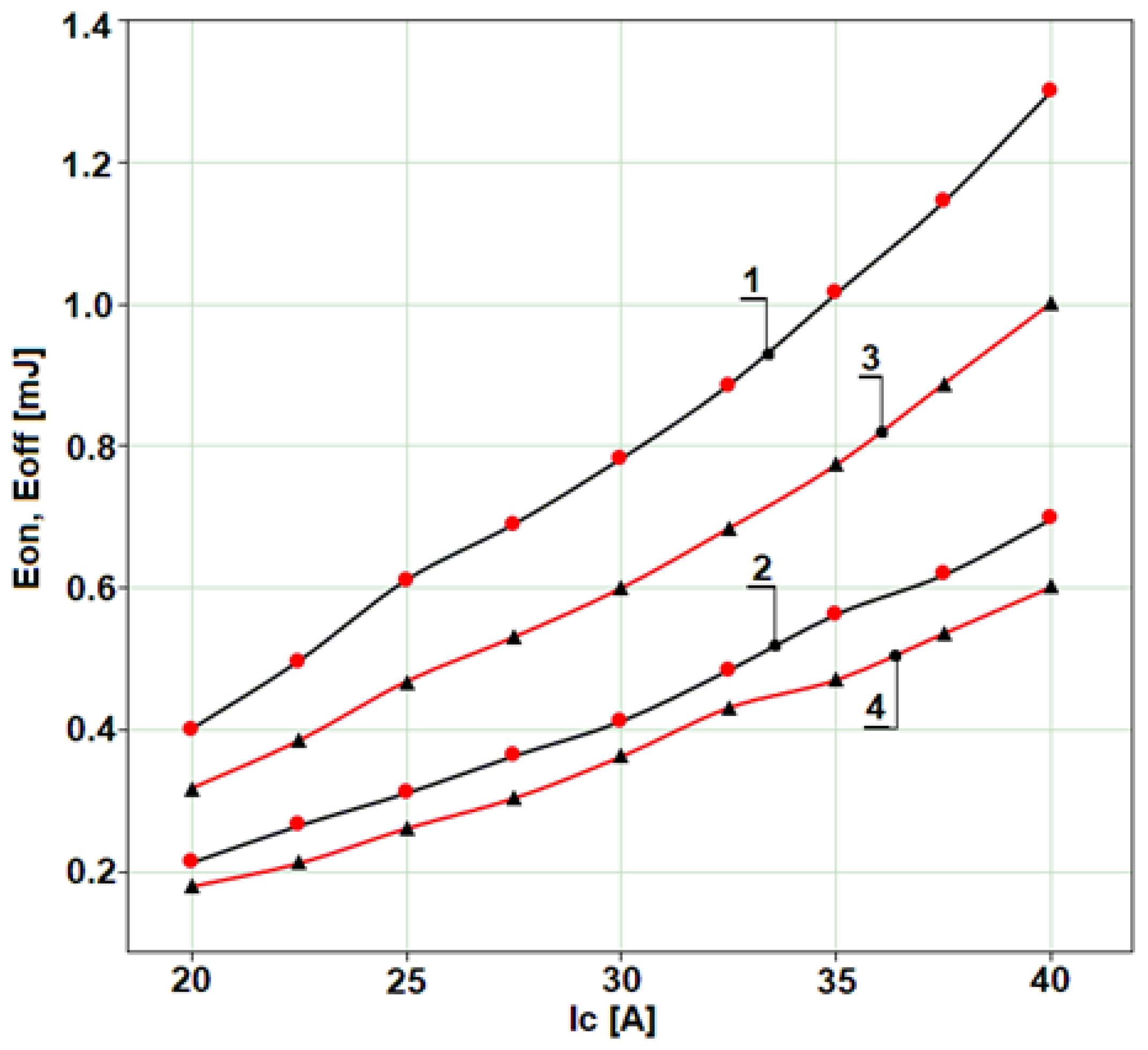

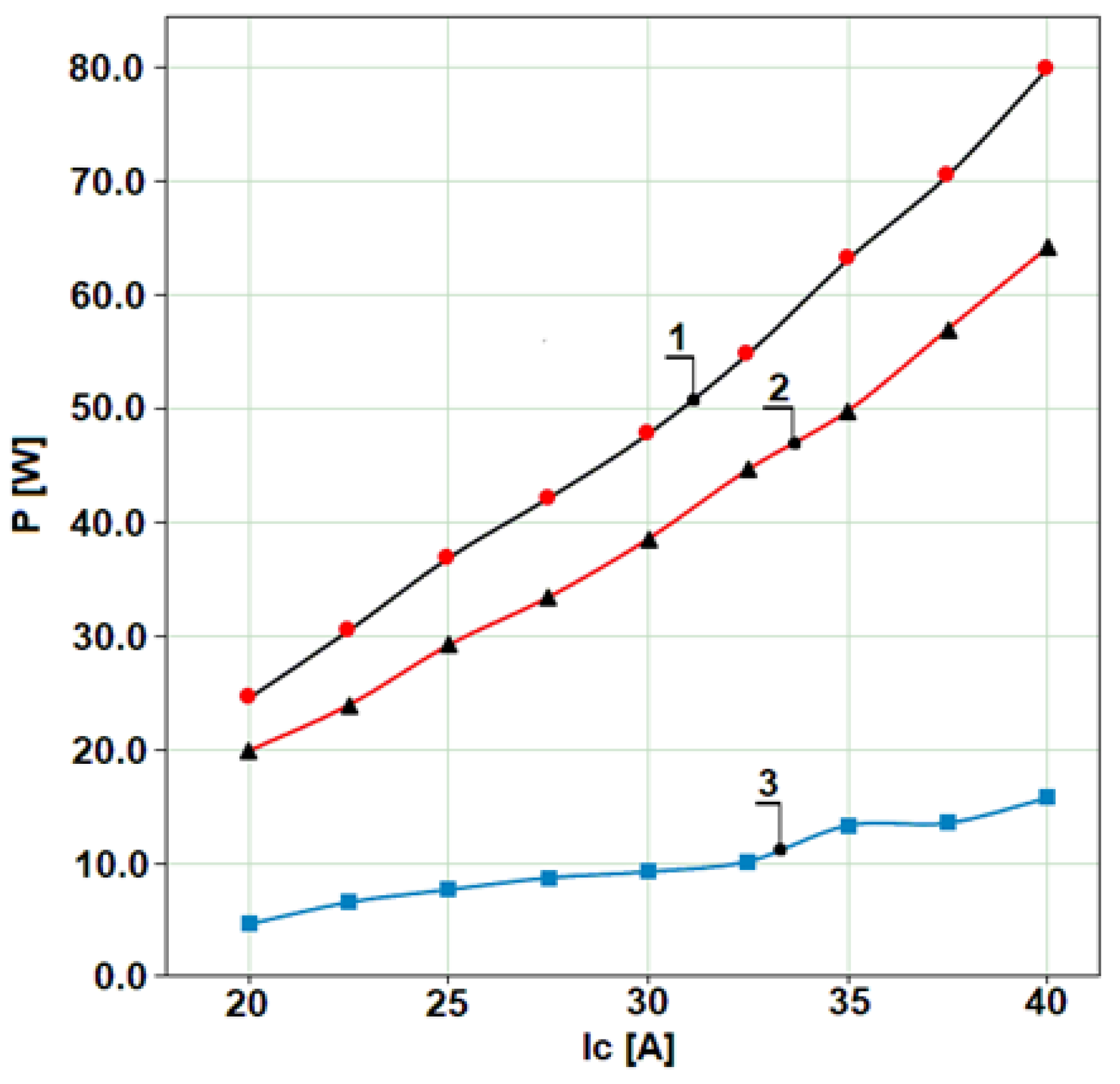

- The statistical data collected from multiple 4-pin Kelvin-connected and their 3-pin analogue TO-247 IGBTs and MOSFETs show a power loss reduction for the 4-pin package. The calculations were conducted using Equations (1)–(19) describing both packages’ power losses, and these are depicted graphically (Figure 3, Figure 4, Figure 5 and Figure 6) in the range 20–30 A, consistent with conditions in automotive onboard battery chargers. The results show that the expected power loss reduction obtained by applying Kelvin-connected transistors is between 8.6 W and 17.9 W.

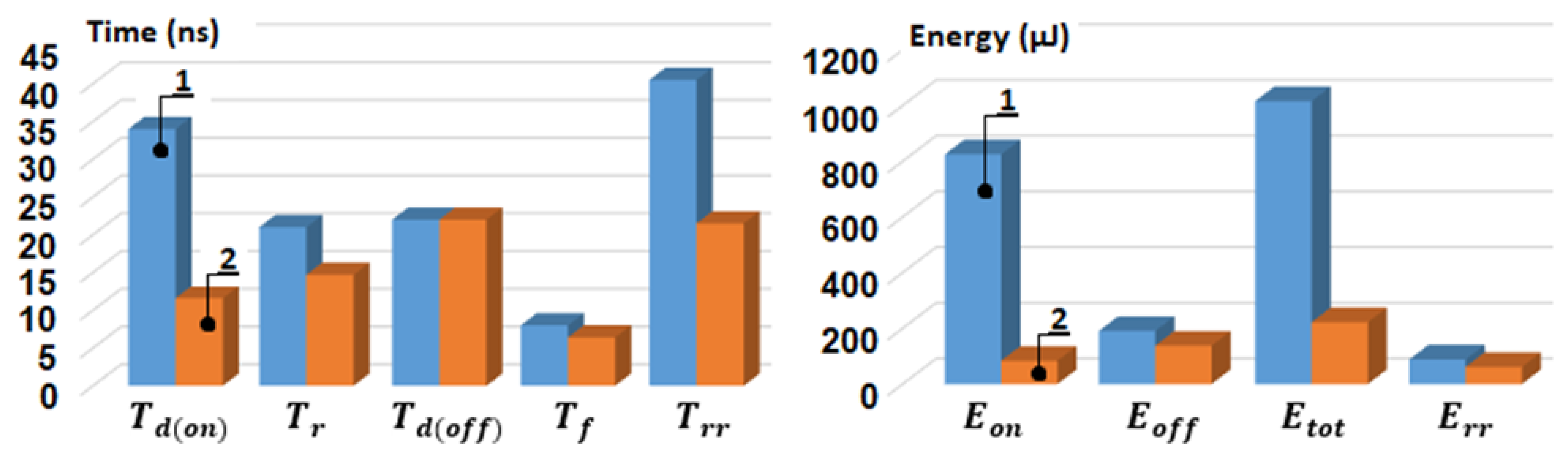

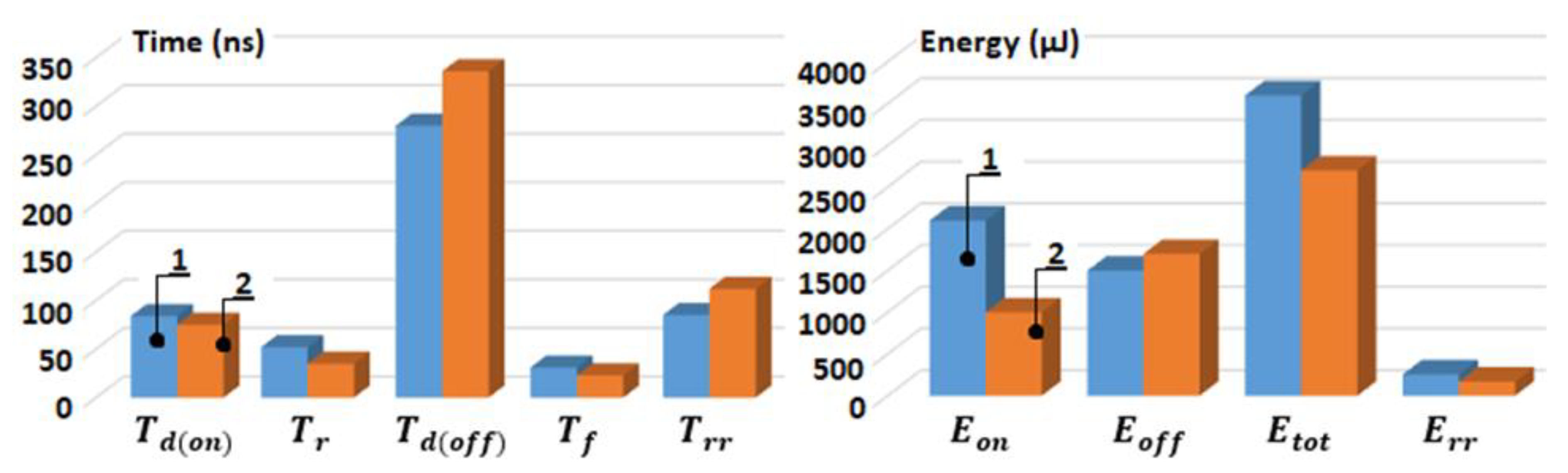

- The same calculations were applied to two specific IGBTs and MOSFETs (Table 1), including thermal models (Table 2) based on the equivalent circuits. The preliminary study shows that it can be expected that a 4-pin Kelvin-connected package offers a power loss reduction, leading to lower junction temperatures (Table 3). The results are obtained due to reduced ON and OFF switching times and, respectively, and energies, for the Kelvin-connected transistors, as depicted in Figure 7 and Figure 8.

- The 4-pin Kelvin-connected packages were successfully utilised in the design methodology of the Boost PFC (using IGBTs) and the resonant LLC converter (using MOSFETs). The case studies for both converters show that applying Kelvin-connected IGBTs to the interleaved Boost PFC reduces the switching loss. For the LLC converter, CoolSiC 4-pin MOSFETs can be recommended. The experimental study shows the stable operation of the Boost-PFC (Figure 17 and Figure 18) and LLC converters (Figure 20 and Figure 21).

- The experimental study confirms the analytical results, showing a total power loss reduction of 26.63 W, or 8.9 W per transistor, for the three interleaved IGBTs in the Boost-PFC converter. The power loss reduction and efficiency improvement, experimentally depicted in Figure 23 and Figure 24, match the preliminary results presented in Section 2 and shown in Figure 3, Figure 4, Figure 5 and Figure 6.

- Due to the power loss reduction, the heat sink temperature decreases proportionally from 101.2 °C to 85.6 °C, as the infrared images in Figure 22 show. Further temperature reductions, potentially leading to heat sink minimisation and power density improvement, could be achieved by applying SiC 4-pin MOSFET to the Boost-PFC converter (Figure 23 and Figure 24).

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Appendix A

| Infineon [60] | ON Semiconductor [61] | ST Microelectronics [62] |

|---|---|---|

| IPZA65R029CFD7; IPZA60R024P7 | FCH023N65S3L4 | stw48n60m2-4; stw56n60m2-4 |

| IPZA60R016CM8; IPZ65R019C7 | FCH041N65EFL4 | stw56n65m2-4; stw57n65m5-4 |

| IPZ60R017C7; IMZA65R030M1H | NTH4L027N65S3F | stw65n023m9-4; stw68n60m6-4 |

| IMZA65R027M1H; IMZA65R027M1H | NTH4L040N65S3F | stw70n60dm6-4; stw70n60m2-4 |

| IMZA65R020M2H; IMZA65R015M2H | NVH4L040N65S3F | stw75n60m6-4; stw75n65dm6-4 |

| Infineon [60] | ON Semiconductor [61] | ST Microelectronics [62] |

|---|---|---|

| IGZ50N65H5; IGZ75N65H5; IGZ100N65H5 IKZ50N65EH5; IKZ75N65EH5; IKZ75N65ES5 IKZA50N65EH7; IKZA75N65EH7; IKZA100N65EH7 | FGH4L50T65MQDC50 FGH4L75T65MQDC50 FGH75T65SHDTL4 FGH75T65SQDNL4 FGHL50T65MQDTL4 FGHL75T65MQDTL4 | STGW50H65DFB2-4 STGW60H65DFB-4 STGW75H65DFB2-4 STGW100H65FB2-4 |

References

- Wang, Y.; Zhao, D.; Ma, X.; Chen, B.; Chen, C. Accurate model and switching characteristics of SIC MOSFET power modules with Kelvin source package. In Proceedings of the 11th International Conference on Power Electronics, Machines and Drives (PEMD 2022), Newcastle, UK, 21–23 June 2022; pp. 680–684. [Google Scholar] [CrossRef]

- Rizzo, S.A.; Salerno, N. Actual Reasons Involving Turn-Off Losses Improvement with Increasing Load and Gate Resistance in MOSFETs Enhanced with Kelvin Source. IEEE Trans. Ind. Electron. 2024, 71, 369–379. [Google Scholar] [CrossRef]

- Cherif, O.M.; Nadji, B.; Tadjer, S.A.; Bencherif, H. An Analytical Approach for Evaluating Turn-On Switching Losses in SiC MOSFET with Kelvin Pin: Concept and Implementation. IEEE Trans. Electron Devices 2024, 71, 3116–3122. [Google Scholar] [CrossRef]

- Zhang, W.; Zhang, Z.; Wang, F.; Costinett, D.; Tolbert, L.; Blalock, B. Common source inductance introduced self-turn-on in MOSFET turn-off transient. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 837–842. [Google Scholar]

- Zhang, X. Performance Evaluation of Different Freewheeling Device Implementations for SiC MOSFETs with Kelvin Source Connections. In Proceedings of the 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 29 November–2 December 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Pu, S.; Yang, F.; Zhang, N.; Vankayalapati, B.T.; Akin, B. A Comparative Study on Reliability and Ruggedness of Kelvin and Non-Kelvin Packaged SiC Mosfets. IEEE Trans. Ind. Appl. 2022, 58, 3863–3874. [Google Scholar] [CrossRef]

- Mandal, M.; Roy, S.K.; Basu, K. Analytical Switching Transient Model of TO-247-4 Packaged SiC MOSFETs and Comparison with TO-247-3 Devices. In Proceedings of the 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 9–13 October 2022; pp. 1–8. [Google Scholar] [CrossRef]

- Yang, F.; Wang, Z.; Liang, Z.; Wang, F. Electrical Performance Advancement in SiC Power Module Package Design with Kelvin Drain Connection and Low Parasitic Inductance. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 84–98. [Google Scholar] [CrossRef]

- Chang, C.-W.; Spieler, M.; Burgos, R.; El-Refaie, A.; Dong, D. A Passive Balancing Method for Dynamic Current Sharing of Paralleled SiC MOSFETs with Kelvin-Source Connection. In Proceedings of the 2024 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 11 July 2024; pp. 1589–1595. [Google Scholar]

- Ding, Y.; Mao, S.; Wang, Z.; Yang, S.; Li, W.; Zeng, K. A Review of the Crosstalk Suppression Methods for SiC MOSFETs in the Phase-leg Circuit Configuration. In Proceedings of the 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Wuhan, China, 25–27 August 2021; pp. 206–212. [Google Scholar] [CrossRef]

- Zhao, C.; Wang, L.; Zhang, F. Effect of Asymmetric Layout and Unequal Junction Temperature on Current Sharing of Paralleled SiC MOSFETs with Kelvin-Source Connection. IEEE Trans. Power Electron. 2020, 35, 7392–7404. [Google Scholar] [CrossRef]

- Xu, F.; Chen, L. Suppressing Gate Voltage Oscillation in Paralleled SiC MOSFETs for HEV/EV Traction Inverter Application. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 3548–3553. [Google Scholar] [CrossRef]

- Baker, N.; Iannuzzo, F.; Li, H. Impact of Kelvin-Source Resistors on Current Sharing and Failure Detection in Multichip Power Modules. In Proceedings of the 2018 20th European Conference on Power Electronics and Applications (EPE’18 ECCE Europe), Riga, Latvia, 17–21 September 2018; pp. P.1–P.7. [Google Scholar]

- Xie, M.; Sun, P.; Ouyang, W.; Luo, Q.; Du, X. Online Monitoring Bond Wires Fault of SiC MOSFETs with Kelvin Package Based on Turn-on Source Voltage Ringing. IEEE Trans. Ind. Electron. 2024, 71, 9767–9776. [Google Scholar] [CrossRef]

- Sun, K.; Wang, J.; Burgos, R.; Boroyevich, D. Design, Analysis, and Discussion of Short Circuit and Overload Gate-Driver Dual-Protection Scheme for 1.2-kV, 400-A SiC MOSFET Modules. IEEE Trans. Power Electron. 2020, 35, 3054–3068. [Google Scholar] [CrossRef]

- Chen, J.; Jiang, X.; Li, Z.; Yu, H.; Wang, J.; Shen, Z.J. Investigation on Effects of Thermal Stress on SiC MOSFET Degradation through Power Cycling Tests. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 1106–1110. [Google Scholar]

- Smutka, J.; Scarpa, V.; Svetlik, J.; Hajek, J. Improvement of Dynamic Characteristics of discrete 1200V SiC MOSFETs through Kelvin Source connection. PCIM Europe Digital Days 2020. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 6–18 November 2020; pp. 1–7. [Google Scholar]

- Xue, P.; Davari, P. The Trade-off of Switching Losses and EMI Generation for SiC MOSFET with Common Source and Kelvin Source Configurations. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023; pp. 1–8. [Google Scholar]

- Iwanaga, T.; Omori, H.; Sakamoto, K.; Morizane, T.; Matayoshi, H. A New Type of Kelvin-Source SiC-VMOSFET for a High-Power Single-Ended Wireless EV Charger. In Proceedings of the 2020 2nd International Conference on Electrical, Control and Instrumentation Engineering (ICECIE), Kuala Lumpur, Malaysia, 28 November 2020; pp. 1–6. [Google Scholar]

- Cacciato, M.; Giorgio, F.; Nardo, D.; Rizzo, S.A.; Salerno, N.; Scarcella, G.; Vinci, G. Analysis of the different impact of the external Gate Resistance in 3-lead and 4-lead SuperJunction MOSFETs. In Proceedings of the 2021 AEIT International Annual Conference (AEIT), Milan, Italy, 4–8 October 2021; pp. 1–6. [Google Scholar]

- Abbatelli, L.; Cacciato, M.; Paternostro, D.; Rizzo, S.A.; Scarcella, G.; Scelba, G. Performance Assessment of an Automotive-grade TO-247 IGBT copacked with SiC diode in a bidirectional buck converter. In Proceedings of the 2020 AEIT International Conference of Electrical and Electronic Technologies for Automotive (AEIT AUTOMOTIVE), Turin, Italy, 18–20 November 2020; pp. 1–5. [Google Scholar]

- Klobucar, B.; Yuan, Z. 1200V Discrete CoolSiC(TM) MOSFETs in a Comparison with the Trenchstop HighSpeed IGBTs for High-Speed Spindles and Servo Drive System. In Proceedings of the PCIM Europe Digital Days 2020; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 7–8 July 2020; pp. 1–6. [Google Scholar]

- Rizzo, S.A.; Scelba, G.; Susinni, G.; Paternostro, D.; Scollo, R. Comparison between innovative TO-247 IGBT copacked with SiC diode and SiC MOSFET in bidirectional boost converter. In Proceedings of the 2020 2nd IEEE International Conference on Industrial Electronics for Sustainable Energy Systems (IESES), Cagliari, Italy, 1–3 September 2020; pp. 359–364. [Google Scholar]

- Sobe, K.; Engl, L.; Haque, N.U. Experimental analysis of the current-carrying capacity of discrete IGBTs in TO-247-based packages. PCIM Asia 2020. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Shanghai, China, 10 May 2020; pp. 1–6. [Google Scholar]

- Crisafulli, V. A new package with kelvin source connection for increasing power density in power electronics design. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–8. [Google Scholar] [CrossRef]

- Shen, S.; Sahan, B.; Jaeger, C.; Puyadena, A.; Brodt, A.; Lenze, A.; Mueller, C.R. Higher efficiency and power density of variable speed drives with new TRENCHSTOP(TM) IGBT7. PCIM Asia 2018. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Shanghai, China, 5–7 June 2018; pp. 1–6. [Google Scholar]

- Zhu, H.; Cheng, X.; Ng, W.T.; Xu, D.; Li, X.; Xia, Y. A Self-Adaptive Measurement System for IGBT Collector Current Using Package Parasitics. IEEE Trans. Ind. Electron. 2021, 68, 7545–7555. [Google Scholar] [CrossRef]

- Chen, Y.; Meng, F.; Zhu, A.; Li, W.; He, X. Chip Metallization Aging Monitoring with Induced Voltage veE between Kelvin and Power Emitter for High Power IGBT Modules. In Proceedings of the 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2020; pp. 4012–4016. [Google Scholar] [CrossRef]

- Wu, Q.; Chen, Y.; Luo, H.; Zhang, J.; Li, W.; He, X.; Fujishima, N.; Nishio, H.; Sumida, H. Identification Method for Various Failure Modes with Shared Kelvin and Power Wires Configuration in IGBT Power Modules. In Proceedings of the 2022 International Power Electronics Conference (IPEC-Himeji 2022- ECCE Asia), Himeji, Japan, 15–19 May 2022; pp. 133–138. [Google Scholar] [CrossRef]

- Baker, N.; Dupont, L.; Beczkowski, S.M.; Iannuzzo, F. Proof-of-Concept for an On-Chip Kelvin-Emitter RTD Sensor for Junction Temperature Monitoring of IGBTs. In IEEE Transactions on Components, Packaging and Manufacturing Technology; IEEE: Piscataway, NJ, USA, 2024. [Google Scholar] [CrossRef]

- Huang, M.-S.; Hu, J.-C.; Hsu, W.-H.; Huang, C.-W.A. Three-Level LLC Resonant Converter with PFM and PWM Control for Battery Charging Application. In Proceedings of the 2023 IEEE International Future Energy Electronics Conference (IFEEC), Sydney, Australia, 20–23 November 2023; pp. 57–61. [Google Scholar] [CrossRef]

- Lin, P.; Zhu, Y.; Li, H.; Zhao, X. Design Methodology and Control Strategy of Phase shifted LLC Resonant Converter Based SiC MOSFET for Battery Charger of High-Speed Train. In Proceedings of the 2023 9th International Conference on Electrical Engineering, Control and Robotics (EECR), Wuhan, China, 24–26 February 2023; pp. 187–191. [Google Scholar] [CrossRef]

- Ditze, S.; Ehrlich, S.; Weitz, N.; Sauer, M.; Abmus, F.; Sacher, A.; Joffe, C.; Seßler, C.; Meibner, P. A High-Efficiency High-Power-Density SiC-Based Portable Charger for Electric Vehicles. Electronics 2022, 11, 1818. [Google Scholar] [CrossRef]

- Campanini, A.; Simonazzi, M.; Bosi, M.; Rossi, C. Design and Comparison between PSFB and LLC 400/48V DC/DC Stage for Onboard Battery Charger During Total and Partial CC-CV Charging Cycles. In Proceedings of the 2022 IEEE 21st Mediterranean Electrotechnical Conference (MELECON), Palermo, Italy, 14–16 June 2022; pp. 1102–1106. [Google Scholar]

- Alatai, S.; Salem, M.; Alhamrouni, I.; Ishak, D.; Bughneda, A.; Kamarol, M. Design Methodology and Analysis of Five-Level LLC Resonant Converter for Battery Chargers. Sustainability 2022, 14, 8255. [Google Scholar] [CrossRef]

- Kim, J.-Y.; Lee, B.-S.; Kwon, D.-H.; Lee, D.-W.; Kim, J.-K. Low Voltage Charging Technique for Electric Vehicles with 800 V Battery. IEEE Trans. Ind. Electron. 2020, 69, 7890–7896. [Google Scholar] [CrossRef]

- Shen, Y.; Zhao, W.; Chen, Z.; Cai, C. Full-Bridge LLC Resonant Converter with Series-Parallel Connected Transformers for Electric Vehicle Onboard Charger. IEEE Access 2018, 6, 13490–13500. [Google Scholar] [CrossRef]

- Shahzad, M.I.; Iqbal, S.; Taib, S. Interleaved LLC Converter with Cascaded Voltage-Doubler Rectifiers for Deeply Depleted PEV Battery Charging. IEEE Trans. Transp. Electrif. 2018, 4, 89–98. [Google Scholar] [CrossRef]

- Arshadi, S.A.; Ordonez, M.; Eberle, W.; Craciun, M.; Botting, C. Three-Phase LLC Battery Charger: Wide Regulation and Improved Light-Load Operation. IEEE Trans. Power Electron. 2021, 36, 1519–1531. [Google Scholar] [CrossRef]

- Tang, Y.; Kong, D.; Duan, C.; Sun, H. Optimal Design of LLC Resonant DC Transformer under Adaptive Frequency Tracking Strategy. Electronics 2020, 9, 2160. [Google Scholar] [CrossRef]

- Bae, J.; Resonance, Y. Characteristics of the LLC Resonant Half-Bridge Converter for the Rapid Charging of Personal Mobility Device Smart Batteries. Energies 2023, 16, 6538. [Google Scholar] [CrossRef]

- Ortiz-Castrillón, R.; Mejía-Ruíz, G.; Muñoz-Galeano, N.; López-Lezama, J.; Saldarriaga-Zuluaga, S. PFC Single-Phase AC/DC Boost Converters: Bridge, Semi-Bridgeless, and Bridgeless Topologies. Appl. Sci. 2021, 11, 7651. [Google Scholar] [CrossRef]

- Yeung, R.S.-C.; Fan, J.W.-T.; Chung, H.S.-H. A totem-pole PFC using hybrid pulse-width-modulation scheme. In Proceedings of the 2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017-ECCE Asia), Kaohsiung, Taiwan, 3–7 June 2017; pp. 1286–1290. [Google Scholar] [CrossRef]

- Do, N.-N.; Huang, B.-S.; Phan, N.-T.; Nguyen, T.-T.; Wu, J.-H.; Liu, Y.-C.; Chui, H.-J. Design and Implementation of a Control Method for GaN-Based Totem-Pole Boost-Type PFC Rectifier in Energy Storage Systems. Energies 2020, 13, 6297. [Google Scholar] [CrossRef]

- Kwak, B.; Kim, J. Digital Implementation Method for Synchronous PWM Control of GaN Transistor at Zero-Crossing of Totem-Pole PFC in Energy Storage Applications. Electronics 2021, 10, 30. [Google Scholar] [CrossRef]

- Qiqi, L.; Bangyin, L.; Shanxu, D. Simplified Analytical Model for Estimation of Switching Loss of Cascode GaN HEMTs in Totem-pole PFC Converters. Chin. J. Electr. Eng. 2019, 5, 1–9. [Google Scholar]

- Huang, Y.-Y.; Lai, Y.-S. Novel Efficiency Optimized Inductor Design for GaN-Based Totem-Pole PFC. In Proceedings of the 2022 IEEE 31st International Symposium on Industrial Electronics (ISIE), Anchorage, AK, USA, 1–3 June 2022; pp. 933–938. [Google Scholar] [CrossRef]

- Yu, D.; Xie, X.; Dong, H. An Error Amplifier Scheme to Reduce Compensation Capacitor for Boost PFC Converter. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 2816–2825. [Google Scholar] [CrossRef]

- Yao, K.; Liu, J.; Zhu, D.; Jin, Z. High Power Factor CRM Boost PFC Converter with Optimum Switching Frequency Variation Range Control Based on Variable Inductor. IEEE Trans. Power Electron. 2021, 36, 11019–11025. [Google Scholar] [CrossRef]

- Bendicks, A.; Peters, A.; Frei, S. FPGA-Based Active Cancellation of the EMI of a Boost Power Factor Correction (PFC) by Injecting Modulated Sine Waves. IEEE Lett. Electromagn. Compat. Pract. Appl. 2021, 3, 11–14. [Google Scholar] [CrossRef]

- Campos, H.M.V.D.B.; Soares, J.W.M.; Badin, A.A.; Cortez, D.F. Single-Phase Hybrid Switched-Capacitor PFC Boost Rectifier with Low Voltage Gain. IEEE Trans. Power Electron. 2023, 38, 968–976. [Google Scholar] [CrossRef]

- Babaei, A.; Kaffashan, I.; Abrishamifar, A. An Improved Threefold Interleaved PFC Circuit with Better Voltage Profile and Optimising Current-Sharing Method. IEEE Can. J. Electr. Comput. Eng. 2021, 44, 253–260. [Google Scholar] [CrossRef]

- Soares, J.W.M.; Badin, A.A. An Interleaved PFC Boost Converter with Soft Commutations and Voltage Follower Characteristics. IEEE Trans. Ind. Electron. 2022, 69, 6732–6740. [Google Scholar] [CrossRef]

- Gangavarapu, S.; Rathore, A.K. Analysis and Design of Interleaved DCM Buck–Boost Derived Three-Phase PFC Converter for MEA. IEEE Trans. Transp. Electrif. 2021, 7, 1954–1963. [Google Scholar] [CrossRef]

- Duan, M.; Sun, D.; Duan, J.; Sun, L.; Liu, Y. Interleaved Modulation Scheme with Optimised Phase Shifting for Double-Switch Buck-Boost Converter. IEEE Access 2021, 9, 55422–55435. [Google Scholar] [CrossRef]

- Yang, F.; Li, C.; Cao, Y.; Yao, K. Two-Phase Interleaved Boost PFC Converter with Coupled Inductor Under Single-Phase Operation. IEEE Trans. Power Electron. 2020, 35, 169–184. [Google Scholar] [CrossRef]

- Bousungnoen, P.; Pao-La-Or, P. A Single-Phase Integrated Battery Charger Simulation Compare Onboard Battery Charger with PFC Boost Converter and PSFB DC-DC Converter. In Proceedings of the 2023 International Electrical Engineering Congress (iEECON), Krabi, Thailand, 8–10 March 2023; pp. 163–168. [Google Scholar] [CrossRef]

- Mamun, K.A.; Islam, F.R.; Haque, R.; Chand, A.A.; Prasad, K.A.; Goundar, K.K.; Prakash, K.; Maharaj, S. Systematic Modeling and Analysis of Onboard Vehicle Integrated Novel Hybrid Renewable Energy System with Storage for Electric Vehicles. Sustainability 2022, 14, 2538. [Google Scholar] [CrossRef]

- Dimitrov, B.S. A Battery Cell Equalisation System Based on a Supercapacitors Tank and DC-DC Converters for Automotive Applications. World Electr. Veh. J. 2023, 14, 185. [Google Scholar] [CrossRef]

- Available online: https://www.infineon.com/ (accessed on 22 September 2024).

- Available online: https://www.onsemi.com/ (accessed on 22 September 2024).

- Available online: https://www.st.com/ (accessed on 22 September 2024).

| MOSFET | IGBTs | |||

|---|---|---|---|---|

| IMW65R015M2H TO-247 3-pin | IMZA65R015M2H TO-247 4-pin | STGW80H65DFB TO-247 3-pin | STGW80H65DFB-4 TO-247 4-pin | |

| Times (ns) | ||||

| 34 | 11.6 | 84 | 75 | |

| 21 | 14.7 | 52 | 35 | |

| 22 | 22 | 280 | 336 | |

| 8 | 6.4 | 31 | 23 | |

| 40.5 | 21.5 | 85 | 112 | |

| Energies (µJ) | ||||

| 825 | 84 | 2100 | 1000 | |

| 191 | 138 | 1500 | 1700 | |

| 1016 | 222 | 3600 | 2700 | |

| 88.4 | 61.6 | 257 | 170 | |

| Design Specification | |||

|---|---|---|---|

| Input Parameters | Output Parameters | ||

| Minimum voltage | Minimum voltage | ||

| Nominal voltage | Nominal voltage | ||

| Maximum voltage | Maximum voltage | ||

| Estimated efficiency | 0.96 | Output power | |

| Minimum switching frequency | Nominal output current | ||

| Resonant frequency | |||

| Maximum switching frequency | |||

| Design parameters | |||

| Input power | Magnetising inductance | ||

| Transformer turns ratio | 0.5 | Resonant inductance | |

| Minimum gain | 0.64 | Resonant capacitance | |

| Maximum gain | 1.93 | Nominal resistance | |

| Quality factor | 0.88 | Peak primary-side current | |

| Resonant current | Maximum output current | ||

| Magnetising current at minimum switching frequency | Secondary half-wave current | ||

| Magnetising current at nominal switching frequency | Energy accumulated in parasitic capacitors in both transistors | ||

| Magnetising current at maximum switching frequency | Dead time | ||

| Selected semiconductors | |||

| Primary-side transistors: IMZA65R015M2H (CoolSiC™ 4-pin Kelvin-connected MOSFET) | |||

| Secondary-side rectifiers: VS-E5PH7506LHN3 | |||

| Design Specification | |||

|---|---|---|---|

| Input Parameters | Output Parameters | ||

| Minimum AC voltage | Nominal output DC voltage | ||

| Maximum AC voltage | Minimum output DC voltage | ||

| Line frequency | Output power | ||

| Number of channels | 3 | Output voltage ripples | |

| Switching frequency | |||

| Efficiency (estimated) | |||

| Design parameters | |||

| Input power | Duty cycle | 0.399 | |

| Nominal output DC current | Inductor | ||

| Current per channel | Inductor peak current at line brownout 160 V | ||

| Power per channel | Output capacitor | ||

| Maximum switch current | |||

| Selected semiconductors | |||

| IGBT: STGW80H65DFB-4 | |||

| Fast-recovery diode: VS-E5PH7506LHN3 | |||

| 3-pin IGBTs | 4-pin IGBTs | |||||

|---|---|---|---|---|---|---|

| Total Loss for Three Interleaved PFC IGBTs (W) | Total Loss per IGBT (W) | Heat Sink/Junction Temperatures (°C) | Total Loss for Three Interleaved PFC IGBTs (W) | Loss per IGBT (W) | Heat Sink/Junction Temperatures (°C) | |

| Calculated | 93.7 | 31.24 | 118.1/ 128.1 | 66.6 | 22.2 | 95.61/ 102.73 |

| ||||||

| Measured | 75 | 25 | 101.2/ 95.6 | 48.4 | 16.1 | 85.6/ 78.5 |

| ||||||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dimitrov, B.; McMahon, R. Design and Experimental Verification of Electric Vehicle Battery Charger Using Kelvin-Connected Discrete MOSFETs and IGBTs for Energy Efficiency Improvement. Electricity 2024, 5, 684-711. https://doi.org/10.3390/electricity5040034

Dimitrov B, McMahon R. Design and Experimental Verification of Electric Vehicle Battery Charger Using Kelvin-Connected Discrete MOSFETs and IGBTs for Energy Efficiency Improvement. Electricity. 2024; 5(4):684-711. https://doi.org/10.3390/electricity5040034

Chicago/Turabian StyleDimitrov, Borislav, and Richard McMahon. 2024. "Design and Experimental Verification of Electric Vehicle Battery Charger Using Kelvin-Connected Discrete MOSFETs and IGBTs for Energy Efficiency Improvement" Electricity 5, no. 4: 684-711. https://doi.org/10.3390/electricity5040034

APA StyleDimitrov, B., & McMahon, R. (2024). Design and Experimental Verification of Electric Vehicle Battery Charger Using Kelvin-Connected Discrete MOSFETs and IGBTs for Energy Efficiency Improvement. Electricity, 5(4), 684-711. https://doi.org/10.3390/electricity5040034