Comparison of Reactive Power Compensation Methods in an Industrial Electrical System with Power Quality Problems

Abstract

1. Introduction

- This study compares technical and economic aspects of concentrated and distributed power factor compensation in IESs.

- This study considers the mitigation of harmonics in IESs affected by power quality problems.

- This evaluation incorporates an energy efficiency approach to analyze the impact on electrical losses with the location of power factor compensators in an IES.

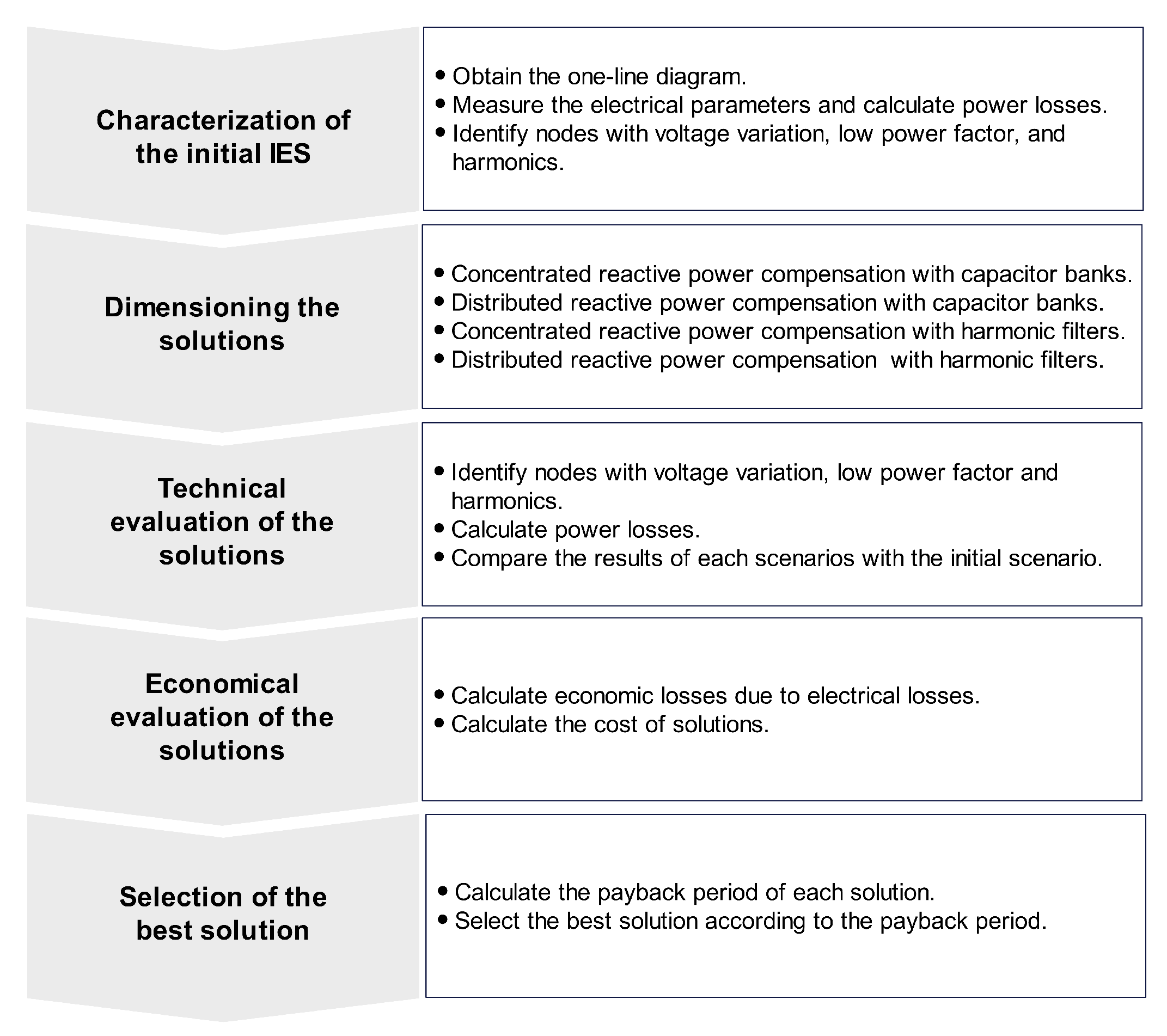

2. Materials and Methods

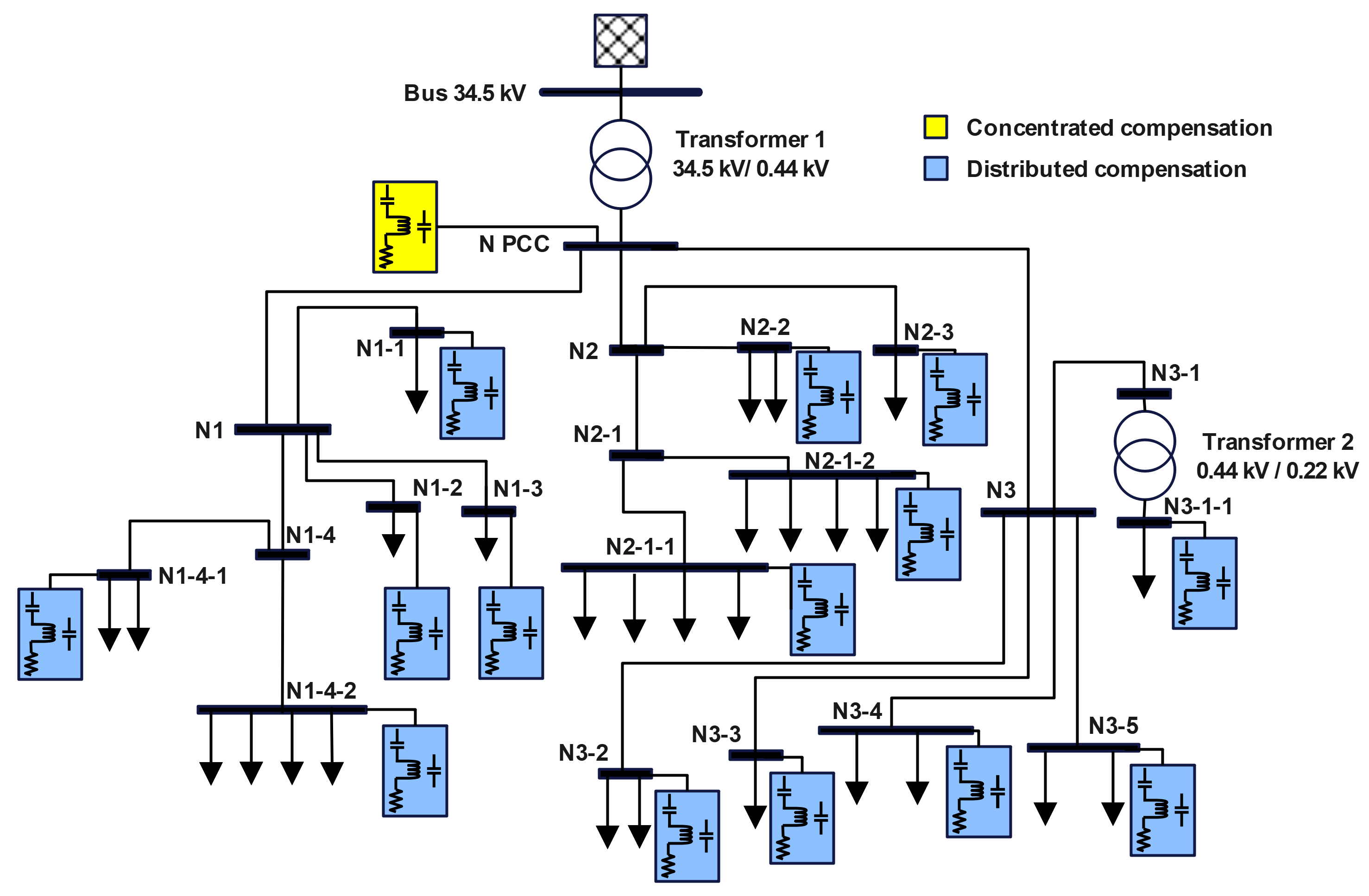

2.1. Characterization of the IES

- The voltage variation is calculated with the NEPLAN software.

- The load factor is calculated as the ratio between the measured power and the nominal power of the transformer in the PCC.

- The PF is calculated with the NEPLAN software.

- The total harmonic distortion of voltage (THDV) is calculated with the NEPLAN software.

- The electrical losses due to harmonics are calculated as the difference between the total and the fundamental power.

- The total losses are calculated as the sum of harmonic losses and electrical losses.

2.2. Dimension of the Solutions

- Solution 1 (S1): concentrated reactive power compensation with capacitor banks.

- Solution 2 (S2): distributed reactive power compensation with capacitor banks.

- Solution 3 (S3): concentrated reactive power compensation with harmonic filters.

- Solution 4 (S4): distributed reactive power compensation with harmonic filters.

2.3. Evaluation of Solutions

- Verify that in the PCC, the PF complies with the provisions of CREG resolution 015 of 2018 [6].

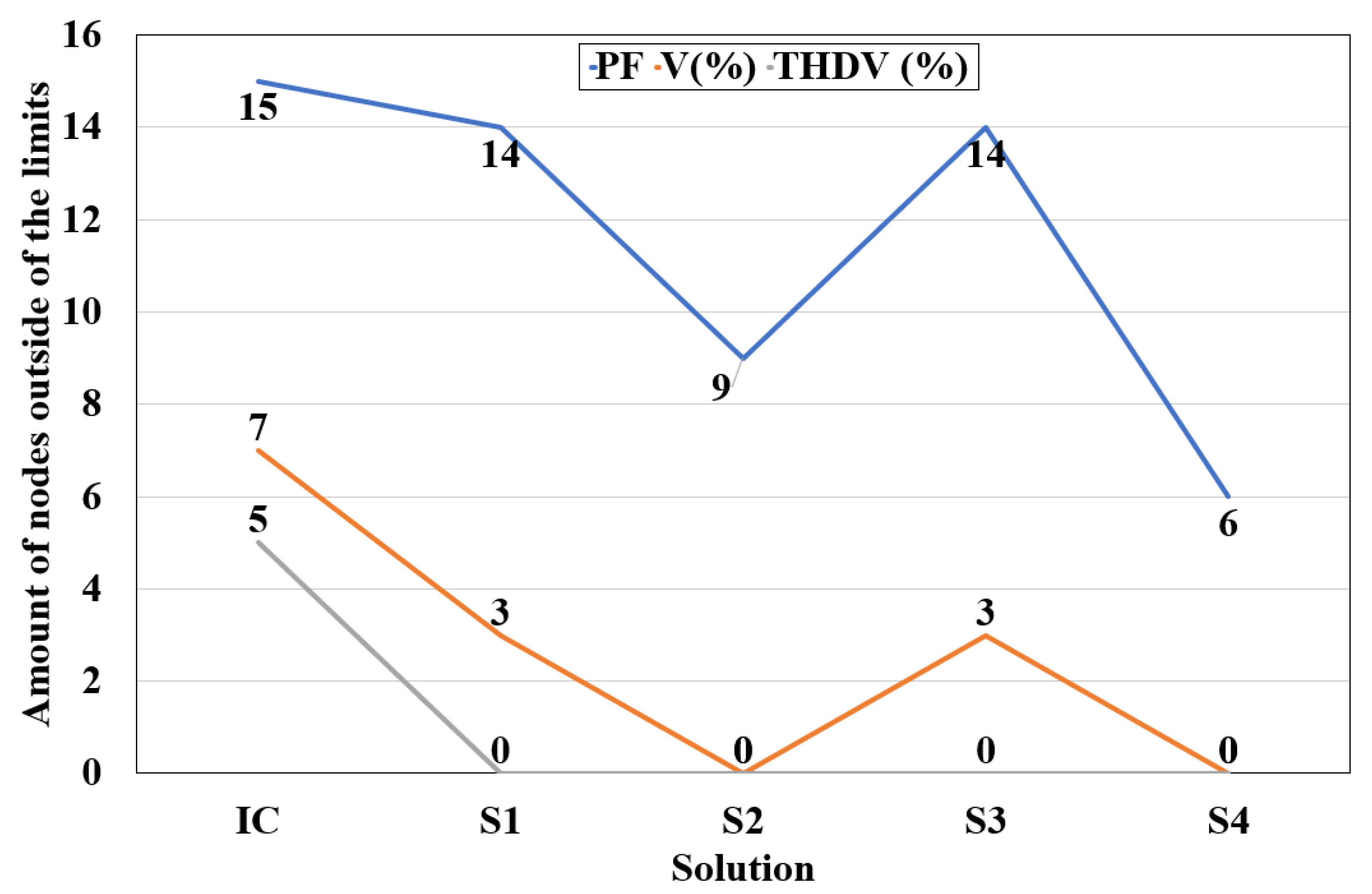

- Quantify the number of nodes (PCC and distribution) with PF outside the range established in CREG resolution 015 of 2018 [6].

- Quantify the number of nodes (PCC and distribution) with voltage outside the range established by the NTC 1340 standard [46].

- Quantify the number of nodes (PCC and distribution) with harmonics outside the range established by the IEEE 519 standard [40].

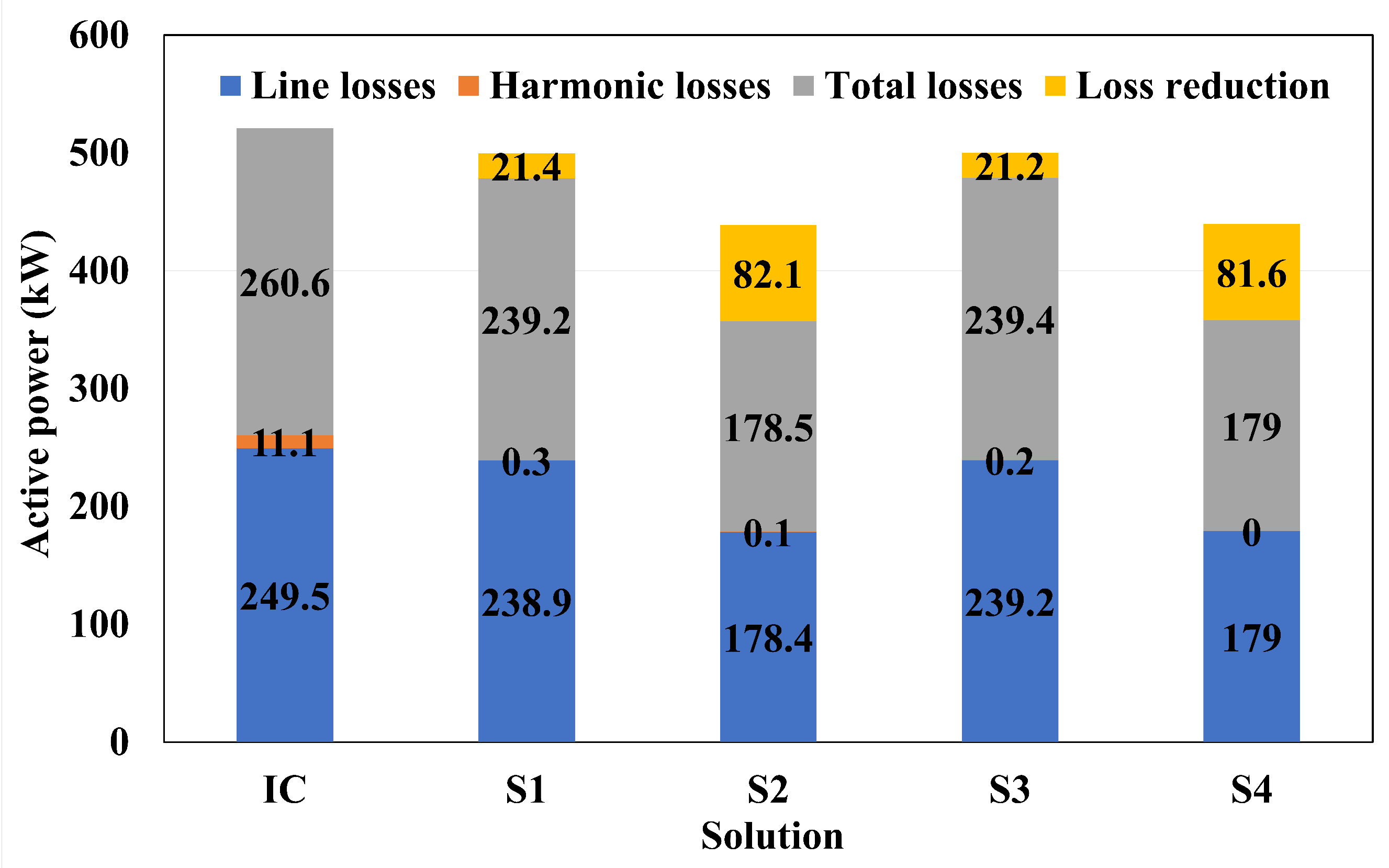

- Calculation of harmonic losses in the lines and total electrical losses in the IES.

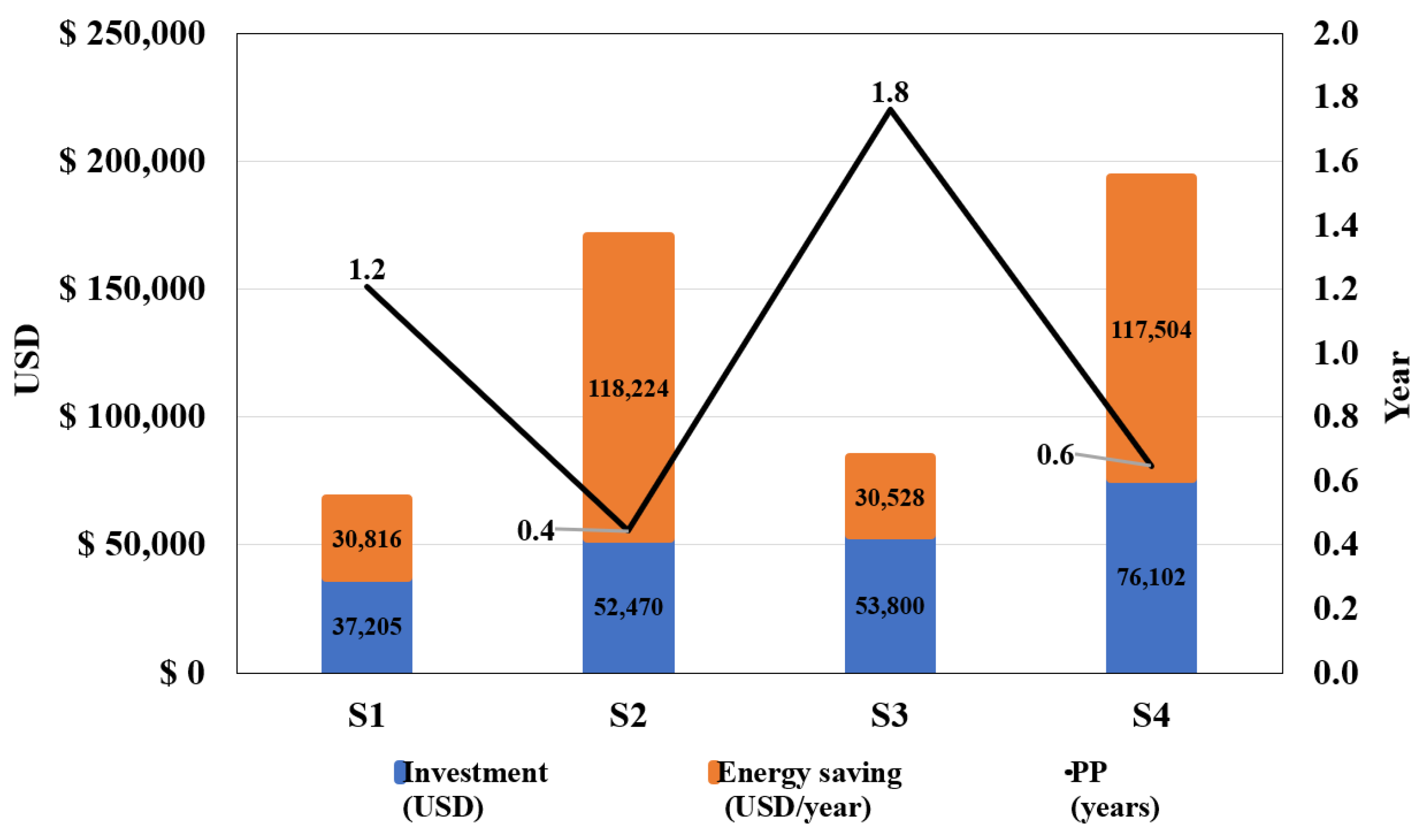

- Economic evaluation of solutions.

2.4. Comparison and Best Solution

3. Results and Analysis

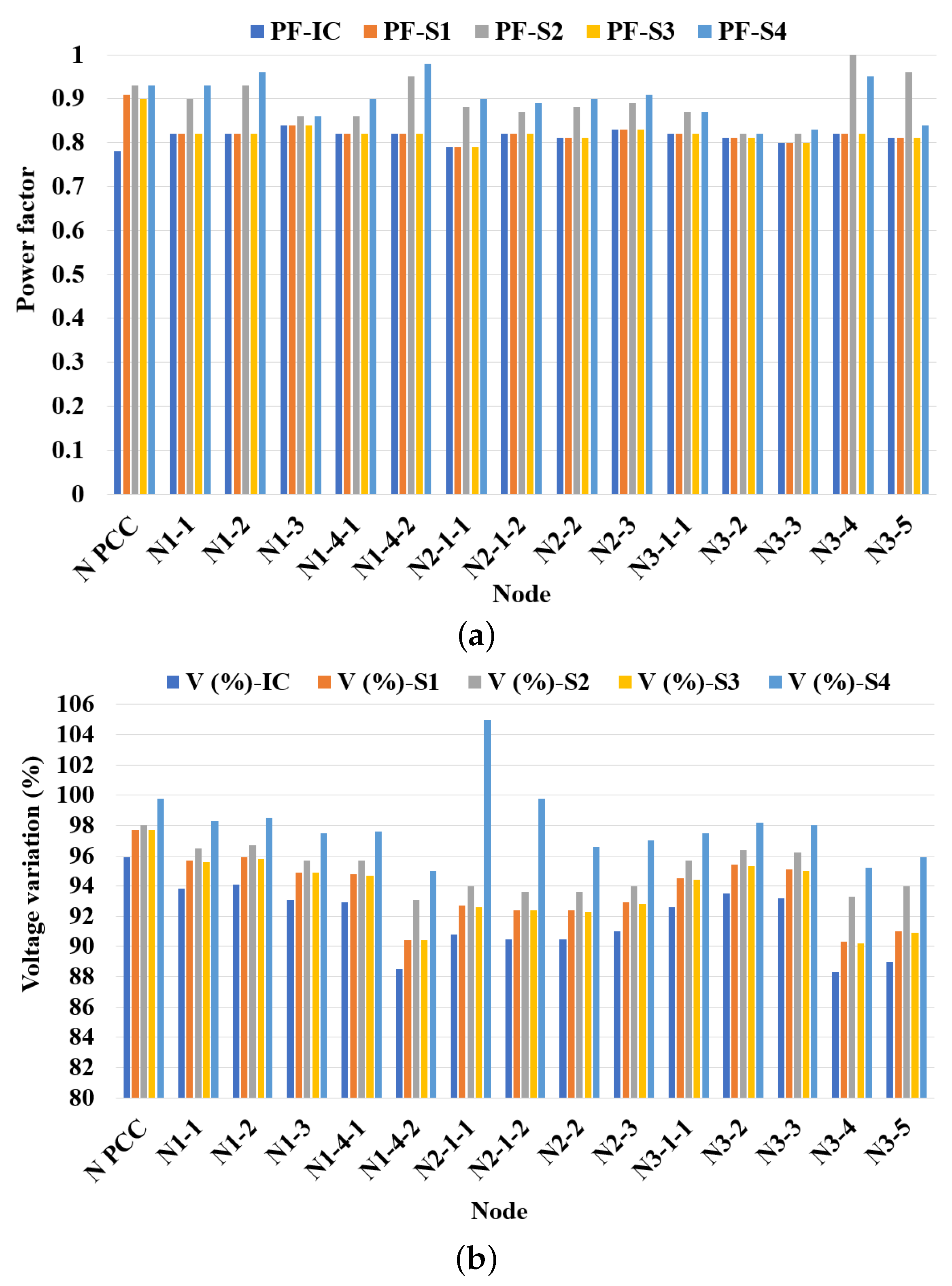

3.1. Solution 1

- Improve the PF in the PCC.

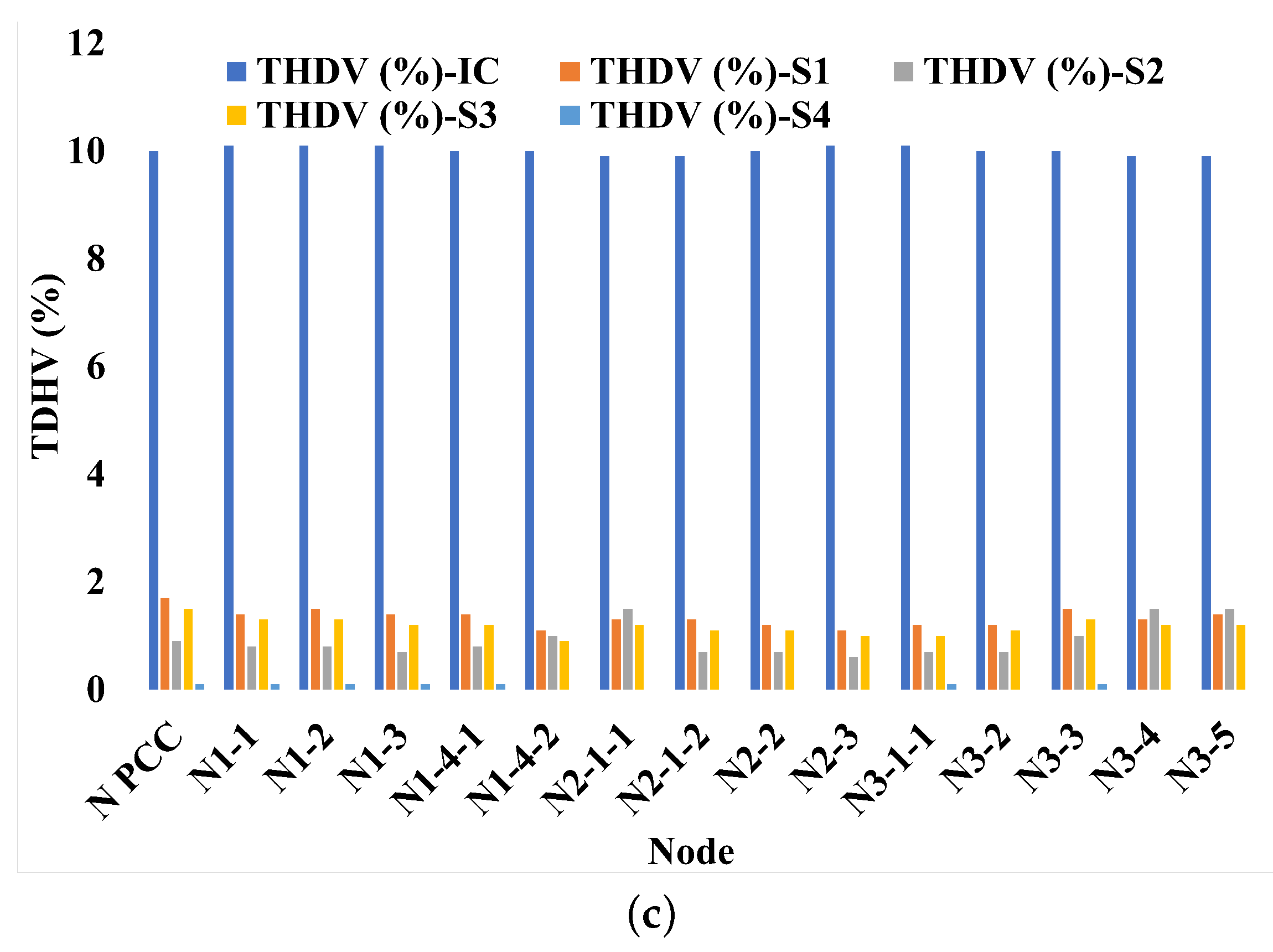

- Reduction of harmonics.

- Reduction of electrical losses.

3.2. Solution 2

- Improvement of the PF in the PCC.

- Elimination of voltage variation problems throughout the circuit.

- Reduction of harmonics.

- Reduction in electrical losses.

3.3. Solution 3

- Improvement of the PF in the PCC.

- Reduction of harmonics.

- Reduction in electrical losses.

3.4. Solution 4

- Improvement of the PF in the PCC.

- Elimination of voltage variation problems throughout the circuit.

- Reduction of harmonics.

- Reduction in electrical losses.

3.5. Comparison

- Permanently connected fixed capacitor banks.

- Automatic capacitor banks with measurement in a single phase, the phase with the highest consumption.

4. Conclusions

- The results show that distributed compensation is more effective in improving PF, reducing voltage variation, and mitigating harmonics in the PCC and IES nodes. Although the initial investment in concentrated compensation was lower, the savings from energy losses in distributed compensation resulted in a better PP.

- These results demonstrate that, for the analysis of a technical solution to an engineering problem, consultants’ expertise is required because sometimes technical and economic evaluations alone are not always sufficient, but comprehensive analyses must be carried out, such as the case presented.

- Implementing capacitor banks or harmonic filters reduced harmonics throughout the IES. However, the capacitor banks showed a reduction in their useful life due to overheating caused by current harmonics. Selecting the optimal solution considered both technical and financial aspects, resulting in the preference for distributed harmonic filters due to their effectiveness and lower impact on the useful life of the devices.

- Despite the common practice of concentrated compensation of capacitor banks in the PCC due to its low initial cost and easy installation, it was concluded that this is not the most viable solution, especially in environments with increasing nonlinear loads that affect the useful life of the capacitor banks and provide negligible improvements in the PF and the voltage variation in the IES nodes.

- Exploring technologies based on active filters that can be installed at different points in the IES circuit, not only at the PCC, is recommended. In addition, the need to continue research on electrical power quality problems in IESs is emphasized, as studies focus on distribution and power systems.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lin, L.; Wang, J.; Gao, W. Effect of load power factor on voltage stability of distribution substation. In Proceedings of the 2012 IEEE Power and Energy Society General Meeting, San Diego, CA, USA, 22–26 July 2012; pp. 1–4. [Google Scholar]

- Sagiroglu, S.; Colak, I.; Bayindir, R. Power factor correction technique based on artificial neural networks. Energy Convers. Manag. 2006, 47, 3204–3215. [Google Scholar] [CrossRef]

- Hofmann, W.; Schlabbach, J.; Just, W. Reactive Power Compensation: A Practical Guide; John Wiley & Sons: Chichester, UK, 2012. [Google Scholar]

- Jain, R.; Sharma, S.; Sreejeth, M.; Singh, M. PLC based power factor correction of 3-phase Induction Motor. In Proceedings of the 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Delhi, India, 4–6 July 2016; pp. 1–5. [Google Scholar]

- Mendis, S.R.; Bishop, M.T.; Blooming, T.M.; Moore, R.T. Improving system operations with the installation of capacitor filter banks in a paper facility with multiple generating units. In Proceedings of the Conference Record of 1995 Annual Pulp and Paper Industry Technical Conference, Vancouver, BC, Canada, 12–16 June 1995. [Google Scholar]

- CREG. Metodología para la Remuneración de la Actividad de Distribución de Energía Electrica en el Sistema Interconectado Nacional; Resolución CREG 015-2018, Technical Report; Comisión de Regulación de Energía y Gas—CREG: Bogotá, Colombia, 2018. [Google Scholar]

- Grainger, J.J.; Stevenson, W.U.D., Jr. Power System Analysis; McGraw Hill: New York, NY, USA, 1994. [Google Scholar]

- Riaz, M.T.; Afzal, M.M.; Aaqib, S.M.; Ali, H. Analysis and Evaluating the Effect of Harmonic Distortion Levels in Industry. In Proceedings of the 2021 4th International Conference on Energy Conservation and Efficiency (ICECE), Lahore, Pakistan, 16–17 March 2021; pp. 1–7. [Google Scholar]

- Singh, R.; Paniyil, P.; Zhang, Z. Transformative Role of Power Electronics: In solving climate emergency. IEEE Power Electron. Mag. 2022, 9, 39–47. [Google Scholar] [CrossRef]

- Williamson, S.S. The success of electric mobility will depend on power electronics. Nat. Electron. 2022, 5, 14–15. [Google Scholar] [CrossRef]

- Tang, Y.; Cao, D.; Xiao, J.; Jiang, C.; Huang, Q.; Li, Y.; Chen, Z.; Blaabjerg, F.; Hu, W. AI-aided power electronic converters automatic online real-time efficiency optimization method. Fundam. Res. 2023; in press. [Google Scholar]

- Hannan, M.A.; Lipu, M.S.H.; Ker, P.J.; Begum, R.A.; Agelidis, V.G.; Blaabjerg, F. Power electronics contribution to renewable energy conversion addressing emission reduction: Applications, issues, and recommendations. Appl. Energy 2019, 251, 113404. [Google Scholar] [CrossRef]

- Erickson, R.W.; Maksimović, D. Fundamentals of Power Electronics; Springer International Publishing: Berlin/Heidelberg, Germany, 2020. [Google Scholar]

- Zhao, B.; Assawaworrarit, S.; Santhanam, P.; Orenstein, M.; Fan, S. High-performance photonic transformers for DC voltage conversion. Nat. Commun. 2021, 12, 4684. [Google Scholar] [CrossRef]

- Angarita, E.N.; Santos, V.S.; Donolo, P.D.; Quispe, E.C. Assessing power quality in individual circuits of industrial electrical system. Int. J. Elect. Computer Syst. Eng. 2024, 14, 4888–4896. [Google Scholar] [CrossRef]

- Waleed, A.; Javed, M.R.; Riaz, M.T.; Virk, U.S.; Khan, S.; Mujtaba, A.; Ahmad, S.; Arshad, G. Study on Hybrid Wind-Solar System for Energy Saving Analysis in Energy Sector. In Proceedings of the 2020 3rd International Conference on Computing, Mathematics and Engineering Technologies (iCoMET), Sukkur, Pakistan, 29–30 January 2020; pp. 1–6. [Google Scholar]

- Waleed, A.; Virk, U.S.; Riaz, M.T.; Mehmood, S.B.; Ahmad, S.; Javed, M.R.; Raza, A. Effectiveness and comparison of digital substations over conventional substations. Adv. Sci. Technol. Eng. Syst. J. 2019, 4, 431–439. [Google Scholar] [CrossRef]

- Ma, H.; Zheng, C.; Yu, W.; Lai, J.S.j. A single-stage integrated bridgeless AC/DC converter for electrolytic capacitor-less LED lighting applications. Int. J. Circuit Theory Appl. 2015, 43, 742–755. [Google Scholar] [CrossRef]

- Zheng, F.; Zhang, W. Long term effect of power factor correction on the industrial load: A case study. In Proceedings of the 2017 Australasian Universities Power Engineering Conference (AUPEC), Melbourne, VIC, Australia, 19–22 November 2017; pp. 1–5. [Google Scholar]

- Babu, V.; Manikandan, M. Total harmonic distortion reduction for power quality improvement: A review. Int. J. Sci. Res. 2017, 6, 1681–1684. [Google Scholar]

- El-Mahayni, R.; Van De Vijver, R.; Rashidi, R.; Al-Nujaimi, A. Corporate wide power factor correction application: Economic and technical assessment. In Proceedings of the 2017 Petroleum and Chemical Industry Conference Europe (PCIC Europe), Vienna, Austria, 16–18 May 2017; pp. 1–13. [Google Scholar]

- Matsumoto, I.; Nomura, S. Power factor correction of large current line commutated converters using variable series capacitors. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–9. [Google Scholar]

- Farag, H.E.Z.; El-Saadany, E.F. Optimum Shunt Capacitor Placement in Multimicrogrid Systems With Consideration of Islanded Mode of Operation. IEEE Trans. Sustain. Energy 2015, 6, 1435–1446. [Google Scholar] [CrossRef]

- Askarzadeh, A. Capacitor placement in distribution systems for power loss reduction and voltage improvement: A new methodology. IET Gener. Transm. Distrib. 2016, 10, 3631–3638. [Google Scholar] [CrossRef]

- Tahir, M.J.; Bakar, B.A.; Alam, M.; Mazlihum, M.S. Optimal capacitor placement in a distribution system using ETAP software. Indones. J. Electr. Eng. Comput. Sci. 2019, 15, 650. [Google Scholar] [CrossRef]

- Etemadi, A.H.; Fotuhi-Firuzabad, M. Distribution system reliability enhancement using optimal capacitor placement. IET Gener. Transm. Distrib. 2008, 2, 621. [Google Scholar] [CrossRef]

- Rahmani-andebili, M. Reliability and economic-driven switchable capacitor placement in distribution network. IET Gener. Transm. Distrib. 2015, 9, 1572–1579. [Google Scholar] [CrossRef]

- Kavousi Fard, A.; Niknam, T. Optimal stochastic capacitor placement problem from the reliability and cost views using firefly algorithm. IET Sci. Meas. Technol. 2014, 8, 260–269. [Google Scholar] [CrossRef]

- Blooming, T.M. Capacitor failure analysis. IEEE Ind. Appl. Mag. 2006, 12, 38–48. [Google Scholar] [CrossRef]

- Blooming, T.M.; Carnovale, D.J. Capacitor Application Issues. IEEE Trans. Ind. Appl. 2008, 44, 1013–1026. [Google Scholar] [CrossRef]

- Shakeri, S.; Rezaeian Koochi, M.H.; Ansari, H.; Esmaeili, S. Optimal power quality monitor placement to ensure reliable monitoring of sensitive loads in the presence of voltage sags and harmonic resonances conditions. Electr. Power Syst. Res. 2022, 212, 108623. [Google Scholar] [CrossRef]

- Boonseng, C.; Gitnumlapcharoen, P. Effect of Low Harmonic Current Under Large Transformers on Harmonic Resonance Assessment in Industrial Systems. In Proceedings of the 2022 IEEE International Conference on Power and Energy (PECon), Langkawi, Kedah, Malaysia, 5–6 December 2022; pp. 181–185. [Google Scholar]

- Kalair, A.; Abas, N.; Kalair, A.R.; Saleem, Z.; Khan, N. Review of harmonic analysis, modeling and mitigation techniques. Renew. Sustain. Energy Rev. 2017, 78, 1152–1187. [Google Scholar] [CrossRef]

- Karuppanan, P.; Mahapatra, K.K. Active harmonic current compensation to enhance power quality. Int. J. Electr. Power Energy Syst. 2014, 62, 144–151. [Google Scholar] [CrossRef]

- Gonzatti, R.B.; Ferreira, S.C.; da Silva, C.H.; Pereira, R.R.; da Silva, L.E.B.; Lambert-Torres, G. Smart Impedance: A New Way to Look at Hybrid Filters. IEEE Trans. Smart Grid 2016, 7, 837–846. [Google Scholar] [CrossRef]

- Ioana, G.; Cazacu, E.; Stănculescu, M.; Pușcașu, S. Power Factor Correction and Harmonic Mitigation for a Heavy Industrial Nonlinear Load. In Proceedings of the 2023 13th International Symposium on Advanced Topics in Electrical Engineering (ATEE), Bucharest, Romania, 23–25 March 2023; pp. 1–6. [Google Scholar]

- Satish, G.; Rameshkumar, K.; Dhanasakkaravarthi, B.; Jeyalakshmi, K.; Chaudhary, S.; Singh, N. Non-Linear Controller Based 3–Phase Shunt Active Filter for Improvement of Power Quality in Non-Linear Load. In Proceedings of the 2023 IEEE International Conference on Integrated Circuits and Communication Systems (ICICACS), Raichur, India, 24–25 February 2023; pp. 1–4. [Google Scholar]

- Chennai, S.; Electrical Engineering Department CRNB, B.P.O. 180 Ain-Ousserra, Algeria. Series APF based on Five and Seven-Level NPC Inverters using modified PQ Method. Electroteh. Electron. Autom. 2023, 71, 22–29. [Google Scholar] [CrossRef]

- Kamat, P.R.; Naik, A.J. Performance Evaluation of Butterworth, Chebyshev, and Elliptic filter for Harmonic Mitigation using P-Q based SAPF. In Proceedings of the 2022 International Conference on Smart Generation Computing, Communication and Networking (SMART GENCON), Bangalore, India, 23–25 December 2022; pp. 1–5. [Google Scholar]

- IEEE Std 519-2022; IEEE Standard for Harmonic Control in Electric Power Systems. Technical Report; Institute of Electrical and Electronics Engineers: Piscataway, NJ, USA, 2022.

- Icontec. Norma téCnica NTC 5001. Calidad de la Potencia Eléctrica; Technical Report; Instituto Colombiano de Normas Técnicas y Certificación—ICONTEC: Bogotá, Colombia, 2008. [Google Scholar]

- Attachie, J.C.; Amuzuvi, C.K. Investigating harmonic resonance and capacitor bank switching at a power distribution substation using a fixed capacitor bank. Res. J. Eng. Appl. Sci. 2013, 2, 343–348. [Google Scholar]

- Candelo, J.E.; Hernández Riaño, H. Location and size of distributed generation to reduce power losses using a bat-inspired algorithm. In Proceedings of the VII Simposio Internacional sobre la Calidad de la Energía Eléctrica—SICEL 2013, Medellín, Colombia, 27–29 November 2013; pp. 1–9. [Google Scholar]

- Arias, J.; Calle, M.; Turizo, D.; Guerrero, J.; Candelo-Becerra, J.E. Historical Load Balance in Distribution Systems Using the Branch and Bound Algorithm. Energies 2019, 12, 1219. [Google Scholar] [CrossRef]

- IEEE Std 1159-2019; IEEE Recommended Practice for Monitoring Electric Power Quality. Technical Report; Institute of Electrical and Electronics Engineers: Piscataway, NJ, USA, 2019.

- Icontec. Norma Técnica NTC 1340. Tensiones y Frecuencias Nominales en Sistemas de Energía Eléctrica en Redes de Servicio Publico; Technical Report; Icontec: Bogota, Colombia, 2013. [Google Scholar]

- Legrand. Compensación de Energía Reactiva y Monitoreo de la Calidad de la Potencia; Technical Report; Legrand: Limoges, France, 2018. [Google Scholar]

- Pérez Abril, I. Cálculo de parámetros de filtros pasivos de armónicos. Ing. Energética 2012, XXXIII, 134–143. [Google Scholar]

- Boylestad, R.L. Introducción al Análisis de Circuitos, 12th ed.; Pearson Educación: Naucalpan de Juárez, Mexico, 2019. [Google Scholar]

- Frutos Cabrera, C.L.; Cayetano Lotero, R. Compensación reactiva en sistemas eléctricos industriales con presencia de armónicos. FPUNE Sci. 2019, 12, 53–69. [Google Scholar]

- Reyes Calderón, G. Armónicas en Sistemas de Distribución de Energía Eléctrica. Master Thesis, Universidad Autónoma de Nuevo León, San Nicolás de los Garza, Mexico, 1996. [Google Scholar]

- Aguado Giraldo, E.J.; Bravo Jordán, R.D. Efectos Causados por Los Armónicos en Bancos de Condensadores; Corporación Universitaria Autónoma de Occidente: Santiago de Cali, Colombia, 1995. [Google Scholar]

- Arcos Lopez, E.R.; Chicaiza Díaz, D.M. Diseño y Construcción de un Tablero de Control Automático Para la Corrección del Factor de Potencia, Empleando un Módulo DCRA. Escuela Politécnica Nacional—Escuela de Formación de Tecnólogos. 2015. Available online: https://bibdigital.epn.edu.ec/handle/15000/10583 (accessed on 3 September 2024).

| Node | Type | P (kW) | Q (kVAr) |

|---|---|---|---|

| N PCC | Transformer 1 | 5507 | 4470 |

| N1 | Link | - | - |

| N1-1 | Load | 82 | 58 |

| N1-2 | Load | 67 | 46 |

| N1-3 | Load | 481 | 310 |

| N1-4 | Link | - | - |

| N1-4-1 | Load | 124 | 86 |

| N1-4-2 | Load | 933 | 663 |

| N2 | Link | - | - |

| N2-1 | Link | - | - |

| N2-1-1 | Load | 317 | 248 |

| N2-1-2 | Load | 249 | 176 |

| N2-2 | Load | 560 | 410 |

| N2-3 | Load | 740 | 490 |

| N3 | Link | - | - |

| N3-1 | Transformer 2 | - | - |

| N3-1-1 | Load | 142 | 98 |

| N3-2 | Load | 482 | 354 |

| N3-3 | Load | 253 | 190 |

| N3-4 | Load | 472 | 325 |

| N3-5 | Load | 355 | 258 |

| Node | PF | V (%) | THDV (%) |

|---|---|---|---|

| N PCC | 0.78 | 95.9 | 10.0 |

| N1 | - | - | - |

| N1-1 | 0.82 | 93.8 | 10.1 |

| N1-2 | 0.82 | 94.1 | 10.1 |

| N1-3 | 0.84 | 93.1 | 10.1 |

| N1-4 | - | - | - |

| N1-4-1 | 0.82 | 92.9 | 10.0 |

| N1-4-2 | 0.82 | 88.5 | 10.0 |

| N2 | - | - | - |

| N2-1 | - | - | - |

| N2-1-1 | 0.79 | 90.8 | 9.9 |

| N2-1-2 | 0.82 | 90.5 | 9.9 |

| N2-2 | 0.81 | 90.5 | 10.0 |

| N2-3 | 0.83 | 91.0 | 10.1 |

| N3 | - | - | - |

| N3-1 | - | - | - |

| N3-1-1 | 0.82 | 92.6 | 10.1 |

| N3-2 | 0.81 | 93.5 | 10.0 |

| N3-3 | 0.80 | 93.2 | 10.0 |

| N3-4 | 0.82 | 88.3 | 9.9 |

| N3-5 | 0.81 | 89.0 | 9.9 |

| Line Losses (kW) | Harmonic Losses (kW) | Total Losses (kW) | Cost per Losses (USD) |

|---|---|---|---|

| 249.5 | 11.1 | 260.6 | 53.31 |

| Node | Type | Capacitor Bank (kVAr) | Cost (USD) | (kVA) | |

|---|---|---|---|---|---|

| N PCC | Transformer 1 | 1700 | 36,056 | 10,061 | 2 |

| Node | Type | P (kW) | Q (kVAr) | PF | V (%) | THDV (%) |

|---|---|---|---|---|---|---|

| N PCC | Transformer 1 | 5495.9 | 2548.7 | 0.91 | 97.7 | 1.7 |

| N1-1 | Load | 82 | 58 | 0.82 | 95.7 | 1.4 |

| N1-2 | Load | 67 | 46 | 0.82 | 95.9 | 1.5 |

| N1-3 | Load | 481 | 310 | 0.84 | 94.9 | 1.4 |

| N1-4-1 | Load | 124 | 86 | 0.82 | 94.8 | 1.4 |

| N1-4-2 | Load | 933 | 663 | 0.82 | 90.4 | 1.1 |

| N2-1-1 | Load | 317 | 248 | 0.79 | 92.7 | 1.3 |

| N2-1-2 | Load | 249 | 176 | 0.82 | 92.4 | 1.3 |

| N2-2 | Load | 560 | 410 | 0.81 | 92.4 | 1.2 |

| N2-3 | Load | 740 | 490 | 0.83 | 92.9 | 1.1 |

| N3-1-1 | Load | 142 | 98 | 0.82 | 94.5 | 1.2 |

| N3-2 | Load | 482 | 354 | 0.81 | 95.4 | 1.2 |

| N3-3 | Load | 253 | 190 | 0.80 | 95.1 | 1.5 |

| N3-4 | Load | 472 | 325 | 0.82 | 90.3 | 1.3 |

| N3-5 | Load | 355 | 258 | 0.81 | 91.0 | 1.4 |

| Line Losses (kW) | Harmonic Losses (kW) | Total Losses (kW) | Cost of Losses (USD) |

|---|---|---|---|

| 238.9 | 0.3 | 239.2 | 48.94 |

| Node | Type | Capacitor Bank (kVAr) | Cost (USD) | (kVA) | |

|---|---|---|---|---|---|

| N1-1 | Load | 25 | 851.12 | 7.179 | 17 |

| N1-2 | Load | 25 | 851.12 | 8.173 | 18 |

| N1-3 | Load | 25 | 851.12 | 8.173 | 18 |

| N1-4-1 | Load | 25 | 851.12 | 7.199 | 17 |

| N1-4-2 | Load | 500 | 11,611.53 | 7.004 | 4 |

| N2-1-1 | Load | 100 | 2560.16 | 6.343 | 8 |

| N2-1-2 | Load | 50 | 2207.21 | 6.030 | 11 |

| N2-2 | Load | 150 | 4588.34 | 7.029 | 7 |

| N2-3 | Load | 150 | 4588.34 | 7.289 | 7 |

| N3-1-1 | Load | 18 | 490.31 | 4.406 | 16 |

| N3-2 | Load | 18 | 490.31 | 9.035 | 22 |

| N3-3 | Load | 18 | 490.31 | 7.370 | 20 |

| N3-4 | Load | 500 | 11,611.53 | 6.062 | 3 |

| N3-5 | Load | 500 | 11,611.53 | 5.731 | 3 |

| Node | Type | P (kW) | Q (kVAr) | PF | V (%) | THDV (%) |

|---|---|---|---|---|---|---|

| N PCC | Transformer 1 | 5435.4 | 2219 | 0.93 | 98.0 | 0.9 |

| N1-1 | Load | 82 | 58 | 0.90 | 96.5 | 0.8 |

| N1-2 | Load | 67 | 46 | 0.93 | 96.7 | 0.8 |

| N1-3 | Load | 481 | 310 | 0.86 | 95.7 | 0.7 |

| N1-4-1 | Load | 124 | 86 | 0.86 | 95.7 | 0.8 |

| N1-4-2 | Load | 933 | 663 | 0.95 | 93.1 | 1.0 |

| N2-1-1 | Load | 317 | 248 | 0.88 | 94.0 | 1.5 |

| N2-1-2 | Load | 249 | 176 | 0.87 | 93.6 | 0.7 |

| N2-2 | Load | 560 | 410 | 0.88 | 93.6 | 0.7 |

| N2-3 | Load | 740 | 490 | 0.89 | 94.0 | 0.6 |

| N3-1-1 | Load | 142 | 98 | 0.87 | 95.7 | 0.7 |

| N3-2 | Load | 482 | 354 | 0.82 | 96.4 | 0.7 |

| N3-3 | Load | 253 | 190 | 0.82 | 96.2 | 1.0 |

| N3-4 | Load | 472 | 325 | 1.00 | 93.3 | 1.5 |

| N3-5 | Load | 355 | 258 | 0.96 | 94.0 | 1.5 |

| Line Losses (kW) | Harmonic Losses (kW) | Total Losses (kW) | Cost of Losses (USD) |

|---|---|---|---|

| 178.4 | 0.1 | 178.5 | 36.52 |

| Node | Type | Filter (kVAr) | Cost (USD) | C | L (mH) | R () |

|---|---|---|---|---|---|---|

| N PCC | Transformer 1 | 1700 | 55,044.70 | 23.621 | 0.0119 | 0.0004 |

| Node | Type | P (kW) | Q (kVAr) | PF | V (%) | THDV (%) |

|---|---|---|---|---|---|---|

| N PCC | Transformer 1 | 5496.2 | 2617.2 | 0.90 | 97.7 | 1.5 |

| N1-1 | Load | 82 | 58 | 0.82 | 95.6 | 1.3 |

| N1-2 | Load | 67 | 46 | 0.82 | 95.8 | 1.3 |

| N1-3 | Load | 481 | 310 | 0.84 | 94.9 | 1.2 |

| N1-4-1 | Load | 124 | 86 | 0.82 | 94.7 | 1.2 |

| N1-4-2 | Load | 933 | 663 | 0.82 | 90.4 | 0.9 |

| N2-1-1 | Load | 317 | 248 | 0.79 | 92.6 | 1.2 |

| N2-1-2 | Load | 249 | 176 | 0.82 | 92.4 | 1.1 |

| N2-2 | Load | 560 | 410 | 0.81 | 92.3 | 1.1 |

| N2-3 | Load | 740 | 490 | 0.83 | 92.8 | 1.0 |

| N3-1-1 | Load | 142 | 98 | 0.82 | 94.4 | 1.0 |

| N3-2 | Load | 482 | 354 | 0.81 | 95.3 | 1.1 |

| N3-3 | Load | 253 | 190 | 0.80 | 95.0 | 1.3 |

| N3-4 | Load | 472 | 325 | 0.82 | 90.2 | 1.2 |

| N3-5 | Load | 355 | 258 | 0.81 | 90.9 | 1.2 |

| Line Losses (kW) | Harmonic Losses (kW) | Total Losses (kW) | Cost per Losses (USD) |

|---|---|---|---|

| 239.2 | 0.2 | 239.4 | 48.96 |

| Node | Type | Filter (kVAr) | Cost (USD) | Capacitance (F) | Inductance (mH) | Resistance () |

|---|---|---|---|---|---|---|

| N1-1 | Load | 25 | 1389.54 | 358 | 0.7862 | 0.02964 |

| N1-2 | Load | 25 | 1389.54 | 356 | 0.7895 | 0.02977 |

| N1-3 | Load | 25 | 1389.54 | 364 | 0.7736 | 0.02916 |

| N1-4-1 | Load | 25 | 1389.54 | 364 | 0.7736 | 0.02916 |

| N1-4-2 | Load | 500 | 16,451.31 | 7770 | 0.0362 | 0.00137 |

| N2-1-1 | Load | 100 | 3778.96 | 1514 | 0.1859 | 0.00701 |

| N2-1-2 | Load | 50 | 3285.31 | 763 | 0.3689 | 0.01391 |

| N2-2 | Load | 150 | 6615.70 | 2289 | 0.1230 | 0.00464 |

| N2-3 | Load | 150 | 6615.70 | 2268 | 0.1241 | 0.00468 |

| N3-1-1 | Load | 18 | 883.89 | 1048 | 0.2685 | 0.01012 |

| N3-2 | Load | 18 | 883.89 | 258 | 1.0893 | 0.04107 |

| N3-3 | Load | 18 | 883.89 | 260 | 1.0831 | 0.04083 |

| N3-4 | Load | 500 | 16,451.31 | 7751 | 0.0363 | 0.00137 |

| N3-5 | Load | 500 | 16,451.31 | 7626 | 0.0369 | 0.00139 |

| Node | Type | P (kW) | Q (kVAr) | PF | V (%) | THDV (%) |

|---|---|---|---|---|---|---|

| N PCC | Transformer 1 | 5444.5 | 2213.3 | 0.93 | 99.8 | 0.1 |

| N1-1 | Load | 82.1 | 58 | 0.93 | 98.3 | 0.1 |

| N1-2 | Load | 67.1 | 46 | 0.96 | 98.5 | 0.1 |

| N1-3 | Load | 481.1 | 310 | 0.86 | 97.5 | 0.1 |

| N1-4-1 | Load | 124.1 | 86 | 0.90 | 97.6 | 0.1 |

| N1-4-2 | Load | 935 | 663 | 0.98 | 95.0 | 0.0 |

| N2-1-1 | Load | 317.4 | 248 | 0.90 | 105 | 0.0 |

| N2-1-2 | Load | 249.2 | 176 | 0.89 | 99.8 | 0.0 |

| N2-2 | Load | 560.6 | 410 | 0.90 | 96.6 | 0.0 |

| N2-3 | Load | 740.6 | 490 | 0.91 | 97.0 | 0.0 |

| N3-1-1 | Load | 142.1 | 98 | 0.87 | 97.5 | 0.1 |

| N3-2 | Load | 482.1 | 354 | 0.82 | 98.2 | 0.0 |

| N3-3 | Load | 253.1 | 190 | 0.83 | 98.0 | 0.1 |

| N3-4 | Load | 474 | 325 | 0.95 | 95.2 | 0.0 |

| N3-5 | Load | 357 | 258 | 0.84 | 95.9 | 0.0 |

| Line Losses (kW) | Harmonic Losses (kW) | Total Losses (kW) | Cost of Losses (USD) |

|---|---|---|---|

| 179.0 | 0.0 | 179.0 | 36.60 |

| Solution | PF Improvement in the PCC | Elimination of Voltage Variation Problems in All Nodes | Reduction in Harmonics | Reduction of Electrical Losses | Reduction in Useful Life for Harmonics | PP |

|---|---|---|---|---|---|---|

| S1 | X | X | X | X | 1.2 | |

| S2 | X | X | X | X | X | 0.4 |

| S3 | X | X | X | 1.8 | ||

| S4 | X | X | X | X | 0.6 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Giha Yidi, S.A.; Sousa Santos, V.; Berdugo Sarmiento, K.; Candelo-Becerra, J.E.; de la Cruz, J. Comparison of Reactive Power Compensation Methods in an Industrial Electrical System with Power Quality Problems. Electricity 2024, 5, 642-661. https://doi.org/10.3390/electricity5030032

Giha Yidi SA, Sousa Santos V, Berdugo Sarmiento K, Candelo-Becerra JE, de la Cruz J. Comparison of Reactive Power Compensation Methods in an Industrial Electrical System with Power Quality Problems. Electricity. 2024; 5(3):642-661. https://doi.org/10.3390/electricity5030032

Chicago/Turabian StyleGiha Yidi, Salim Adolfo, Vladimir Sousa Santos, Kelly Berdugo Sarmiento, John E. Candelo-Becerra, and Jorge de la Cruz. 2024. "Comparison of Reactive Power Compensation Methods in an Industrial Electrical System with Power Quality Problems" Electricity 5, no. 3: 642-661. https://doi.org/10.3390/electricity5030032

APA StyleGiha Yidi, S. A., Sousa Santos, V., Berdugo Sarmiento, K., Candelo-Becerra, J. E., & de la Cruz, J. (2024). Comparison of Reactive Power Compensation Methods in an Industrial Electrical System with Power Quality Problems. Electricity, 5(3), 642-661. https://doi.org/10.3390/electricity5030032