Tribological, Thermal, Kinetic, and Surface Microtextural Characterization of Prime p-Type <100> Silicon Wafer CMP for Direct Wafer Bonding Applications

Abstract

1. Introduction

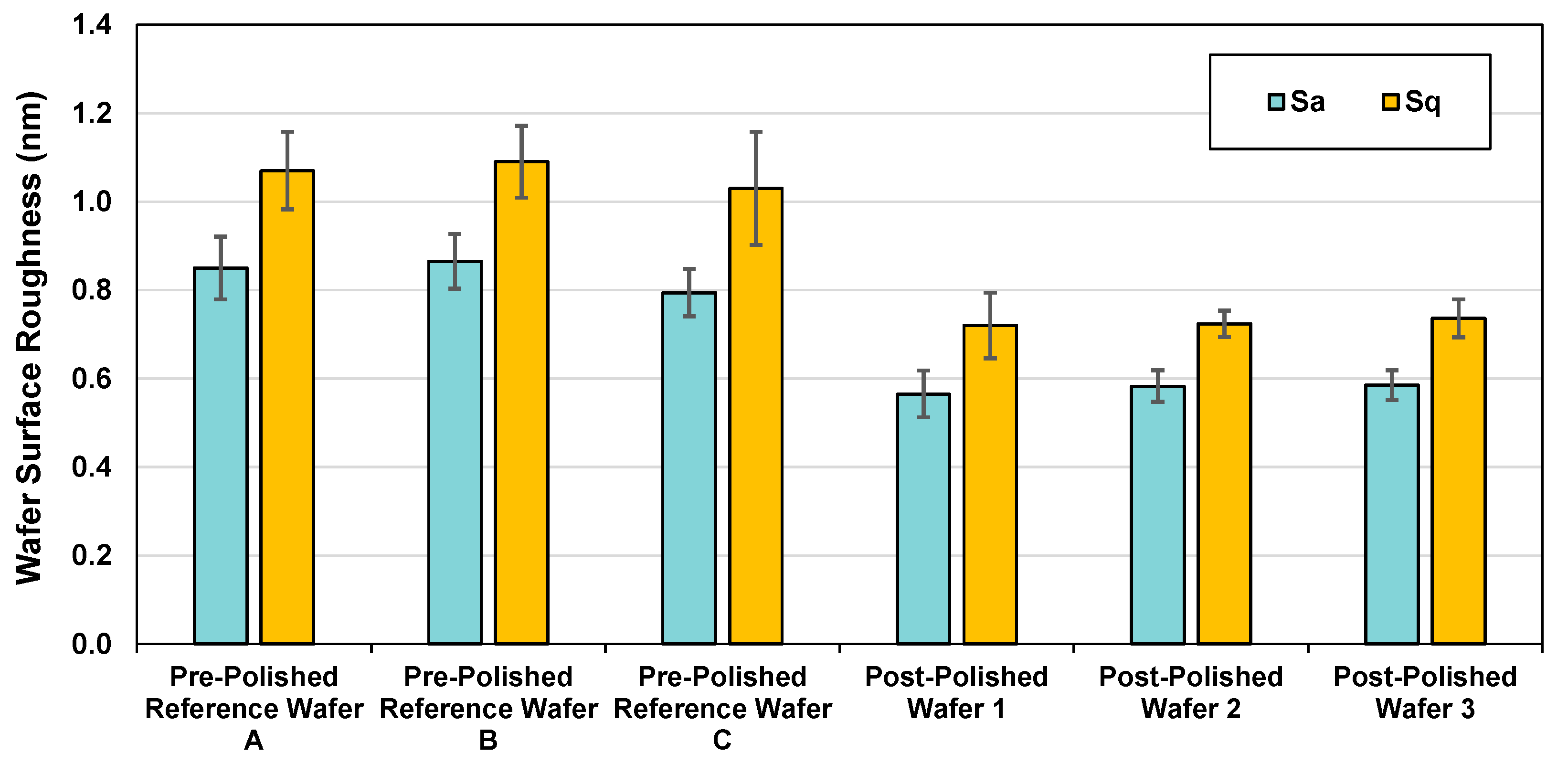

2. Experimental Apparatus and Procedure

3. Results

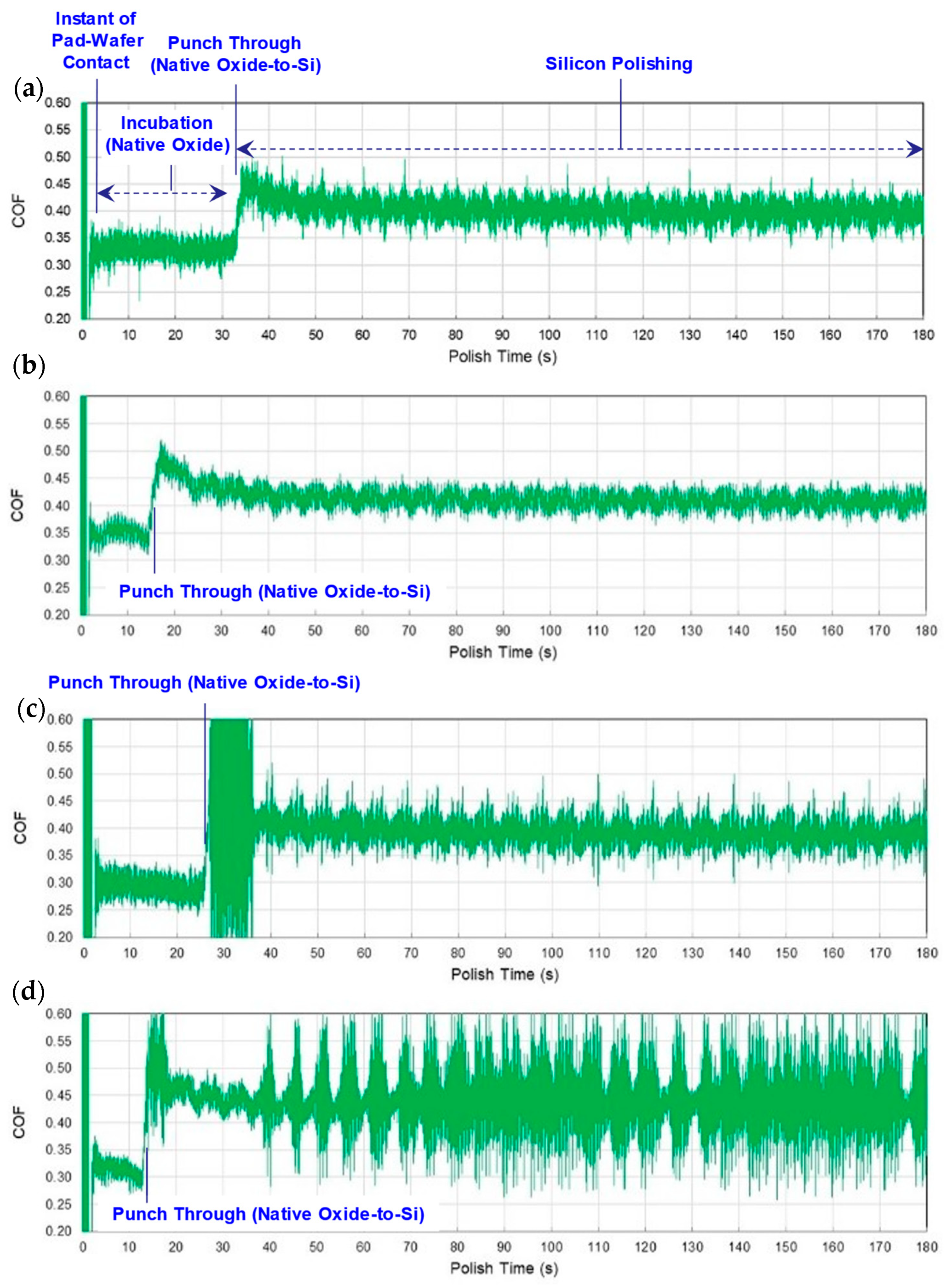

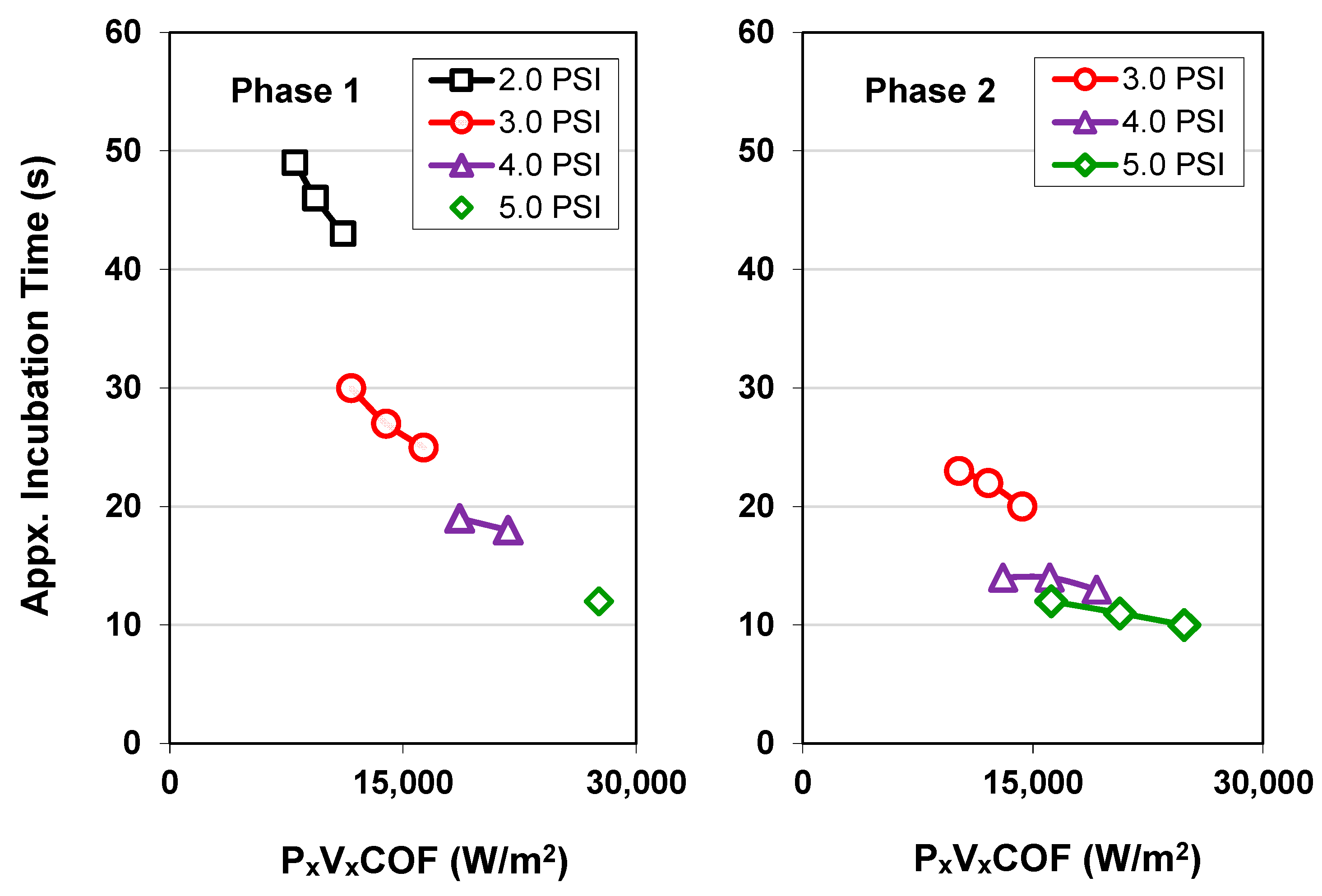

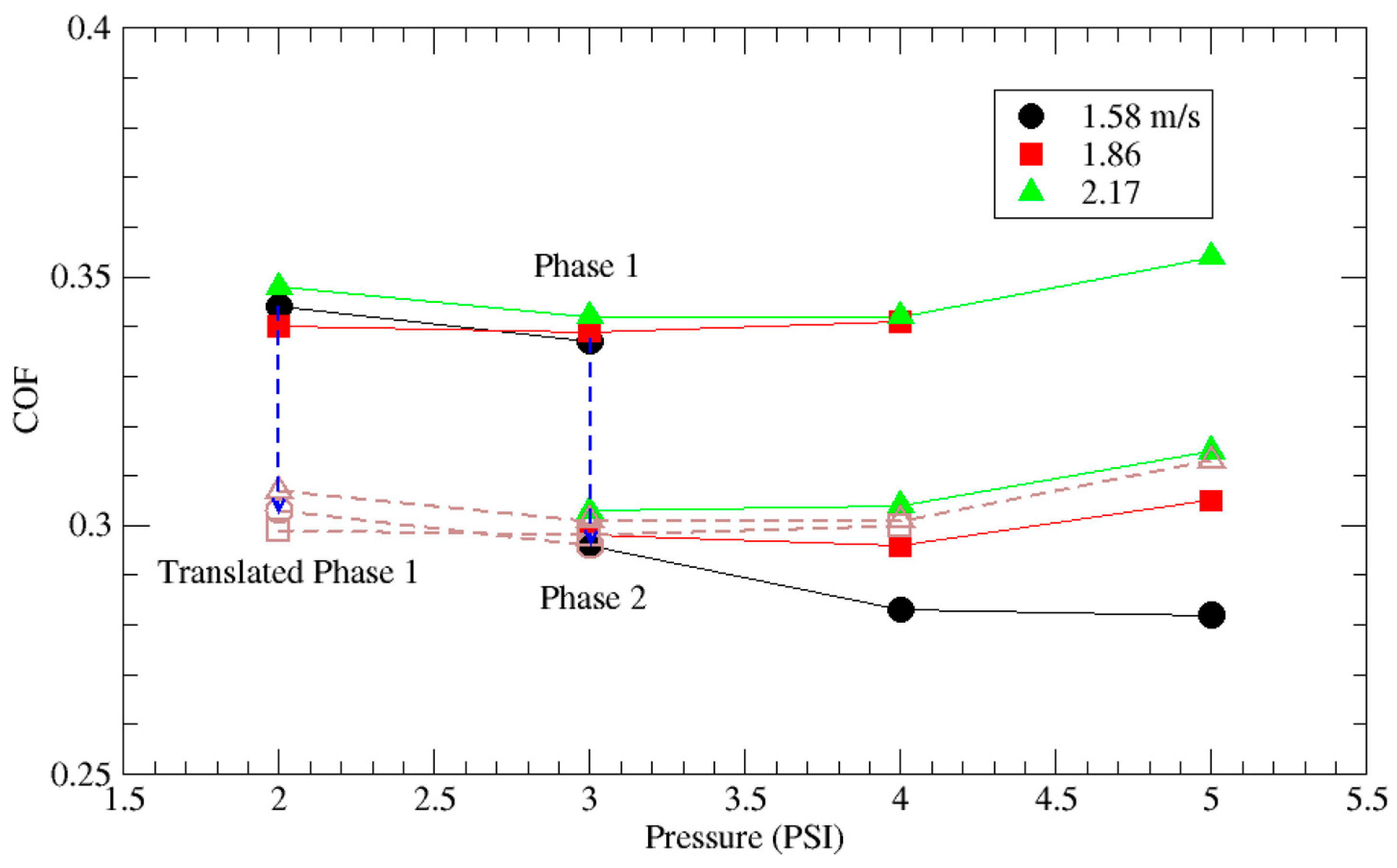

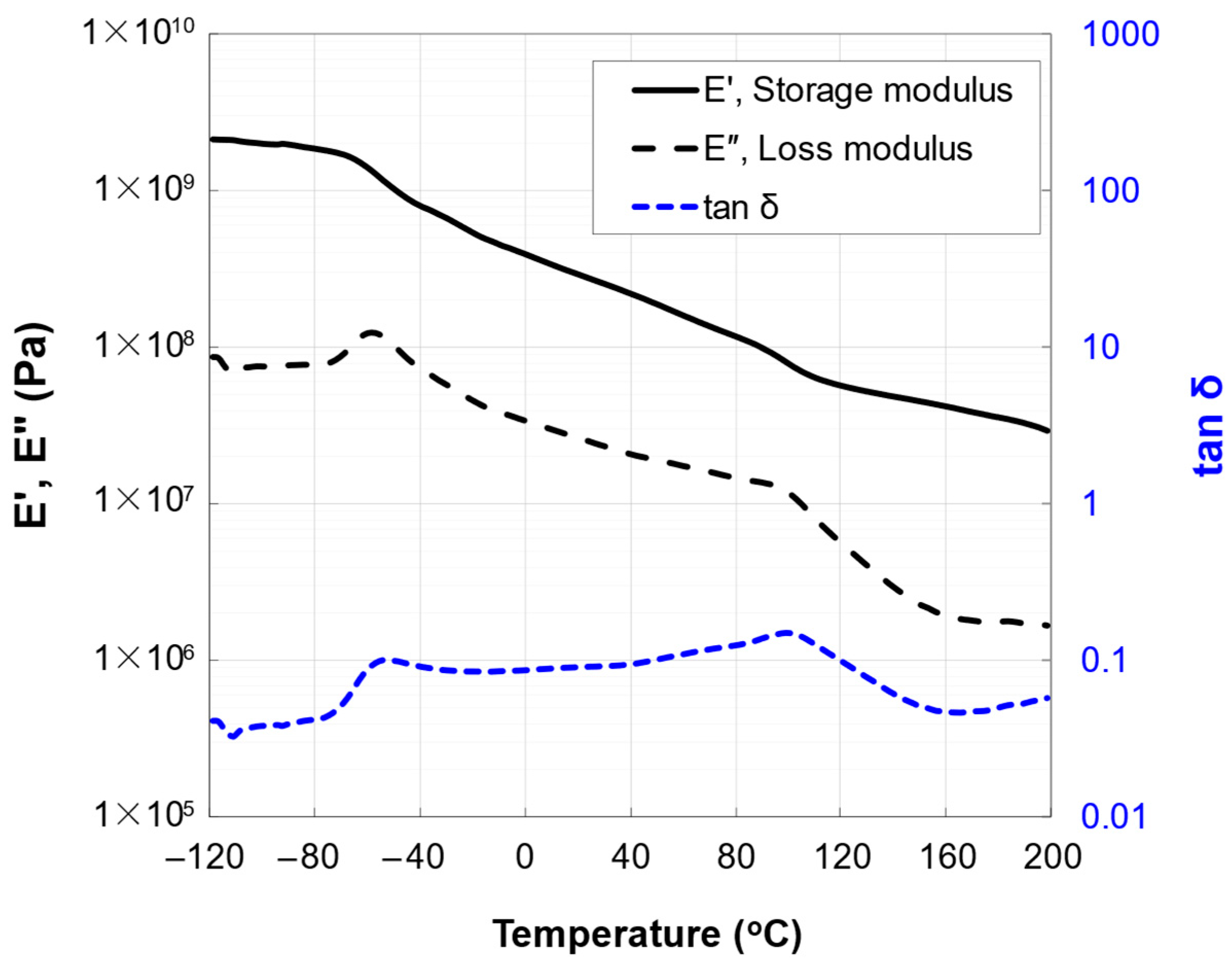

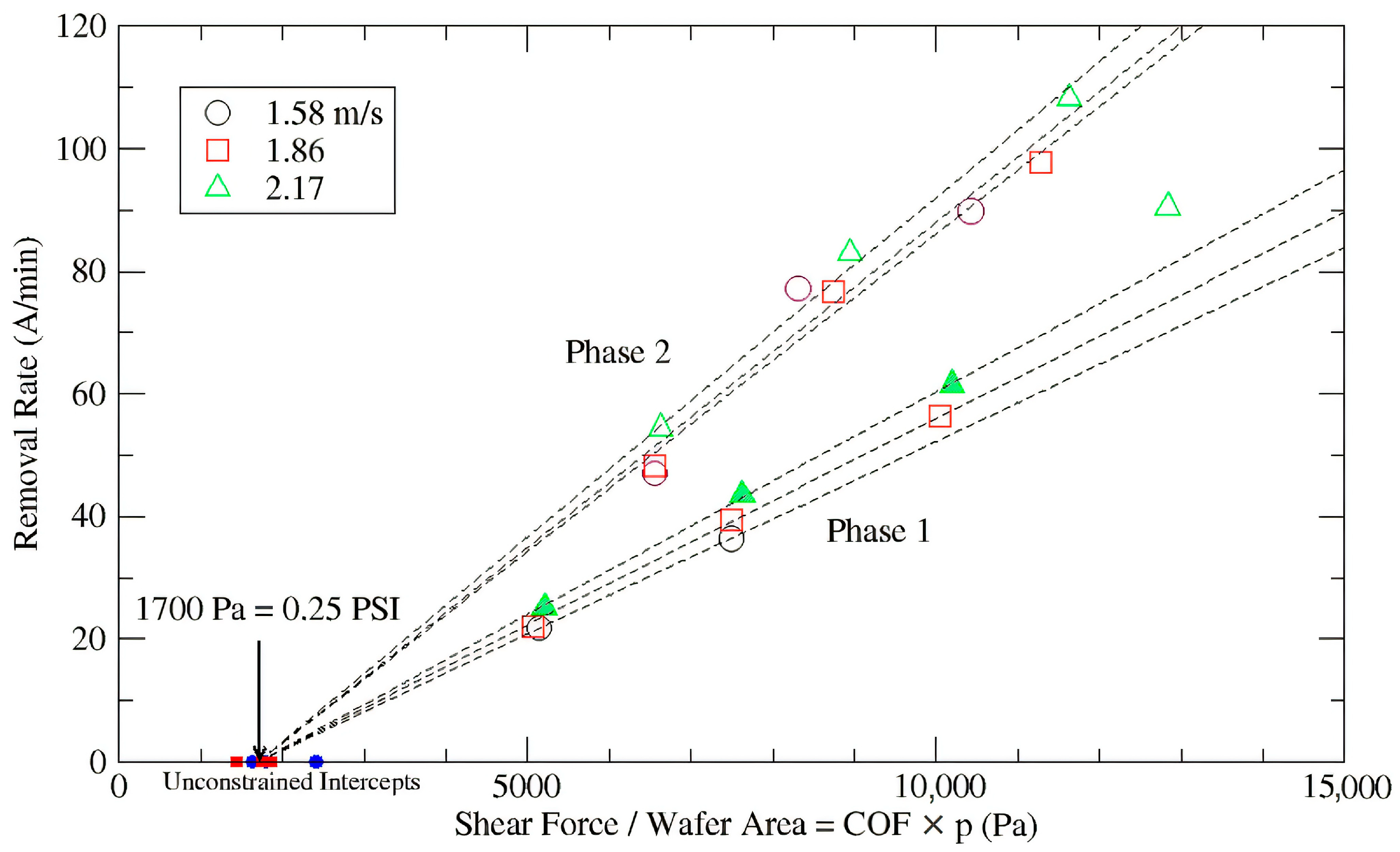

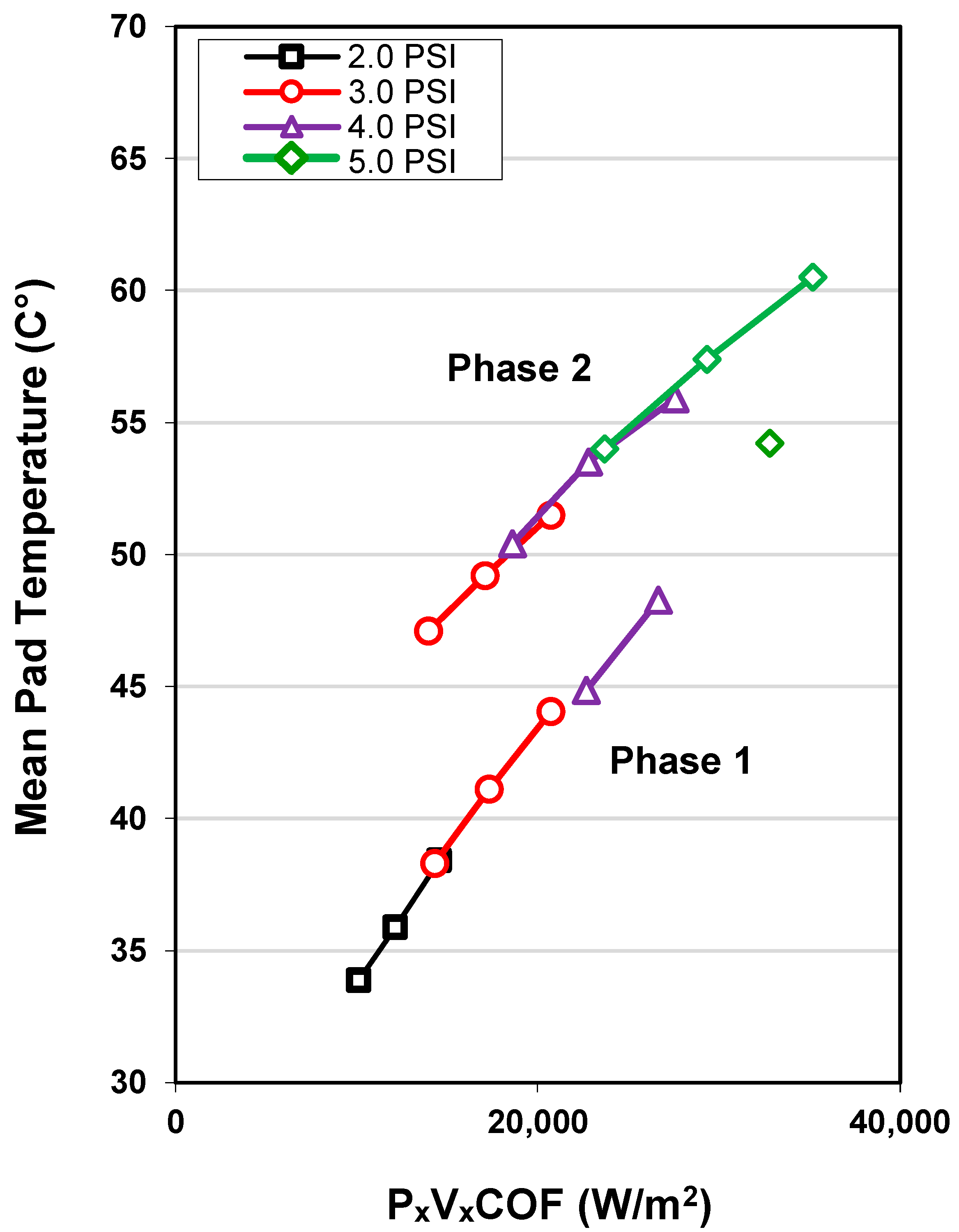

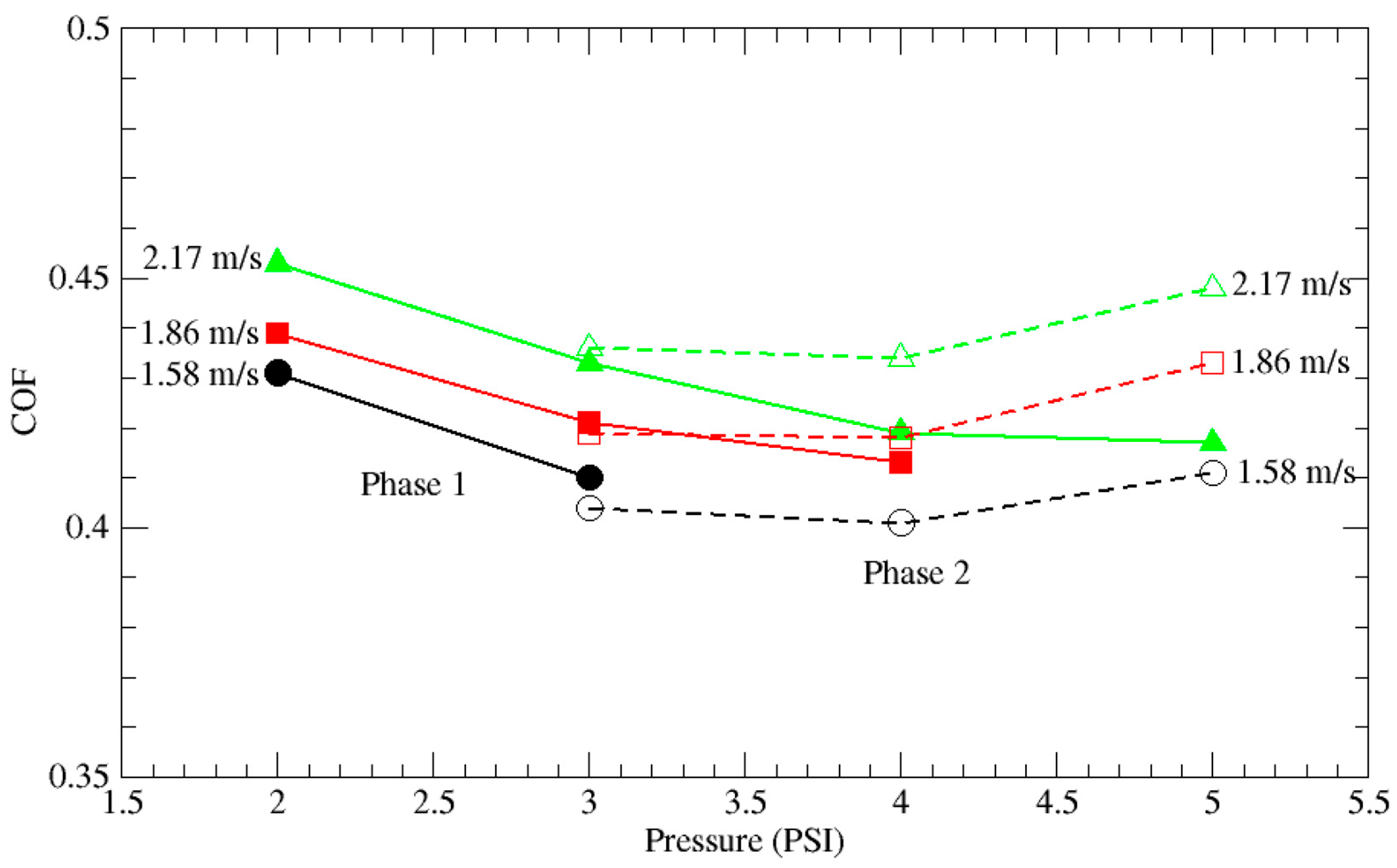

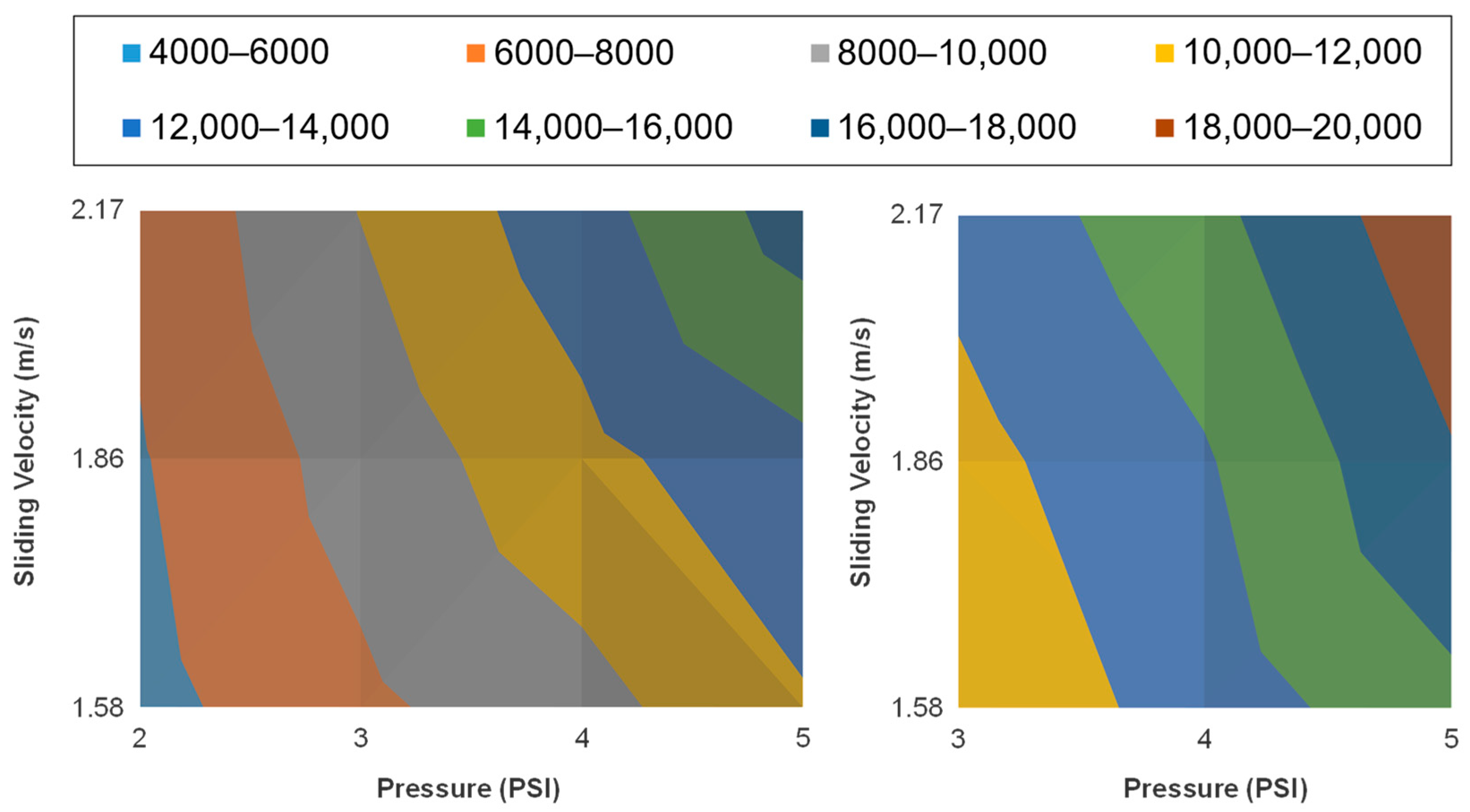

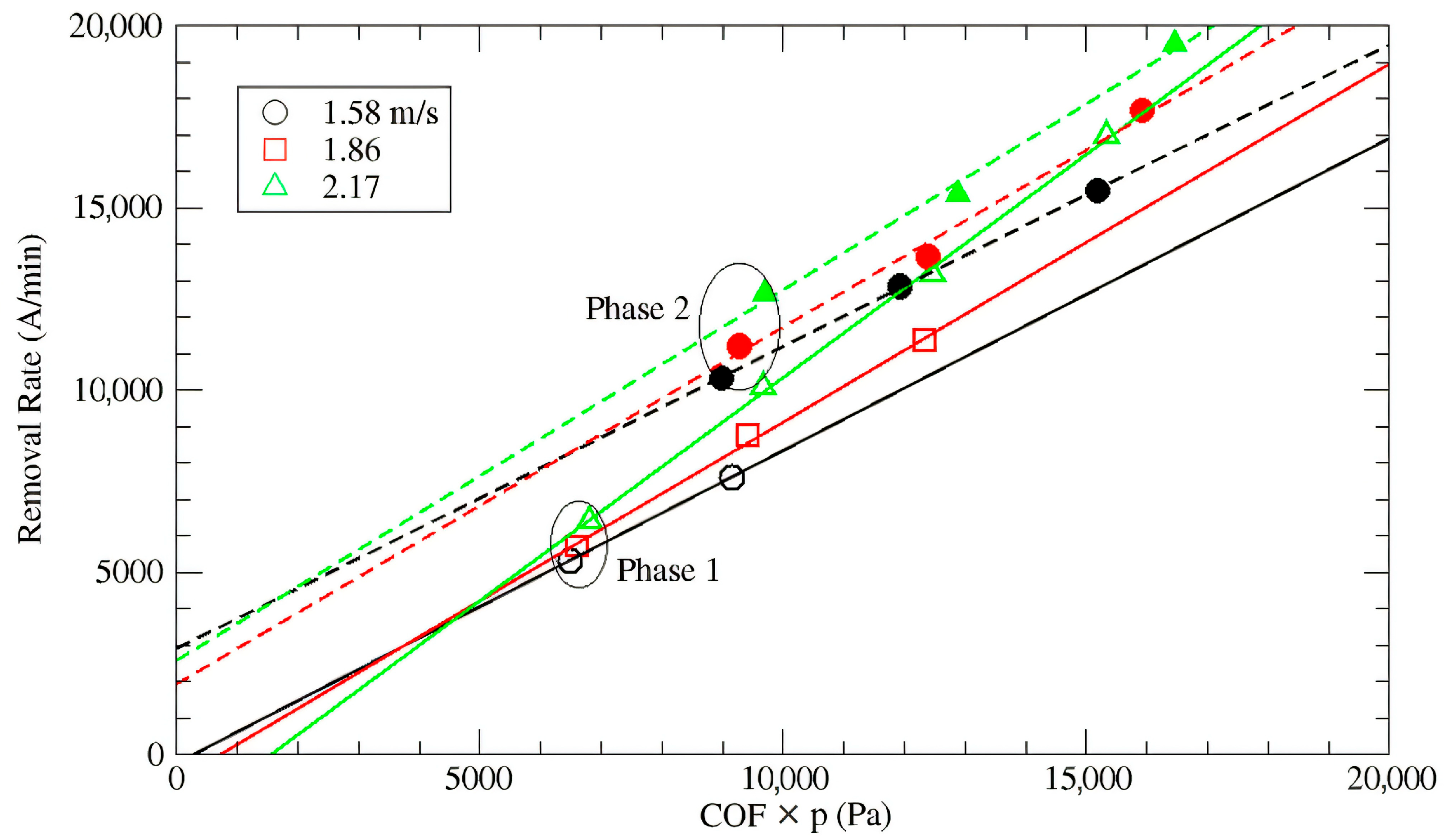

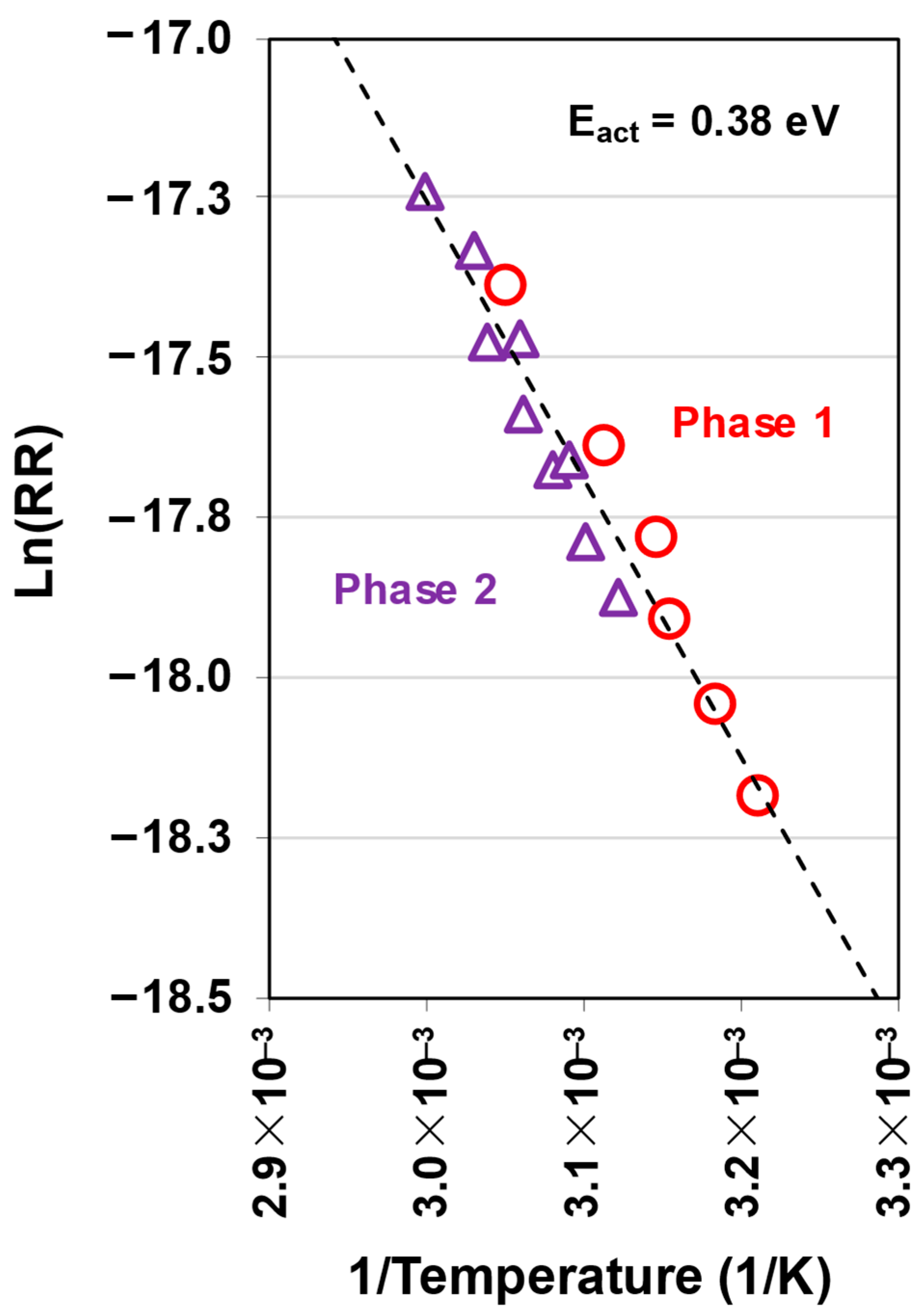

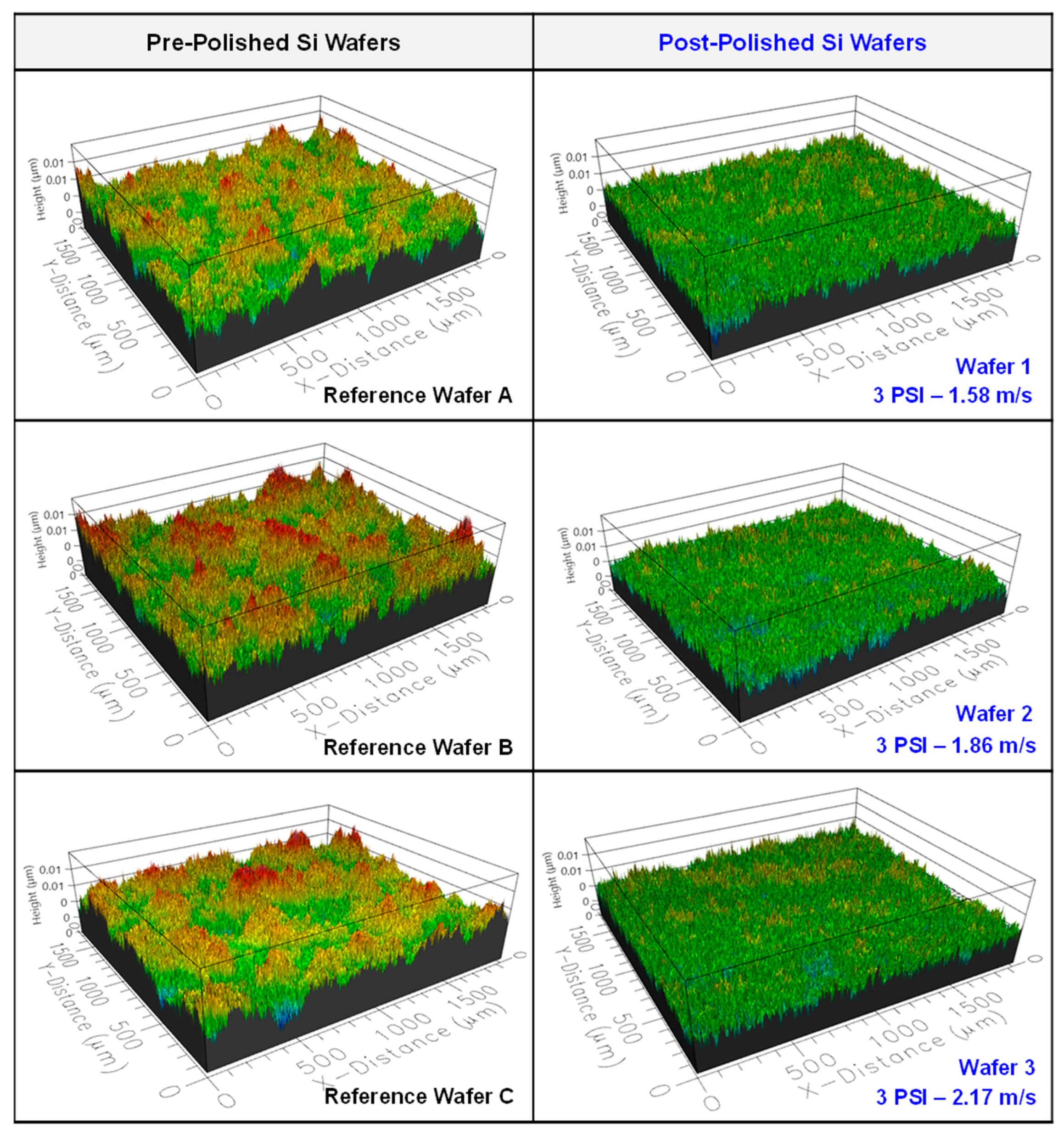

3.1. Native Oxide Polishing

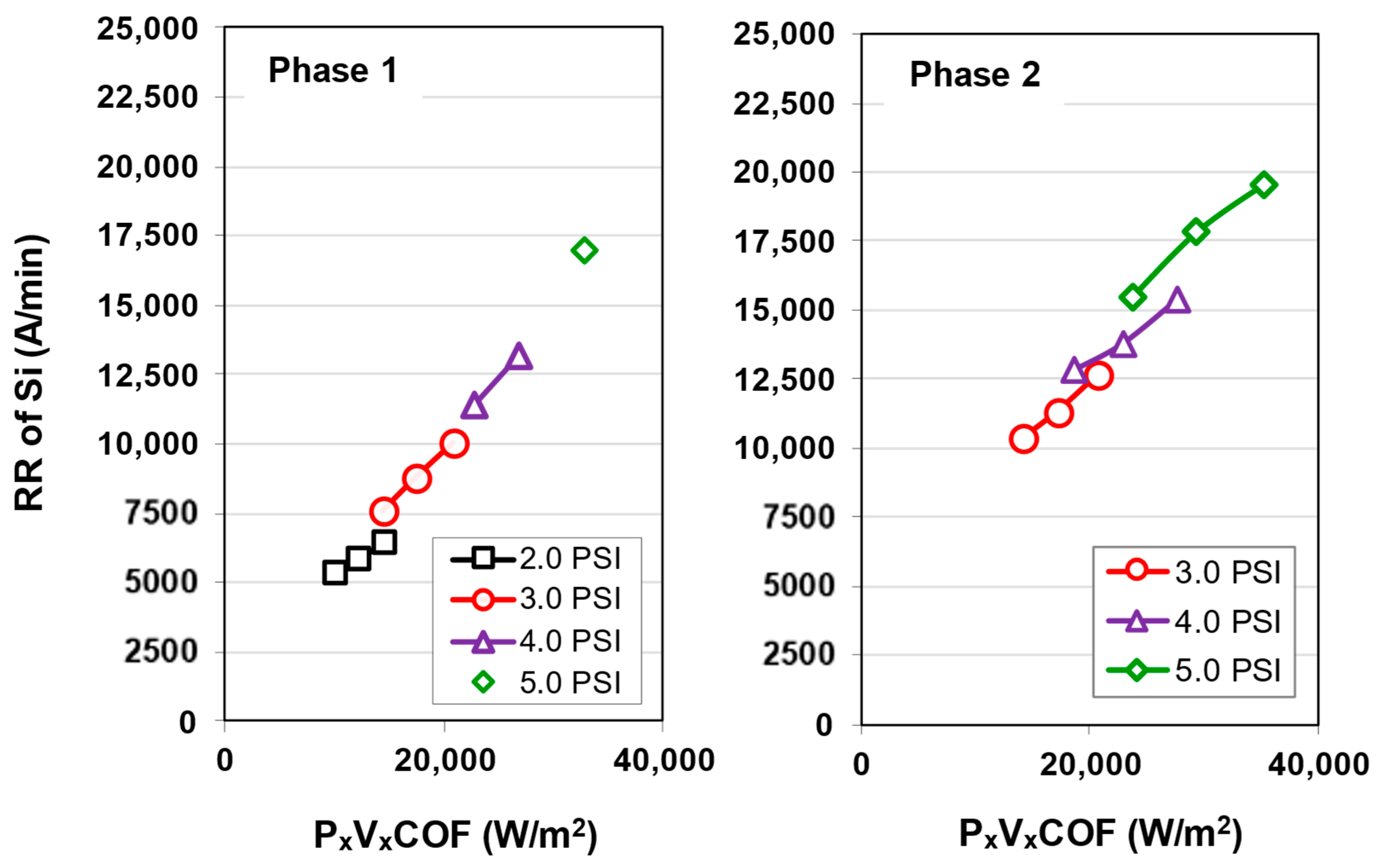

3.2. Silicon Polishing

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Steigerwald, J.; Murarka, S.; Gutmann, R. Chemical Mechanical Planarization of Microelectronic Materials; Wiley: New York, NY, USA, 2008. [Google Scholar]

- Oliver, M.R. Chemical-Mechanical Planarization of Semiconductor Materials; Springer: New York, NY, USA, 2003. [Google Scholar]

- Chen, C.; Shu, L.; Lee, S. Mechano-Chemical Polishing of Silicon Wafers. J. Mater. Process. Technol. 2003, 140, 373–378. [Google Scholar] [CrossRef]

- Wang, Y.G.; Zhang, L.C.; Biddut, A. Chemical Effect on the Material Removal rate in the CMP of Silicon Wafers. Wear 2011, 270, 312–316. [Google Scholar] [CrossRef]

- Srivastava, M.; Singh, J.; Mishra, D.; Singh, R. Review on the Various Strategies Adopted for the Polishing of Silicon Wafer—A Chemical Perspective. Mater. Today Proc. 2022, 63, 62–68. [Google Scholar] [CrossRef]

- Hong, J.; Niu, X.; Liu, Y.; Wang, C.; Zhang, B.; Sun, M.; Wang, J.; Han, L.; Zhang, W. Removal Rate and Surface Quality of the GLSI Silicon Substrate during the CMP Process. Microelectron. Eng. 2017, 168, 76–81. [Google Scholar] [CrossRef]

- Teichert, C.; MacKay, J.F.; Savage, D.E.; Lagally, M.G.; Brohl, M.; Wagner, P. Comparison of Surface Roughness of Polished Silicon Wafers Measured by Light Scattering Topography, Soft-X-Ray Scattering, and Atomic-force Microscopy. Appl. Phys. Lett. 1995, 66, 2346–2348. [Google Scholar] [CrossRef]

- Yasseen, A.A.; Mourla, N.J.; Mehregan, M. Chemical-Mechanical Polishing for Polysilicon Surface Micromachining. J. Electrochem. Soc. 1997, 144, 237. [Google Scholar] [CrossRef]

- Park, J.; Prasad, Y.; Kang, Y.; Kim, I.; Hong, Y.; Han, S.; Yun, S.; Yoo, B.; Busnaina, A. Effect of Polysilicon Wettability on Polishing and Organic Defects during CMP. J. Electrochem. Soc. 1999, 156, H869. [Google Scholar] [CrossRef]

- Chao, T.; Penigalapati, D.; Yang, J.; Huang, H.; Koli, D. The Role of Polysilicon Slurry and Its Application in 7nm CMP. ECS Trans. 2017, 77, 227. [Google Scholar] [CrossRef]

- Jeon, S.; Hong, J.; Hong, S.; Kanade, C.; Park, K.; Seok, H.; Kim, H.; Lee, S.; Kim, T. Investigation of Abrasive-free Slurry for Polysilicon Buffing Chemical Mechanical Planarization. Mater. Sci. Semicond. Process. 2021, 128, 105755. [Google Scholar] [CrossRef]

- Joshi, V.; Orlov, A.; Snider, G. Controlled Chemical Mechanical Polishing of Polysilicon and Silicon Dioxide for single-electron Device. J. Vac. Sci. Technol. A 2007, 25, 1034–1037. [Google Scholar] [CrossRef]

- Pirayesh, H.; Cadien, K. The Effect of Slurry Properties on the CMP Removal Rate of Boron Doped Polysilicon. ECS J. Solid State Sci. Technol. 2016, 5, P233. [Google Scholar] [CrossRef]

- Huang, H.; Koli, D.; Zhang, J.; Tsai, S.; Chao, T.; Lu, Y.; Kim, H.; Fang, Q.; Lu, W. New CMP Processes Development and Challenges for 7nm and Beyond. In Proceedings of the 2018 China Semiconductor Technology International Conference (CSTIC), Shanghai, China, 11–12 March 2018; pp. 1–5. [Google Scholar]

- Pirayesh, H.; Cadien, K. High Rate Chemical Mechanical Polishing of Boron-Doped Polycrystalline Silicon. ECS J. Solid State Sci. Technol. 2014, 3, P213. [Google Scholar] [CrossRef]

- Bao, S.; Wang, Y.; Lina, K.; Zhang, L.; Wang, B.; Sasangka, W.; Lee, K.; Chua, S.; Michel, J.; Fitzgerald, E.; et al. A Review of Silicon-based Wafer Bonding Processes, an Approach to Realize the Monolithic Integration of Si-CMOS and III–V-on-Si Wafers. J. Semicond. 2021, 42, 023106. [Google Scholar] [CrossRef]

- Park, S.; Yoon, S.; Kim, H.; Jeong, H. A Hybrid Polysilicon Planarization for Suppressing Dishing Defects. J. Mater. Process. Technol. 2012, 212, 2635–2641. [Google Scholar] [CrossRef]

- Masteika, V.; Kowal, J.; Braithwaite, N.; Rogers, T. A Review of Hydrophilic Silicon Wafer Bonding. ECS J. Solid State Sci. Technol. 2014, 3, Q42. [Google Scholar] [CrossRef]

- He, R.; Fujino, M.; Yamauchi, A.; Suga, T. Novel Hydrophilic SiO2 Wafer Bonding Using Combined Surface-activated Bonding Technique. Jpn. J. Appl. Phys. 2015, 54, 030218. [Google Scholar] [CrossRef]

- Wang, X.; Wang, C.; Zhu, M.; Zhou, J.; Luo, C.; Chen, Z.; Yang, X.; Wang, H.; Zhang, X. Insight on Surface Changes Post Chemical Mechanical Polishing (CMP) of the Silicon Substrate by Adding Polyoxyethylene Ether. ECS J. Solid State Sci. Technol. 2023, 12, 114005. [Google Scholar] [CrossRef]

- Philipossian, A. The Activity of HF/H2O Treated Silicon Surfaces in Ambient Air Before and After Gate Oxidation. J. Electrochem. Soc. 1992, 139, 2956. [Google Scholar] [CrossRef]

- Morita, M.; Ohmi, T.; Hasegawa, E.; Kawakami, M.; Ohwada, M. Growth of Native Oxide on a Silicon Surface. J. Appl. Phys. 1990, 68, 1272–1281. [Google Scholar] [CrossRef]

- Taft, E. Growth of Native Oxide on Silicon. J. Electrochem. Soc. 1998, 135, 1022. [Google Scholar] [CrossRef]

- Grundner, M.; Jacob, H. Investigations on Hydrophilic and Hydrophobic Silicon (100) Wafer Surfaces by X-ray Photoelectron and High-resolution Electron Energy Loss-spectroscopy. Appl. Phys. A 1986, 39, 73–82. [Google Scholar] [CrossRef]

- Raider, S.; Fitsch, R.; Palmer, M. Oxide Growth on Etched Silicon in Air at Room Temperature. J. Electrochem. Soc. 1975, 122, 413. [Google Scholar] [CrossRef]

- Li, F.; Balazs, M.; Anderson, S. Effects of Ambient and Dissolved Oxygen Concentration in Ultrapure Water on Initial Growth of Native Oxide on a Silicon (100) Surface. J. Electrochem. Soc. 2005, 152, G669. [Google Scholar] [CrossRef]

- Morita, M.; Ohmi, T.; Hasegawa, E.; Kawakami, M.; Suma, K. Control Factor of Native Oxide Growth on Silicon in Air or in Ultrapure Water. Appl. Phys. Lett. 1989, 55, 562–564. [Google Scholar] [CrossRef]

- Shin, W.; Cho, H.; Lee, H.; Jeong, H. Effect of Native Oxide on Polycrystalline Silicon CMP. J. Korean Phys. Soc. 2009, 54, 1077. [Google Scholar] [CrossRef]

- Venkatesh, R.; Prasad, Y.; Kwon, T.; Kang, Y.; Park, J. Effect of Alkaline pH on Polishing and Etching of Single and Polycrystalline Silicon. Jpn. J. Appl. Phys. 2012, 51, 071301. [Google Scholar] [CrossRef]

- Park, J.; Venkatesh, R.; Kwon, T. Material Removal Mechanism of Single and Polycrystalline Silicon in Alkaline Slurry. ECS Trans. 2013, 52, 545. [Google Scholar] [CrossRef]

- Sampurno, Y. Fundamental Consumables Characterization of Advanced Dielectric and Metal Chemical Mechanical Planarization Processes. Ph.D. Dissertation, University of Arizona, Tucson, AZ, USA, 2008. [Google Scholar]

- APD-800 Prime® Polisher and Tribometer for R&D and Low-Volume Manufacturing. Available online: https://aracainc.com/wp-content/uploads/2023/10/APD-800-Prime-Brochure-2023.pdf (accessed on 28 October 2024).

- Borucki, L.; Sampurno, Y.; Philipossian, A. Pad-Wafer-Slurry Interface Information from Force Data. ECS J. Solid State Sci. Technol. 2019, 8, P3133–P3144. [Google Scholar] [CrossRef]

- Meled, A. Optimization of Polishing Kinematics and Consumables During Chemical Mechanical Planarization Processes. Ph.D. Dissertation, University of Arizona, Tucson, AZ, USA, 2011. [Google Scholar]

- Han, R. Fundamental Characterization of Chemical Mechanical Planarization Relating to Slurry Dispensing and Conditioning Method. Ph.D. Dissertation, University of Arizona, Tucson, AZ, USA, 2017. [Google Scholar]

- Polar Series Accel 500 LC Cooling/Heating Recirculating Chillers. Available online: https://www.thermofisher.com/order/catalog/product/223322100 (accessed on 28 October 2024).

- Sampurno, Y.; Gu, X.; Nemoto, T.; Zhuang, Y.; Teramoto, A.; Philipossian, A.; Ohmi, T. End-Point Detection of Ta/TaN Chemical Mechanical Planarization via Forces Analysis. Jpn. J. Appl. Phys. 2010, 49, 05FC01. [Google Scholar] [CrossRef]

- Sampurno, Y.; Sudargho, F.; Zhuang, Y.; Ashizawa, T.; Morishima, H.; Philipossian, A. Pattern Evolution in Shallow Trench Isolation Chemical Mechanical Planarization via Real-Time Shear and Down Forces Spectral Analyses. Microelectron. Eng. 2011, 88, 2857–2861. [Google Scholar] [CrossRef]

- Mariscal, J.; McAllister, J.; Sampurno, Y.; Suarez, J.; O’Neill, M.; Zhou, H.; Grief, M.; Slutz, D.; Philipossian, A. Tribological, Thermal and Kinetic Characterization of SiO2 and Si3N4 Polishing for STI CMP on Blanket and Patterned Wafers. ECS J. Solid State Sci. Technol. 2020, 9, 044008. [Google Scholar] [CrossRef]

- Preston, F.W. The Theory and Design of Plate Glass Polishing Machines. J. Soc. Glass Technol. 1927, 11, 214–256. [Google Scholar]

- Zhao, B.; Shi, E.G. Chemical Mechanical Polishing: Threshold Pressure and Mechanism. Electrochem. Solid State Lett. 1999, 2, 145–147. [Google Scholar] [CrossRef]

- Tseng, W.T.; Wang, Y.L. Re-examination of Pressure and Speed Dependences of Removal Rate during Chemical-Mechanical Polishing Processes. J. Electrochem. Soc. 1997, 144, L15. [Google Scholar] [CrossRef]

- Shi, E.G.; Zhao, B. Ordered Mesoporous Non-Oxide Materials. Appl. Phys. A 1997, 67, 249. [Google Scholar] [CrossRef]

- Sampurno, Y.; Borucki, L.; Zhuang, Y.; Misra, S.; Holland, K.; Boning, D.; Philipossian, A. Characterization of Thermoset and Thermoplastic Polyurethane Pads and Molded and Machined Grooving Methods for Oxide CMP Applications. Thin Solid Film. 2009, 517, 1719–1726. [Google Scholar] [CrossRef]

- Chen, T.; Chui, J.; Shieh, T. Glass Transition Behaviors of a Polyurethane Hard Segment based on 4,4‘-Diisocyanatodiphenylmethane and 1,4-Butanediol and the Calculation of Microdomain Composition. Macromolecules 1997, 30, 5068–5074. [Google Scholar] [CrossRef]

- Pugar, J.; Childs, C.; Huang, C.; Haider, K.; Washburn, N. Elucidating the Physicochemical Basis of the Glass Transition Temperature in Linear Polyurethane Elastomers with Machine Learning. J. Phys. Chem. B 2020, 124, 9722–9733. [Google Scholar] [CrossRef] [PubMed]

- Borucki, L.; Sampurno, Y.; Philipossian, A. A New Summit Heating Kinetic Model for Copper and Tungsten CMP. In Proceedings of the Symposium on Chemical-Mechanical Planarization (CAMP), Lake Placid, NY, USA, 11−14 August 2021. [Google Scholar]

- Lim, S.; Ashby, M. Wear-mechanism Maps. Acta Metall. 1987, 35, 1–24. [Google Scholar] [CrossRef]

- Williams, J. Wear Modeling: Analytical, Computational and Mapping: A Continiuum Mechanics Approach. Wear 1999, 225, 1–17. [Google Scholar] [CrossRef]

- Borucki, L.; Sampurno, Y.; Philipossian, A. The Shear Force Law: A Guide to Modeling CMP Removal Rates. ECS J. Solid State Sci. Technol. 2023, 12, 044003. [Google Scholar] [CrossRef]

- Tsou, C.; Huang, Y.S.; Li, H.C.; Lai, T.H. Determination of Thermal Expansion Coefficient of Thermal Oxide. Sens. Mater. 2005, 17, 441–451. [Google Scholar]

- Philipossian, A.; Sampurno, Y.; Redeker, F.; Cahue, K.; Keleher, J. Slurry Activation for Enhanced Surface Redox Reactions in CMP. Solid State Phenom. 2021, 346, 311–317. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yap, M.; Yap, C.; Sampurno, Y.; Whitener, G.; Keleher, J.; Borucki, L.; Philipossian, A. Tribological, Thermal, Kinetic, and Surface Microtextural Characterization of Prime p-Type <100> Silicon Wafer CMP for Direct Wafer Bonding Applications. Electron. Mater. 2025, 6, 1. https://doi.org/10.3390/electronicmat6010001

Yap M, Yap C, Sampurno Y, Whitener G, Keleher J, Borucki L, Philipossian A. Tribological, Thermal, Kinetic, and Surface Microtextural Characterization of Prime p-Type <100> Silicon Wafer CMP for Direct Wafer Bonding Applications. Electronic Materials. 2025; 6(1):1. https://doi.org/10.3390/electronicmat6010001

Chicago/Turabian StyleYap, Michelle, Catherine Yap, Yasa Sampurno, Glenn Whitener, Jason Keleher, Len Borucki, and Ara Philipossian. 2025. "Tribological, Thermal, Kinetic, and Surface Microtextural Characterization of Prime p-Type <100> Silicon Wafer CMP for Direct Wafer Bonding Applications" Electronic Materials 6, no. 1: 1. https://doi.org/10.3390/electronicmat6010001

APA StyleYap, M., Yap, C., Sampurno, Y., Whitener, G., Keleher, J., Borucki, L., & Philipossian, A. (2025). Tribological, Thermal, Kinetic, and Surface Microtextural Characterization of Prime p-Type <100> Silicon Wafer CMP for Direct Wafer Bonding Applications. Electronic Materials, 6(1), 1. https://doi.org/10.3390/electronicmat6010001