Reliability Improvement of 28 nm Intel FPGA Ring Oscillator PUF for Chip Identification

Abstract

1. Introduction

2. Background

2.1. Motivation

2.2. Related Works

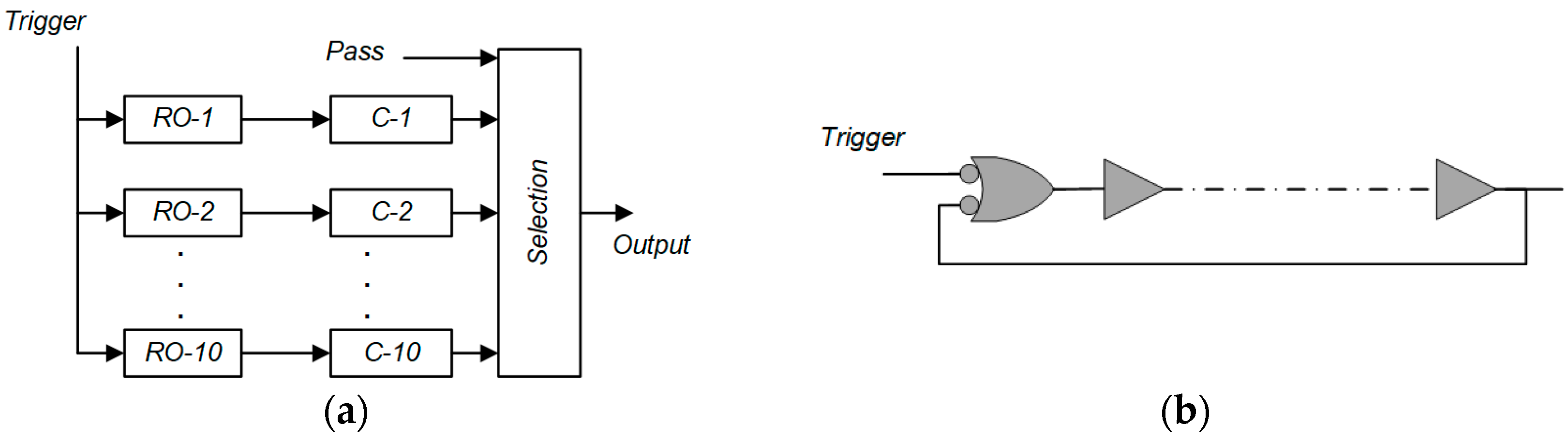

3. Ring Oscillator PUF Scheme

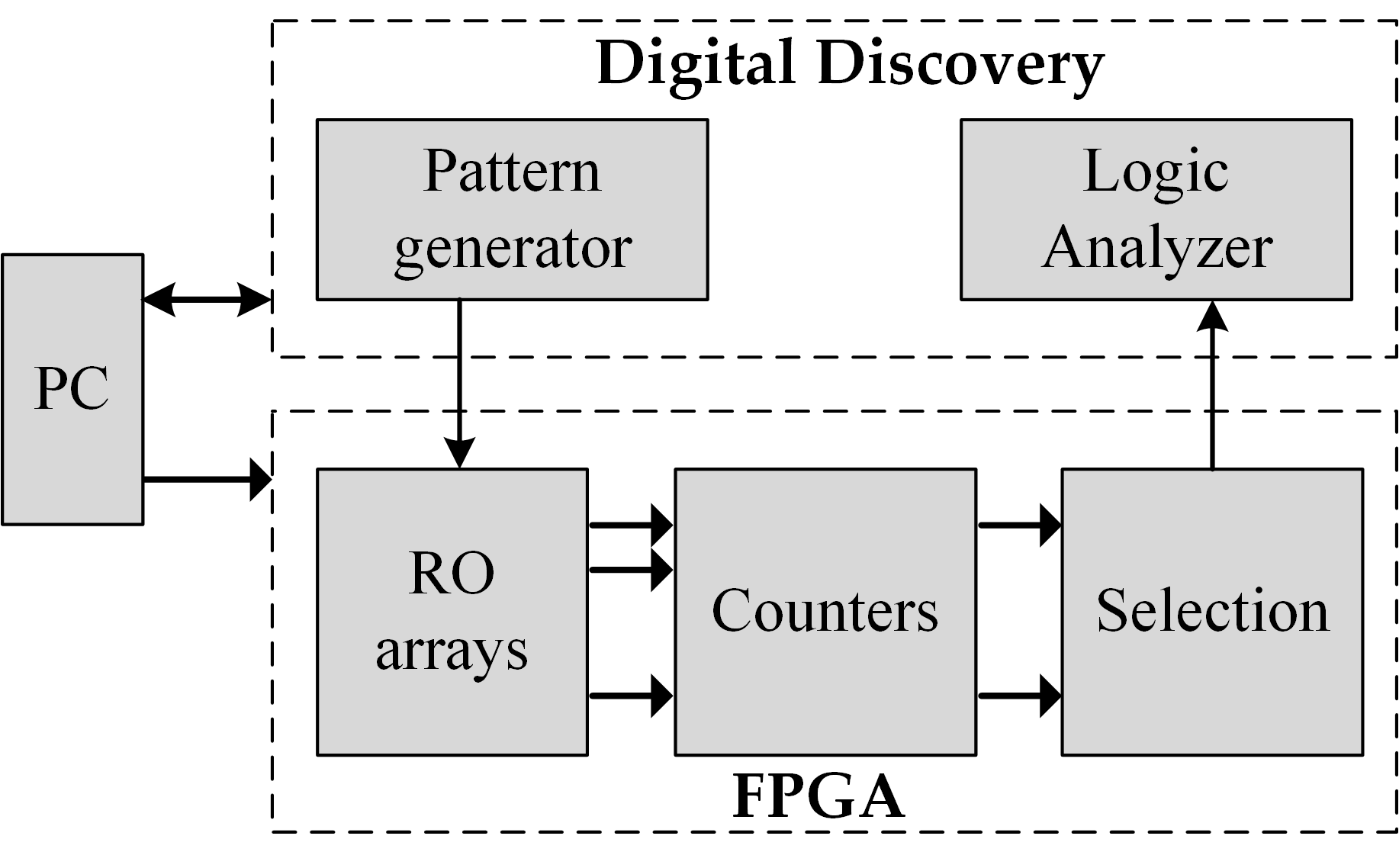

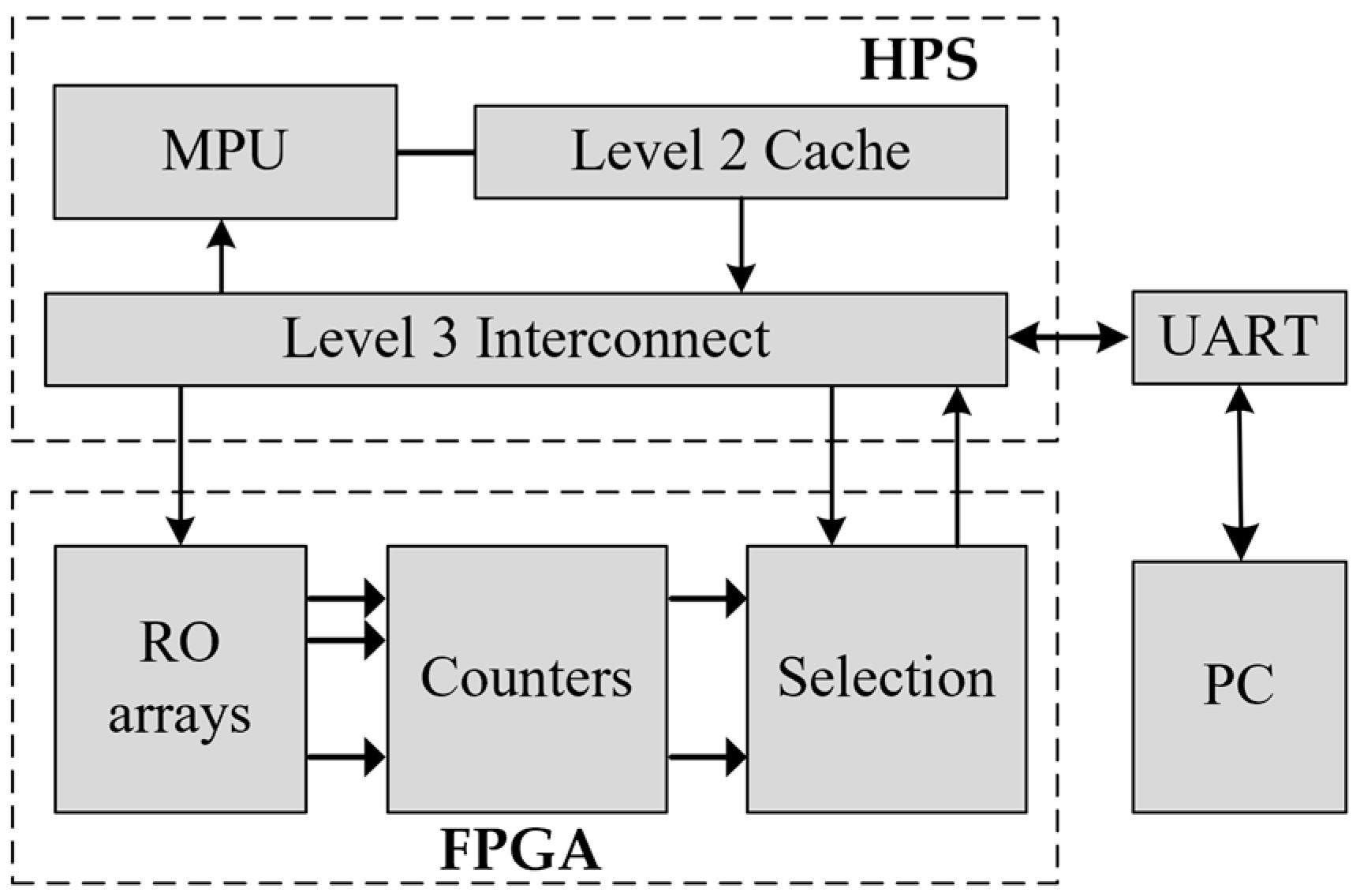

3.1. Frequency Measurement

3.2. Identity Characterization

3.3. Response Generation

3.4. Resource Utilization

4. Evaluation and Stability Improvement Scenarios

4.1. PUF Metrics

4.2. Proposed Frequency Mapping

| Algorithm 1 Proposed step for frequency mapping |

| f_temp = [Initial f]; --reads frequencies and their position |

| f_sort = sortrows(f_temp,2); --sorts frequencies |

| f_dif = range(f)/(n − 1); --calculates average difference |

| f_sort(1,2) = min(f); --reads out minimum frequency |

| for p = 2: n |

| f_sort(p,2) = f_sort(p-1,2) + f_dif; --maps into new values |

| end |

| f_re_sort = sortrows(f_sort,1); --reposition frequencies to initial |

4.3. Proposed Response Generation

| Items | Specification/Condition |

|---|---|

| Chip | Cyclone V |

| Hard Processor | ARM Cortex A-9 |

| Lithography | 28 nm |

| No. of chips | 11 |

| Temperatures | 25 °C, 50 °C |

| Recorded frequency | 11,000 |

| RO placement | Fixed location |

| Routing hotspots | Uniform [16] |

| No. of ROs | Ten |

| Measurement tools | Pattern Generator, Logic Analyzer |

5. Results

5.1. Metric Evaluation

- Activate ROs during a specific time.

- Read counter values out of the chip.

- Convert the values into frequencies.

- Calculate Q values (Q2, Q3, … Qn−1).

- Set quantization level (ql).

- Generate response bits.

- Calculate uniqueness and reliability.

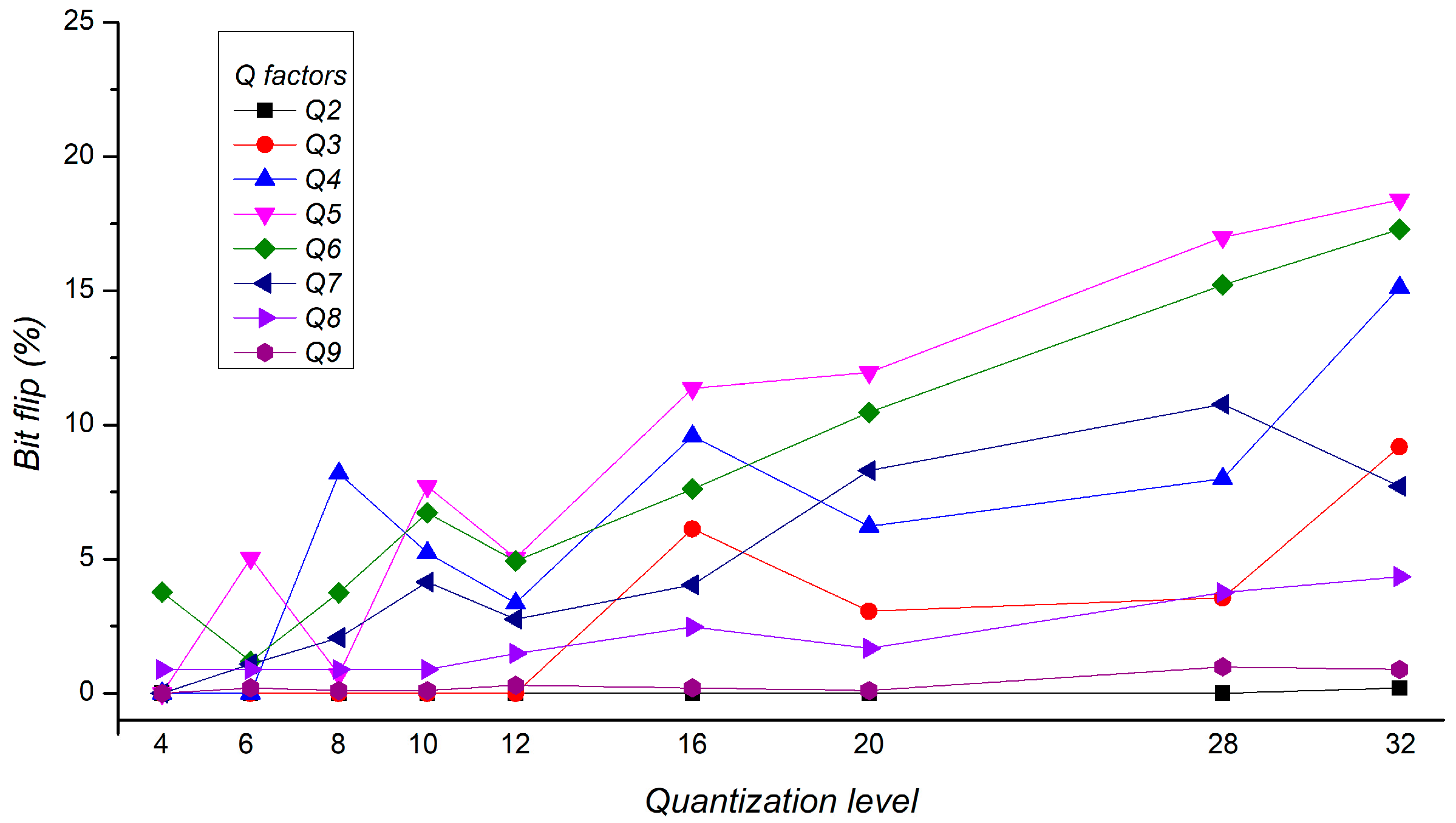

5.2. Bit Flip Contribution of Q

- Q2 and Q8: each 45 values.

- Q3 and Q7: each 120 values.

- Q4 and Q6: each 210 values.

- Q5: 252 values.

- Q9: 10 values.

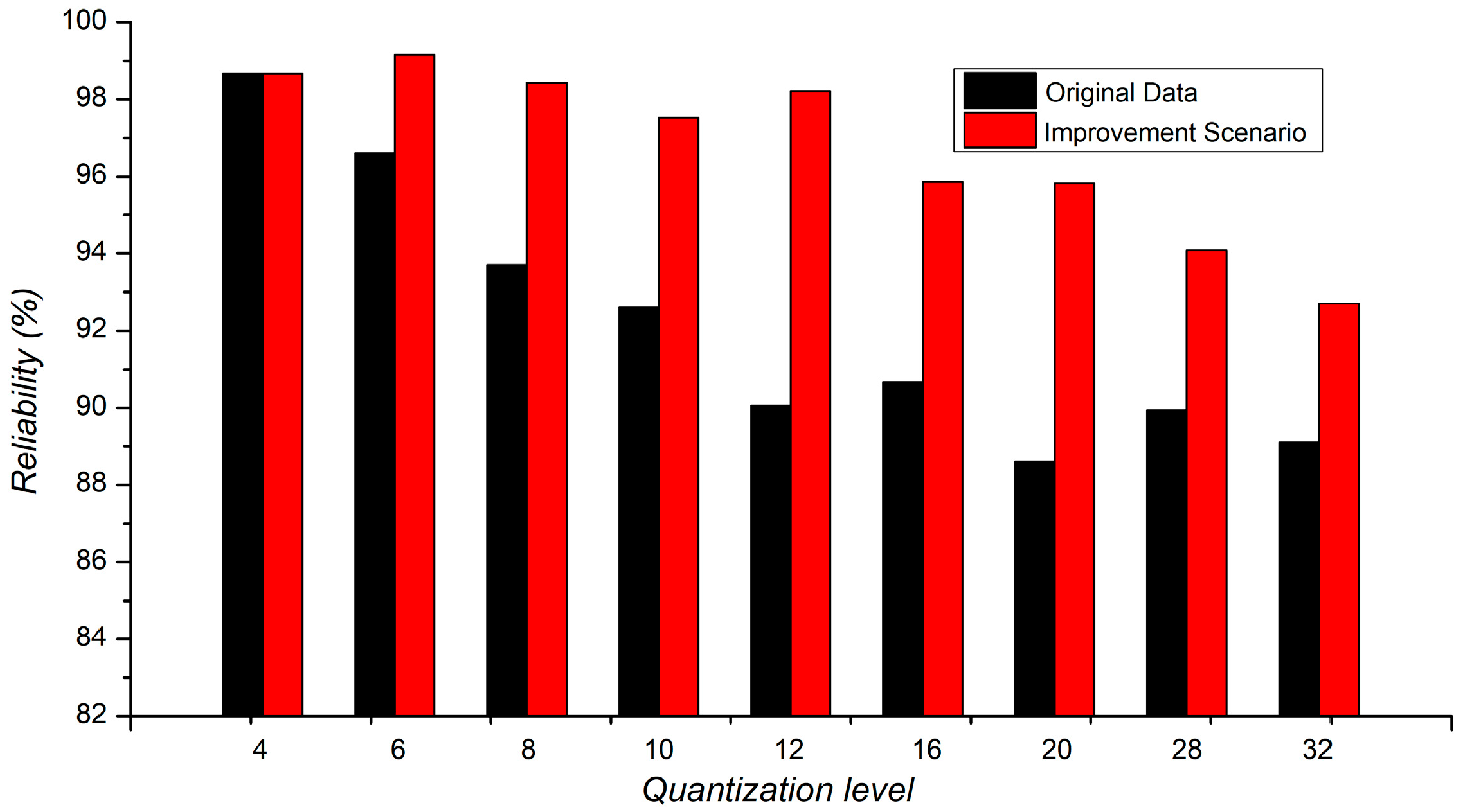

5.3. Improvement of Q

5.4. Improvement in Response

- Apply Q improvement using the proposed frequency mapping. As Qs are extracted to distinguish among chips, the shift in frequency difference between low and high temperatures causes lower reliability. The frequency mapping is proposed to uniformize frequency differences and improve Qs, as shown in Figure 7.

- Consider Qs that contribute fewer bit flips. Response bits are generated using several Qs, for instance, Q2, Q3, Q8, and Q9 (others are neglected). Exclusion is based on a detailed analysis, as can be seen in Figure 5, where Q4, Q5, and Q6 contribute a significant bit flip. The response is expected to be more immune to temperature change, even though this scenario produces fewer response bits.

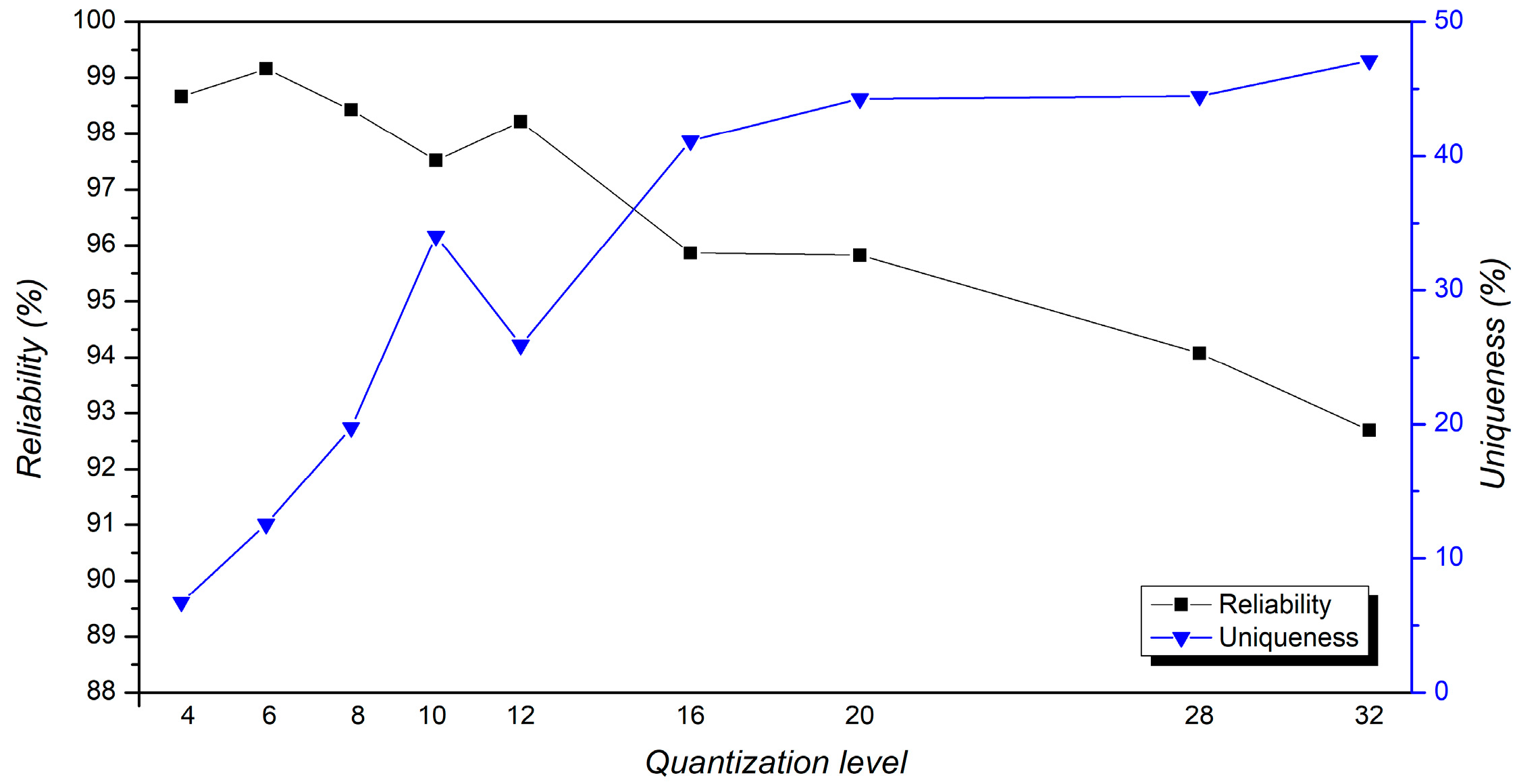

- Choose a quantization level that balances reliability and uniqueness. This work suggests generating responses using a quantization level of ql = 16. At this point, the reliability is around 95.8%, which is acceptable, and the uniqueness is approximately 42%. The score is also acceptable since the ideal uniqueness value is estimated using 11 chips, implying that uniqueness is less than 50% [22]. The selected quantization level affects responses when higher Q values are involved because the levels derived from a range of Q values shift.

5.5. Uniformity and Bit Aliasing

5.6. Performance Comparison

| Uniqueness (%) | Reliability (%) | Uniformity (%) | Bit Aliasing (%) | |

|---|---|---|---|---|

| Suh et al. [9], 2007 | 46.15 | 99.52 | - | - |

| Maiti et al. [10], 2009 | 35.91–45.90 | - | - | - |

| Xin et al. [33], 2011 | 32, 41 | 99.29 | - | - |

| Maiti et al. [17], 2011 | 49.99–50.07 | ±92 *, ±70 * | 50.02, 49.4 | 50.02, 49.4 |

| Feiten et al. [3], 2013 | 6.68–37.03 | 99.41–82.5 | 50.00, 62.07 | - |

| Sahoo et al. [4], 2013 | 47.57 | 90.70 ** | 47 | 14.95 |

| Kodytek et al. [24], 2016 | 48.42–48.74 | 98.22, 97.55 | - | - |

| Delavar et al. [18], 2016 | 49.81 | 96.07 | - | - |

| Chauhan et al. [25], 2019 | 49.9 | 97.85–99.80 | - | - |

| Deng et al. [26], 2020 | 49.95 | 91.4–99.13 * | 49.61 | - |

| Zulfikar et al. [14], 2021 | 50.18 # | 99.51 # | 47.55 | 62.98 |

| Martinez et al. [19], 2022 | 47.52–48.94 | 96.84−98.53 | - | - |

| This work | 42% # | 95.8% # | 56.97 # | 56.97 # |

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| RO-PUF | Ring Oscillator Physical Unclonable Function |

| CRP | Challenge and Response |

| FPGA | Field-Programmable Gate Array |

| PC | Personal Computer |

| UART | Universal Asynchronous Receiver/Transmitter |

| HPS | Hard Processor |

| HD | Hamming Distance |

| HW | Hamming Weight |

| AXI | Advanced eXtensible Interface |

Appendix A

| No. | Measurement (Pulse) | Frequency (MHz) | Proposed Freq. Mapping Frequency (MHz) | Q2 | Response |

|---|---|---|---|---|---|

| 1 | 434,405 | 434.405 | 436.8086667 | 1.086994 | 1 |

| 2 | 433,389 | 433.389 | 435.6271111 | 2.430592 | 1 |

| 3 | 440,266 | 440.266 | 442.7164444 | 2.173988 | 1 |

| 4 | 437,535 | 437.535 | 441.5348889 | 1.086994 | 1 |

| 5 | 434,414 | 434.414 | 437.9902222 | 1.882729 | 0 |

| 6 | 433,264 | 433.264 | 433.264 | 2.66258 | 1 |

| 7 | 443,898 | 443.898 | 443.898 | 1.882729 | 1 |

| 8 | 436,520 | 436.52 | 440.3533333 | 1.537241 | 1 |

| 9 | 433,556 | 433.556 | 434.4455556 | 1.537241 | 1 |

| 10 | 434,452 | 434.452 | 439.1717778 | 2.66258 | 0 |

| 11 | - | - | - | 2.430592 | 0 |

| 12 | - | - | - | 1.537241 | 1 |

| 13 | - | - | - | 1.537241 | 1 |

| 14 | - | - | - | 2.875915 | 0 |

| 15 | - | - | - | 2.173988 | 0 |

| 16 | - | - | - | 1.086994 | 1 |

| 17 | - | - | - | 1.882729 | 1 |

| 18 | - | - | - | 1.086994 | 1 |

| 19 | - | - | - | 2.173988 | 0 |

| 20 | - | - | - | 3.074483 | 0 |

| 21 | - | - | - | 1.086994 | 1 |

| 22 | - | - | - | 1.537241 | 1 |

| 23 | - | - | - | 2.875915 | 0 |

| 24 | - | - | - | 1.882729 | 1 |

| 25 | - | - | - | 1.882729 | 1 |

| 26 | - | - | - | 2.875915 | 0 |

| 27 | - | - | - | 1.537241 | 1 |

| 28 | - | - | - | 1.086994 | 1 |

| 29 | - | - | - | 2.66258 | 0 |

| 30 | - | - | - | 1.537241 | 1 |

| 31 | - | - | - | 2.173988 | 1 |

| 32 | - | - | - | 2.430592 | 0 |

| 33 | - | - | - | 1.537241 | 1 |

| 34 | - | - | - | 1.882729 | 1 |

| 35 | - | - | - | 1.086994 | 1 |

| 36 | - | - | - | 3.260981 | 0 |

| 37 | - | - | - | 2.66258 | 0 |

| 38 | - | - | - | 1.086994 | 1 |

| 39 | - | - | - | 2.430592 | 1 |

| 40 | - | - | - | 1.882729 | 1 |

| 41 | - | - | - | 3.074483 | 0 |

| 42 | - | - | - | 2.173988 | 0 |

| 43 | - | - | - | 2.430592 | 1 |

| 44 | - | - | - | 1.086994 | 1 |

| 45 | - | - | - | 2.173988 | 1 |

References

- Halak, B. Physically Unclonable Functions: From Basic Design Principles to Advanced Hardware Security Applications; Springer: Berlin/Heidelberg, Germany, 2018. [Google Scholar]

- Maes, R. Physically Unclonable Functions: Constructions, Properties and Applications; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2013. [Google Scholar]

- Feiten, L.; Spilla, A.; Sauer, M.; Schubert, T.; Becker, B. Implementation and analysis of ring oscillator PUFs on 60 nm Altera Cyclone FPGAs. Inf. Secur. J. Glob. Perspect. 2013, 22, 265–273. [Google Scholar] [CrossRef]

- Sahoo, D.P.; Mukhopadhyay, D.; Chakraborty, R.S. Design of low area-overhead ring oscillator PUF with large challenge space. In Proceedings of the 2013 International Conference on Reconfigurable Computing and FPGAs (ReConFig), Cancun, Mexico, 9–11 December 2013; pp. 1–6. [Google Scholar]

- Karmakar, M.; Naz, S.F.; Shah, A.P. Fault-tolerant reversible logic gate-based RO-PUF design. Mem.-Mater. Devices Circuits Syst. 2023, 4, 100055. [Google Scholar] [CrossRef]

- Zhu, Y.; Fang, Y.; Hu, X.; Yang, R. Design and FPGA Implementation of a Password Management System Utilizing RO PUF. In Proceedings of the 2024 5th International Seminar on Artificial Intelligence, Networking and Information Technology (AINIT), Nanjang, China, 29–31 March 2024; pp. 303–307. [Google Scholar]

- Khan, S.; Shah, A.P.; Gupta, N.; Chouhan, S.S.; Pandey, J.G.; Vishvakarma, S.K. An ultra-low power, reconfigurable, aging resilient RO PUF for IoT applications. Microelectron. J. 2019, 92, 104605. [Google Scholar] [CrossRef]

- Abulibdeh, E.; Saleh, H.; Mohammad, B.; Al-Qutayri, M.; Santikellur, P. Boosted PUF: Boosting Efficiency and Resilience in Configurable RO PUF for IoT Devices. TechRxiv 2024. [Google Scholar]

- Suh, G.E.; Devadas, S. Physical unclonable functions for device authentication and secret key generation. In Proceedings of the DAC07: The 44th Design Automation Conference, San Diego, CA, USA, 4–8 June 2007; pp. 9–14. [Google Scholar]

- Maiti, A.; Schaumont, P. Improving the quality of a physical unclonable function using configurable ring oscillators. In Proceedings of the 2009 International Conference on Field Programmable Logic and Applications, Prague, Czech Republic, 31 August–2 September 2009; pp. 703–707. [Google Scholar]

- Yin, C.-E.; Qu, G. Obtaining statistically random information from silicon physical unclonable functions. IEEE Trans. Emerg. Top. Comput. 2014, 2, 96–106. [Google Scholar] [CrossRef]

- Giechaskiel, I.; Rasmussen, K.B.; Eguro, K. Leaky Wires: Information Leakage and Covert Communication Between FPGA Long Wires. In Proceedings of the 2018 on Asia Conference on Computer and Communications Security, Incheon, Republic of Korea, 4 June 2018; pp. 15–27. [Google Scholar]

- Ikeda, M.; Kang, H.; Iwamura, K. Direct challenge ring oscillator PUF (DC-ROPUF) with novel response selection. In Proceedings of the 2017 IEEE 6th Global Conference on Consumer Electronics (GCCE), Las Vegas, NV, USA, 24–27 October 2017; pp. 1–2. [Google Scholar]

- Zulfikar, Z.; Soin, N.; Wan Muhamad Hatta, S.F.; Abu Talip, M.S.; Jaafar, A. Routing density analysis of area-efficient ring oscillator physically unclonable functions. Appl. Sci. 2021, 11, 9730. [Google Scholar] [CrossRef]

- Merli, D.; Stumpf, F.; Eckert, C. Improving the quality of ring oscillator PUFs on FPGAs. In Proceedings of the 5th Workshop on Embedded Systems Security, Scottdale, AZ, USA, 24 October 2010; pp. 1–9. [Google Scholar]

- Zulfikar, Z.; Soin, N.; Wan Muhamad Hatta, S.F.; Abu Talip, M.S. Runtime analysis of area-efficient uniform RO-PUF for uniqueness and reliability balancing. Electronics 2021, 10, 2504. [Google Scholar] [CrossRef]

- Maiti, A.; Kim, I.; Schaumont, P. A robust physical unclonable function with enhanced challenge-response set. IEEE Trans. Inf. Forensics Secur. 2011, 7, 333–345. [Google Scholar] [CrossRef]

- Delavar, M.; Mirzakuchaki, S.; Mohajeri, J. A ring oscillator-based PUF with enhanced challenge-response pairs. Can. J. Electr. Comput. Eng. 2016, 39, 174–180. [Google Scholar] [CrossRef]

- Martínez-Rodríguez, M.C.; Rojas-Muñoz, L.F.; Camacho-Ruiz, E.; Sánchez-Solano, S.; Brox, P. Efficient RO-PUF for generation of identifiers and keys in resource-constrained embedded systems. Cryptography 2022, 6, 51. [Google Scholar] [CrossRef]

- Zulfikar, Z.; Soin, N.; Hatta, S.W.M.; Talip, M.S.A.; bin Jaafar, A. Uniformizing Routing Hotspots of Ring Oscillators on the Cyclone V FPGA for PUF Applications. In Proceedings of the 2019 IEEE Regional Symposium on Micro and Nanoelectronics (RSM), Putrajaya, Malaysia, 21–23 August 2019; pp. 176–179. [Google Scholar]

- Feiten, L.; Sauer, M.; Becker, B. Implementation of Delay-Based PUFs on Altera FPGAs. In Hardware Security and Trust; Springer: Berlin/Heidelberg, Germany, 2017; pp. 211–235. [Google Scholar]

- Maiti, A.; Schaumont, P. Improved ring oscillator PUF: An FPGA-friendly secure primitive. J. Cryptol. 2011, 24, 375–397. [Google Scholar] [CrossRef]

- Lopes, R.H.; Reid, I.; Hobson, P.R. The Two-Dimensional Kolmogorov-Smirnov Test; Proceedings of Science: Treste, Italy, 2007. [Google Scholar]

- Kodýtek, F.; Lórencz, R.; Buček, J. Improved ring oscillator PUF on FPGA and its properties. Microprocess. Microsyst. 2016, 47, 55–63. [Google Scholar] [CrossRef]

- Chauhan, A.S.; Sahula, V.; Mandal, A.S. Novel randomized placement for FPGA based robust ROPUF with improved uniqueness. J. Electron. Test. 2019, 35, 581–601. [Google Scholar] [CrossRef]

- Deng, D.; Hou, S.; Wang, Z.; Guo, Y. Configurable ring oscillator PUF using hybrid logic gates. IEEE Access 2020, 8, 161427–161437. [Google Scholar] [CrossRef]

- Maiti, A.; Gunreddy, V.; Schaumont, P. A systematic method to evaluate and compare the performance of physical unclonable functions. In Embedded Systems Design with FPGAs; Springer: Berlin/Heidelberg, Germany, 2013; pp. 245–267. [Google Scholar]

- Abulibdeh, E.; Saleh, H.; Mohammad, B.; Al-Qutayri, M.; Hussain, A. Kernel-based response extraction approach for efficient configurable ring oscillator PUF. Sci. Rep. 2025, 15, 5938. [Google Scholar] [CrossRef] [PubMed]

- Hsieh, M.-H.; Huang, Y.-C.; Yew, T.-Y.; Wang, W.; Lee, Y.-H. The impact and implication of BTI/HCI decoupling on ring oscillator. In Proceedings of the 2015 IEEE International Reliability Physics Symposium, Monterey, CA, USA, 13–23 April 2015; pp. 6A. 4.1–6A. 4.5. [Google Scholar]

- Karimi, N.; Danger, J.-L.; Guilley, S. Impact of aging on the reliability of delay PUFs. J. Electron. Test. 2018, 34, 571–586. [Google Scholar] [CrossRef]

- Maiti, A.; Schaumont, P. The impact of aging on a physical unclonable function. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2013, 22, 1854–1864. [Google Scholar] [CrossRef]

- Bernard, F.; Fischer, V.; Costea, C.; Fouquet, R. Implementation of ring-oscillators-based physical unclonable functions with independent bits in the response. Int. J. Reconfigurable Comput. 2012, 2012, 13. [Google Scholar] [CrossRef]

- Xin, X.; Kaps, J.-P.; Gaj, K. A configurable ring-oscillator-based PUF for Xilinx FPGAs. In Proceedings of the 2011 14th Euromicro Conference on Digital System Design, Oulu, Finland, 31 August–2 September 2011; pp. 651–657. [Google Scholar]

| Author | No. of CRPs | CRP Enhance/Location |

|---|---|---|

| Suh et al. [9] | n/8 | no/inside chip |

| Maiti et al. [10] | n − 1 | no/inside chip |

| Merli et al. [15] | n/2 | no/inside chip |

| Maiti et al. [17] | 2n − n − 1 | yes/outside chip |

| Yin et al. [11] | log2 n! | no/inside chip |

| Delavar et. al. [18] | 2n − 1 | yes/outside chip |

| Zulfikar et al. [14] | n!/2(n − 2)! | yes/inside or outside |

| This work | nC2 + nC3 | yes/outside chip |

| Factor Q | Mathematical Expressions | ||

|---|---|---|---|

| Subtraction | Power/Square | Summation | |

| Q2 | 1 | 1 | 0 |

| Q3 | 3 | 3 | 2 |

| Q4 | 6 | 6 | 5 |

| Q5 | 10 | 10 | 9 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zulfikar, Z.; Walidainy, H.; Rahman, A.; Muchtar, K. Reliability Improvement of 28 nm Intel FPGA Ring Oscillator PUF for Chip Identification. Cryptography 2025, 9, 36. https://doi.org/10.3390/cryptography9020036

Zulfikar Z, Walidainy H, Rahman A, Muchtar K. Reliability Improvement of 28 nm Intel FPGA Ring Oscillator PUF for Chip Identification. Cryptography. 2025; 9(2):36. https://doi.org/10.3390/cryptography9020036

Chicago/Turabian StyleZulfikar, Zulfikar, Hubbul Walidainy, Aulia Rahman, and Kahlil Muchtar. 2025. "Reliability Improvement of 28 nm Intel FPGA Ring Oscillator PUF for Chip Identification" Cryptography 9, no. 2: 36. https://doi.org/10.3390/cryptography9020036

APA StyleZulfikar, Z., Walidainy, H., Rahman, A., & Muchtar, K. (2025). Reliability Improvement of 28 nm Intel FPGA Ring Oscillator PUF for Chip Identification. Cryptography, 9(2), 36. https://doi.org/10.3390/cryptography9020036