Non-Invasive Detection Method for Recycled Flash Memory Using Timing Characteristics †

Abstract

1. Introduction

- Detection method has to be quick, non-invasive, and inexpensive.

- The detection approach has to be suitable for mass-volume recycled Flash chips because some detection technique (e.g., ID-based) is complex and does not support detection for mass-volume chips.

- The detection mechanism needs to be robust against temperature and voltage variation.

- Minimal usage or no usage of the database is another criteria for the detection mechanism.

- The detection method needs to be straightforward and should provide a yes-no decision with a high confidence level. The detection technique should also identify the exact usage of the memory.

- Detection techniques should be independent of the vendor, technology node, and capacity. However, the threshold of detection parameter might vary across manufacturers, technology nodes, and capacities.

- We propose a universal and widely applicable framework to identify recycled Flash memories by measuring the Flash array characteristics, such as erase time, program time, fail bit counts, etc.

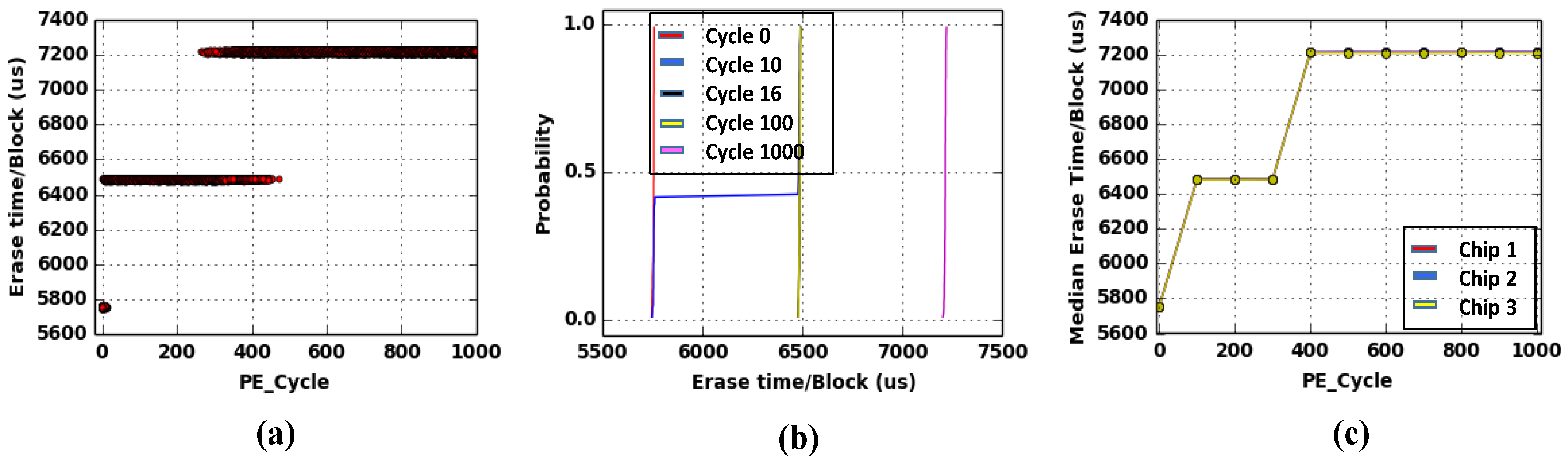

- Experimental data shows that erase time is the best metric to detect recycled Flash chip. We find that erase time shows minimum variation between different memory blocks and it increases significantly with usage.

- We validate our proposed method with commercial off the shelf Flash chips from several vendors, technology nodes, memory types (SLC vs. MLC), and capacity (i.e., memory size). Measurement results show that we can detect a recycled Flash chip with high accuracy if it has been used as less as 0.05% to 3.0% of its total lifetime.

- Proposed method does not require any hardware modification or any prior database maintenance. Hence it can be implemented on many existing storage solution with system updates.

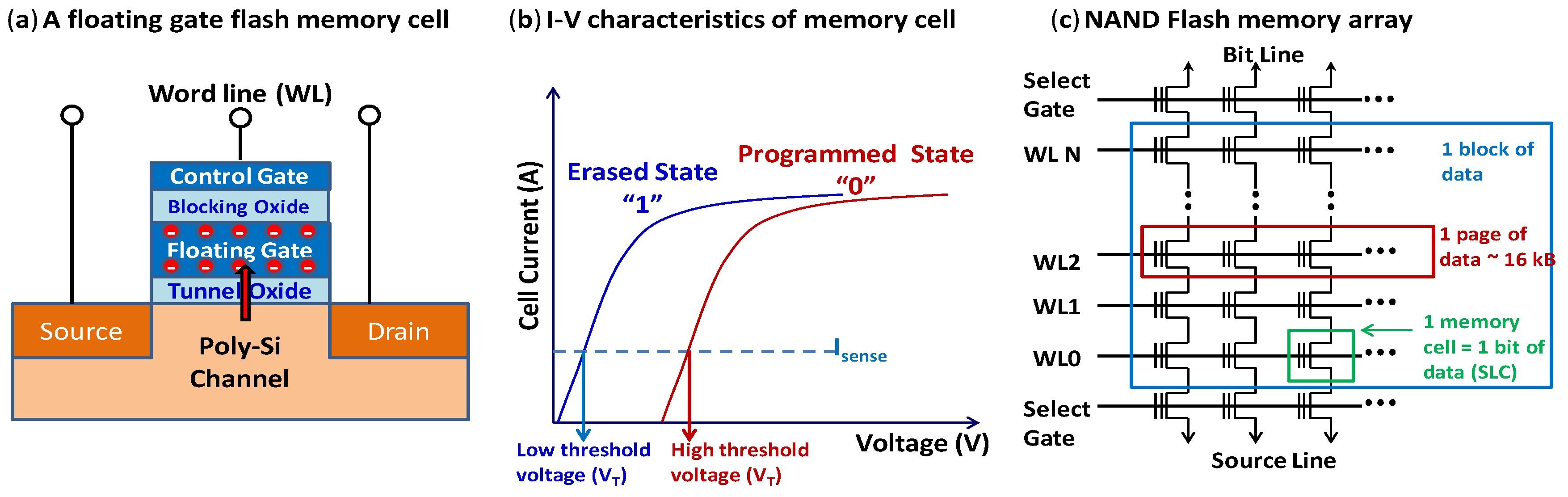

2. Background

3. Existing Work on Detecting Counterfeit IC

4. Recycled Flash Memory Detection

5. Results and Analysis

5.1. Experimental Set-Up

- At first a block is selected on which we want to perform program-erase operation.

- The selected block is then erased, or in other words, all the bits of that block is set to “1”.

- Then the block is programmed with all “0” data pattern.

- Read operation is then carry out on one page at a time.

- Program time, Erase time and FBC are then recorded.

- Process is then continued for other blocks of the memory.

- Finally different plots are obtained by analyzing the recorded data.

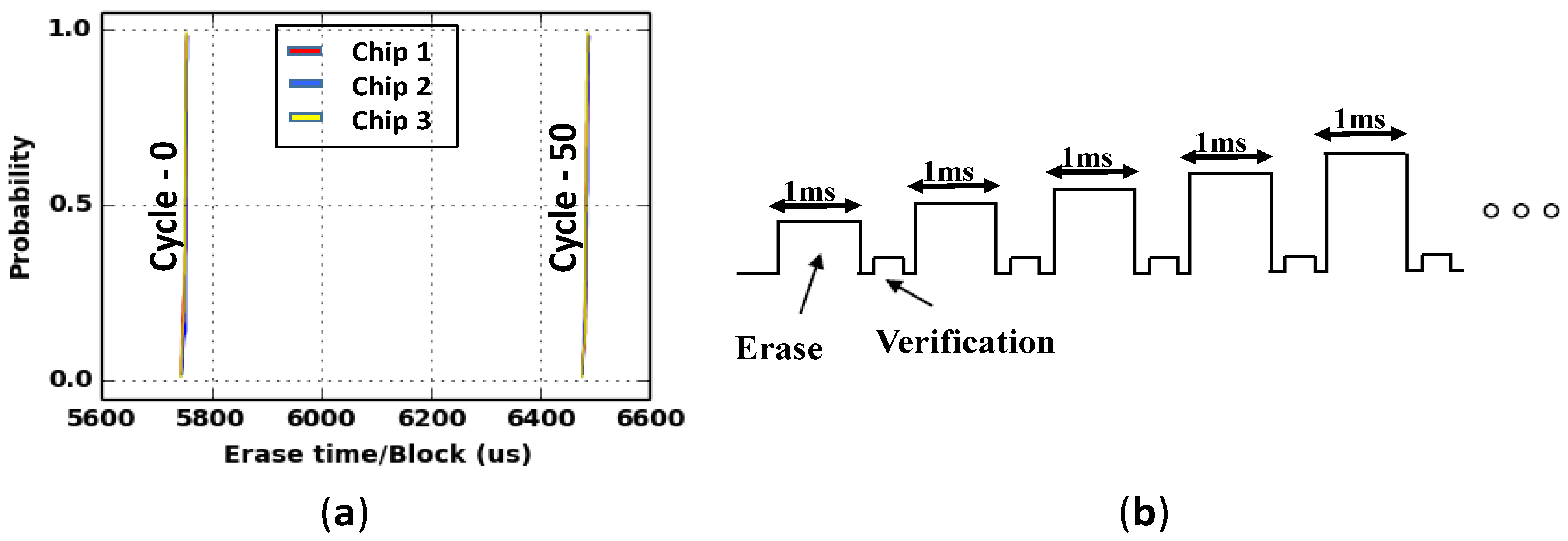

5.2. Measurement Procedure for Flash Timing

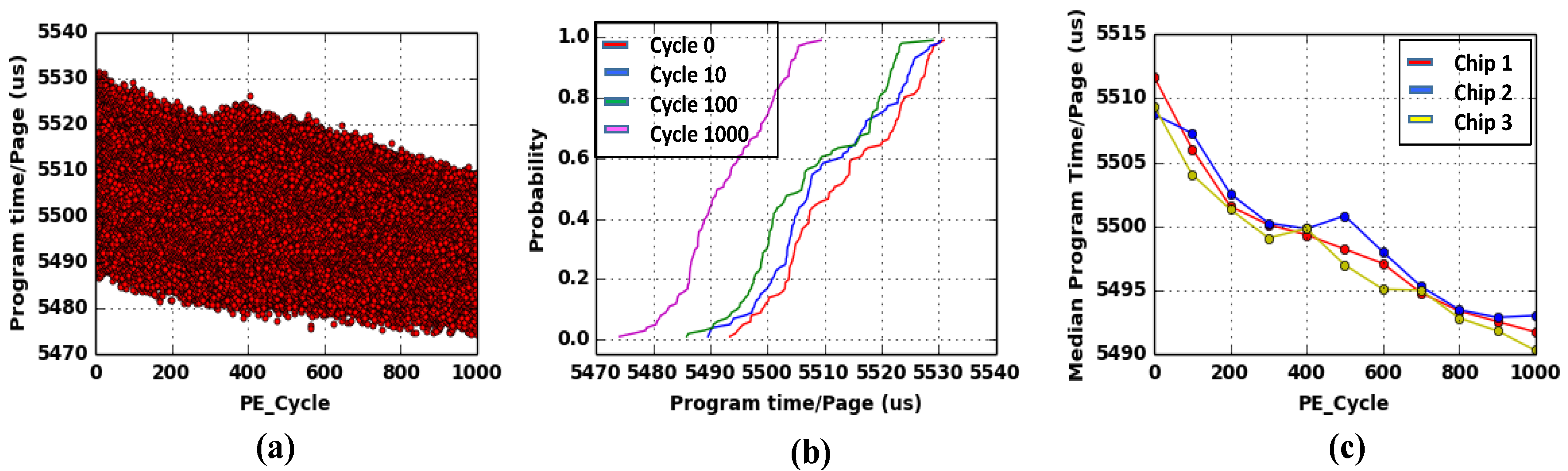

5.3. Evaluation of Different Flash Characteristics for Early Detection

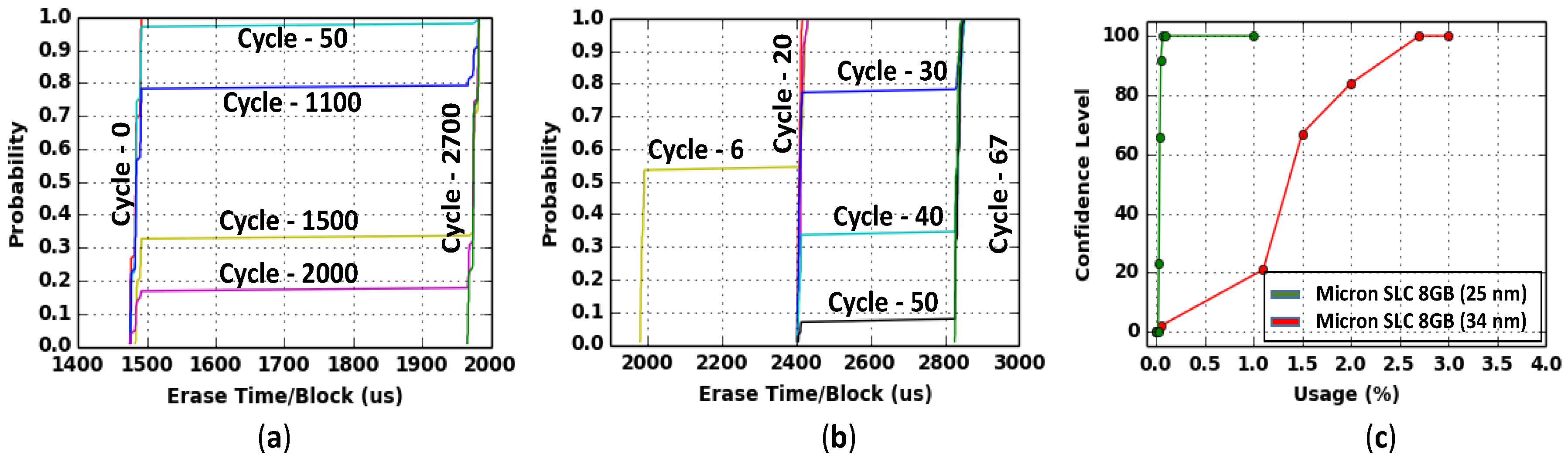

5.4. Validation on Different Technology Nodes

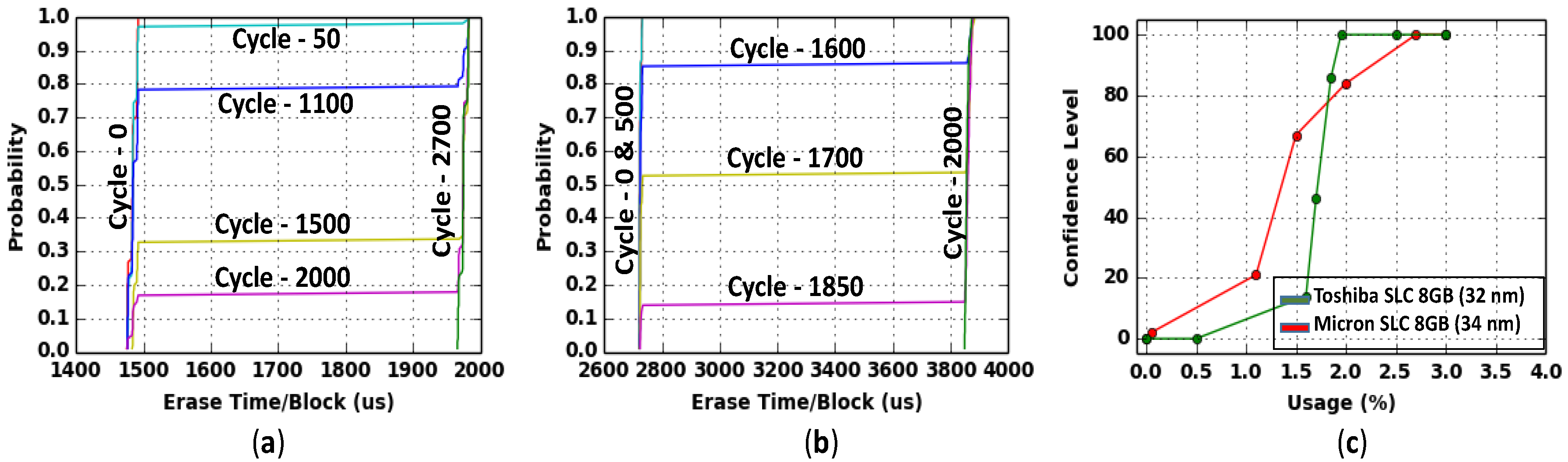

5.5. Validation on Flash Chip from Different Manufacturers

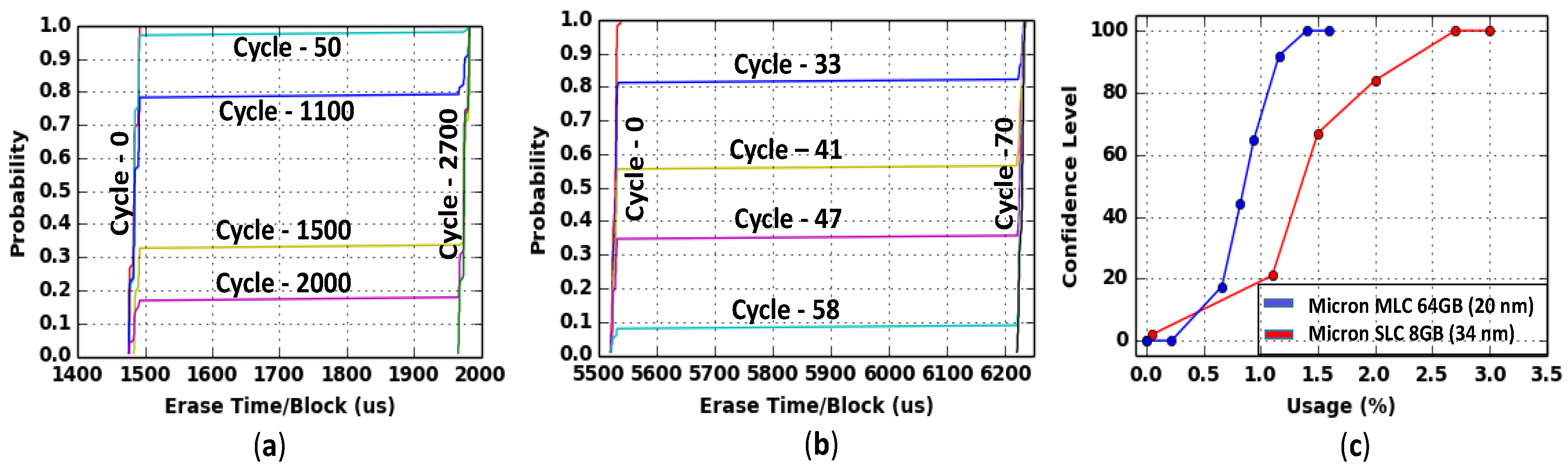

5.6. Validation on SLC and MLC Flash Chips

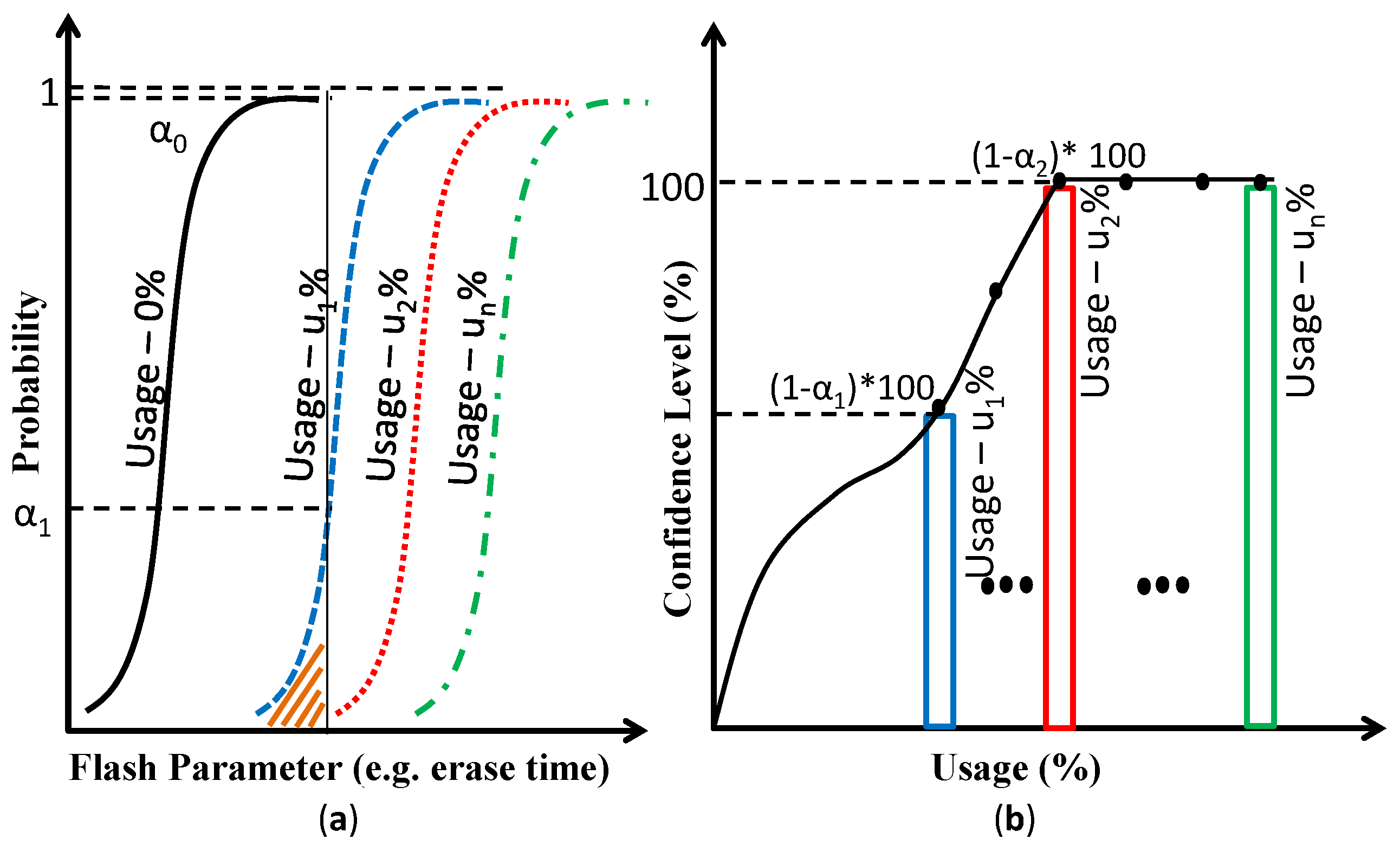

5.7. Usage vs. Confidence Level

- Timing investigation ensures that erase time distribution can be applied for the detection of recycled and fresh Flash memory at acceptable accuracy.

- How early a Flash chip can be detected (i.e., the “usage”) with acceptable confidence depends on manufacturers, technology nodes, memory types (SLC vs. MLC), and capacity.

- Among three Flash memory parameters, erase time is the best to identify a recycled Flash memory as early as possible (i.e., with minimal usage). Program time and FBC also demonstrate changes over time however not sufficient to use to identify a recycled Flash memory from fresh one with minimal usage.

- Impact of Testing on Wear-out: Our technique involves one erase operation per block, which have minimal impact on aging (typical erase count for a chip is ∼100,000).

- Test Time: Testing the entire chip can take a few seconds because a typical erase operation take 1 to 10 milliseconds per block and a chip can contain more than 1000 blocks.

- Temperature Effect: Our methodology works for all different temperatures; however, the exact detection threshold depends on the operating temperature.

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Karri, R.; Koushanfar, F. Trustworthy Hardware [Scanning the Issue]. Proc. IEEE 2014, 102, 1123–1125. [Google Scholar] [CrossRef]

- Fern, N.; San, I.; Koç, Ç.K.; Cheng, K.T.T. Hiding Hardware Trojan Communication Channels in Partially Specified SoC Bus Functionality. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2017, 36, 1435–1444. [Google Scholar] [CrossRef]

- Our E-Waste Problem Is Ridiculous, and Gadget Makers Aren’t Helping. 2012. Available online: https://www.wired.com/2014/12/product-design-and-recycling/ (accessed on 23 January 2018).

- Sinanoglu, O.; Karimi, N.; Rajendran, J.; Karri, R.; Jin, Y.; Huang, K.; Makris, Y. Reconciling the IC test and security dichotomy. In Proceedings of the 2013 18th IEEE European Test Symposium (ETS), Avignon, France, 27–30 May 2013; pp. 1–6. [Google Scholar]

- Guin, U.; Huang, K.; DiMase, D.; Carulli, J.M.; Tehranipoor, M.; Makris, Y. Counterfeit Integrated Circuits: A Rising Threat in the Global Semiconductor Supply Chain. Proc. IEEE 2014, 102, 1207–1228. [Google Scholar] [CrossRef]

- Kumari, P.; Talukder, B.M.S.B.; Sakib, S.; Ray, B.; Rahman, M.T. Independent detection of recycled flash memory: Challenges and solutions. In Proceedings of the 2018 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), Washington, DC, USA, 30 April–4 May 2018; pp. 89–95. [Google Scholar]

- Guo, Z.; Xu, X.; Tehranipoor, M.M.; Forte, D. FFD: A Framework for Fake Flash Detection. In Proceedings of the 54th Annual Design Automation Conference 2017 (DAC ’17); ACM: New York, NY, USA, 2017; p. 8. [Google Scholar]

- “Global Report—eBay Fake Memory 2008—2009,” Fake Flash Memory Information—FlashChipDirector, 10 January 2010. Available online: https://flashfakecentral.wordpress.com/2010/01/10/global-report-ebay-fake-memory-2008-2009/ (accessed on 23 January 2018).

- “Fake Flash News—Internet & eBay Fraud”, Fake Flash News—Internet & eBay Fraud. Available online: https://fakeflashnews.wordpress.com/ (accessed on 29 July 2018).

- “Fake and Counterfeit USB Flash Drives Spreading on Amazon”, Myce.com. Available online: https://www.myce.com/news/fake-and-counterfeit-usb-flash-drives-spreading-on-amazon-72165/ (accessed on 18 June 2018).

- “Feds Close Huge Chip Counterfeiting Case (Exclusive)”, VentureBeat, 25 September 2011. Available online: https://venturebeat.com/2011/09/25/feds-close-the-books-on-a-huge-chip-counterfeiting-scheme/ (accessed on 29 July 2018).

- “Report A Fake”, SOSFakeFlash, 10 May 2010. Available online: https://sosfakeflash.wordpress.com/report-a-fake/ (accessed on 18 June 2018).

- Samarin, P.; Lemke-Rust, K. Detection of counterfeit ICs using public identification sequences. In Proceedings of the 2017 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), McLean, VA, USA, 1–5 May 2017; p. 163. [Google Scholar]

- Liu, M.; Kim, C.H. A powerless and non-volatile counterfeit IC detection sensor in a standard logic process based on an exposed floating-gate array. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–7 June 2017; pp. T102–T103. [Google Scholar]

- He, K.; Huang, X.; Tan, S.X.D. EM-Based On-Chip Aging Sensor for Detection of Recycled ICs. IEEE Des. Test 2016, 33, 56–64. [Google Scholar] [CrossRef]

- Alam, M.; Chowdhury, S.; Tehranipoor, M.M.; Guin, U. Robust, Low-Cost, and Accurate Detection of Recycled ICs using Digital Signatures. In Proceedings of the 2018 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), Washington, DC, USA, 30 April–4 May 2018; pp. 209–214. [Google Scholar]

- Guin, U.; Zhang, X.; Forte, D.; Tehranipoor, M. Low-cost On-Chip Structures for Combating Die and IC Recycling. In Proceedings of the 2014 51st ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 2–5 June 2014; pp. 1–6. [Google Scholar]

- Lin, C.W.; Ghosh, S. Novel self-calibrating recycling sensor using Schmitt-Trigger and voltage boosting for fine-grained detection. In Proceedings of the Sixteenth International Symposium on Quality Electronic Design, Santa Clara, CA, USA, 2–4 March 2015; pp. 465–469. [Google Scholar]

- Shahbazmohamadi, S.; Forte, D.; Tehranipoor, M. Advanced Physical Inspection Methods for Counterfeit IC Detection. In Proceedings of the 40th International Symposium for Testing and Failure Analysis (ISTFA), Houston, TX, USA, 9–13 November 2014; pp. 55–64. [Google Scholar]

- Ahi, K.; Asadizanjani, N.; Shahbazmohamadi, S.; Tehranipoor, M.; Anwar, M. Terahertz characterization of electronic components and comparison of terahertz imaging with x-ray imaging techniques. In Terahertz Physics, Devices, and Systems IX: Advanced Applications in Industry and Defense; SPIE: Bellingham, WA, USA, 2015; Volume 9483, p. 94830K. [Google Scholar]

- Hu, B.B.; Nuss, M.C. Imaging with terahertz waves. Opt. Lett. 1995, 20, 1716–1718. [Google Scholar] [CrossRef] [PubMed]

- Bushnell, M.; Agrawal, V.D. Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits; Springer: New York, NY, USA, 2002. [Google Scholar]

- Guin, U.; Forte, D.; Tehranipoor, M. Design of Accurate Low-Cost On-Chip Structures for Protecting Integrated Circuits Against Recycling. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 1233–1246. [Google Scholar] [CrossRef]

- Guin, U.; DiMase, D.; Tehranipoor, M. A Comprehensive Framework for Counterfeit Defect Coverage Analysis and Detection Assessment. J. Electron. Test. 2014, 30, 25–40. [Google Scholar] [CrossRef]

- Galey, J.M.; Norby, R.E.; Roth, J.P. Techniques for the diagnosis of switching circuit failures. IEEE Trans. Commun. Electron. 1964, 83, 509–514. [Google Scholar] [CrossRef]

- Koushanfar, F. Can EDA Combat the Rise of Electronic Counterfeiting? In Proceedings of the 49th Annual Design Automation Conference, New York, NY, USA, 3–7 June 2012; pp. 133–138. [Google Scholar]

- Kahng, A.B.; Kirovski, D.; Mantik, S.; Potkonjak, M.; Wong, J.L. Copy Detection for Intellectual Property Protec-tion of VLSI Designs. In Proceedings of the 1999 IEEE/ACM International Conference on Computer-aided Design, Piscataway, NJ, USA, 7–11 November 1999; pp. 600–605. [Google Scholar]

- Wei, S.; Meguerdichian, S.; Potkonjak, M. Gate-level Characterization: Foundations and Hardware Security Applications. In Proceedings of the 47th Design Automation Conference, New York, NY, USA, 13–18 June 2010; pp. 222–227. [Google Scholar]

- Wei, S.; Nahapetian, A.; Potkonjak, M. Robust Passive Hardware Metering. In Proceedings of the International Conference on Computer-Aided Design; IEEE Press: Piscataway, NJ, USA, 2011; pp. 802–809. [Google Scholar]

- Ye, Y.; Kim, T.; Chen, H.; Wang, H.; Tlelo-Cuautle, E.; Tan, S.X.D. Comprehensive detection of counterfeit ICs via on-chip sensor and post-fabrication authentication policy. In Proceedings of the 2017 14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Giardini Naxos, Italy, 12–15 June 2017; pp. 1–4. [Google Scholar]

- Kim, T.H.; Persaud, R.; Kim, C.H. Silicon Odometer: An On-Chip Reliability Monitor for Measuring Frequency Degradation of Digital Circuits. IEEE J. Solid-State Circuits 2008, 43, 874–880. [Google Scholar] [CrossRef]

- Karl, E.; Singh, P.; Blaauw, D.; Sylvester, D. Compact In-Situ Sensors for Monitoring Negative-Bias-Temperature-Instability Effect and Oxide Degradation. In Proceedings of the 2008 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 410–623. [Google Scholar]

- Kim, K.K.; Wang, W.; Choi, K. On-Chip Aging Sensor Circuits for Reliable Nanometer MOSFET Digital Circuits. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 798–802. [Google Scholar] [CrossRef]

- Dogan, H.; Forte, D.; Tehranipoor, M.M. Aging Analysis for Recycled FPGA Detection. In Proceedings of the 2014 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Amsterdam, The Netherlands, 1–3 October 2014; pp. 171–176. [Google Scholar]

- Zhang, X.; Xiao, K.; Tehranipoor, M. Path-delay fingerprinting for identification of recovered ICs. In Proceedings of the 2012 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Austin, TX, USA, 3–5 October 2012; pp. 13–18. [Google Scholar]

- Guo, Z.; Rahman, M.T.; Tehranipoor, M.M.; Forte, D. A zero-cost approach to detect recycled SoC chips using embedded SRAM. In Proceedings of the 2016 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), McLean, VA, USA, 3–5 May 2016; pp. 191–196. [Google Scholar]

- Guo, Z.; Xu, X.; Rahman, M.T.; Tehranipoor, M.M.; Forte, D. SCARe: An SRAM-Based Countermeasure Against IC Recycling. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 744–755. [Google Scholar] [CrossRef]

- Rahman, M.T. Systematic Correlation and Cell Neighborhood Analysis of SRAM PUF for Robust and Unique Key Generation. J. Hardw. Syst. Secur. 2017, 1, 137–155. [Google Scholar] [CrossRef]

- Tehranipoor, M.; Guin, U.; Forte, D. Counterfeit Integrated Circuits: Detection and Avoidance, 1st ed.; Springer: Berlin, Germany, 2015. [Google Scholar]

- Ray, B.; Milenkovic, A. True Random Number Generation Using Read Noise of Flash Memory Cells. IEEE Trans. Electron Devices 2018, 65, 963–969. [Google Scholar] [CrossRef]

| Part Number | Manufacturer and Chip Description | Endurance (P/E Cycle) | Chip Count | Acceptable * Confidence Level @ |

|---|---|---|---|---|

| MT29F64G08CBABAWP:B TR | Micron 64 Gb MLC (20 nm node) | 5000 | 3 | ≥0.25% usage |

| MT 29F32G08CBADAWP:D | Micron 32 Gb MLC (20 nm node) | 5000 | 3 | ≥1.4% usage |

| TC58NVG3S0FTA00-ND | Toshiba 8 Gb SLC (32 nm node) | 100,000 | 3 | ≥2% usage |

| MT29F8G08ABABAWP:B | Micron 8 GB SLC (34 nm node) | 100,000 | 3 | ≥2.7% usage |

| MT29F8G08ABACAWP:C | Micron 8 GB SLC (25 nm node) | 100,000 | 3 | ≥0.05% usage |

| MT29F4G08ABADAWP:D TR | Micron 4 GB SLC (34 nm node) | 100,000 | 3 | ≥3% usage |

| Usage (%) | Confidence Level | ||

|---|---|---|---|

| Vendor 1 | Vendor 2 | Vendor 3 | |

| 1% | Not Acceptable | Not Acceptable | Not Acceptable |

| 1.4% | * Acceptable | Not Acceptable | Not Acceptable |

| 2% | Acceptable | Acceptable | Not Acceptable |

| 2.7% | Acceptable | Acceptable | Acceptable |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sakib, S.; Kumari, P.; Talukder, B.M.S.B.; Rahman, M.T.; Ray, B. Non-Invasive Detection Method for Recycled Flash Memory Using Timing Characteristics †. Cryptography 2018, 2, 17. https://doi.org/10.3390/cryptography2030017

Sakib S, Kumari P, Talukder BMSB, Rahman MT, Ray B. Non-Invasive Detection Method for Recycled Flash Memory Using Timing Characteristics †. Cryptography. 2018; 2(3):17. https://doi.org/10.3390/cryptography2030017

Chicago/Turabian StyleSakib, Sadman, Preeti Kumari, B. M. S. Bahar Talukder, Md Tauhidur Rahman, and Biswajit Ray. 2018. "Non-Invasive Detection Method for Recycled Flash Memory Using Timing Characteristics †" Cryptography 2, no. 3: 17. https://doi.org/10.3390/cryptography2030017

APA StyleSakib, S., Kumari, P., Talukder, B. M. S. B., Rahman, M. T., & Ray, B. (2018). Non-Invasive Detection Method for Recycled Flash Memory Using Timing Characteristics †. Cryptography, 2(3), 17. https://doi.org/10.3390/cryptography2030017