Enhanced Synaptic Behaviors in Chitosan Electrolyte-Based Electric-Double-Layer Transistors with Poly-Si Nanowire Channel Structures

Abstract

:1. Introduction

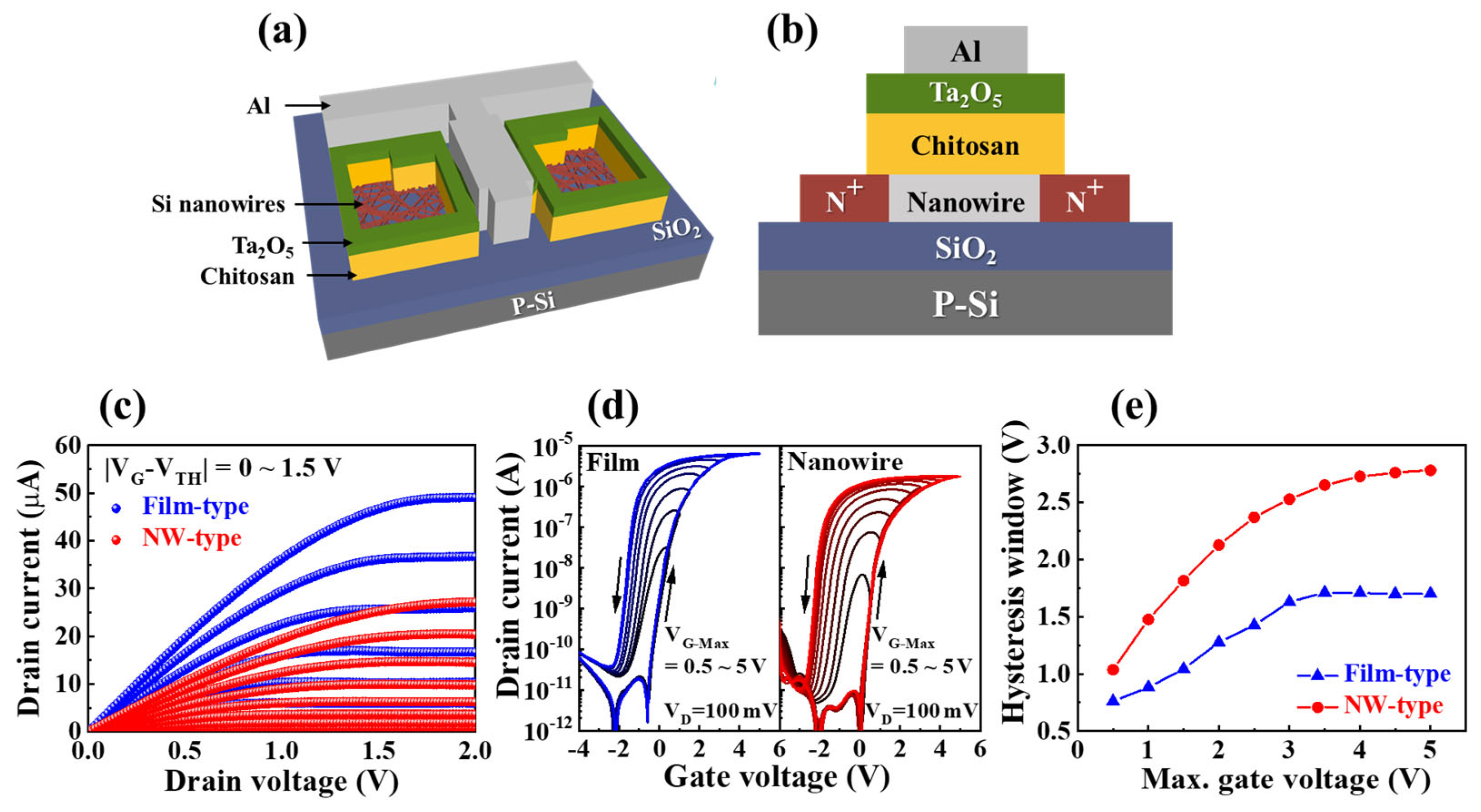

2. Materials and Methods

2.1. Formation of Poly-Si NW Channel

2.2. Preparation of Chitosan Electrolyte Solution

2.3. Fabrication of Synaptic Transistor

2.4. Characterization

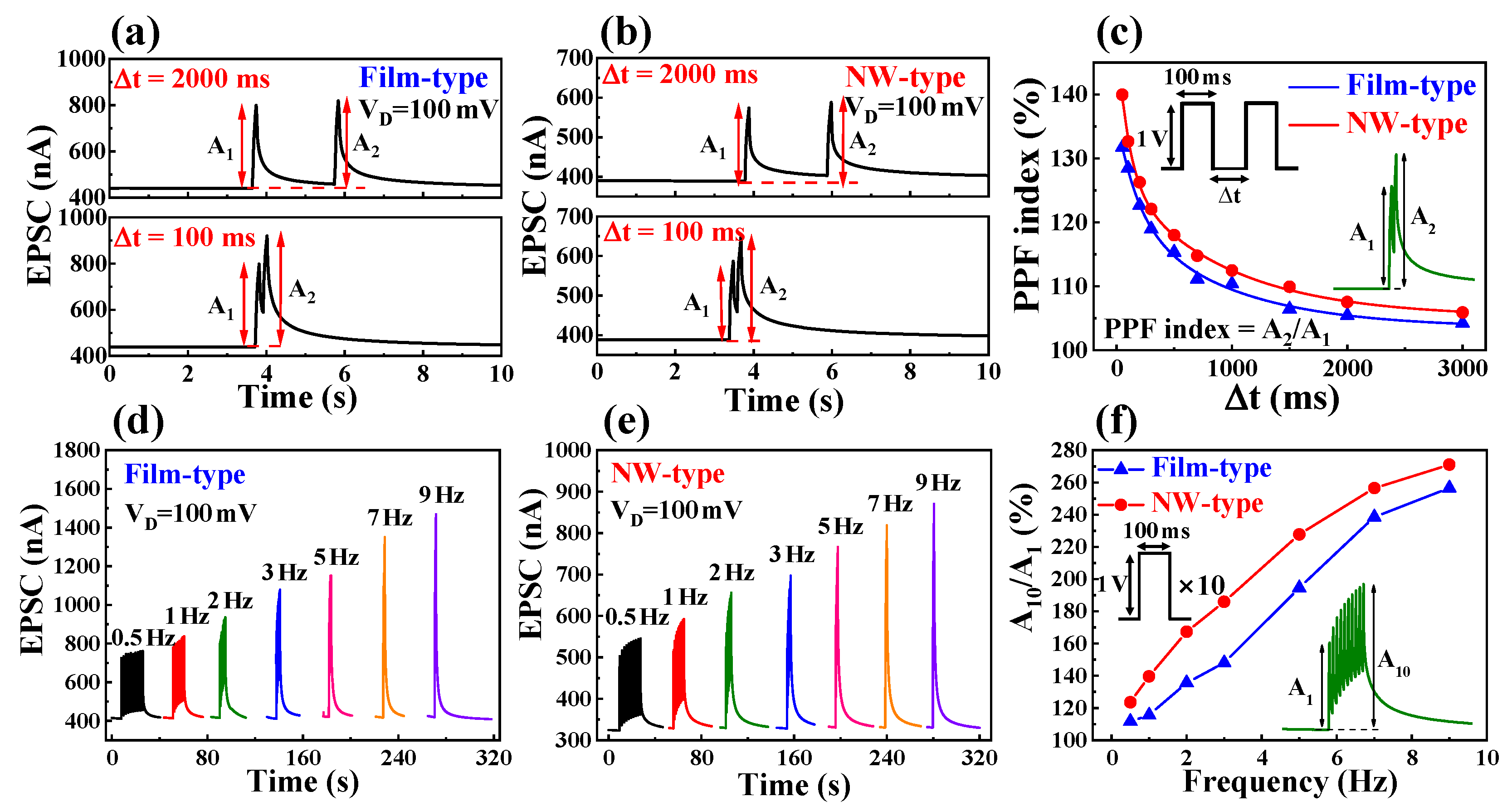

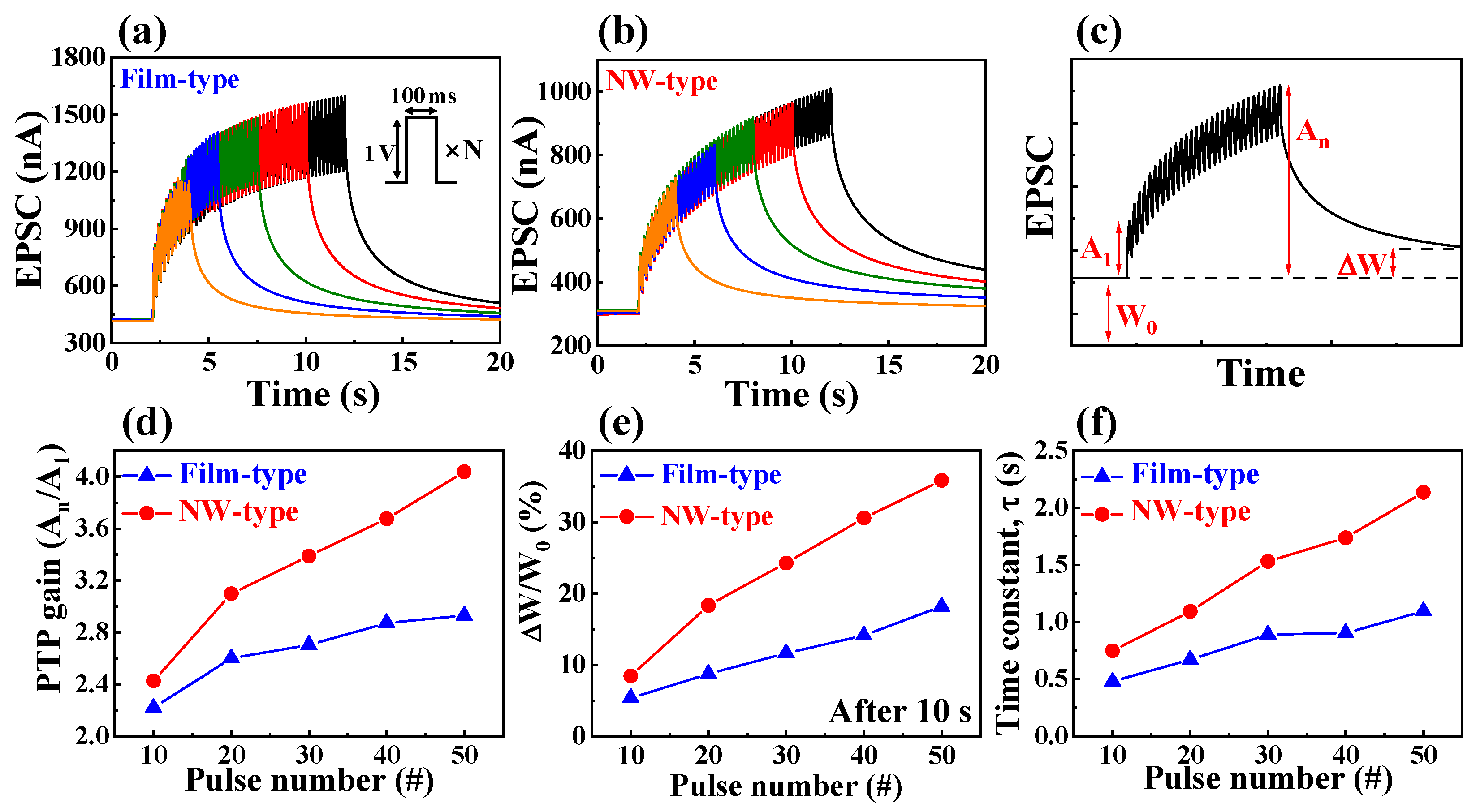

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Li, B.; Hui, W.; Ran, X.; Xia, Y.; Xia, F.; Chao, L.; Chen, Y.; Huang, W. Metal halide perovskites for resistive switching memory devices and artificial synapses. J. Mater. Chem. C 2019, 7, 7476–7493. [Google Scholar] [CrossRef]

- Wang, W.S.; Zhu, L.Q. Recent advances in neuromorphic transistors for artificial perception applications. Sci. Technol. Adv. Mater. 2023, 24, 2152290. [Google Scholar] [CrossRef]

- Lv, Z.; Zhou, Y.; Han, S.T.; Roy, V.A.L. From biomaterial-based data storage to bio-inspired artificial synapse. Mater. Today 2018, 21, 537–552. [Google Scholar] [CrossRef]

- Li, L.; Hu, L.; Liu, K.; Chang, K.C.; Zhang, R.; Lin, X.; Zhang, S.; Huang, P.; Liu, H.J.; Kuo, T.P. Bifunctional homologous alkali-metal artificial synapse with regenerative ability and mechanism imitation of voltage-gated ion channels. Mater. Horiz. 2021, 8, 3072–3081. [Google Scholar] [CrossRef]

- Kuzum, D.; Yu, S.; Wong, H.P. Synaptic electronics: Materials, devices and applications. Nanotechnology 2013, 24, 382001. [Google Scholar] [CrossRef]

- Jo, S.H.; Chang, T.; Ebong, I.; Bhadviya, B.B.; Mazumder, P.; Lu, W. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 2010, 10, 1297–1301. [Google Scholar] [CrossRef]

- Backus, J. Can programming be liberated from the von Neumann style? A functional style and its algebra of programs. Commun. ACM 1978, 21, 613–641. [Google Scholar] [CrossRef]

- Indiveri, G.; Liu, S.C. Memory and information processing in neuromorphic systems. Proc. IEEE 2015, 103, 1379–1397. [Google Scholar] [CrossRef]

- Furber, S. Large-scale neuromorphic computing systems. J. Neural. Eng. 2016, 13, 051001. [Google Scholar] [CrossRef]

- Chklovskii, D.B.; Mel, B.W.; Svoboda, K. Cortical rewiring and information storage. Nature 2004, 431, 782–788. [Google Scholar] [CrossRef]

- Gerstner, W.; Sprekeler, H.; Deco, G. Theory and simulation in neuroscience. Science 2012, 338, 60–65. [Google Scholar] [CrossRef]

- Huang, H.Y.; Ge, C.; Zhang, Q.H.; Liu, C.X.; Du, J.Y.; Li, J.K.; Wang, C.; Gu, L.; Yang, G.Z.; Jin, K.J. Electrolyte-gated synaptic transistor with oxygen ions. Adv. Funct. Mater. 2019, 29, 1902702. [Google Scholar] [CrossRef]

- Guo, L.Q.; Tao, J.; Zhu, L.Q.; Xiao, H.; Gao, W.T.; Yu, F.; Fu, Y.M. Starch-based biopolymer electrolyte gated oxide synaptic transistors. Org. Electron. 2018, 61, 312–317. [Google Scholar] [CrossRef]

- Dai, S.; Wang, Y.; Zhang, J.; Zhao, Y.; Xiao, F.; Liu, D.; Wang, T.; Huang, J. Wood-derived nanopaper dielectrics for organic synaptic transistors. ACS Appl. Mater. Interf. 2018, 10, 39983–39991. [Google Scholar] [CrossRef]

- Wu, G.; Zhang, J.; Wan, X.; Yang, Y.; Jiang, S. Chitosan-based biopolysaccharide proton conductors for synaptic transistors on paper substrates. J. Mater. Chem. C 2014, 2, 6249–6255. [Google Scholar] [CrossRef]

- Du, H.; Lin, X.; Xu, Z.; Chu, D. Electric double-layer transistors: A review of recent progress. J. Mater. Sci. 2015, 50, 5641–5673. [Google Scholar] [CrossRef]

- Sharma, P.; Bhatti, T.S. A review on electrochemical double-layer capacitors. Energy Convers. Manag. 2010, 51, 2901–2912. [Google Scholar] [CrossRef]

- Zhou, J.; Liu, Y.; Shi, Y.; Wan, Q. Solution-processed chitosan-gated IZO-based transistors for mimicking synaptic plasticity. IEEE Electron. Dev. Lett. 2014, 35, 280–282. [Google Scholar] [CrossRef]

- Guo, L.; Wen, J.; Ding, J.; Wan, C.; Cheng, G. Excitatory post-synaptic potential mimicked in indium-zinc-oxide synaptic transistors gated by methyl cellulose solid electrolyte. Sci. Rep. 2016, 6, 38578. [Google Scholar] [CrossRef] [PubMed]

- Ling, H.; Wang, N.; Yang, A.; Liu, Y.; Song, J.; Yan, F. Dynamically reconfigurable short-term synapse with millivolt stimulus resolution based on organic electrochemical transistors. Adv. Mater. Technol. 2019, 4, 1900471. [Google Scholar] [CrossRef]

- Min, S.Y.; Cho, W.J. CMOS-compatible synaptic transistor gated by chitosan electrolyte-Ta2O5 hybrid electric double layer. Sci. Rep. 2020, 10, 15561. [Google Scholar] [CrossRef] [PubMed]

- Koo, S.M.; Fujiwara, A.; Han, J.P.; Vogel, E.M.; Richter, C.A.; Bonevich, J.E. High inversion current in silicon nanowire field effect transistors. Nano Lett. 2004, 4, 2197–2201. [Google Scholar] [CrossRef]

- Fahad, H.M.; Hussain, M.M. Are nanotube architectures more advantageous than nanowire architectures for field effect transistors? Sci. Rep. 2012, 2, 475. [Google Scholar] [CrossRef]

- Heinzig, A.; Slesazeck, S.; Kreupl, F.; Mikolajick, T.; Weber, W.M. Reconfigurable silicon nanowire transistors. Nano Lett. 2012, 12, 119–124. [Google Scholar] [CrossRef]

- Huang, Y.T.; Chen, Y.H.; Ho, Y.J.; Huang, S.W.; Chang, Y.R.; Watanabe, K.; Taniguchi, T.; Chiu, H.C.; Liang, C.T.; Sankar, R.; et al. High-performance InSe transistors with ohmic contact enabled by nonrectifying barrier-type indium electrodes. ACS Appl. Mater. Interf. 2018, 10, 33450–33456. [Google Scholar] [CrossRef]

- Wei, L.; Huang, W.; Fang, X.; Wang, X.; Mou, P.; Shao, F.; Gu, X. Humidity stability of all-sputtered metal-oxide electric-double-layer transistors. IEEE Trans. Electron. Dev. 2020, 67, 5532–5536. [Google Scholar] [CrossRef]

- Kim, S.H.; Cho, W.J. Artificial synapses based on bovine milk biopolymer electric-double-layer transistors. Polymers 2022, 14, 1372. [Google Scholar] [CrossRef] [PubMed]

- Veletić, M.; Balasingham, I. An information theory of neuro-transmission in multiple-access synaptic channels. IEEE Trans. Commun. 2019, 68, 841–853. [Google Scholar] [CrossRef]

- Li, L.; Shao, Y.; Wang, X.; Wu, X.; Liu, W.J.; Zhang, D.W.; Ding, S.J. Flexible femtojoule energy-consumption In-Ga-Zn-O synaptic transistors with extensively tunable memory time. IEEE Trans. Electron. Dev. 2019, 67, 105–112. [Google Scholar] [CrossRef]

- He, W.; Fang, Y.; Yang, H.; Wu, X.; He, L.; Chen, H.; Guo, T. A multi-input light-stimulated synaptic transistor for complex neuromorphic computing. J. Mater. Chem. C 2019, 7, 12523–12531. [Google Scholar] [CrossRef]

- Buonomano, D.V. Decoding temporal information: A model based on short-term synaptic plasticity. J. Neurosci. 2000, 20, 1129–1141. [Google Scholar] [CrossRef]

- Dai, S.; Wu, X.; Liu, D.; Chu, Y.; Wang, K.; Yang, B.; Huang, J. Light-stimulated synaptic devices utilizing interfacial effect of organic field-effect transistors. ACS Appl. Mater. Interf. 2018, 10, 21472–21480. [Google Scholar] [CrossRef]

- Zucker, R.S.; Regehr, W.G. Short-term synaptic plasticity. Ann. Rev. Physiol. 2002, 64, 355–405. [Google Scholar] [CrossRef]

- Li, S.; Lyu, H.; Li, J.; He, Y.; Gao, X.; Wan, Q.; Shi, Y.; Pan, L. Multiterminal ionic synaptic transistor with artificial blink reflex function. IEEE Electron. Dev. Lett. 2021, 42, 351–354. [Google Scholar] [CrossRef]

- Wan, C.J.; Zhu, L.Q.; Zhou, J.M.; Shi, Y.; Wan, Q. Memory and learning behaviors mimicked in nanogranular SiO2-based proton conductor gated oxide-based synaptic transistors. Nanoscale 2013, 5, 10194–10199. [Google Scholar] [CrossRef]

- Fu, Y.M.; Wei, T.; Brownless, J.; Huang, L.; Song, A. Synaptic transistors with a memory time tunability over seven orders of magnitude. Appl. Phys. Lett. 2022, 120, 252903. [Google Scholar] [CrossRef]

- Hu, L.; Wu, S.H.; Cai, W.; Ma, Y.; Mu, X.; Xu, Y.; Wang, H.; Song, Y.; Deng, D.L.; Zou, C.L.; et al. Quantum generative adversarial learning in a superconducting quantum circuit. Sci. Adv. 2019, 5, eaav2761. [Google Scholar] [CrossRef]

- Kim, J.; Lim, J.W.; Lee, J. Characteristics of PEALD–Hafnium dioxide films and their application to gate insulator stacks of photosynaptic transistors. Adv. Electron. Mater. 2022, 8, 2101061. [Google Scholar] [CrossRef]

- Kim, H.; Hwang, S.; Park, J.; Yun, S.; Lee, J.H.; Park, B.G. Spiking neural network using synaptic transistors and neuron circuits for pattern recognition with noisy images. IEEE Electron. Dev. Lett. 2018, 39, 630–633. [Google Scholar] [CrossRef]

- Cao, Y.; Zhao, T.; Zhao, C.; Liu, Y.; Song, P.; Gao, H.; Zhao, C.Z. Advanced artificial synaptic thin-film transistor based on doped potassium ions for neuromorphic computing via third-generation neural network. J. Mater. Chem. C 2022, 10, 3196–3206. [Google Scholar] [CrossRef]

- Davidson, S.; Furber, S.B. Comparison of artificial and spiking neural networks on digital hardware. Front. Neurosci. 2021, 15, 651141. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.; Choi, B.; Lim, M.; Kim, Y.; Kim, H.D.; Choi, S.J. Synaptic device network architecture with feature extraction for unsupervised image classification. Small 2018, 14, 1800521. [Google Scholar] [CrossRef] [PubMed]

- Wang, Y.; Liao, Q.; She, D.; Lv, Z.; Gong, Y.; Ding, G.; Ye, W.; Chen, J.; Xiong, Z.; Wang, G.; et al. Modulation of binary neuroplasticity in a heterojunction-based ambipolar transistor. ACS Appl. Mater. Interf. 2020, 12, 15370–15379. [Google Scholar] [CrossRef] [PubMed]

- Huang, J.; Chen, J.; Yu, R.; Zhou, Y.; Yang, Q.; Li, E.; Chen, Q.; Chen, H.; Guo, T. Tuning the synaptic behaviors of biocompatible synaptic transistor through ion-doping. Organic. Electron. 2021, 89, 106019. [Google Scholar] [CrossRef]

- Yu, J.M.; Lee, C.; Kim, D.J.; Park, H.; Han, J.K.; Hur, J.; Kim, J.K.; Kim, M.S.; Seo, M.; Im, S.G.; et al. All-solid-state ion synaptic transistor for Wafer-scale integration with electrolyte of a nanoscale thickness. Adv. Funct. Mater. 2021, 31, 2010971. [Google Scholar] [CrossRef]

- Jang, J.W.; Park, S.; Burr, G.W.; Hwang, H.; Jeong, Y.H. Optimization of conductance change in Pr1–x Cax MnO3-based synaptic devices for neuromorphic systems. IEEE Electron. Dev. Lett. 2015, 36, 457–459. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, D.-H.; Kim, H.-S.; Park, K.-W.; Park, H.; Cho, W.-J. Enhanced Synaptic Behaviors in Chitosan Electrolyte-Based Electric-Double-Layer Transistors with Poly-Si Nanowire Channel Structures. Biomimetics 2023, 8, 432. https://doi.org/10.3390/biomimetics8050432

Lee D-H, Kim H-S, Park K-W, Park H, Cho W-J. Enhanced Synaptic Behaviors in Chitosan Electrolyte-Based Electric-Double-Layer Transistors with Poly-Si Nanowire Channel Structures. Biomimetics. 2023; 8(5):432. https://doi.org/10.3390/biomimetics8050432

Chicago/Turabian StyleLee, Dong-Hee, Hwi-Su Kim, Ki-Woong Park, Hamin Park, and Won-Ju Cho. 2023. "Enhanced Synaptic Behaviors in Chitosan Electrolyte-Based Electric-Double-Layer Transistors with Poly-Si Nanowire Channel Structures" Biomimetics 8, no. 5: 432. https://doi.org/10.3390/biomimetics8050432

APA StyleLee, D.-H., Kim, H.-S., Park, K.-W., Park, H., & Cho, W.-J. (2023). Enhanced Synaptic Behaviors in Chitosan Electrolyte-Based Electric-Double-Layer Transistors with Poly-Si Nanowire Channel Structures. Biomimetics, 8(5), 432. https://doi.org/10.3390/biomimetics8050432