Wordline Input Bias Scheme for Neural Network Implementation in 3D-NAND Flash

Abstract

1. Introduction

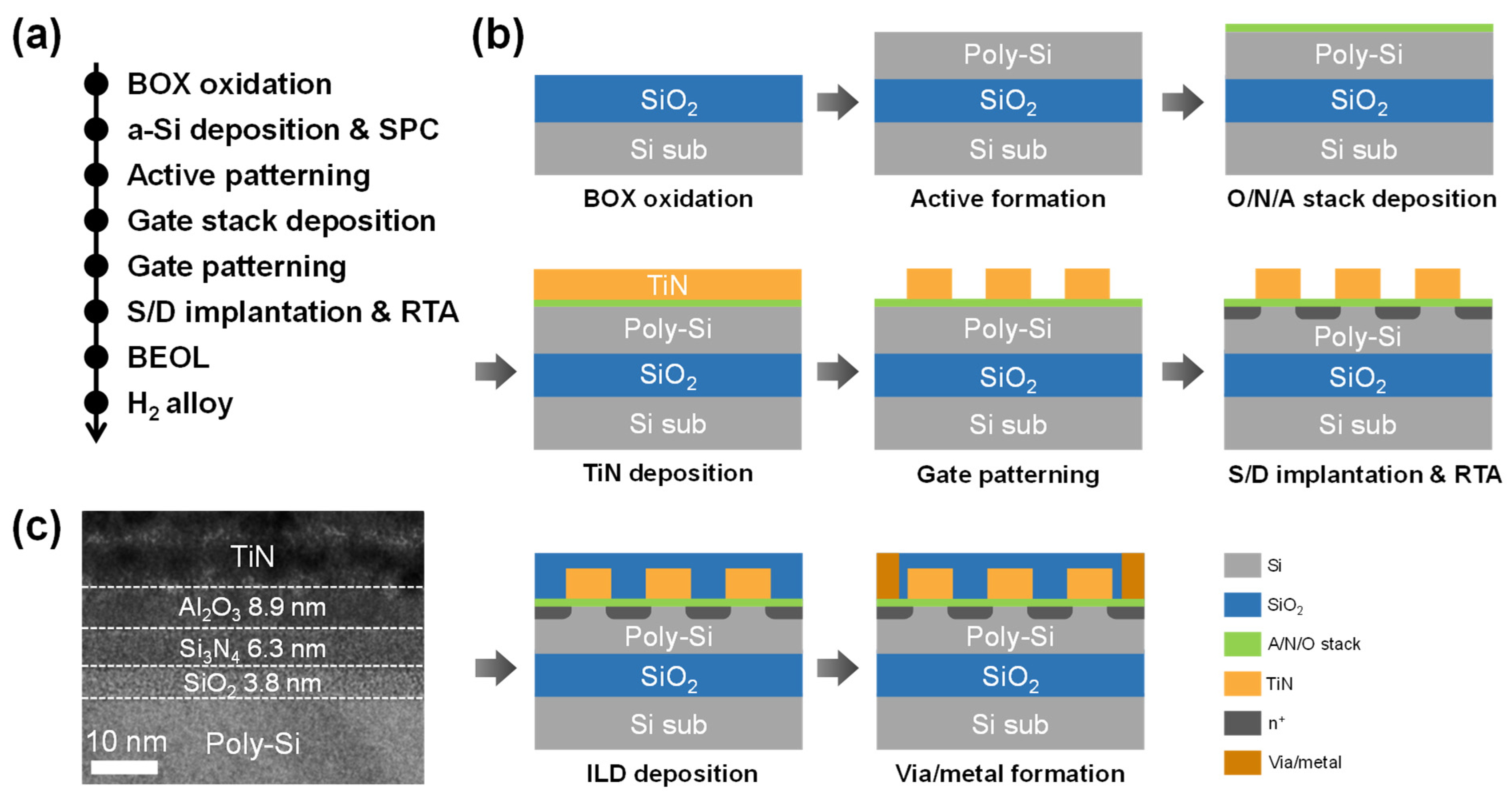

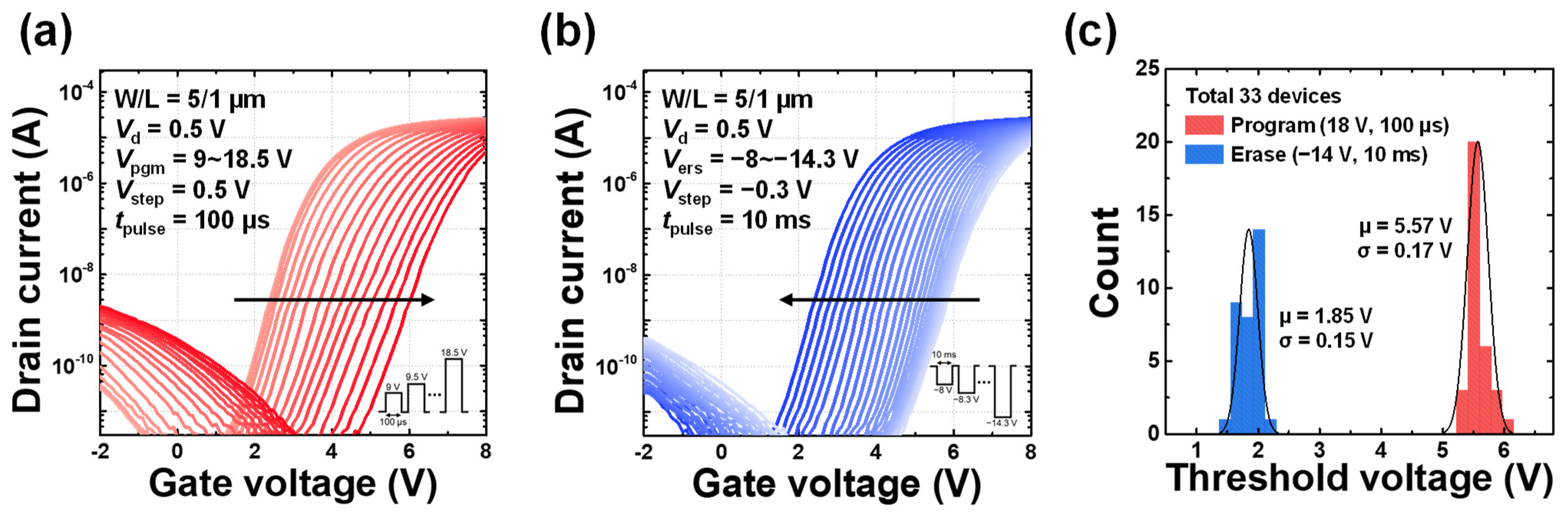

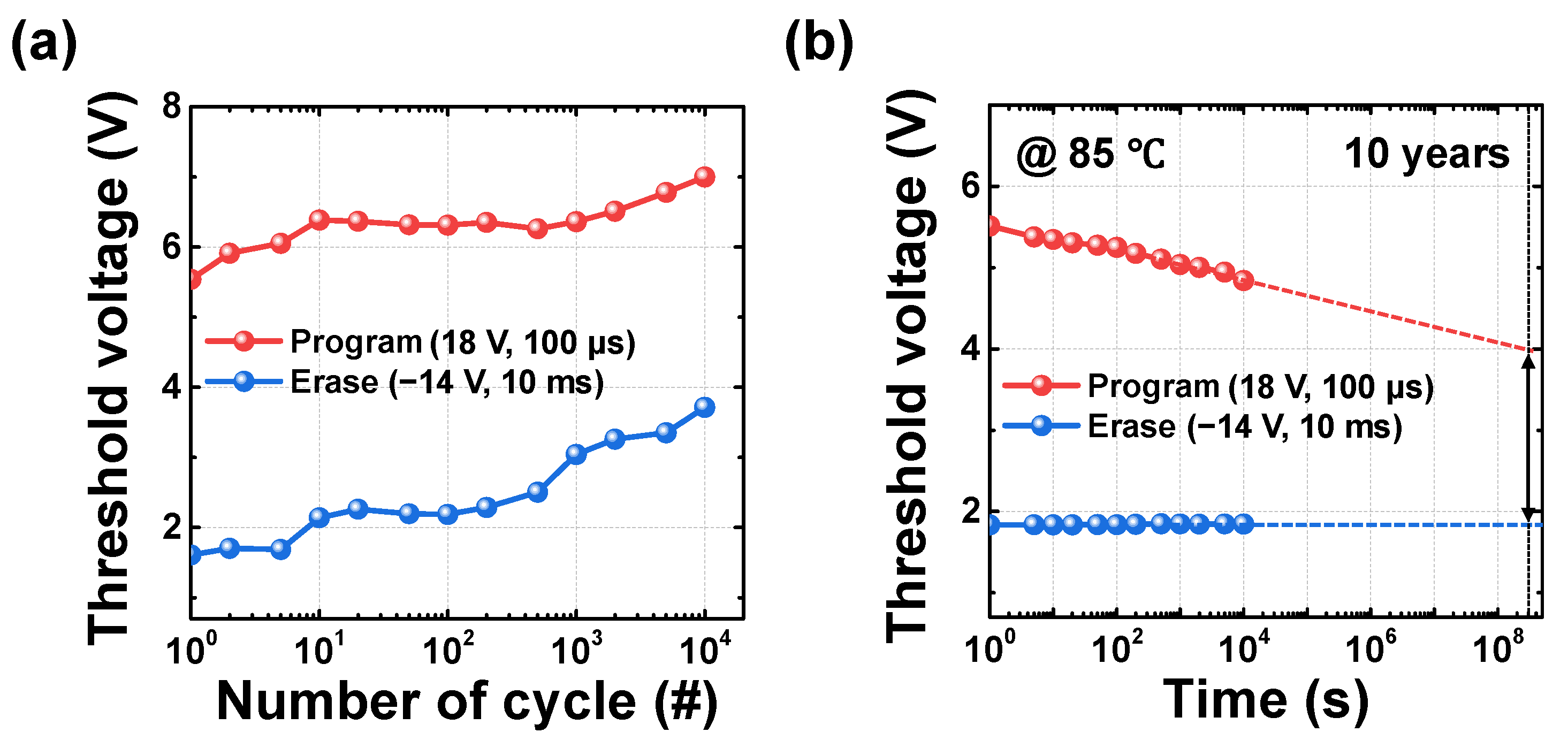

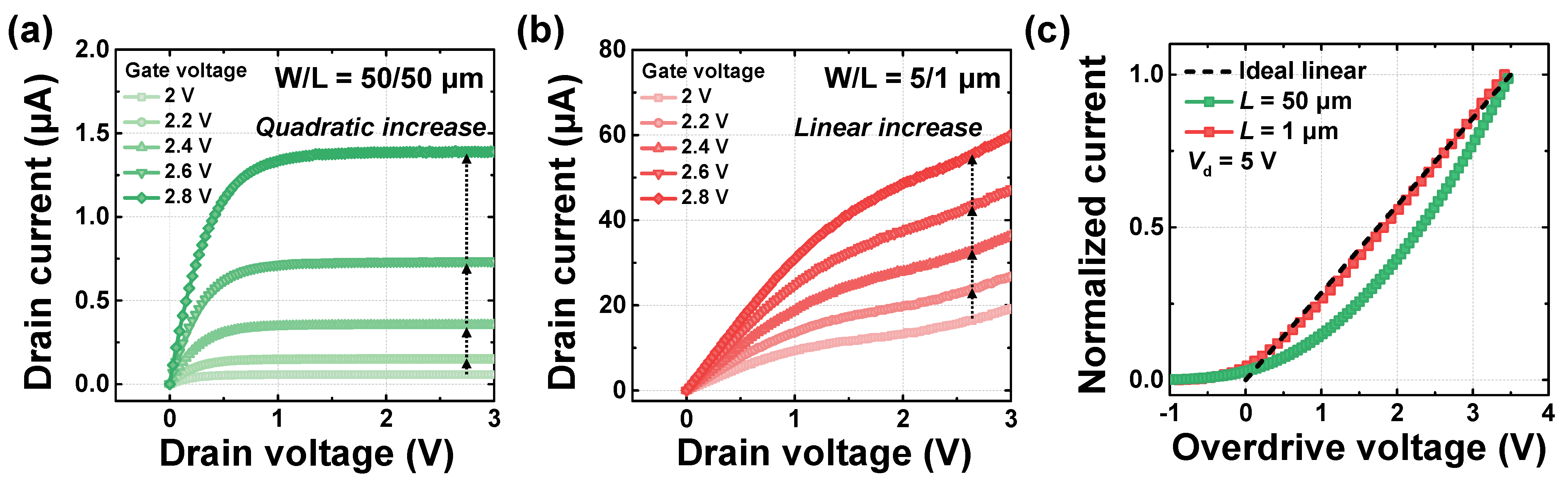

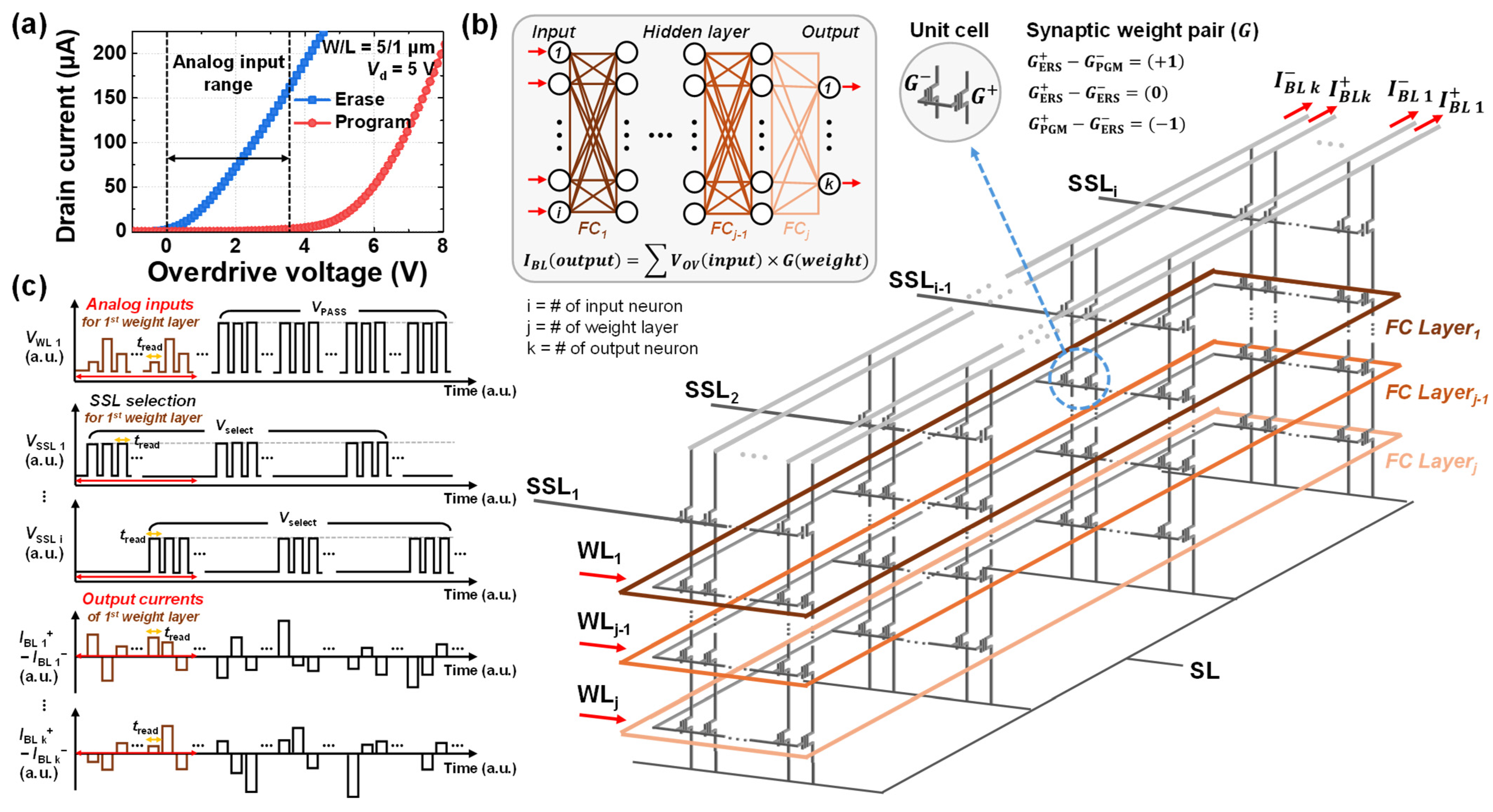

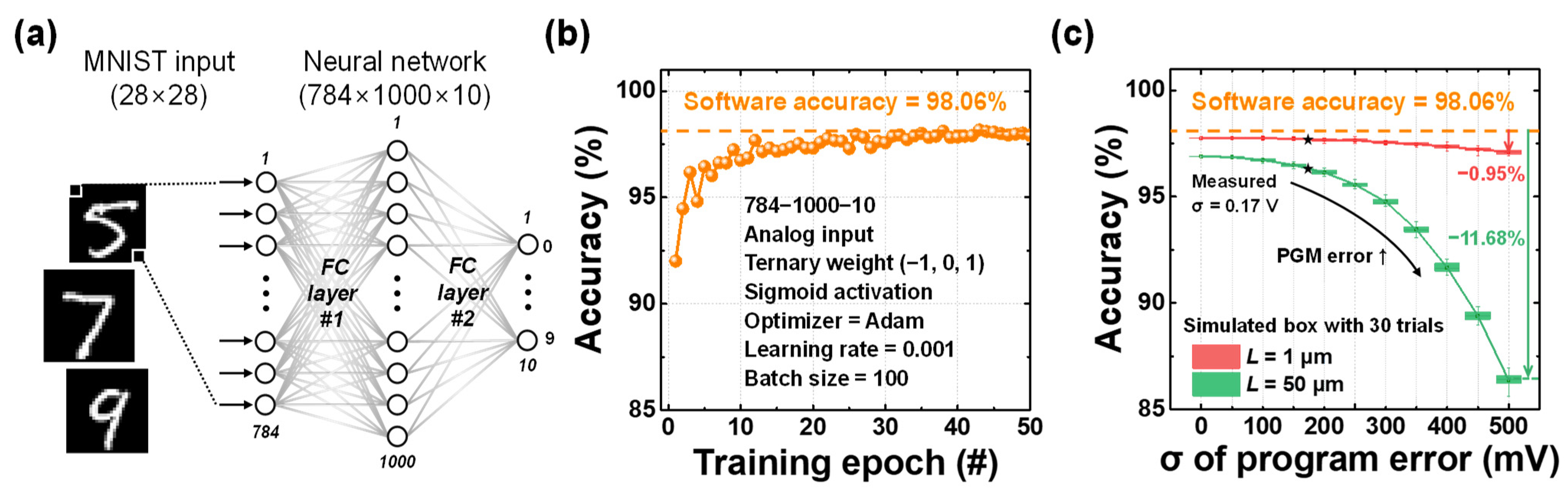

2. Device Fabrication and Electrical Characteristics

3. Wordline Input Bias Scheme for Neural Network Implementation

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Backus, J. Can programming be liberated from the von Neumann style? A functional style and its algebra of programs. Commun. ACM 1978, 21, 613–641. [Google Scholar] [CrossRef]

- Yu, S.; Jiang, H.; Huang, S.; Peng, X.; Lu, A. Compute-in-memory chips for deep learning: Recent trends and prospects. IEEE Circuits Syst. Mag. 2021, 21, 31–56. [Google Scholar] [CrossRef]

- Wouters, D.; Brackmann, L.; Jafari, A.; Bengel, C.; Mayahinia, M.; Waser, R.; Menzel, S.; Tahoori, M. Reliability of Computing-In-Memory Concepts Based on Memristive Arrays. In Proceedings of the 2022 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2022; pp. 5.3.1–5.3.4. [Google Scholar]

- Kim, K.; Song, M.S.; Hwang, H.; Hwang, S.; Kim, H. A comprehensive review of advanced trends: From artificial synapses to neuromorphic systems with consideration of non-ideal effects. Front. Neurosci. 2024, 18, 1279708. [Google Scholar] [CrossRef] [PubMed]

- Yu, J.; Lee, G.; Na, T. High-performance Sum Operation with Charge Saving and Sharing Circuit for MRAM-based In-memory Computing. J. Semicond. Technol. Sci. 2024, 24, 111–121. [Google Scholar] [CrossRef]

- Chen, L.; Huang, W.; Zhang, K.; Li, B.; Zhang, Z.; Feng, X.; Lin, K.; He, Y.; Zhao, W.; Zhang, Y. Orthogonal-Bulk-Spin-Orbit-Torque Device for All-Electrical In-Memory Computing. IEEE Electron Device Lett. 2024, 45, 504–507. [Google Scholar] [CrossRef]

- Liu, N.; Zhou, J.; Zheng, S.; Jin, F.; Fang, C.; Chen, B.; Liu, Y.; Hao, Y.; Han, G. Photoelectric In-memory Logic and Computing Achieved in HfO 2-based Ferroelectric Optoelectronic Memcapacitors. IEEE Electron Device Lett. 2024, 45, 1357–1360. [Google Scholar] [CrossRef]

- Wu, B.; Liu, K.; Yu, T.; Zhu, H.; Chen, K.; Yan, C.; Deng, E.; Liu, W. High-performance STT-MRAM-based computing-in-memory scheme utilizing data read feature. IEEE Trans. Nanotechnol. 2023, 22, 817–826. [Google Scholar] [CrossRef]

- Kim, C.-K.; Phadke, O.; Kim, T.-H.; Kim, M.-S.; Yu, J.-M.; Yoo, M.-S.; Choi, Y.-K.; Yu, S. Capacitive Synaptor with Overturned Charge Injection for Compute-in-Memory. IEEE Electron Device Lett. 2024, 45, 929–932. [Google Scholar] [CrossRef]

- Vasilopoulos, A.; Büchel, J.; Kersting, B.; Lammie, C.; Brew, K.; Choi, S.; Philip, T.; Saulnier, N.; Narayanan, V.; Le Gallo, M. Exploiting the state dependency of conductance variations in memristive devices for accurate in-memory computing. IEEE Trans. Electron Devices 2023, 70, 6279–6285. [Google Scholar] [CrossRef]

- Ling, Y.; Wang, Z.; Yu, Z.; Bao, S.; Yang, Y.; Bao, L.; Sun, Y.; Cai, Y.; Huang, R. Temperature-dependent accuracy analysis and resistance temperature correction in RRAM-based in-memory computing. IEEE Trans. Electron Devices 2023, 71, 294–300. [Google Scholar] [CrossRef]

- Quesada, E.P.-B.; Mahadevaiah, M.K.; Rizzi, T.; Wen, J.; Ulbricht, M.; Krstic, M.; Wenger, C.; Perez, E. Experimental assessment of multilevel rram-based vector-matrix multiplication operations for in-memory computing. IEEE Trans. Electron Devices 2023, 70, 2009–2014. [Google Scholar] [CrossRef]

- Shen, Z.; Zhao, C.; Qi, Y.; Xu, W.; Liu, Y.; Mitrovic, I.Z.; Yang, L.; Zhao, C. Advances of RRAM devices: Resistive switching mechanisms, materials and bionic synaptic application. Nanomaterials 2020, 10, 1437. [Google Scholar] [CrossRef]

- Wong, H.-S.P.; Lee, H.-Y.; Yu, S.; Chen, Y.-S.; Wu, Y.; Chen, P.-S.; Lee, B.; Chen, F.T.; Tsai, M.-J. Metal–oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Zahoor, F.; Azni Zulkifli, T.Z.; Khanday, F.A. Resistive random access memory (RRAM): An overview of materials, switching mechanism, performance, multilevel cell (MLC) storage, modeling, and applications. Nanoscale Res. Lett. 2020, 15, 90. [Google Scholar] [CrossRef]

- Youn, S.; Lee, J.; Kim, S.; Park, J.; Kim, K.; Kim, H. Programmable Threshold Logic Implementations in a Memristor Crossbar Array. Nano Lett. 2024, 24, 3581–3589. [Google Scholar] [CrossRef]

- Pan, F.; Gao, S.; Chen, C.; Song, C.; Zeng, F. Recent progress in resistive random access memories: Materials, switching mechanisms, and performance. Mater. Sci. Eng. R-Rep. 2014, 83, 1–59. [Google Scholar] [CrossRef]

- Park, J.; Kim, S.; Song, M.S.; Youn, S.; Kim, K.; Kim, T.-H.; Kim, H. Implementation of Convolutional Neural Networks in Memristor Crossbar Arrays with Binary Activation and Weight Quantization. ACS Appl. Mater. Interfaces 2024, 16, 1054–1065. [Google Scholar] [CrossRef]

- Duan, S.; Hu, X.; Dong, Z.; Wang, L.; Mazumder, P. Memristor-based cellular nonlinear/neural network: Design, analysis, and applications. IEEE Trans. Neural Netw. Learn. Syst. 2014, 26, 1202–1213. [Google Scholar] [CrossRef]

- Kim, T.-H.; Kim, S.; Park, J.; Youn, S.; Kim, H. Memristor Crossbar Array with Enhanced Device Yield for In-Memory Vector–Matrix Multiplication. ACS Appl. Electron. Mater. 2024, 6, 4099–4107. [Google Scholar] [CrossRef]

- Akinaga, H.; Shima, H. Resistive random access memory (ReRAM) based on metal oxides. Proc. IEEE 2010, 98, 2237–2251. [Google Scholar] [CrossRef]

- Kumar, A.; Krishnaiah, M.; Park, J.; Mishra, D.; Dash, B.; Jo, H.B.; Lee, G.; Youn, S.; Kim, H.; Jin, S.H. Multibit, Lead-Free Cs2SnI6 Resistive Random Access Memory with Self-Compliance for Improved Accuracy in Binary Neural Network Application. Adv. Funct. Mater. 2024, 34, 2310780. [Google Scholar] [CrossRef]

- Cai, F.; Correll, J.M.; Lee, S.H.; Lim, Y.; Bothra, V.; Zhang, Z.; Flynn, M.P.; Lu, W.D. A fully integrated reprogrammable memristor–CMOS system for efficient multiply–accumulate operations. Nat. Electron. 2019, 2, 290–299. [Google Scholar] [CrossRef]

- Kim, S.; Park, K.; Hong, K.; Kim, T.H.; Park, J.; Youn, S.; Kim, H.; Choi, W.Y. Overshoot-Suppressed Memristor Crossbar Array with High Yield by AlOx Oxidation for Neuromorphic System. Adv. Mater. Technol. 2024, 9, 2400063. [Google Scholar] [CrossRef]

- Li, Y.; Wang, Z.; Midya, R.; Xia, Q.; Yang, J.J. Review of memristor devices in neuromorphic computing: Materials sciences and device challenges. J. Phys. D Appl. Phys. 2018, 51, 503002. [Google Scholar] [CrossRef]

- Yu, D.; Ahn, S.; Youn, S.; Park, J.; Kim, H. True random number generator using stochastic noise signal of memristor with variation tolerance. Chaos Solitons Fractals 2024, 189, 115708. [Google Scholar] [CrossRef]

- Sarwat, S.G.; Kersting, B.; Moraitis, T.; Jonnalagadda, V.P.; Sebastian, A. Phase-change memtransistive synapses for mixed-plasticity neural computations. Nat. Nanotechnol. 2022, 17, 507–513. [Google Scholar] [CrossRef]

- Wang, L.; Ma, G.; Yan, S.; Cheng, X.; Miao, X. Reconfigurable Multilevel Storage and Neuromorphic Computing Based on Multilayer Phase-Change Memory. ACS Appl. Mater. Interfaces 2024, 16, 54829–54836. [Google Scholar] [CrossRef]

- Chen, X.; Xue, Y.; Sun, Y.; Shen, J.; Song, S.; Zhu, M.; Song, Z.; Cheng, Z.; Zhou, P. Neuromorphic Photonic Memory Devices Using Ultrafast, Non-Volatile Phase-Change Materials. Adv. Mater. 2023, 35, 2203909. [Google Scholar] [CrossRef]

- Hamid, S.B.; Khan, A.I.; Zhang, H.; Davydov, A.V.; Pop, E. Low-Energy Spiking Neural Network using Ge4Sb6Te7 Phase Change Memory Synapses. IEEE Electron Device Lett. 2024, 45, 1819–1822. [Google Scholar] [CrossRef]

- Kang, Y.G.; Ishii, M.; Park, J.; Shin, U.; Jang, S.; Yoon, S.; Kim, M.; Okazaki, A.; Ito, M.; Nomura, A. Solving Max-Cut Problem Using Spiking Boltzmann Machine Based on Neuromorphic Hardware with Phase Change Memory. Adv. Sci. 2024, 11, 2406433. [Google Scholar] [CrossRef]

- Boniardi, M.; Baldo, M.; Allegra, M.; Redaelli, A. Phase Change Memory: A Review on Electrical Behavior and Use in Analog In-Memory-Computing (A-IMC) Applications. Adv. Electron. Mater. 2024, 10, 2400599. [Google Scholar] [CrossRef]

- Pistolesi, L.; Ravelli, L.; Glukhov, A.; de Gracia Herranz, A.; Lopez-Vallejo, M.; Carissimi, M.; Pasotti, M.; Rolandi, P.; Redaelli, A.; Martín, I.M. Differential Phase Change Memory (PCM) Cell for Drift-Compensated In-Memory Computing. IEEE Trans. Electron Devices 2024, 71, 7447–7453. [Google Scholar] [CrossRef]

- Choi, S.; Kim, S. In-Series Phase-Change Memory Pair for Enhanced Data Retention and Large Window in Automotive Application. IEEE Electron Device Lett. 2024, 45, 2363–2366. [Google Scholar] [CrossRef]

- Li, N.; Mackin, C.; Chen, A.; Brew, K.; Philip, T.; Simon, A.; Saraf, I.; Han, J.P.; Sarwat, S.G.; Burr, G.W. Optimization of Projected Phase Change Memory for Analog In-Memory Computing Inference. Adv. Electron. Mater. 2023, 9, 2201190. [Google Scholar] [CrossRef]

- Rasch, M.J.; Mackin, C.; Le Gallo, M.; Chen, A.; Fasoli, A.; Odermatt, F.; Li, N.; Nandakumar, S.; Narayanan, P.; Tsai, H. Hardware-aware training for large-scale and diverse deep learning inference workloads using in-memory computing-based accelerators. Nat. Commun. 2023, 14, 5282. [Google Scholar] [CrossRef]

- Zhou, Z.; Jiao, L.; Zhou, J.; Zheng, Z.; Chen, Y.; Han, K.; Kang, Y.; Gong, X. Inversion-Type Ferroelectric Capacitive Memory and Its 1-Kbit Crossbar Array. IEEE Trans. Electron Devices 2023, 70, 1641–1647. [Google Scholar] [CrossRef]

- Soliman, M.; Maity, K.; Gloppe, A.; Mahmoudi, A.; Ouerghi, A.; Doudin, B.; Kundys, B.; Dayen, J.-F. Photoferroelectric all-van-der-Waals heterostructure for multimode neuromorphic ferroelectric transistors. ACS Appl. Mater. Interfaces 2023, 15, 15732–15744. [Google Scholar] [CrossRef]

- Dang, Z.; Guo, F.; Wang, Z.; Jie, W.; Jin, K.; Chai, Y.; Hao, J. Object motion detection enabled by reconfigurable neuromorphic vision sensor under ferroelectric modulation. ACS Nano 2024, 18, 27727–27737. [Google Scholar] [CrossRef]

- Xiang, H.; Chien, Y.C.; Li, L.; Zheng, H.; Li, S.; Duong, N.T.; Shi, Y.; Ang, K.W. Enhancing Memory Window Efficiency of Ferroelectric Transistor for Neuromorphic Computing via Two-Dimensional Materials Integration. Adv. Funct. Mater. 2023, 33, 2304657. [Google Scholar] [CrossRef]

- Kim, S.; Kim, J.; Kim, D.; Kim, J.; Kim, S. Neuromorphic synaptic applications of HfAlOx-based ferroelectric tunnel junction annealed at high temperatures to achieve high polarization. APL Mater. 2023, 11, 101102. [Google Scholar] [CrossRef]

- Koo, R.H.; Shin, W.; Kim, J.; Yim, J.; Ko, J.; Jung, G.; Im, J.; Park, S.H.; Kim, J.J.; Cheema, S.S. Polarization Pruning: Reliability Enhancement of Hafnia-Based Ferroelectric Devices for Memory and Neuromorphic Computing. Adv. Sci. 2024, 11, 2407729. [Google Scholar] [CrossRef]

- Li, Z.; Meng, J.; Yu, J.; Liu, Y.; Wang, T.; Liu, P.; Chen, S.; Zhu, H.; Sun, Q.; Zhang, D.W. CMOS compatible low power consumption ferroelectric synapse for neuromorphic computing. IEEE Electron Device Lett. 2023, 44, 532–535. [Google Scholar] [CrossRef]

- Huang, W.-Y.; Nie, L.-H.; Lai, X.-C.; Fang, J.-L.; Chen, Z.-L.; Chen, J.-Y.; Jiang, Y.-P.; Tang, X.-G. Synaptic Properties of a PbHfO3 Ferroelectric Memristor for Neuromorphic Computing. ACS Appl. Mater. Interfaces 2024, 16, 23615–23624. [Google Scholar] [CrossRef]

- Gao, J.; Chien, Y.C.; Li, L.; Lee, H.K.; Samanta, S.; Varghese, B.; Xiang, H.; Li, M.; Liu, C.; Zhu, Y. Ferroelectric Aluminum Scandium Nitride Transistors with Intrinsic Switching Characteristics and Artificial Synaptic Functions for Neuromorphic Computing. Small 2024, 20, 2404711. [Google Scholar] [CrossRef]

- Lu, T.; Zhao, X.; Liu, H.; Yan, Z.; Zhao, R.; Shao, M.; Yan, J.; Yang, M.; Yang, Y.; Ren, T.-L. Optimal Weight Models for Ferroelectric Synapses Toward Neuromorphic Computing. IEEE Trans. Electron Devices 2023, 70, 2297–2303. [Google Scholar] [CrossRef]

- Lee, S.-T.; Lee, J.-H. Review of neuromorphic computing based on NAND flash memory. Nanoscale Horiz. 2024, 9, 1475–1492. [Google Scholar] [CrossRef]

- Kim, J.P.; Kim, S.K.; Park, S.; Kuk, S.-H.; Kim, T.; Kim, B.H.; Ahn, S.-H.; Cho, Y.-H.; Jeong, Y.; Choi, S.-Y. Dielectric-engineered high-speed, low-power, highly reliable charge trap flash-based synaptic device for neuromorphic computing beyond inference. Nano Lett. 2023, 23, 451–461. [Google Scholar] [CrossRef]

- Park, E.; Jang, S.; Noh, G.; Jo, Y.; Lee, D.K.; Kim, I.S.; Song, H.-C.; Kim, S.; Kwak, J.Y. Indium–Gallium–Zinc Oxide-Based Synaptic Charge Trap Flash for Spiking Neural Network-Restricted Boltzmann Machine. Nano Lett. 2023, 23, 9626–9633. [Google Scholar] [CrossRef]

- Hwang, S.; Yu, J.; Song, M.S.; Hwang, H.; Kim, H. Memcapacitor crossbar array with charge trap NAND flash structure for neuromorphic computing. Adv. Sci. 2023, 10, 2303817. [Google Scholar] [CrossRef]

- Zhu, A.; Jin, L.; Jia, J.; Ye, T.; Zeng, M.; Huo, Z. HCMS: A Hybrid Conductance Modulation Scheme Based on Cell-to-Cell Z-Interference for 3D NAND Neuromorphic Computing. IEEE J. Electron Devices Soc. 2024. [Google Scholar] [CrossRef]

- Xiang, Y.; Huang, P.; Han, R.; Li, C.; Wang, K.; Liu, X.; Kang, J. Efficient and robust spike-driven deep convolutional neural networks based on NOR flash computing array. IEEE Trans. Electron Devices 2020, 67, 2329–2335. [Google Scholar] [CrossRef]

- Feng, Y.; Tang, M.; Sun, Z.; Qi, Y.; Zhan, X.; Liu, J.; Zhang, J.; Wu, J.; Chen, J. Fully flash-based reservoir computing network with low power and rich states. IEEE Trans. Electron Devices 2023, 70, 4972–4975. [Google Scholar] [CrossRef]

- Wang, H.; Lu, Y.; Liu, S.; Yu, J.; Hu, M.; Li, S.; Yang, R.; Watanabe, K.; Taniguchi, T.; Ma, Y. Adaptive Neural Activation and Neuromorphic Processing via Drain-Injection Threshold-Switching Float Gate Transistor Memory. Adv. Mater. 2023, 35, 2309099. [Google Scholar] [CrossRef]

- Hwang, H.; Song, M.S.; Youn, S.; Kim, H. True Random Number Generator using Memcapacitor with Charge Trapping Layer. IEEE Electron Device Lett. 2024, 45, 1464–1467. [Google Scholar] [CrossRef]

- Ansari, M.H.R.; El-Atab, N. Efficient Implementation of Boolean Logic Functions Using Double Gate Charge-Trapping Memory for In-Memory Computing. IEEE Trans. Electron Devices 2024, 71, 1879–1885. [Google Scholar] [CrossRef]

- Wang, P.; Xu, F.; Wang, B.; Gao, B.; Wu, H.; Qian, H.; Yu, S. Three-dimensional NAND flash for vector–matrix multiplication. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 27, 988–991. [Google Scholar] [CrossRef]

- Lee, S.-T.; Lim, S.; Choi, N.Y.; Bae, J.-H.; Kwon, D.; Park, B.-G.; Lee, J.-H. Operation scheme of multi-layer neural networks using NAND flash memory as high-density synaptic devices. IEEE J. Electron Devices Soc. 2019, 7, 1085–1093. [Google Scholar] [CrossRef]

- Lue, H.-T.; Hsu, P.-K.; Wei, M.-L.; Yeh, T.-H.; Du, P.-Y.; Chen, W.-C.; Wang, K.-C.; Lu, C.-Y. Optimal design methods to transform 3D NAND flash into a high-density, high-bandwidth and low-power nonvolatile computing in memory (nvCIM) accelerator for deep-learning neural networks (DNN). In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 38.31.31–38.31.34. [Google Scholar]

- Lee, S.-T.; Lee, J.-H. Neuromorphic computing using NAND flash memory architecture with pulse width modulation scheme. Front. Neurosci. 2020, 14, 571292. [Google Scholar] [CrossRef]

- Sodini, C.G.; Ko, P.-K.; Moll, J.L. The effect of high fields on MOS device and circuit performance. IEEE Trans. Electron Devices 1984, 31, 1386–1393. [Google Scholar] [CrossRef]

- Duvvury, C. A guide to short-channel effects in MOSFETs. IEEE Circuits Devices Mag. 1986, 2, 6–10. [Google Scholar] [CrossRef]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; et al. Bit Cost Scalable technology with Punch and plug process for ultra high density flash memory. In Proceedings of the 2007 IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 14–15. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hwang, H.; Kim, G.; Yu, D.; Kim, H. Wordline Input Bias Scheme for Neural Network Implementation in 3D-NAND Flash. Biomimetics 2025, 10, 318. https://doi.org/10.3390/biomimetics10050318

Hwang H, Kim G, Yu D, Kim H. Wordline Input Bias Scheme for Neural Network Implementation in 3D-NAND Flash. Biomimetics. 2025; 10(5):318. https://doi.org/10.3390/biomimetics10050318

Chicago/Turabian StyleHwang, Hwiho, Gyeonghae Kim, Dayeon Yu, and Hyungjin Kim. 2025. "Wordline Input Bias Scheme for Neural Network Implementation in 3D-NAND Flash" Biomimetics 10, no. 5: 318. https://doi.org/10.3390/biomimetics10050318

APA StyleHwang, H., Kim, G., Yu, D., & Kim, H. (2025). Wordline Input Bias Scheme for Neural Network Implementation in 3D-NAND Flash. Biomimetics, 10(5), 318. https://doi.org/10.3390/biomimetics10050318