Proposal of a Cascade Photonic Crystal XOR Logic Gate for Optical Integrated Circuits with Investigation of Fabrication Error and Optical Power Changes

Abstract

:1. Introduction

2. Important Parameters in Evaluating the Efficiency of All-Optical Logic Gates

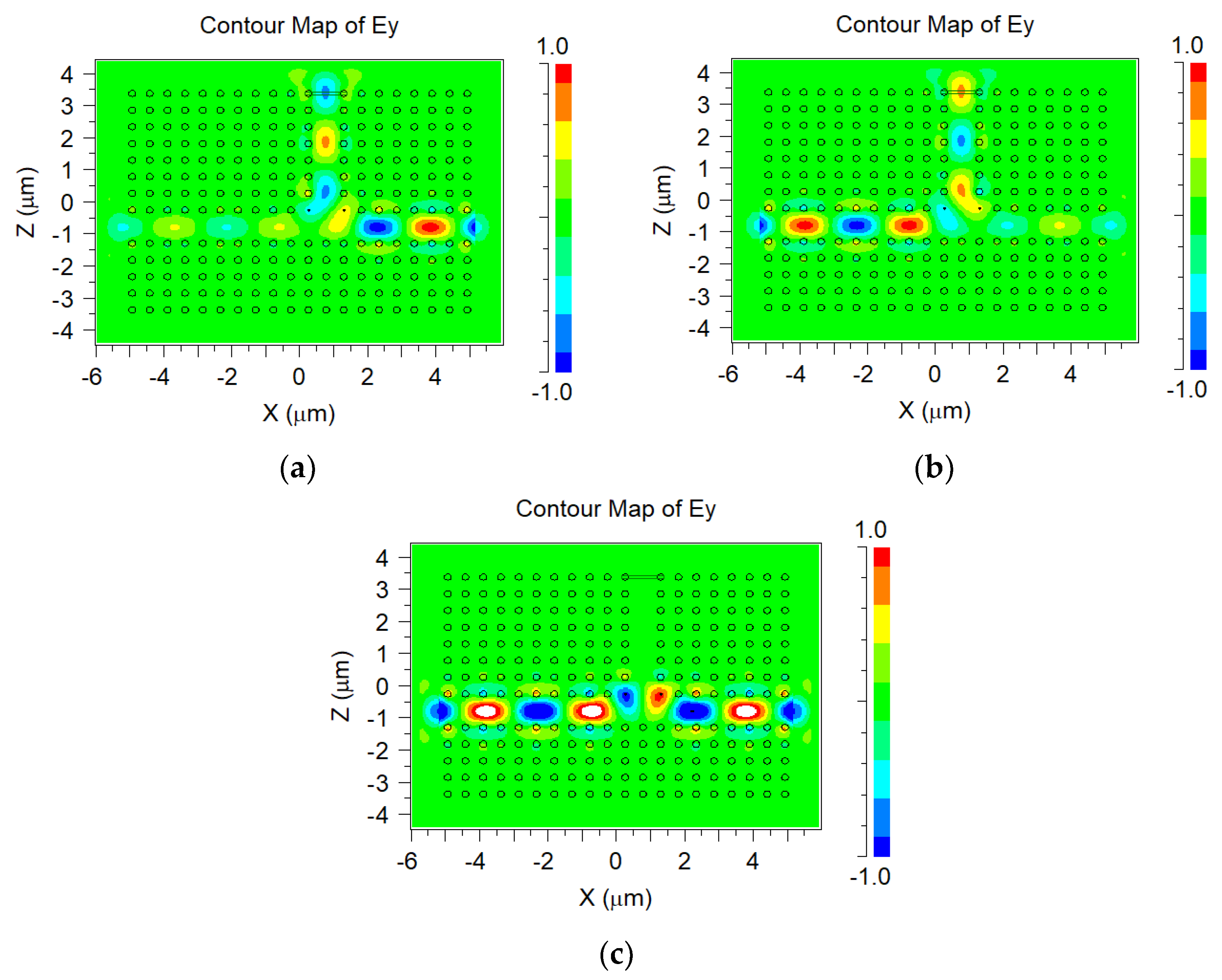

3. The General Structure of the Logic Gate’s Parameters

4. Assessing the Performance of the Logic Gate

5. Investigating the Efficiency of XOR Logic Gates in Optical Integrated Circuits

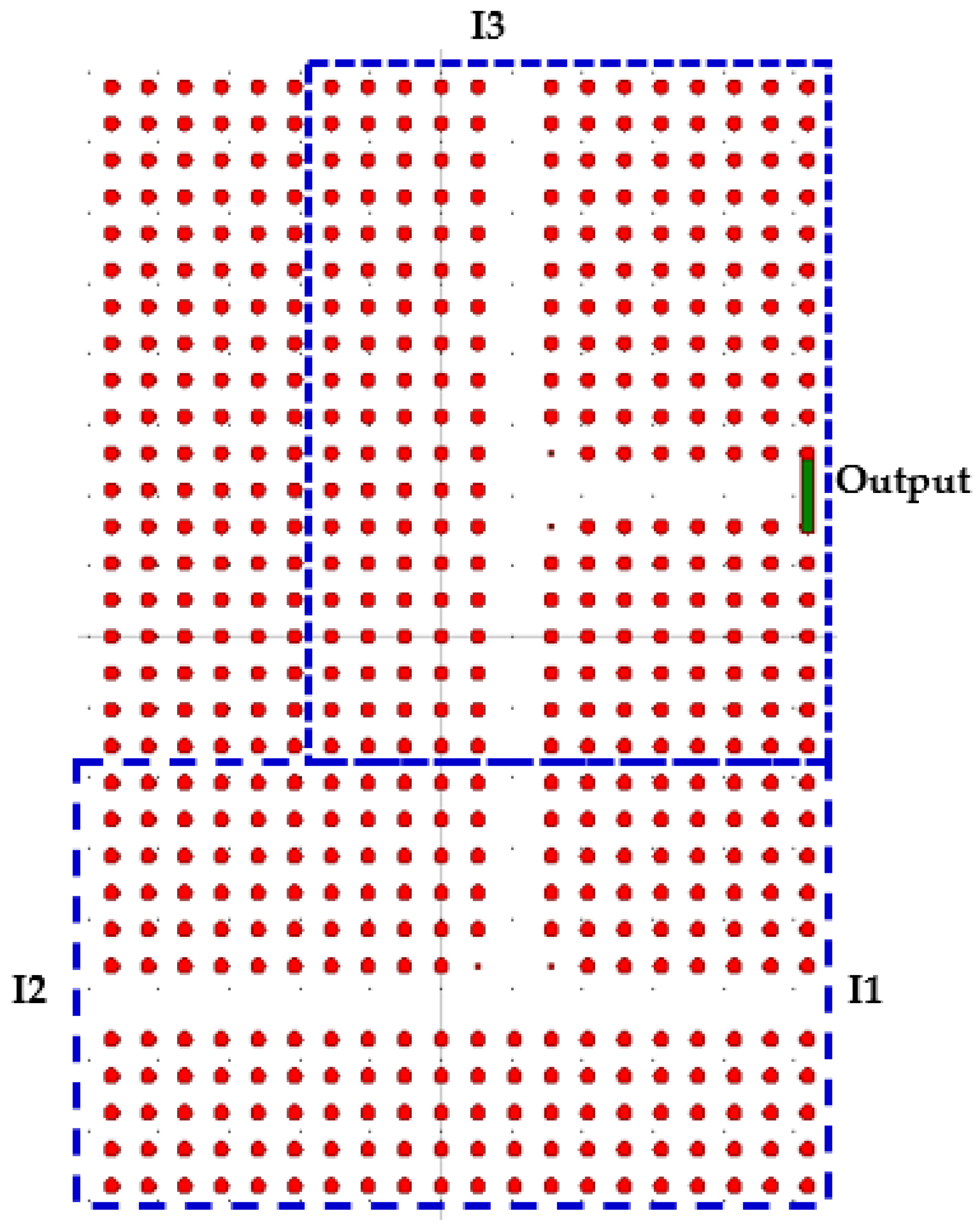

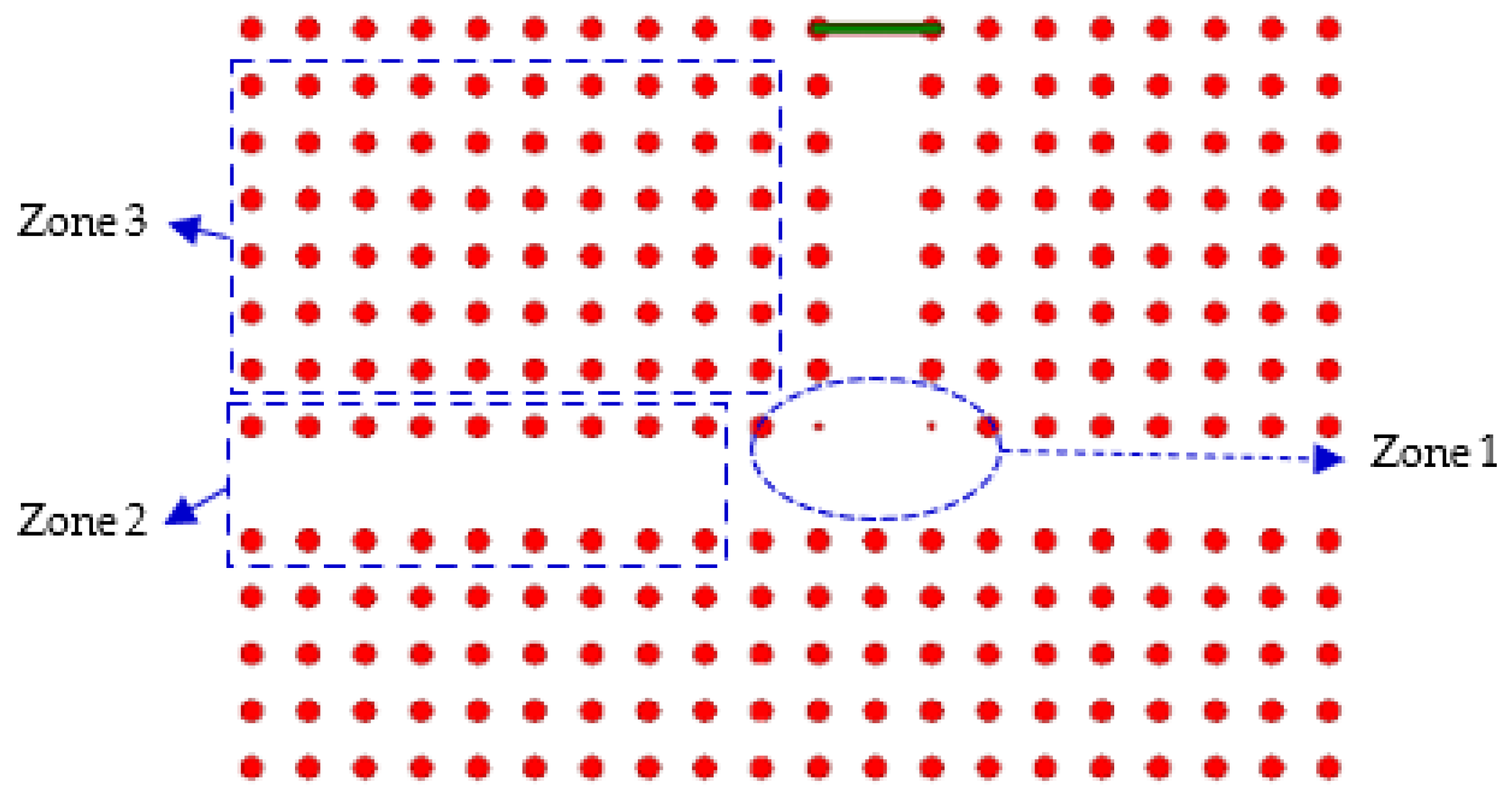

5.1. Cascade All-Optical XOR Logic Gate

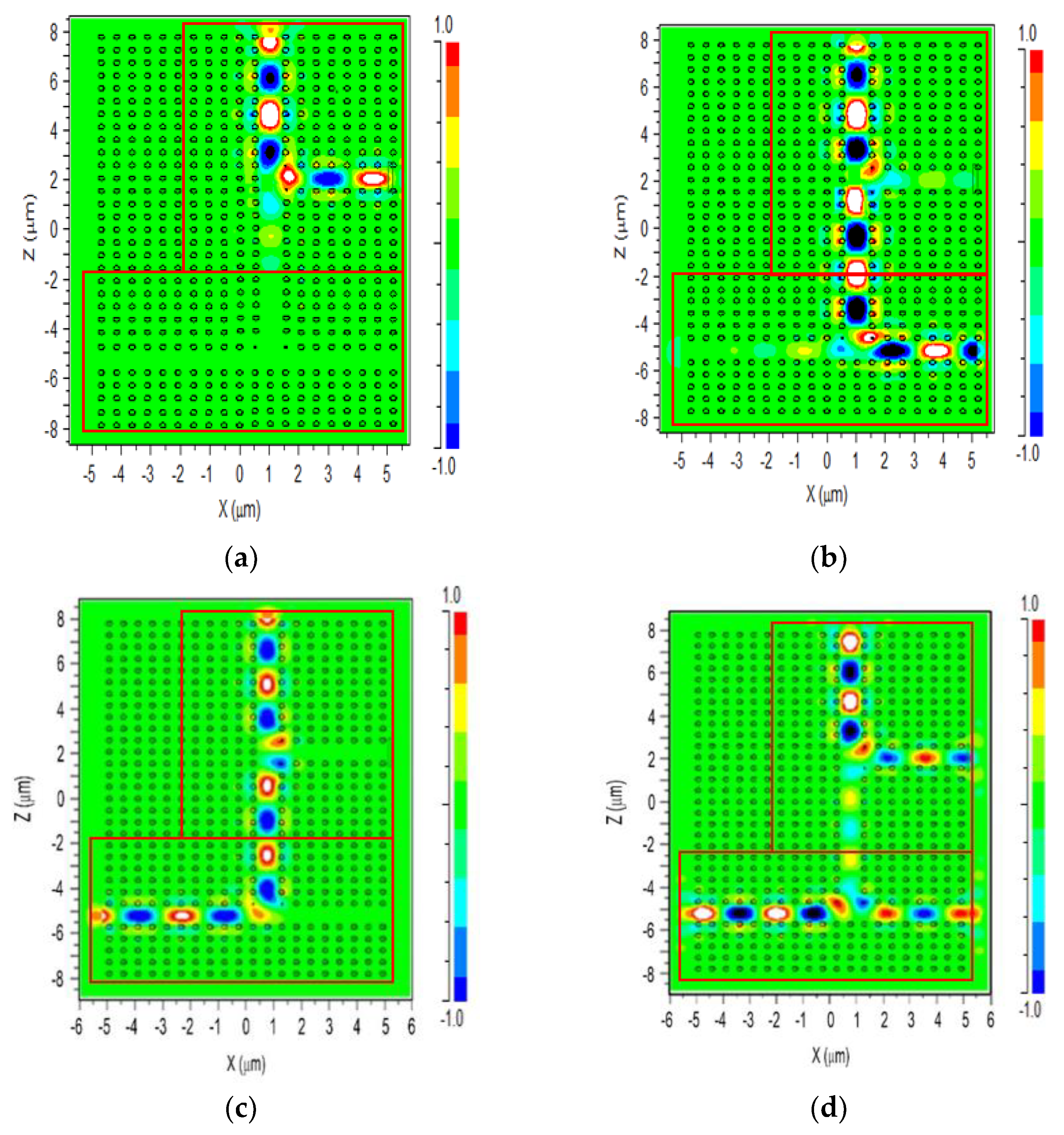

5.2. Investigating the Effects of Fabrication Error

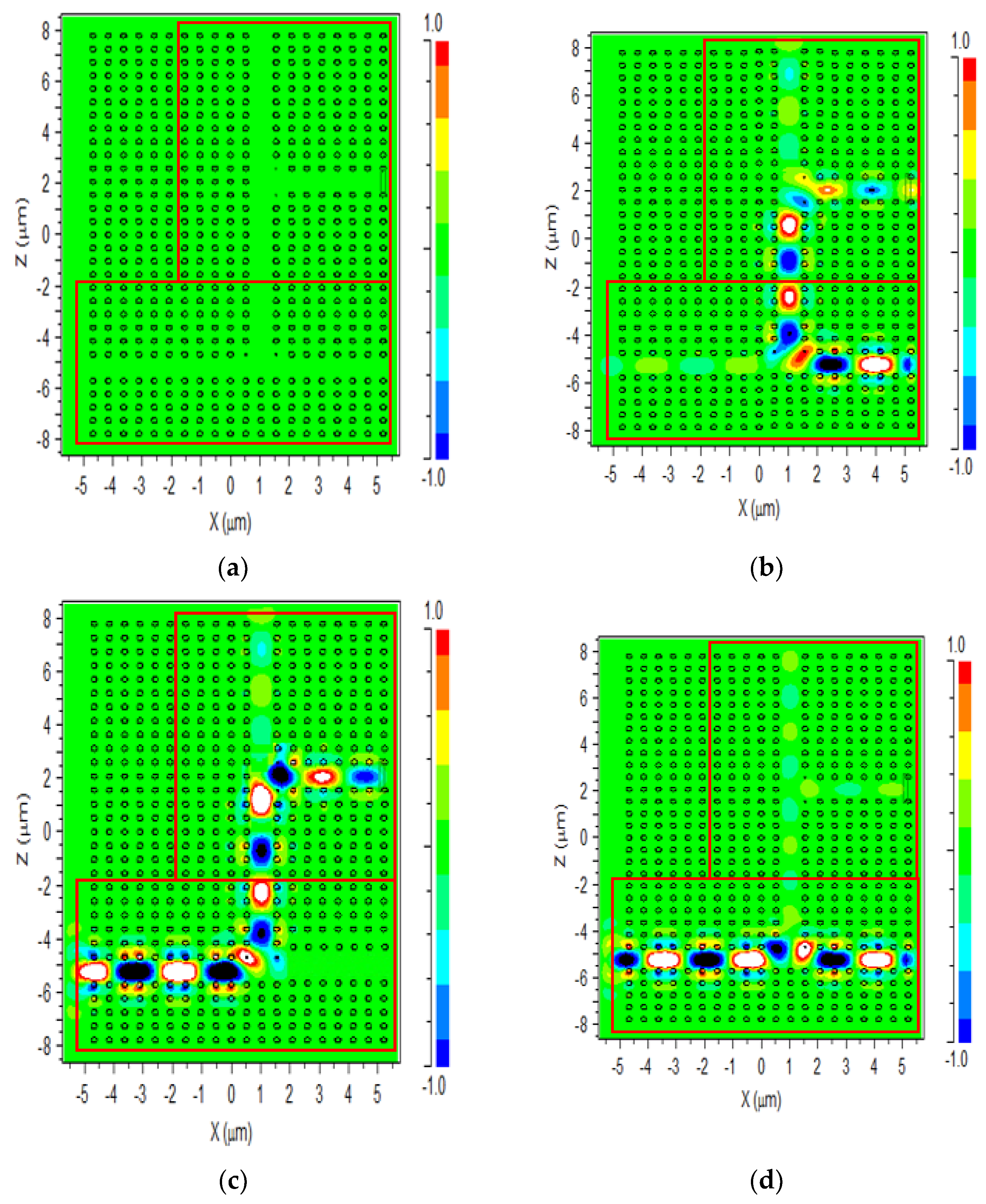

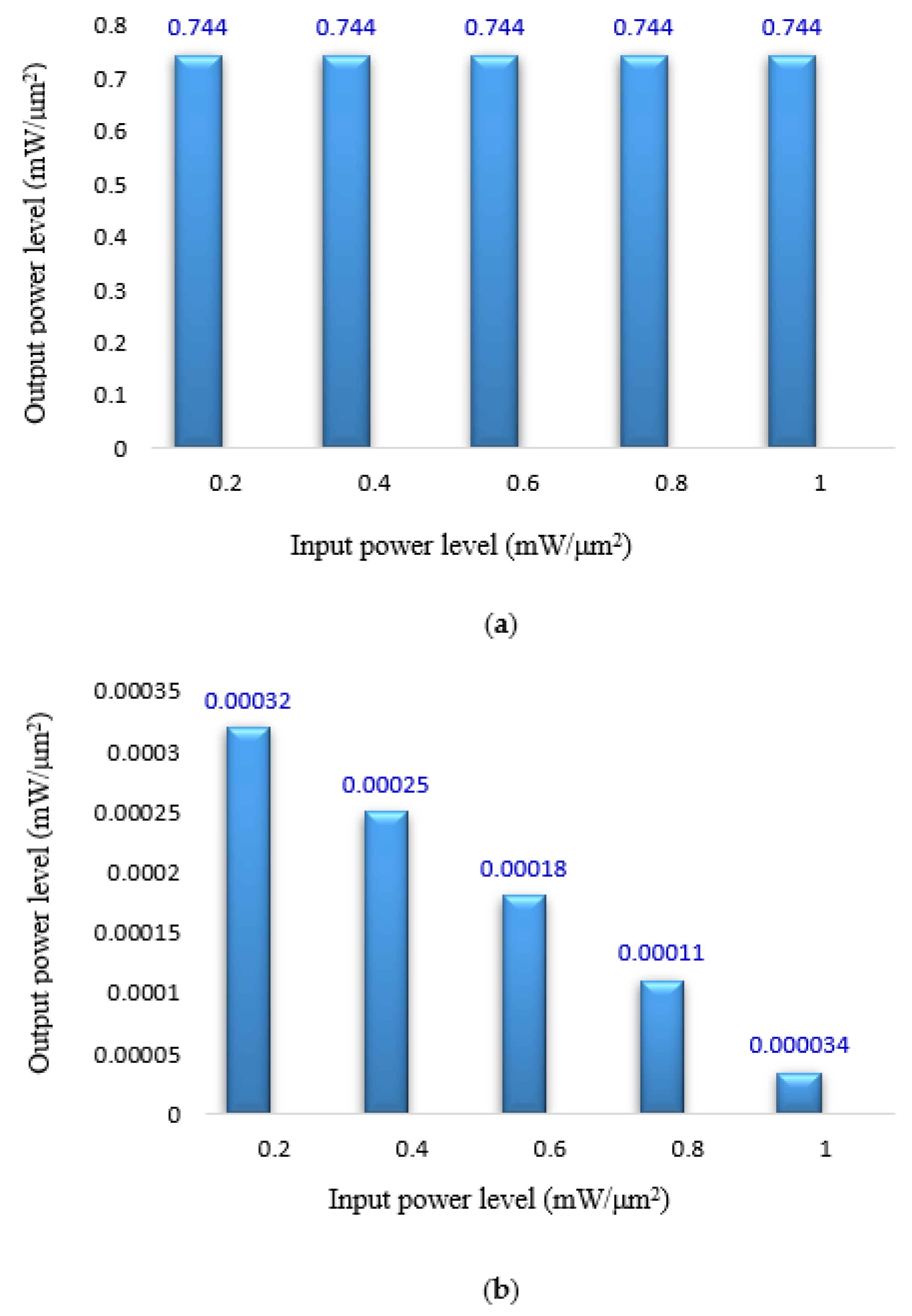

5.3. Investigating the Effects of Changing the Input Optical Power

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Delphi, G.; Olyaee, S.; Seifouri, M.; Mohebzadeh-Bahabady, A. Design of an add filter and a 2-channel optical demultiplexer with high-quality factor based on nano-ring resonator. J. Comput. Electron. 2019, 18, 1372–1378. [Google Scholar] [CrossRef]

- Sharma, S.; Roy, S. A survey on design and synthesis techniques for photonic integrated circuits. J. Supercomput. 2021, 77, 4332–4374. [Google Scholar] [CrossRef]

- Olyaee, S.; Mohebzadeh-Bahabady, A. Designing a novel photonic crystal nano-ring resonator for biosensor application. Opt. Quantum Electron. 2015, 47, 1881–1888. [Google Scholar] [CrossRef]

- Liu, W.; Yang, D.; Shen, G.; Tian, H.; Ji, Y. Design of ultra compact all-optical XOR, XNOR, NAND and OR gates using photonic crystal multi-mode interference waveguides. Opt. Laser Technol. 2013, 50, 55–64. [Google Scholar] [CrossRef]

- Kumar, A.; Medhekar, S. All optical NOR and NAND gates using four circular cavities created in 2D nonlinear photonic crystal. Opt. Laser Technol. 2020, 123, 105910. [Google Scholar] [CrossRef]

- Seifouri, M.; Olyaee, S.; Sardari, M.; Mohebzadeh-Bahabady, A. Ultra-fast and compact all-optical half adder using 2D photonic crystals. IET Optoelectron. 2019, 13, 139–143. [Google Scholar] [CrossRef]

- Parandin, F. High contrast ratio all-optical 4 × 2 encoder based on two-dimensional photonic crystals. Opt. Laser Technol. 2019, 113, 447–452. [Google Scholar] [CrossRef]

- Kotb, A.; Zoiros, K.E.; Guo, C. Ultrafast performance of all-optical AND and OR logic operations at 160 Gb/s using photonic crystal semiconductor optical amplifier. Opt. Laser Technol. 2019, 119, 105611. [Google Scholar] [CrossRef]

- Mohebzadeh-Bahabady, A.; Olyaee, S. Designing low power and high contrast ratio all-optical NOT logic gate for using in optical integrated circuits. Opt. Quantum Electron. 2018, 51, 3. [Google Scholar] [CrossRef]

- Ghadrdan, M.; Mansouri-Birjandi, A. Concurrent implementation of all-optical half-adder and AND & XOR logic gates based on nonlinear photonic crystal. Opt. Quantum Electron. 2013, 45, 1027–1036. [Google Scholar]

- Fu, Y.; Hu, X.; Gong, Q. Silicon photonic crystal all-optical logic gates. Phys. Lett. A 2013, 377, 329–333. [Google Scholar] [CrossRef]

- Mohebbi, Z.; Nozhat, N.; Emami, F. High contrast all-optical logic gates based on 2D nonlinear photonic crystal. Opt. Commun. 2015, 355, 130–136. [Google Scholar] [CrossRef]

- D’Souza, N.M.; Mathew, V. Interference based square lattice photonic crystal logic gates working with different wavelengths. Opt. Laser Technol. 2016, 80, 214–219. [Google Scholar] [CrossRef]

- Hussein, H.; Ali, T.; Rafat, N. New designs of a complete set of Photonic Crystals logic gates. Opt. Commun. 2018, 411, 175–181. [Google Scholar] [CrossRef]

- Olyaee, S.; Seifouri, M.; Mohebzadeh-Bahabady, A.; Sardari, M. Realization of all-optical NOT and XOR logic gates based on interference effect with high contrast ratio and ultra-compacted size. Opt. Quantum Electron. 2018, 50, 385. [Google Scholar] [CrossRef]

- Parandin, F.; Karkhanehchi, M.M. Terahertz all-optical NOR and AND logic gates based on 2D photonic crystals. Superlattices Microstruct. 2017, 101, 253–260. [Google Scholar] [CrossRef]

- Andalib, P.; Granpayeh, N. All-optical ultra-compact photonic crystal NOR gate based on nonlinear ring resonators. J. Opt. A Pure Appl. Opt. 2009, 11, 85203. [Google Scholar] [CrossRef]

- Maleki, M.-J.; Soroosh, M.; Mir, A. Ultra-fast all-optical 2-to-4 decoder based on a photonic crystal structure. Appl. Opt. 2020, 59, 5422. [Google Scholar] [CrossRef]

- Sharifi, H.; Hamidi, S.M.; Navi, K. A design procedure for fan-out improvement in all-optical photonic crystal logic design. Opt. Quantum Electron. 2019, 51, 340. [Google Scholar] [CrossRef]

- Park, I.; Lee, H.-S.; Kim, H.-J.; Moon, K.-M.; Lee, S.-G.; Beom-Hoan, O.; Park, S.-G.; Lee, E.-H. Photonic crystal power-splitter based on directional coupling. Opt. Express 2004, 12, 3599–3604. [Google Scholar] [CrossRef]

- Mohebzadeh-Bahabady, A.; Olyaee, S. Designing an ultracompact all-optical 4-to-2 encoder and investigating its optical power consumption. Appl. Opt. 2020, 59, 2409–2415. [Google Scholar] [CrossRef] [PubMed]

- Bai, J.; Wang, J.; Jiang, J.; Chen, X.; Li, H.; Qiu, Y.; Qiang, Z. Photonic NOT and NOR gates based on a single compact photonic crystal ring resonator. Appl. Opt. 2009, 48, 6923–6927. [Google Scholar] [CrossRef] [PubMed]

- Campbell, M.M.; Sharp, D.N.; Harrison, M.T.; Denning, R.G.; Turberfield, A. Fabrication of photonic crystals for the visible spectrum by holographic lithography. Nat. Cell Biol. 2000, 404, 53–56. [Google Scholar] [CrossRef]

- Bogaerts, W.; Wiaux, V.; Taillaert, D.; Beckx, S.; Luyssaert, B.; Bienstman, P.; Baets, R.; Bogaerts, W.; Wiaux, V.; Taillaert, D.; et al. Fabrication of photonic crystals in silicon-on-insulator using 248-nm deep UV lithography. IEEE J. Sel. Top. Quantum Electron. 2002, 8, 928–934. [Google Scholar] [CrossRef]

- Assefa, S.; Rakich, P.T.; Bienstman, P.; Johnson, S.G.; Petrich, G.S.; Joannopoulos, J.D.; Kolodziejski, L.A.; Ippen, E.P.; Smith, H.I. Guiding 1.5 μm light in photonic crystals based on dielectric rods. Appl. Phys. Lett. 2004, 85, 6110–6112. [Google Scholar] [CrossRef]

- Shih, T.-M.; Kurs, A.; Dahlem, M.; Petrich, G.; Soljačic, M.; Ippen, E.; Kolodziejski, L.; Hall, K.; Kesler, M. Supercollimation in photonic crystals composed of silicon rods. Appl. Phys. Lett. 2008, 93, 131111. [Google Scholar] [CrossRef] [Green Version]

- Suemitsu, M.; Asano, T.; De Zoysa, M.; Noda, S. Wavelength-selective thermal emitters using Si-rods on MgO. Appl. Phys. Lett. 2018, 112, 011103. [Google Scholar] [CrossRef]

- Mohebzadeh-Bahabady, A.; Olyaee, S. All-optical NOT and XOR logic gates using photonic crystal nano-resonator and based on an interference effect. IET Optoelectron. 2018, 12, 191–195. [Google Scholar] [CrossRef]

- Rani, P.; Fatima, S.; Kalra, Y.; Sinha, R. Realization of all optical logic gates using universal NAND gates on photonic crystal platform. Superlattices Microstruct. 2017, 109, 619–625. [Google Scholar] [CrossRef]

- Shaik, E.H.; Rangaswamy, N. Realization of XNOR logic function with all-optical high contrast XOR and NOT gates. Opto-Electron. Rev. 2018, 26, 63–72. [Google Scholar] [CrossRef]

- Jianga, Y.C.; Liua, S.B.; Zhanga, H.F. Reconfigurable design of logic gates based on a two-dimensional photonic crystals waveguide structure. Opt. Commun. 2014, 332, 359–3653. [Google Scholar] [CrossRef]

- Parandin, F.; Malmir, M.R.; Naseri, M.; Zahedi, A. Reconfigurable all-optical NOT, XOR, and NOR logic gates based on two dimensional photonic crystals. Superlattices Microstruct. 2018, 113, 737–744. [Google Scholar] [CrossRef]

| Input Power A | Input Power B | Output Power × 10−3 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | Pin | 740Pin |

| Pin | 0 | 744Pin |

| Pin | Pin | 0.034Pin |

| Input Power I3 | Input Power I2 | Input Power I1 | Output Power × 10−3 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | Pin | 618Pin |

| 0 | Pin | 0 | 621Pin |

| 0 | Pin | Pin | 0.023Pin |

| Pin | 0 | 0 | 728Pin |

| Pin | 0 | Pin | 0.023Pin |

| Pin | Pin | 0 | 0.023Pin |

| Pin | Pin | Pin | 709Pin |

| Crystal Lattice Type | Contrast Ratio (dB) | Power at Zero Logic Value (mW/μm2) | Power at One Logic Value (mW/μm2) | Delay Time (ps) | Size (μm2) | |

|---|---|---|---|---|---|---|

| This paper | Square | 43.38 | 3.4 × 10−5 | 0.740 | 0.317 | 66.53 |

| [10] | Square | 5.67 | 0.22 | 0.81 | 0.85 | 168 |

| [11] | Triangular | 21.44 | 0.0061 | 0.85 | -- | 620 |

| [14] | Square | 12.155 | 0.0182 | 0.535 | -- | 155 |

| [28] | Triangular | 19.28 | 0.0078 | 0.776 | 0.466 | 136 |

| [29] | Triangular | 6.50 | 0.133 | 0.574 | -- | |

| [30] | Square | 55.23 | 1.2 × 10−6 | 0.4 | 0.136 | 106 |

| [31] | Triangular | 8.95 | 0.07 | 0.55 | -- | 729 |

| [32] | Triangular | 30 | -- | -- | 0.10 | 105 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mohebzadeh-Bahabady, A.; Olyaee, S. Proposal of a Cascade Photonic Crystal XOR Logic Gate for Optical Integrated Circuits with Investigation of Fabrication Error and Optical Power Changes. Photonics 2021, 8, 392. https://doi.org/10.3390/photonics8090392

Mohebzadeh-Bahabady A, Olyaee S. Proposal of a Cascade Photonic Crystal XOR Logic Gate for Optical Integrated Circuits with Investigation of Fabrication Error and Optical Power Changes. Photonics. 2021; 8(9):392. https://doi.org/10.3390/photonics8090392

Chicago/Turabian StyleMohebzadeh-Bahabady, Ahmad, and Saeed Olyaee. 2021. "Proposal of a Cascade Photonic Crystal XOR Logic Gate for Optical Integrated Circuits with Investigation of Fabrication Error and Optical Power Changes" Photonics 8, no. 9: 392. https://doi.org/10.3390/photonics8090392

APA StyleMohebzadeh-Bahabady, A., & Olyaee, S. (2021). Proposal of a Cascade Photonic Crystal XOR Logic Gate for Optical Integrated Circuits with Investigation of Fabrication Error and Optical Power Changes. Photonics, 8(9), 392. https://doi.org/10.3390/photonics8090392