A Novel PWM Signal-Generation Strategy for Pockels Cell Drivers

Abstract

1. Introduction

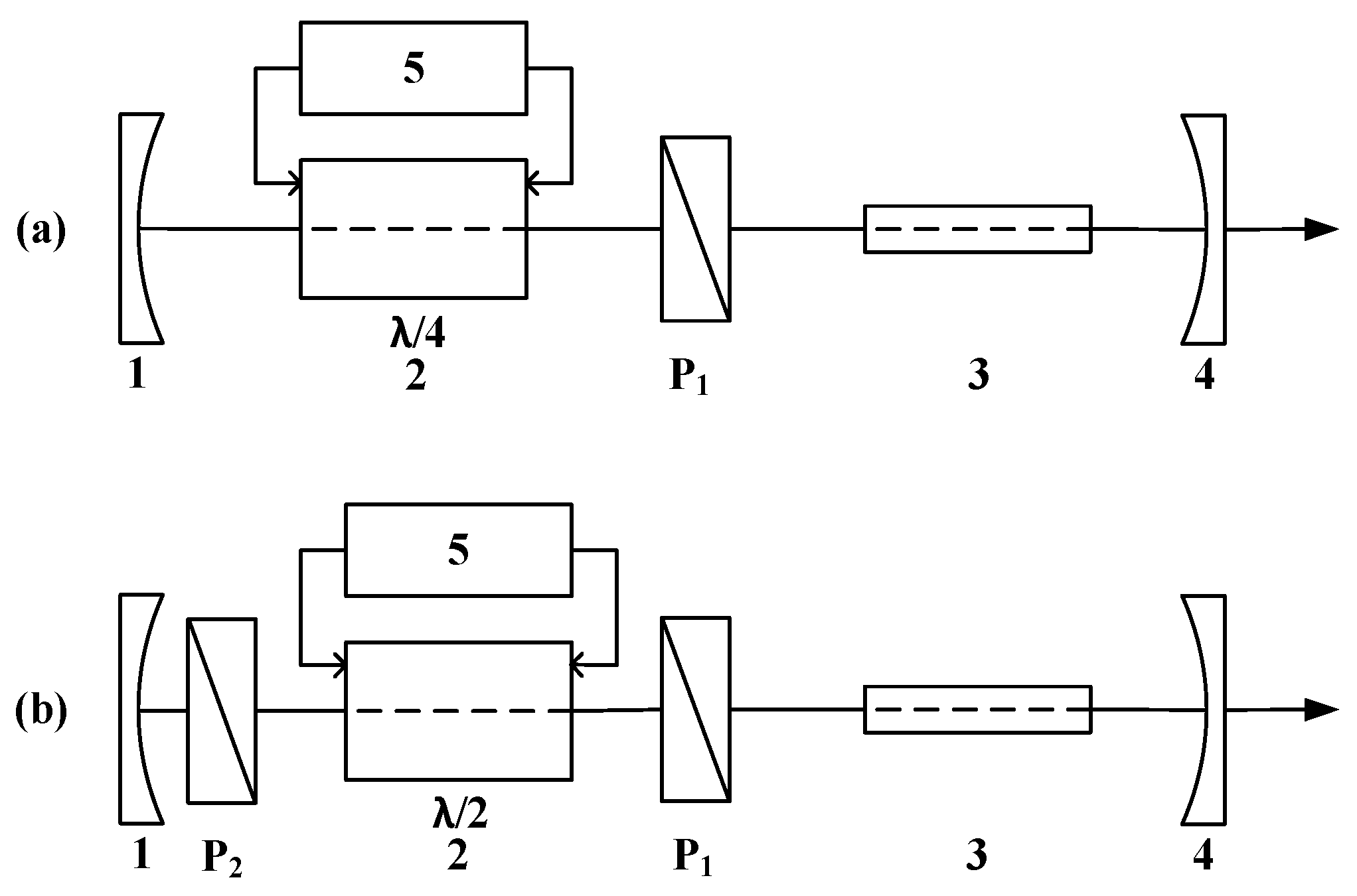

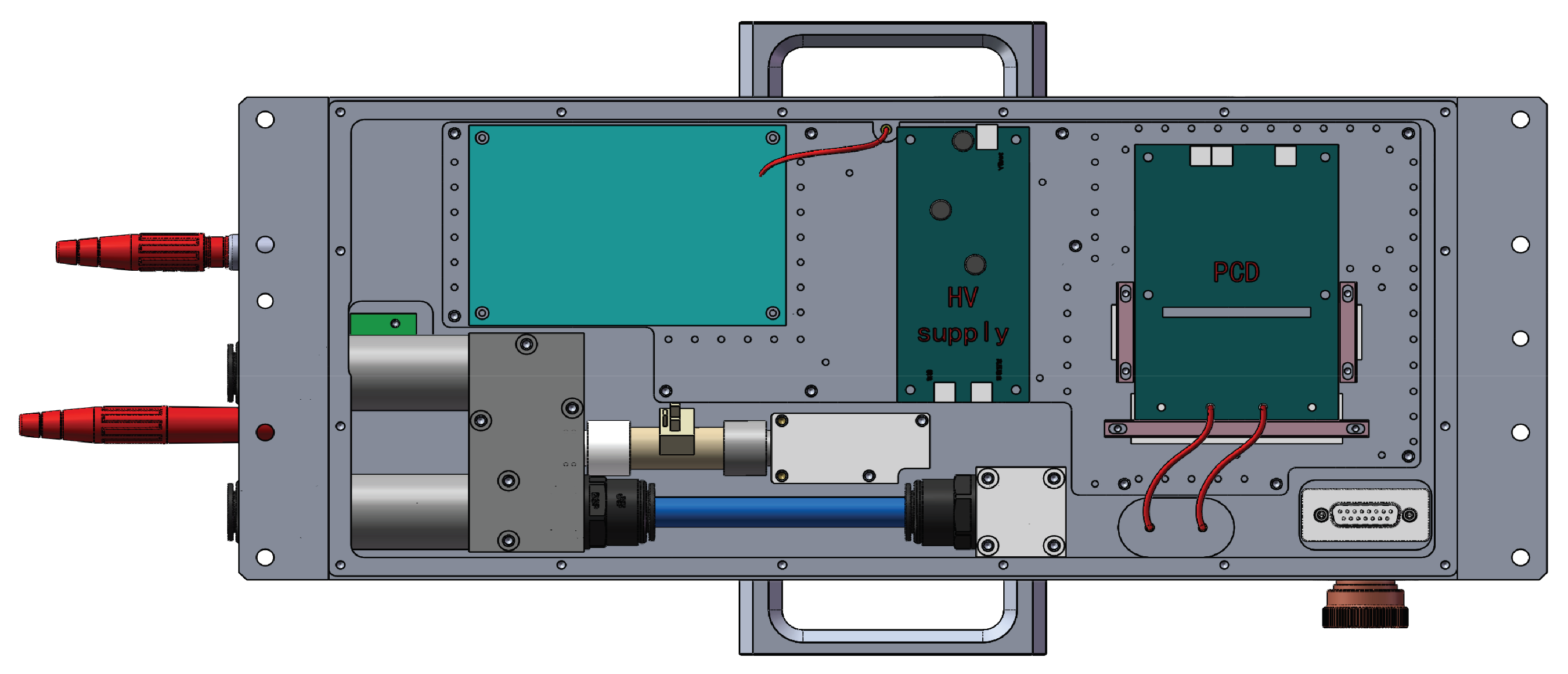

1.1. Description of a PCD

1.2. Major Factors Affecting PCD Performance

1.2.1. Switching Components

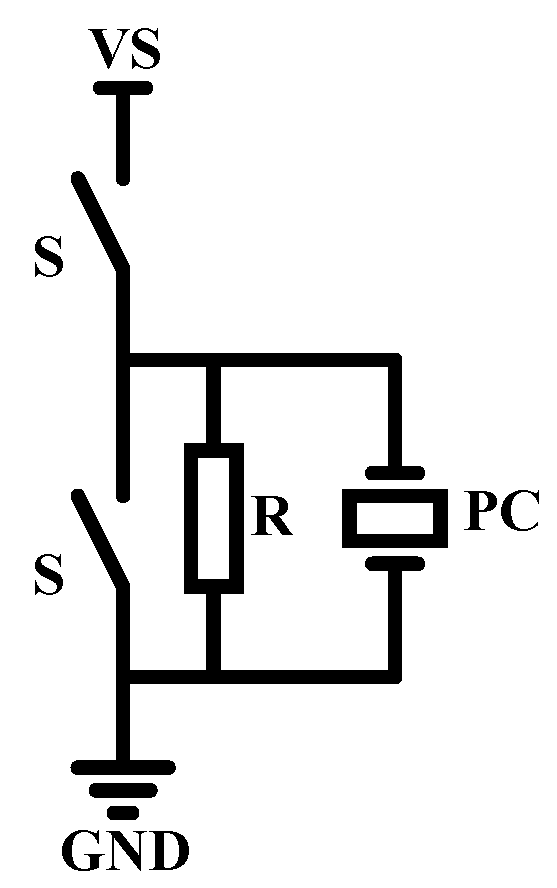

1.2.2. Selection of Topology

1.2.3. Control Method

- (1)

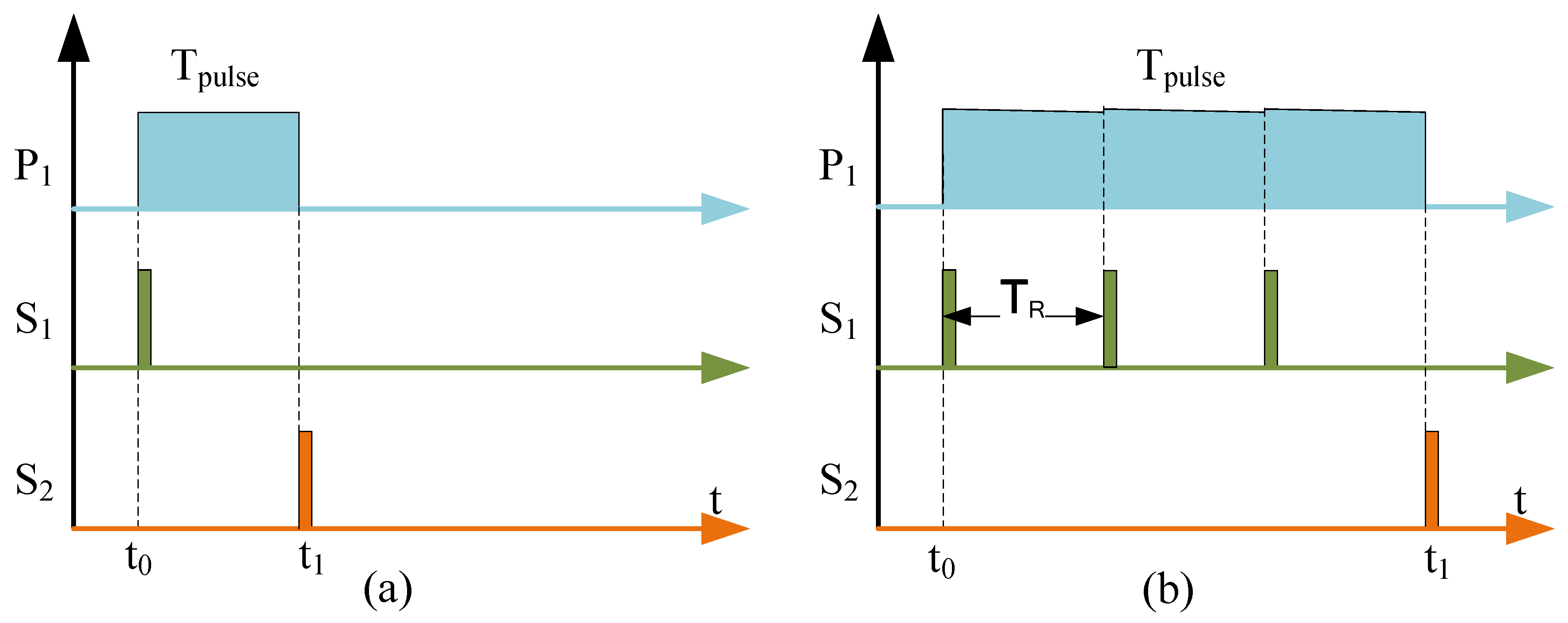

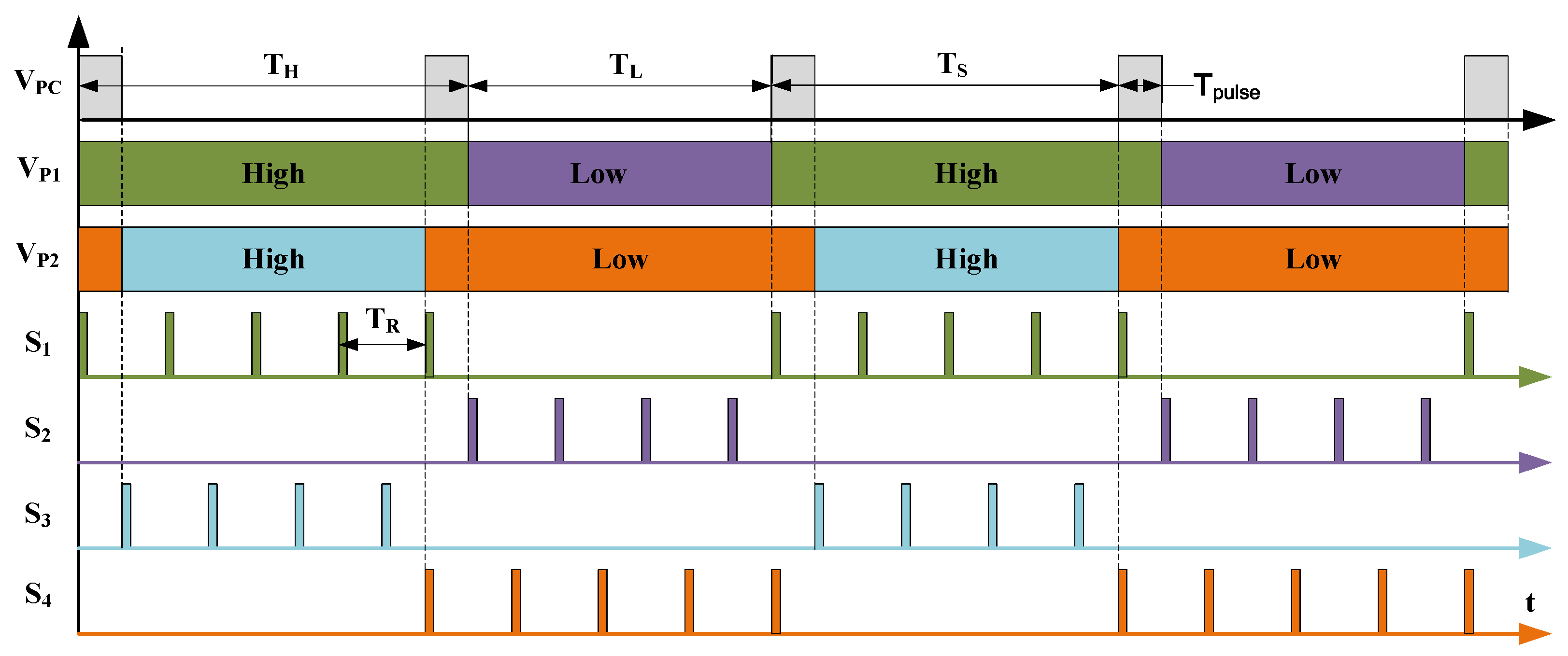

- The on-time lengths of and following the drive signals and are limited to prevent core saturation, which is due to the volt-second product of the gate drive transformers, and this time length is normally on the order of microseconds. When generates a high voltage with switched on, it gradually decreases due to the leakage current, which limits the maximum width that can be achieved. In this paper, we propose a recharging method to extend the pulse width. Although this method produces a certain amount of ripple, it can be reduced to a negligible degree by increasing the repetition rate, as shown in Figure 6b.

- (2)

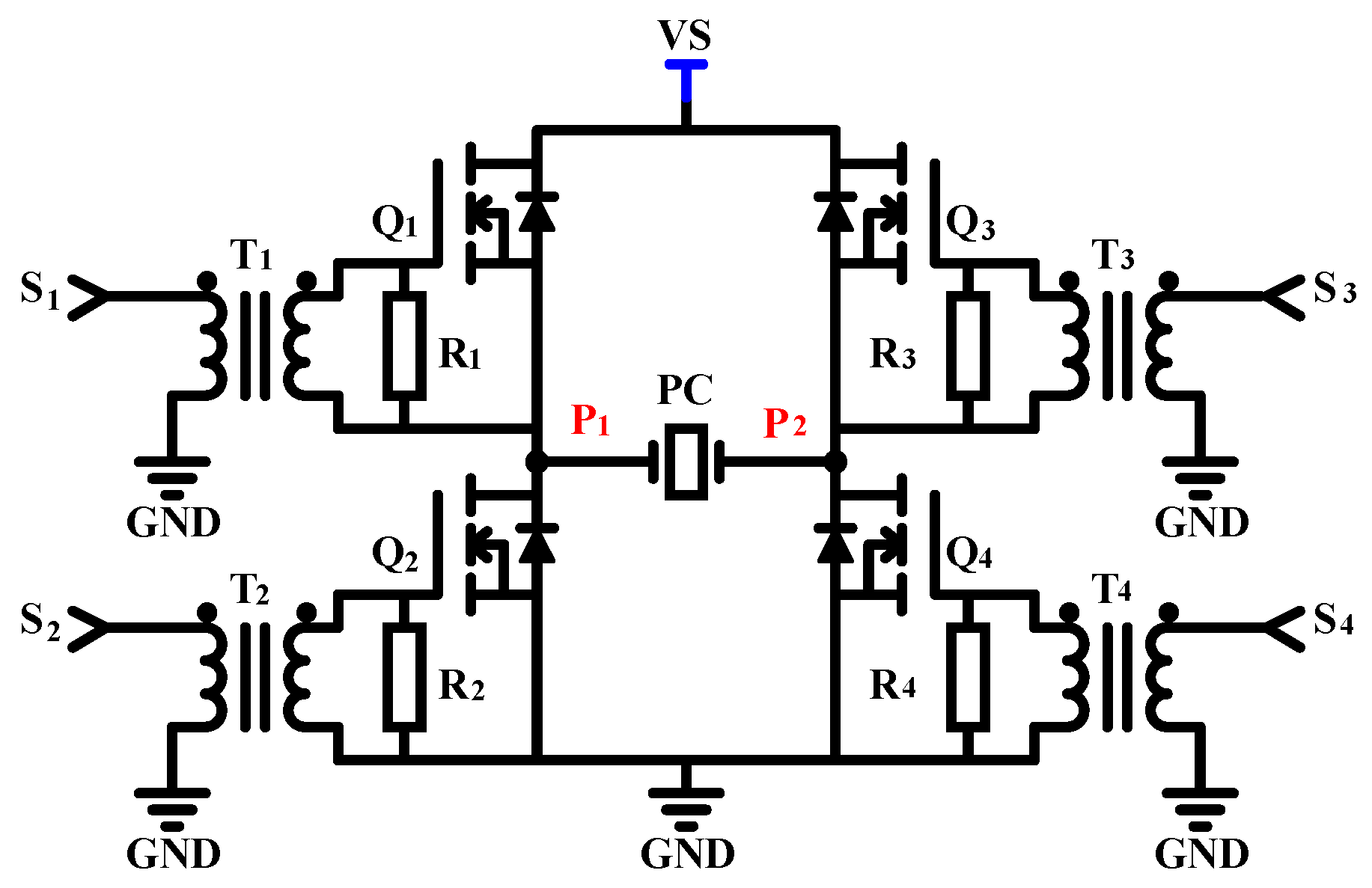

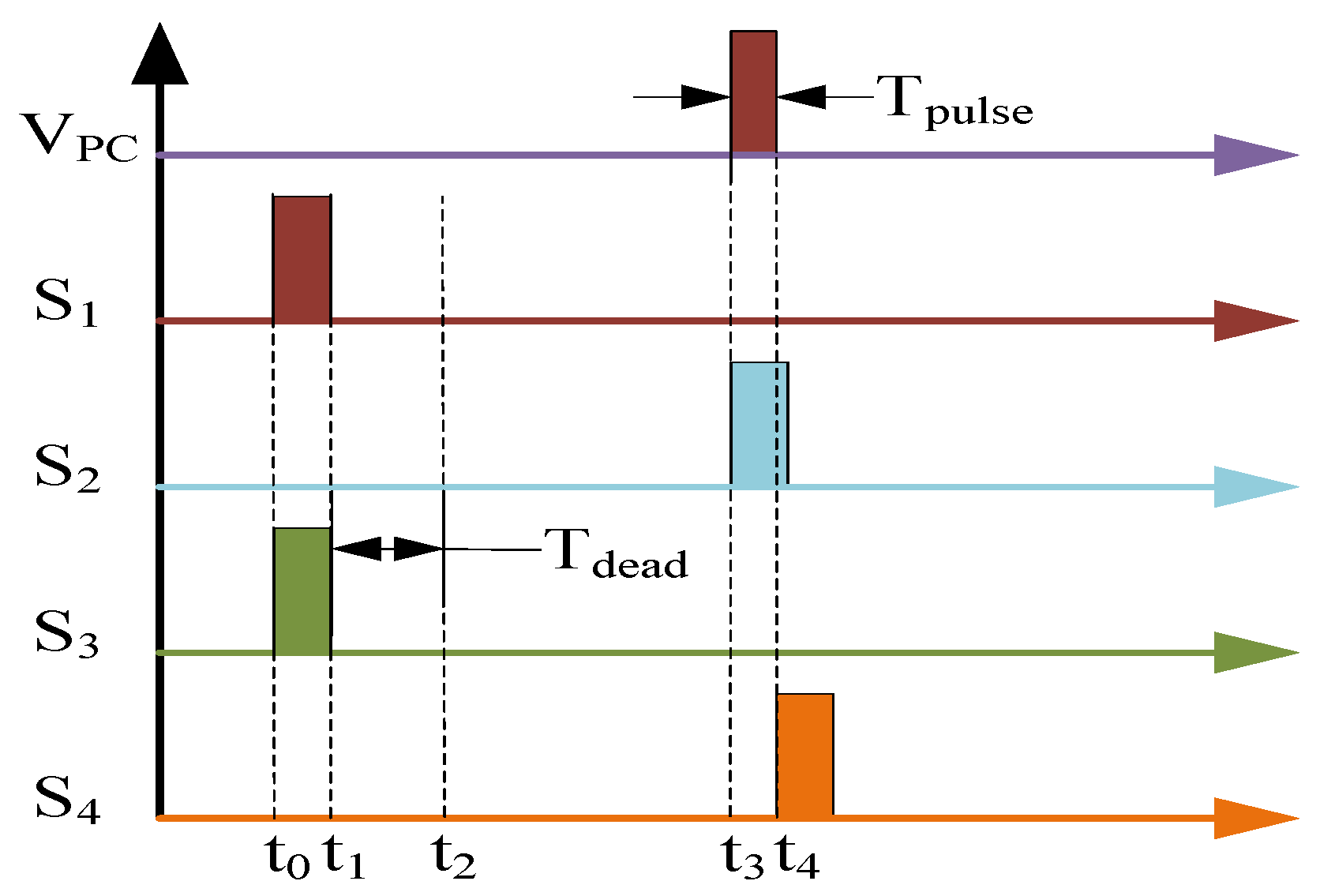

- In addition, a dead time must be introduced to prevent the upper and lower bridge arms from conducting simultaneously, as shown in Figure 7. For fast MOSFET switching, it is safe to set a dead time interval of at least a few tens of nanoseconds, in which case the minimum width that can achieve is represented by Equation (1).

1.3. Introduction of the Proposed PCD with a PWM Signal-Generation Strategy

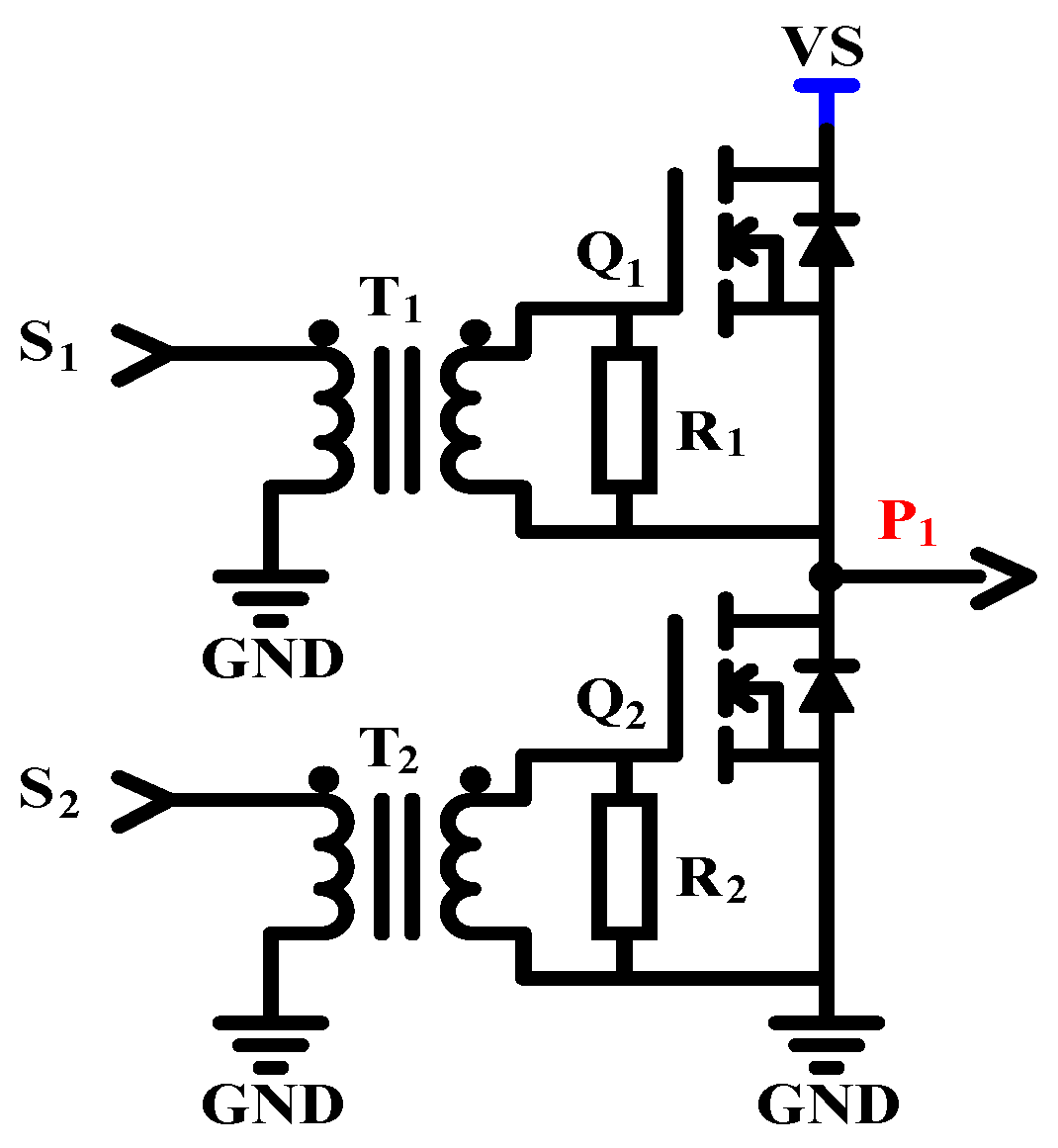

1.3.1. Generation of High-Voltage PWM Signals with Full-Bridge Topology

1.3.2. Applying PWM Timing Control Strategy to the PCD

- (1)

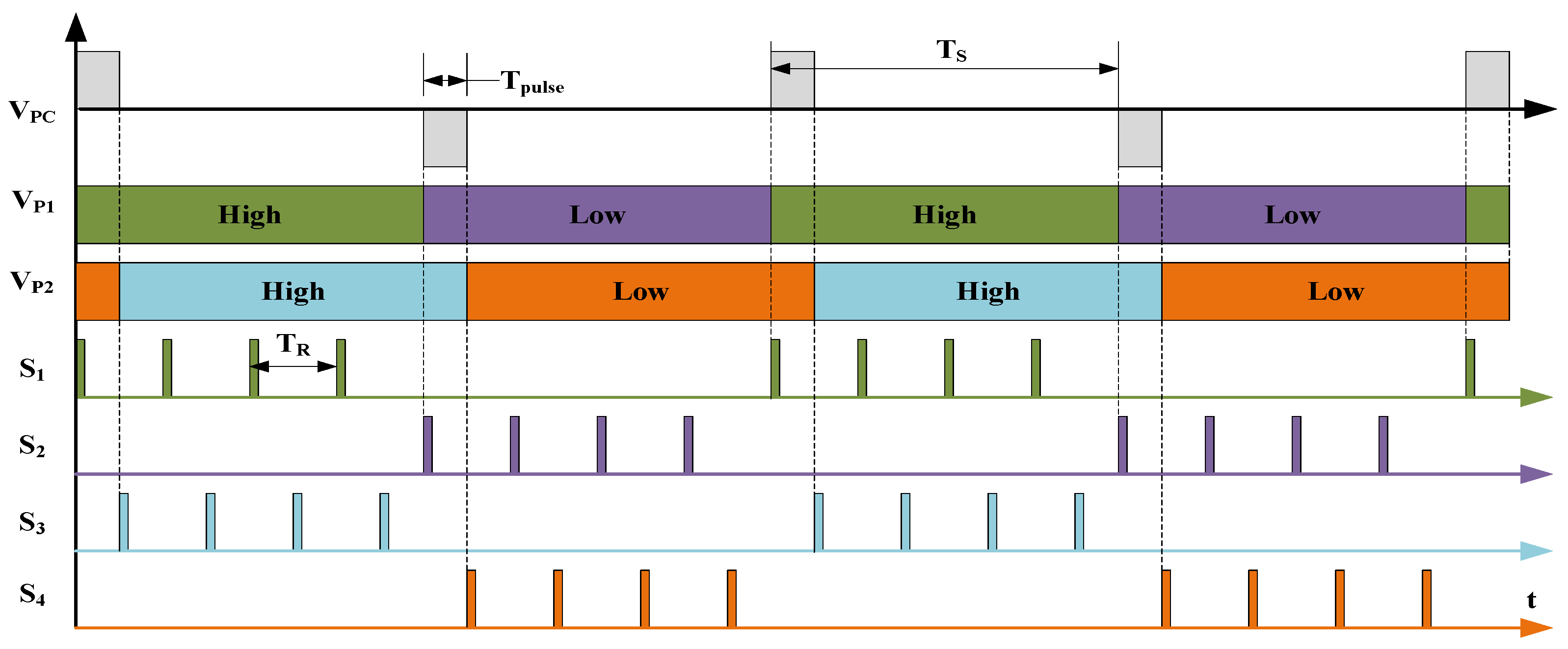

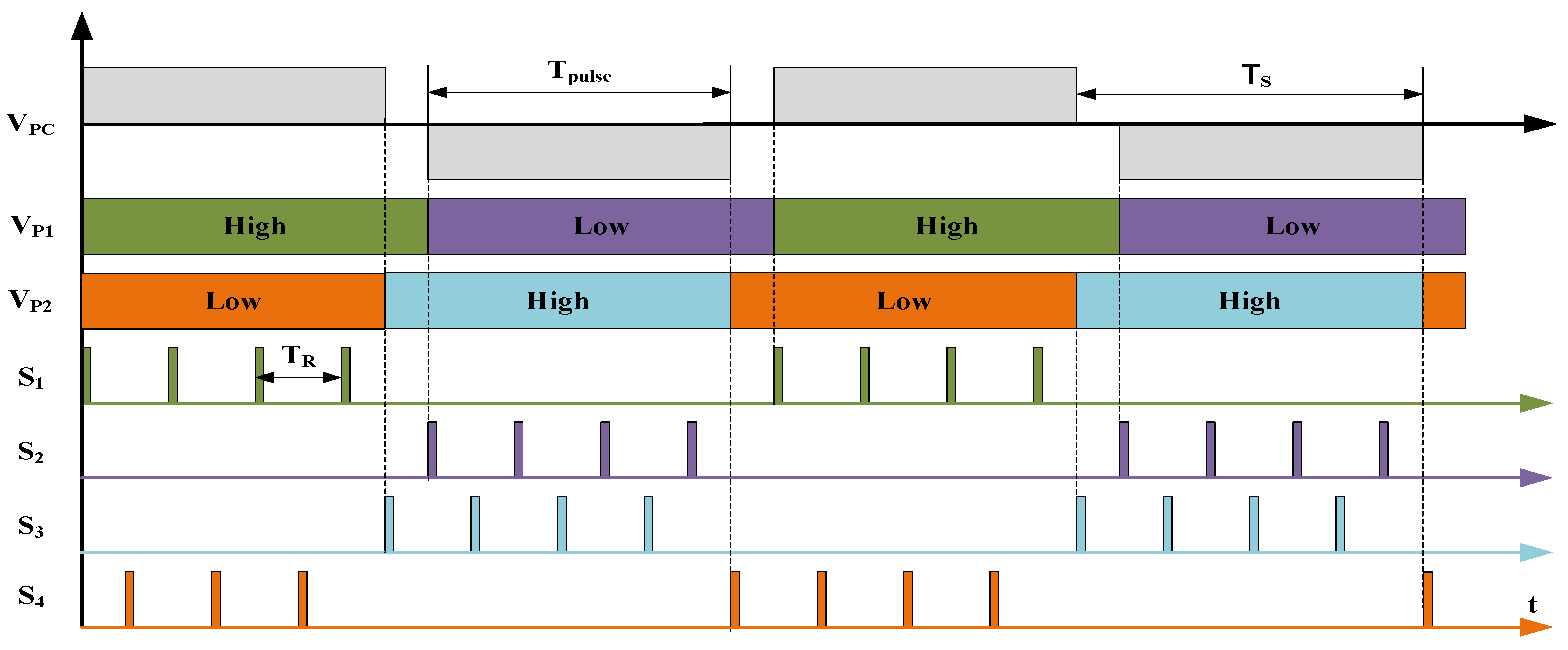

- Generating symmetric positive and negative PWM signals.

- (2)

- Generating unipolar positive PWM signals.

1.3.3. Features of the Proposed PCD

- (1)

- High reliability: the proposed circuit uses a bipolar voltage source instead of a unipolar one, which reduces the maximum voltage by half. This can effectively lessen the stress on the insulation and reduce the chances of arcing over to ground, which could otherwise negatively affect the reliability of the system. Moreover, the circuit employs a reasonable timing control method to ensure that the on-off intervals of the upper and lower MOSFETs are longer than the dead time. The dead time is the time interval between turning off one MOSFET and turning on another MOSFET in the same arm of the bridge. If the dead time is too short or even negative, it may cause a short circuit across the DC bus and damage the devices. Therefore, by avoiding this risk, the proposed circuit enhances the reliability of the system.

- (2)

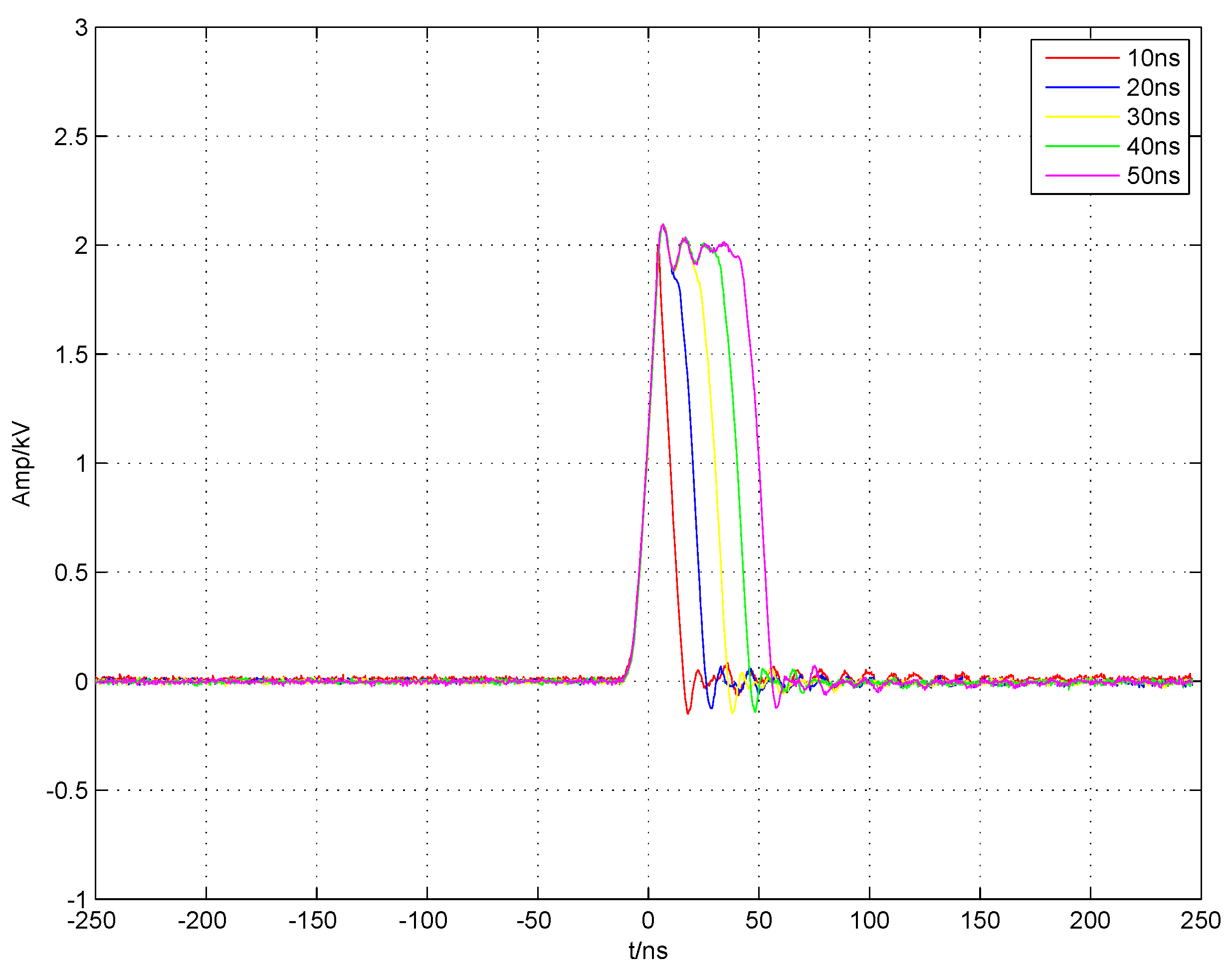

- Short pulse width: the proposed circuit adopts a novel timing control method that eliminates the effect of dead time on the pulse width. In conventional PCDs, the dead time limits the minimum pulse width that can be generated by the full-bridge circuit. However, in the proposed circuit, the dead time is compensated by adjusting the phase shift between the upper and lower MOSFETs in each arm of the bridge. As a result, the proposed circuit can generate extremely short pulses with a minimum pulse width of only 10 ns.

- (3)

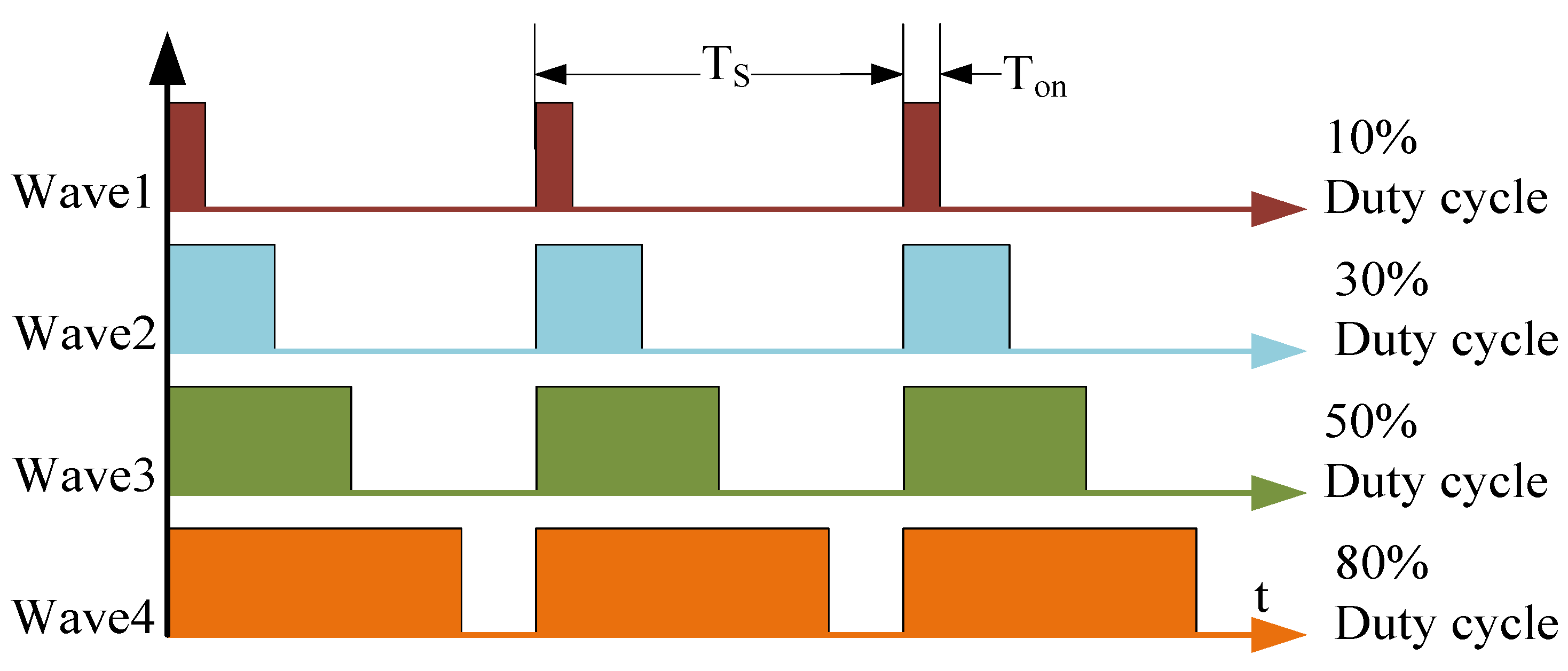

- Adjustable pulse width: the proposed PWM signal generation strategy is based on the precise phase shift of the two square waves with the same frequency generated by the two pairs of bridge arms of the full-bridge circuit to control. By adjusting the phase difference between these two waves, the proposed strategy can generate PWM signals with continuously adjustable duty cycles. The duty cycle is defined as the ratio of pulse width to pulse period. Theoretically, the duty cycle can be adjusted from 0% to 100%. This means that the proposed strategy can generate pulses with various widths to meet different application requirements.

- (4)

- High switching speed: the proposed circuit uses transformer-coupled circuits to drive the gate terminals of the MOSFETs. This can reduce the delay time and improve the synchronization between different MOSFETs. In addition, the proposed circuit uses silicon carbide (SiC) MOSFETs as switching components instead of conventional silicon (Si) MOSFETs. SiC MOSFETs have several advantages over Si MOSFETs, such as higher breakdown voltage, lower on-state resistance, faster rising/falling times, and higher switching repetition rates. These advantages enable SiC MOSFETs to achieve higher switching speed and efficiency than Si MOSFETs.

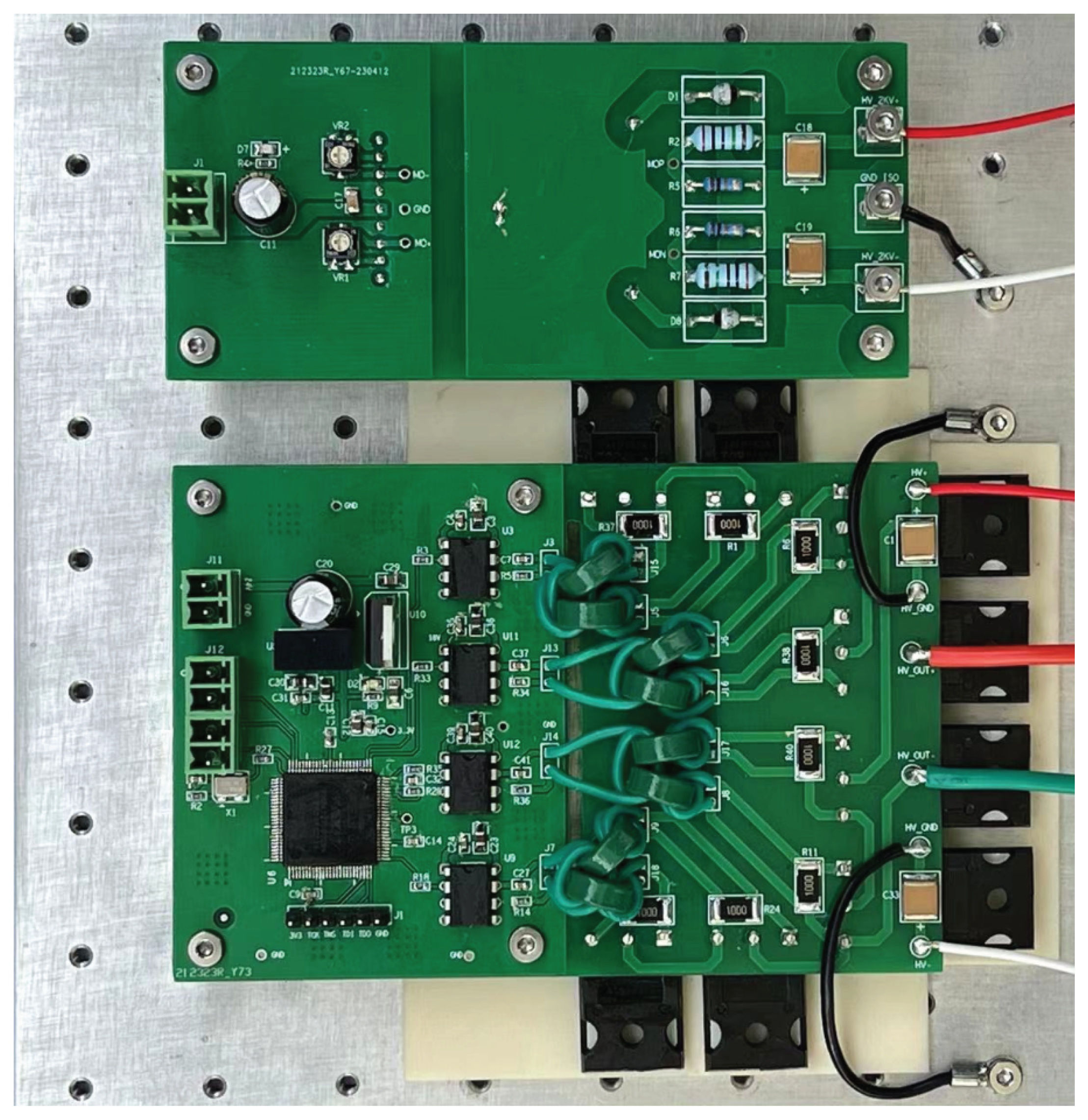

2. Design and Implementation

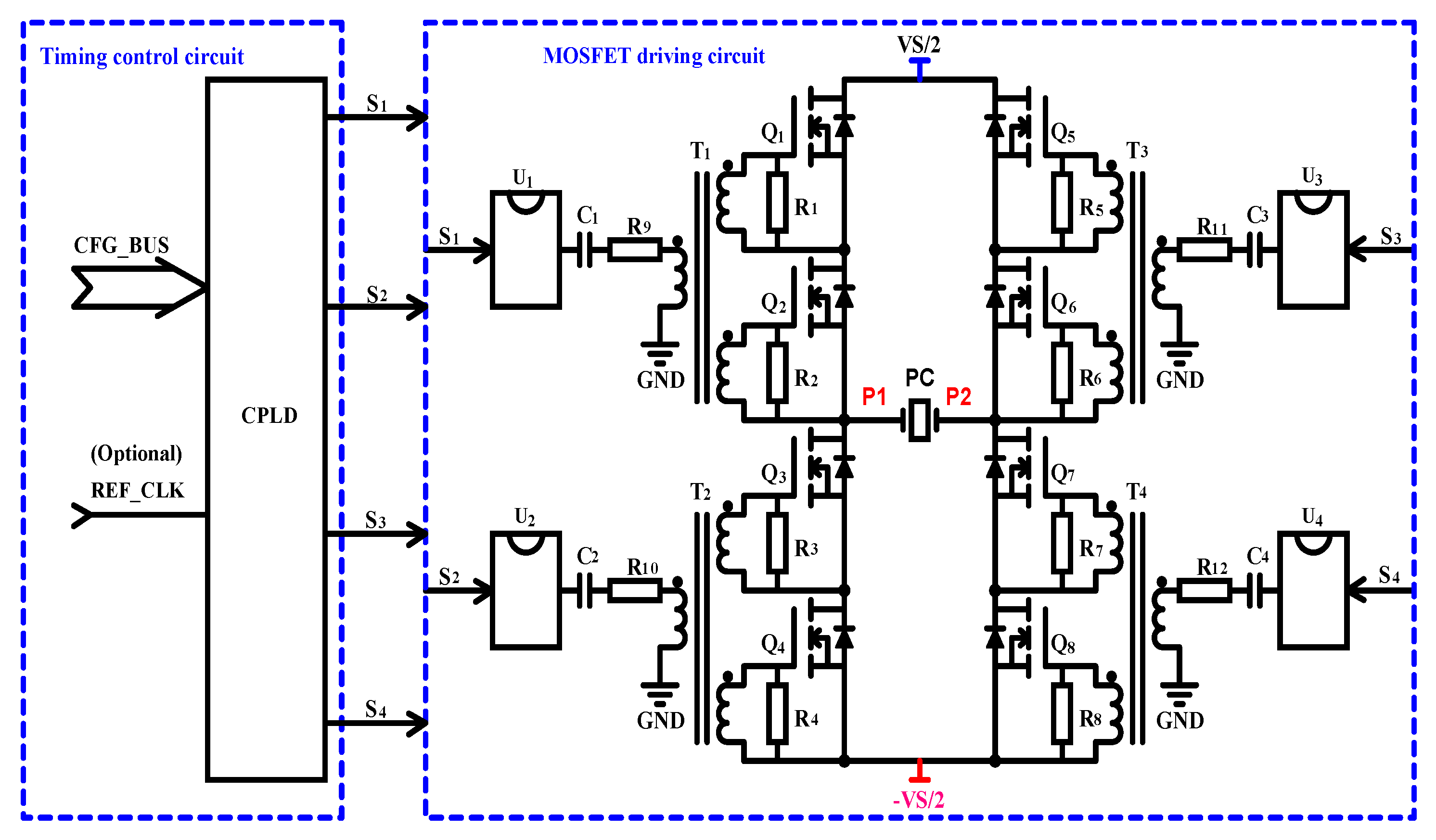

2.1. System Block Diagram and Topology

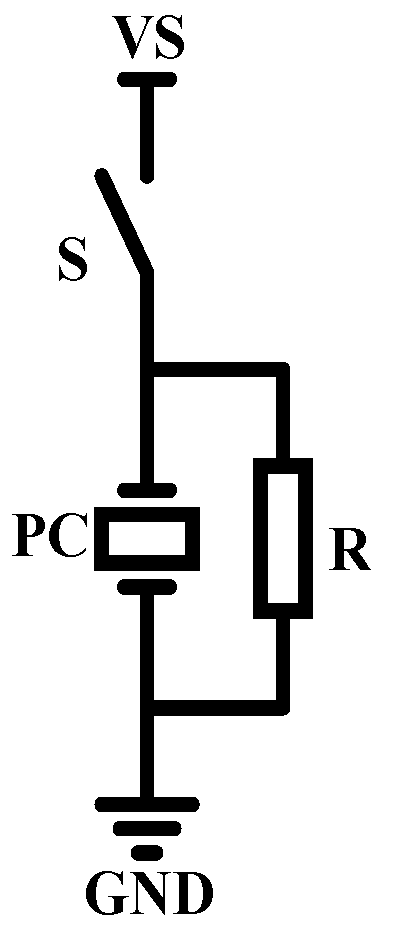

2.1.1. MOSFET Driving Circuit

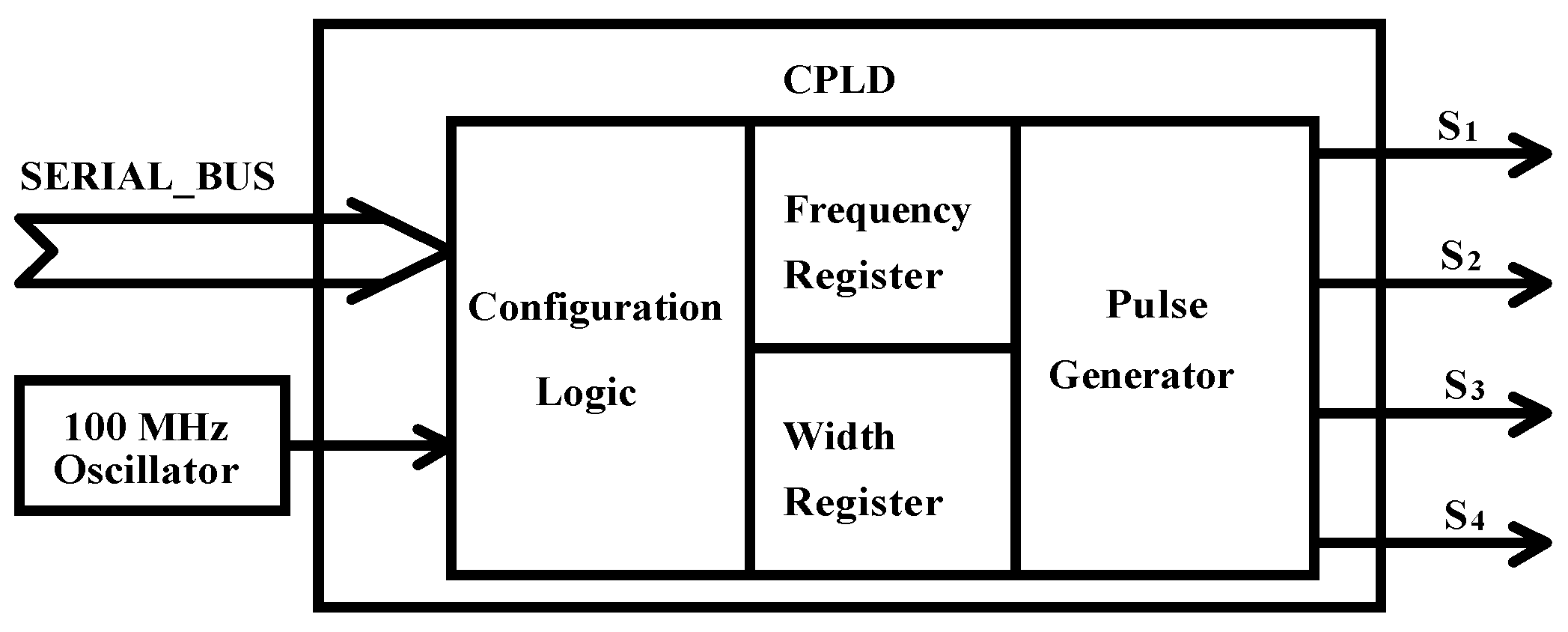

2.1.2. Timing Control Circuit

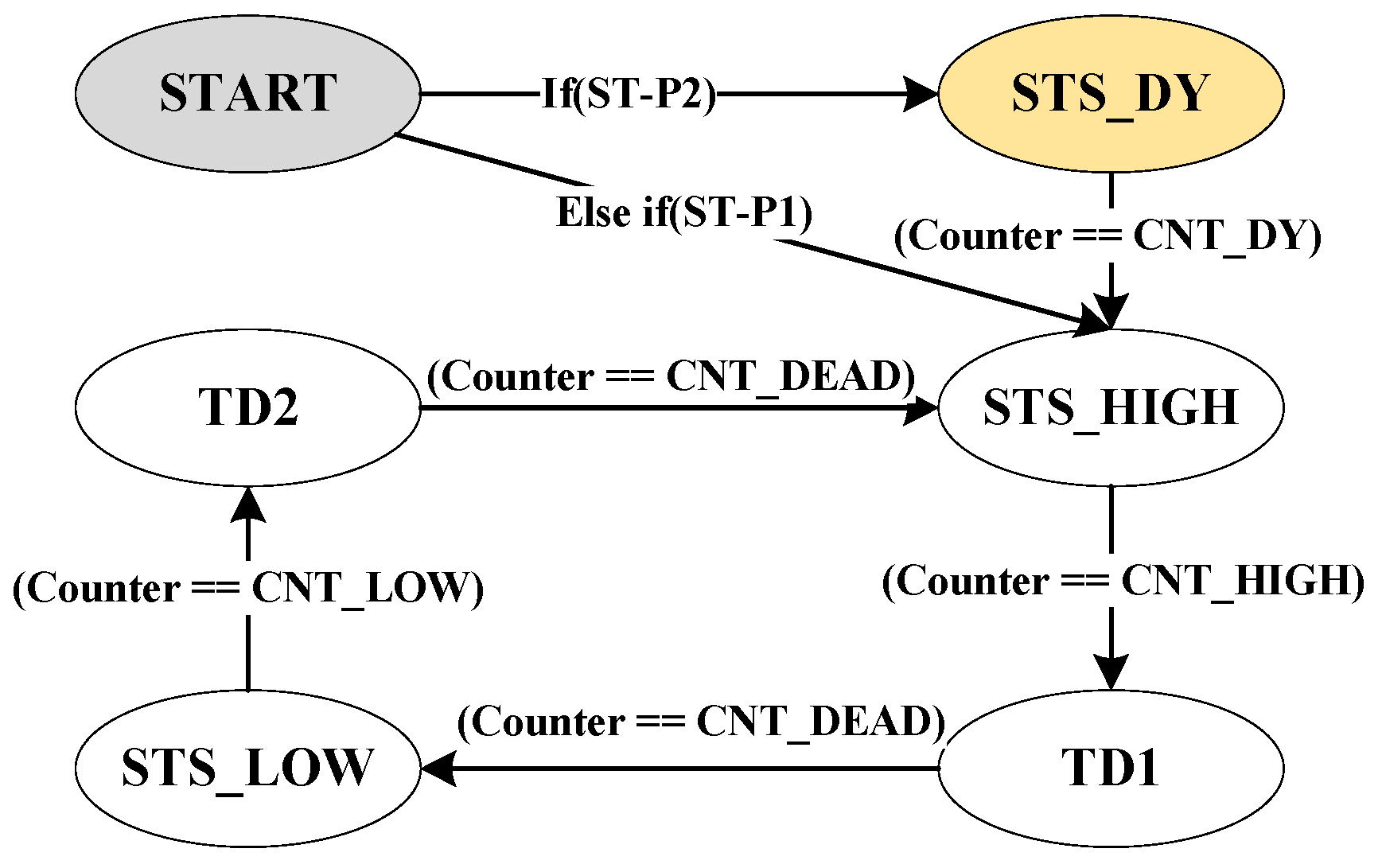

2.2. PWM Timing Control Method

- Duration of STS_DY: CNT_DY = ;

- Duration of STS_HIGH: CNT_HIGH = ;

- Duration of STS_LOW: CNT_LOW = ;

- Dead time is : CNT_DEAD = = 50 ns;

- High-level duration of and : = ;

- Low-level duration of and : = .

2.3. Selection of Switches and Discrete Components

2.4. Transformer-Coupled Gate Drive Circuits

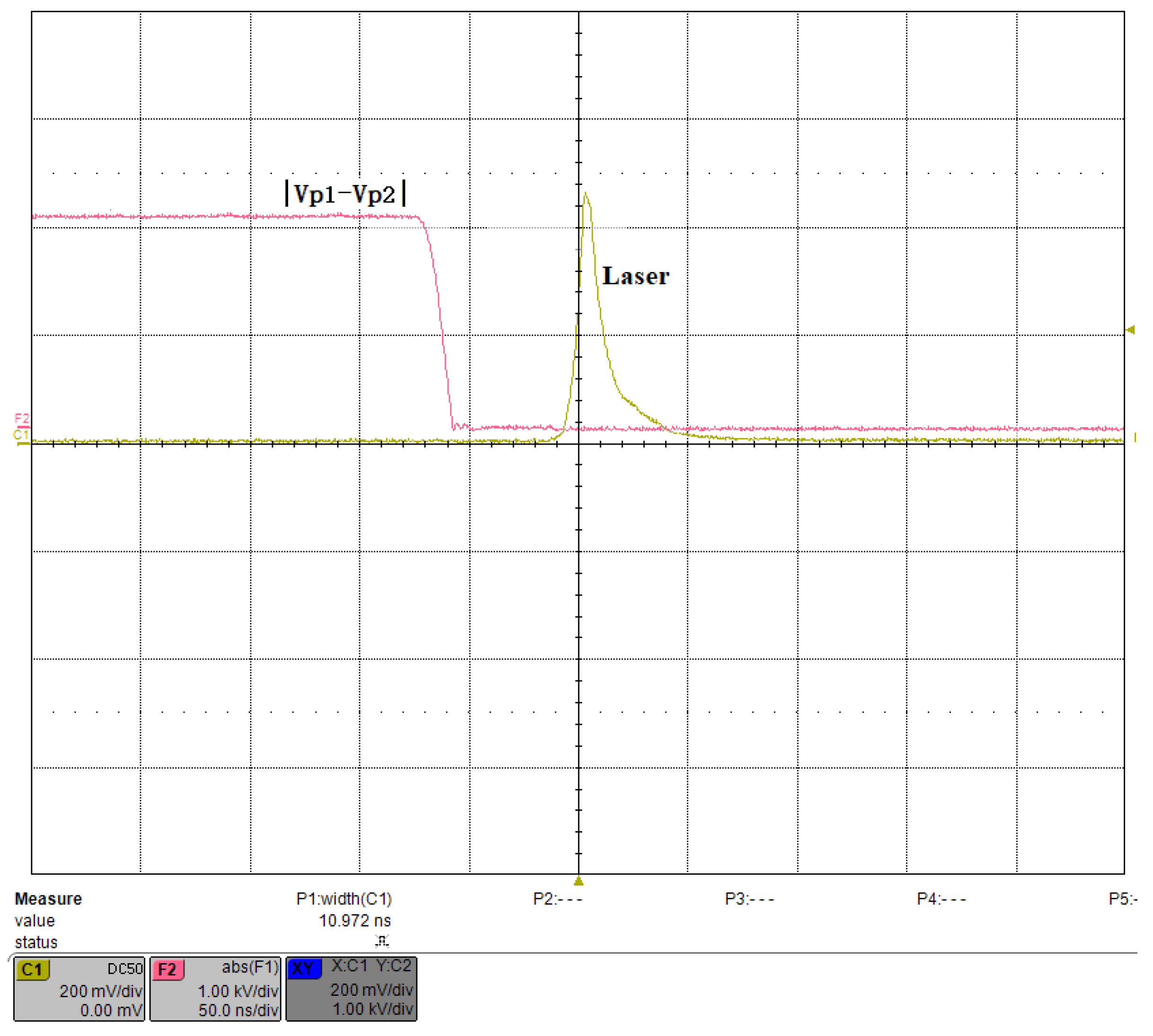

3. Experiment Results

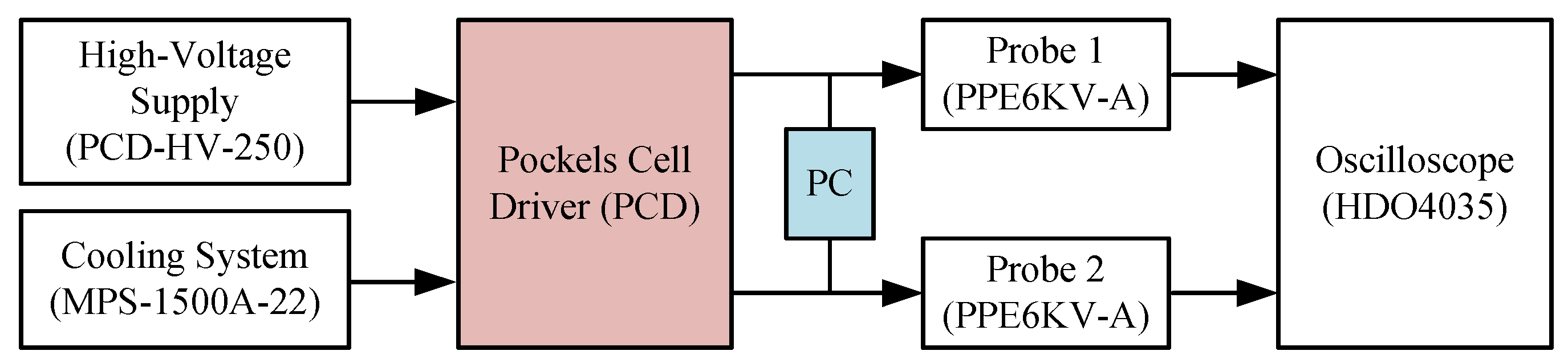

3.1. Experiment Setups

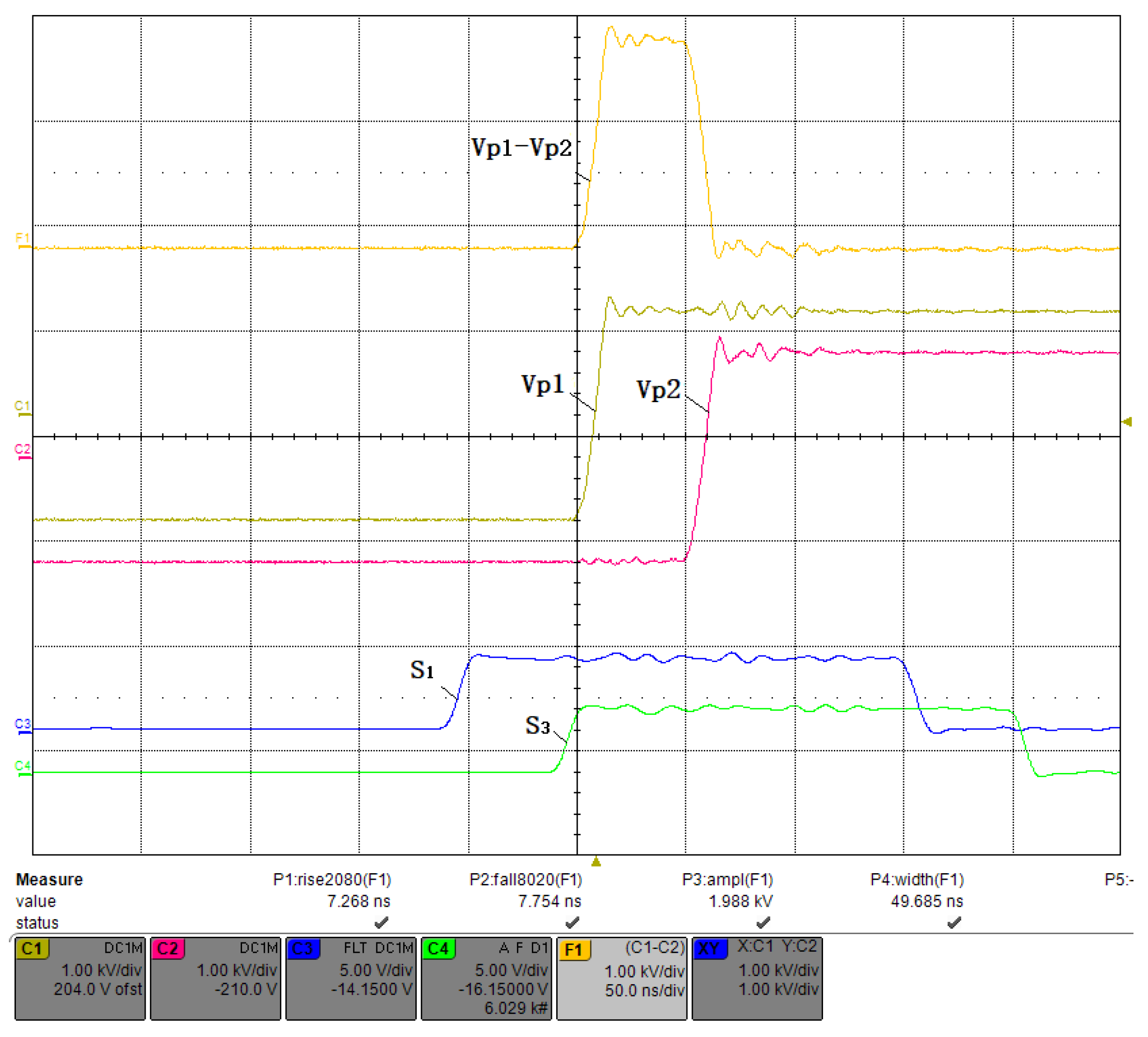

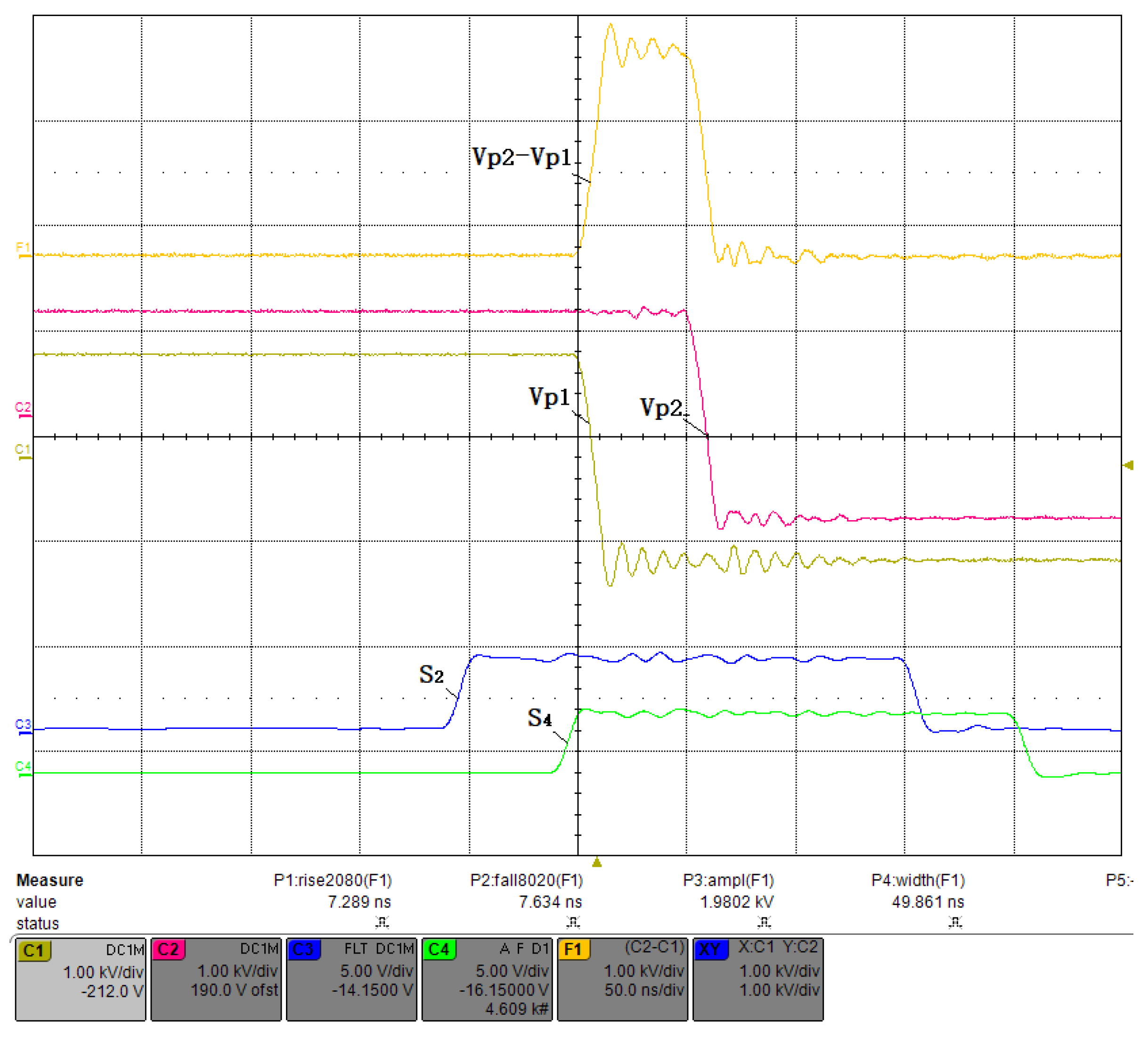

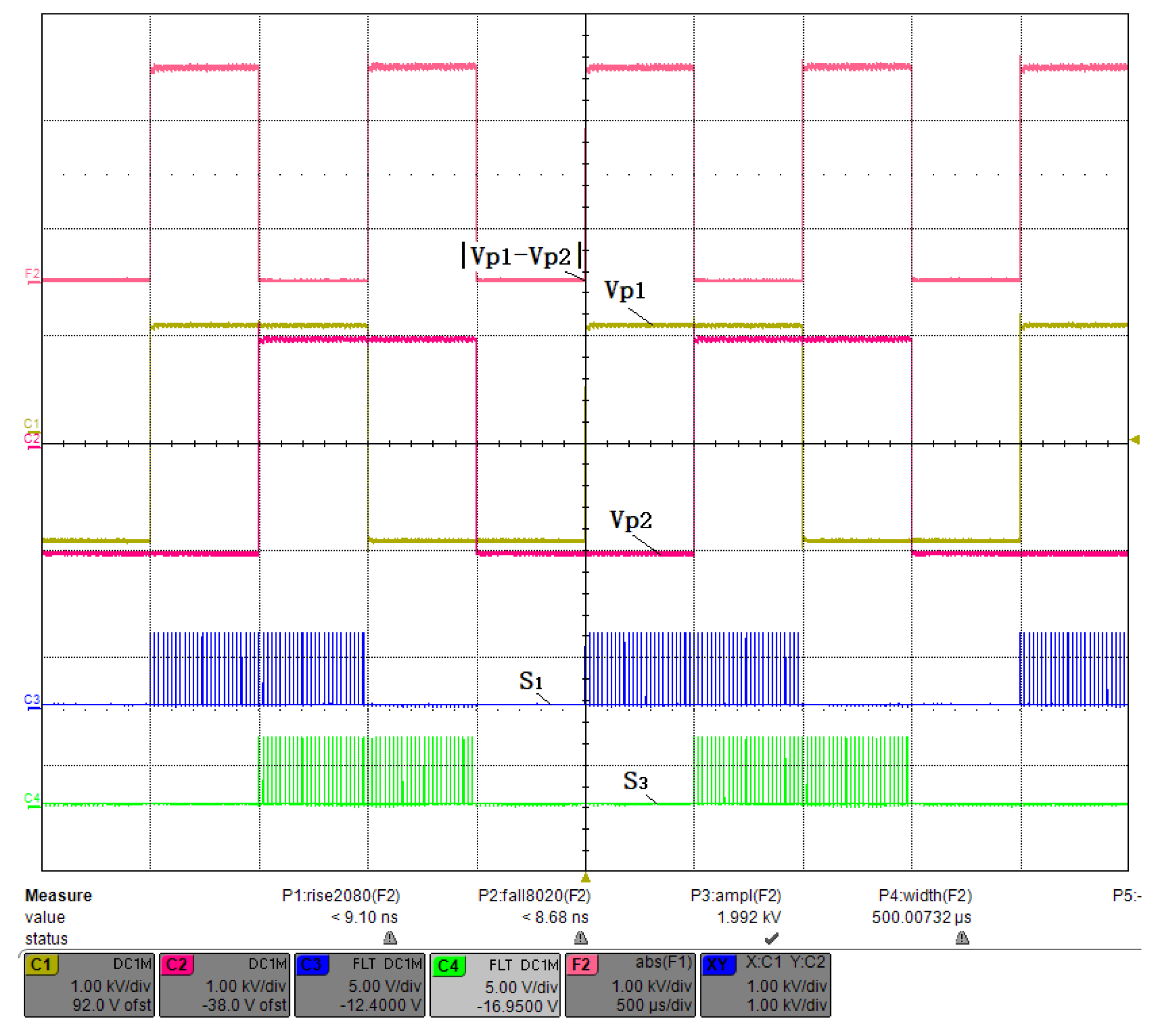

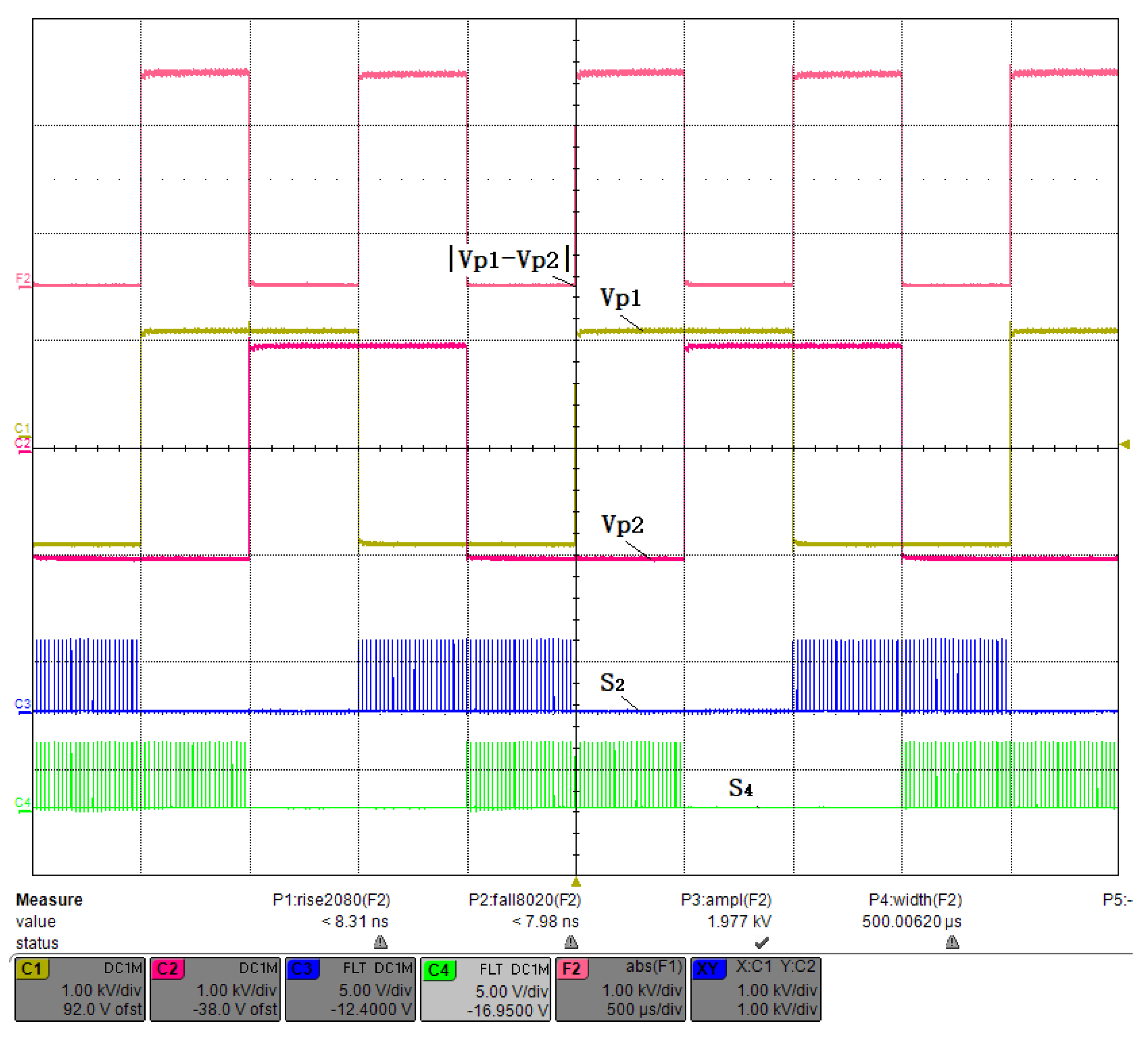

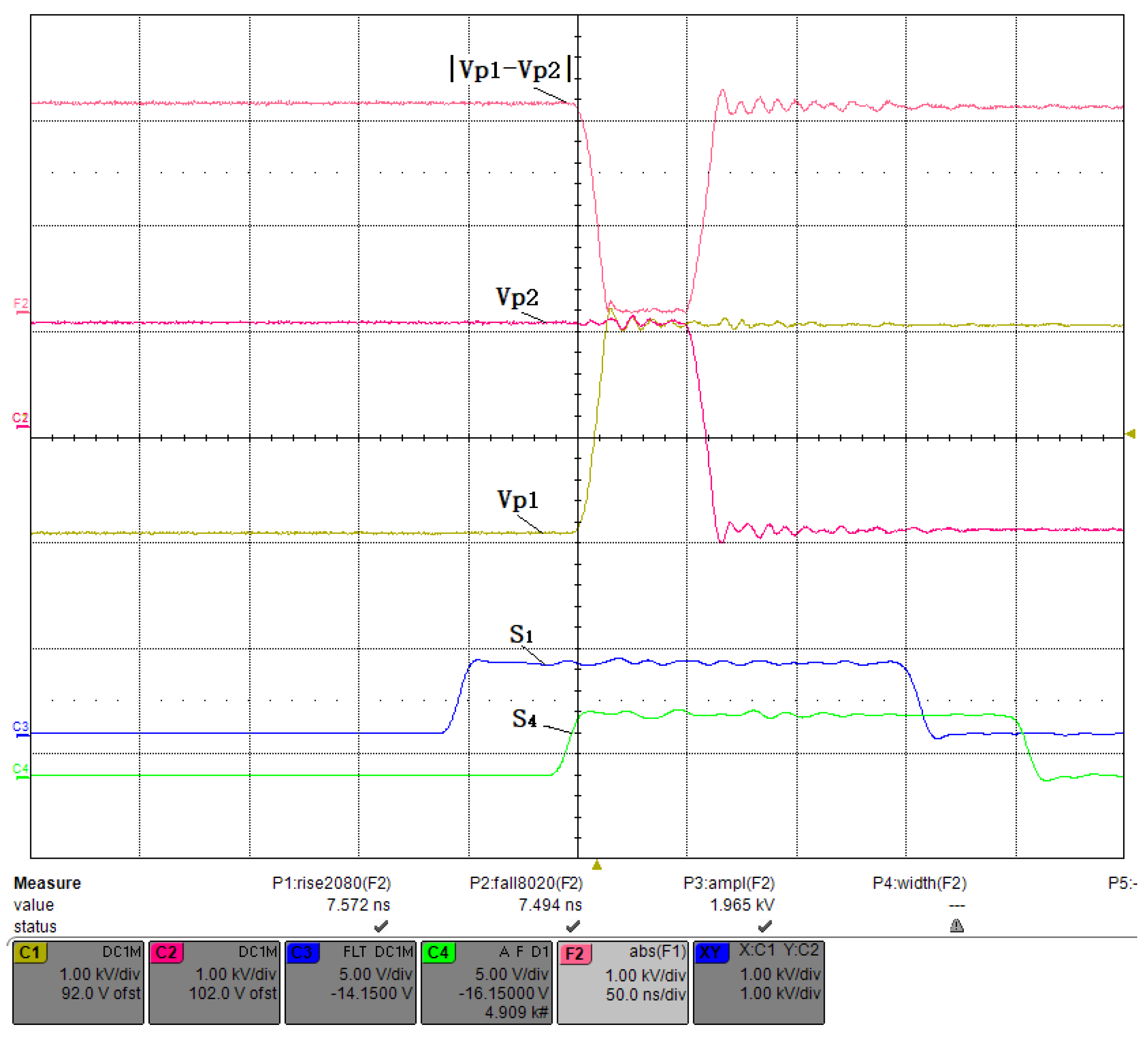

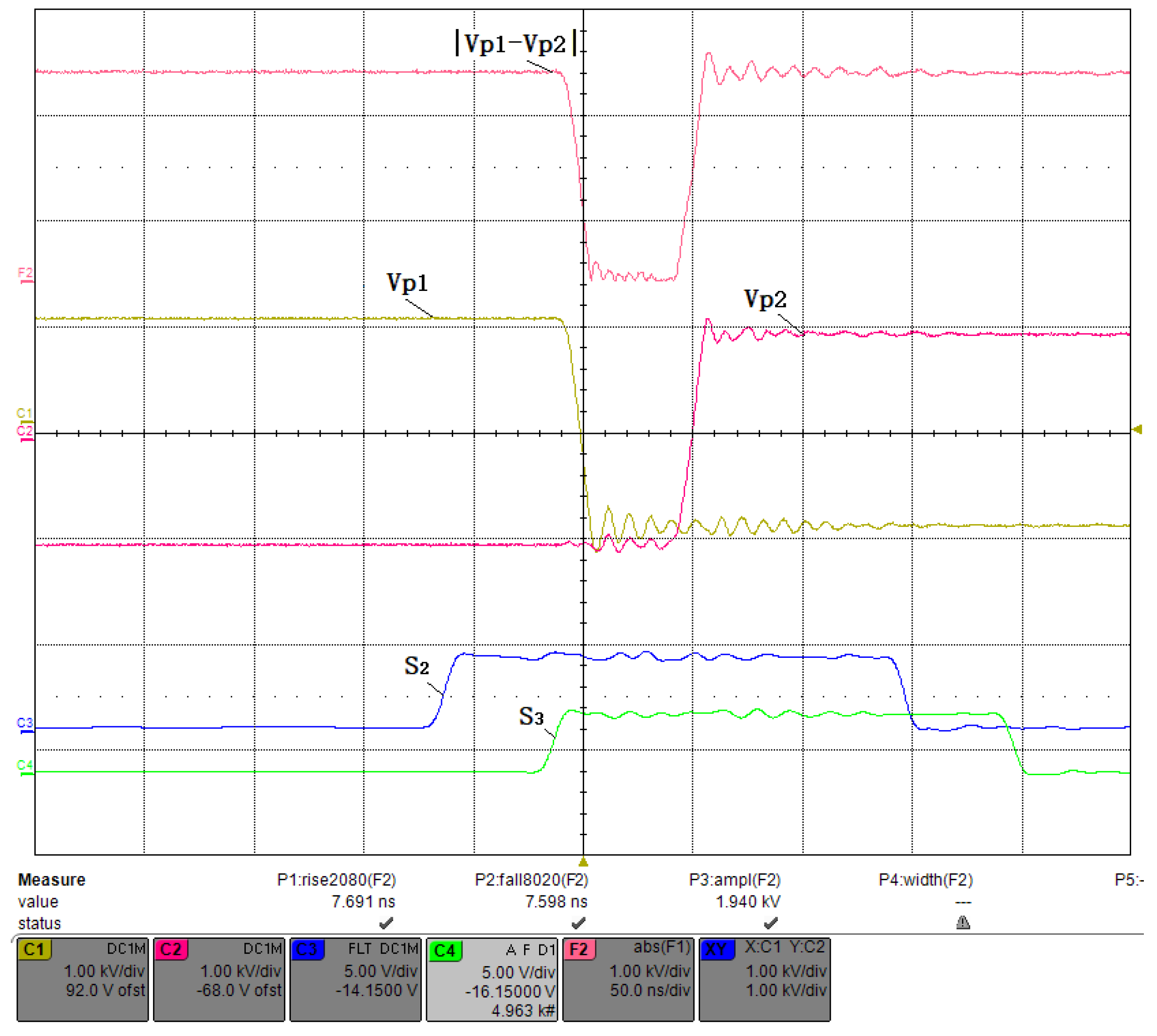

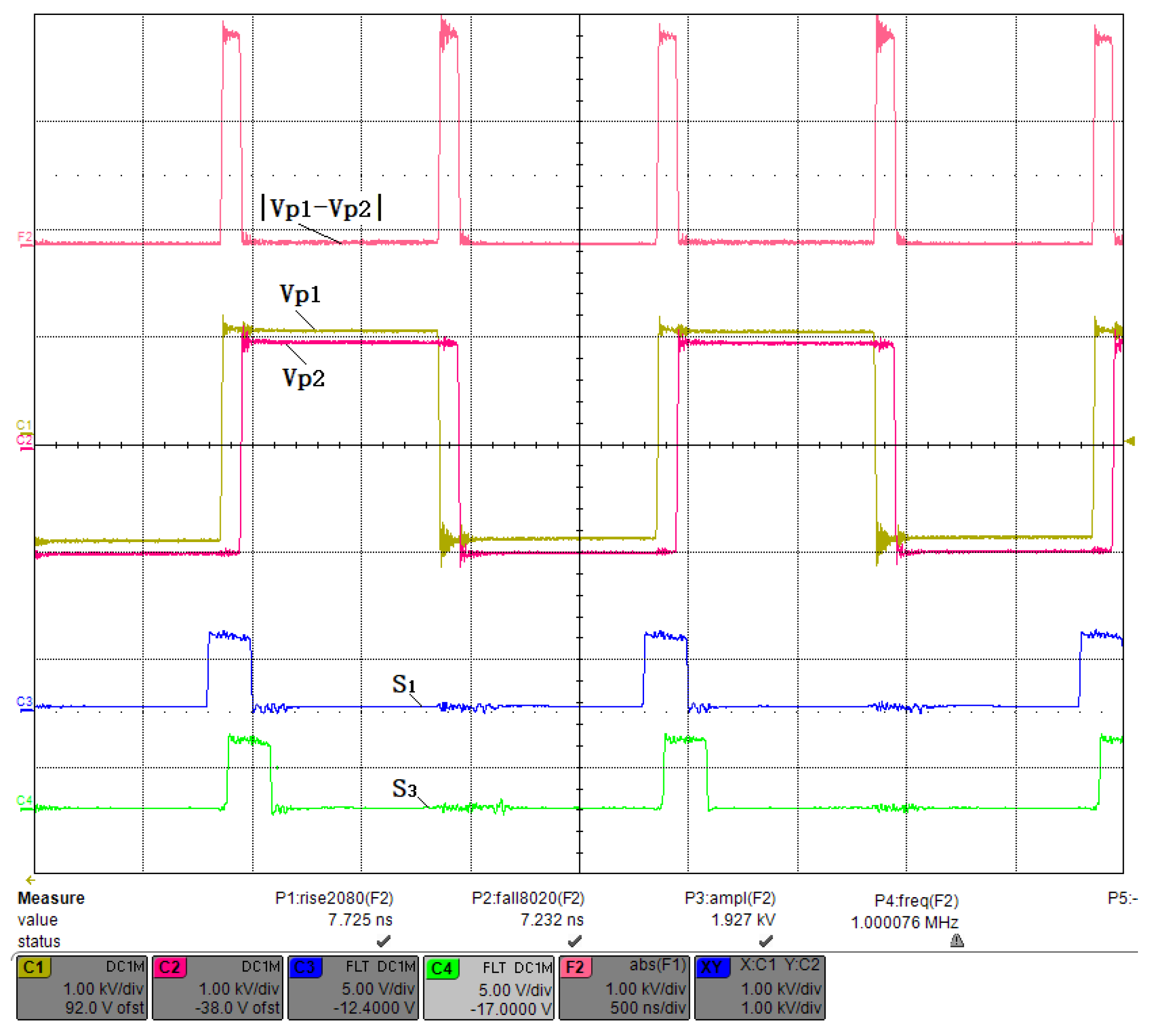

3.2. Small Duty Cycle Test

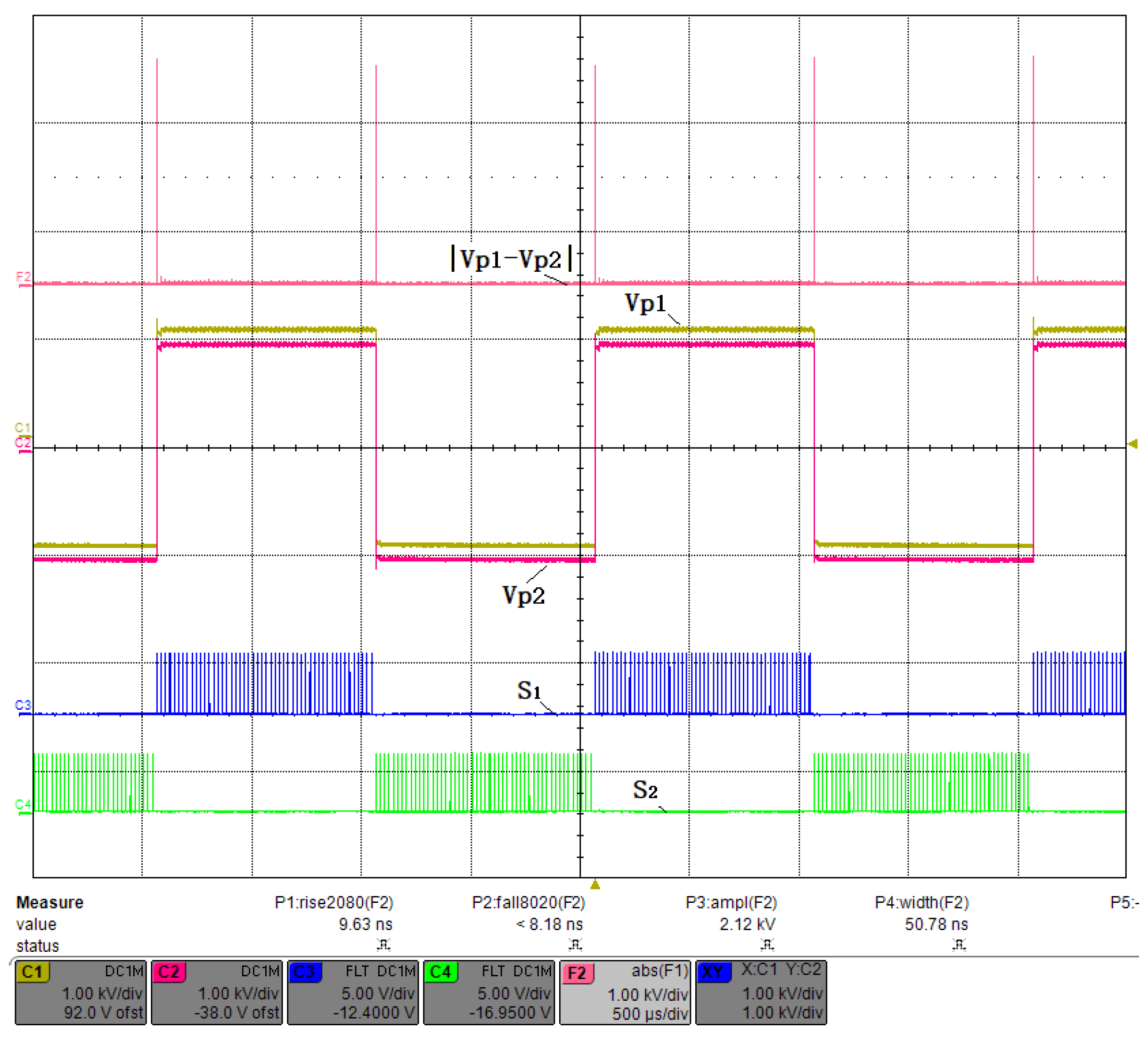

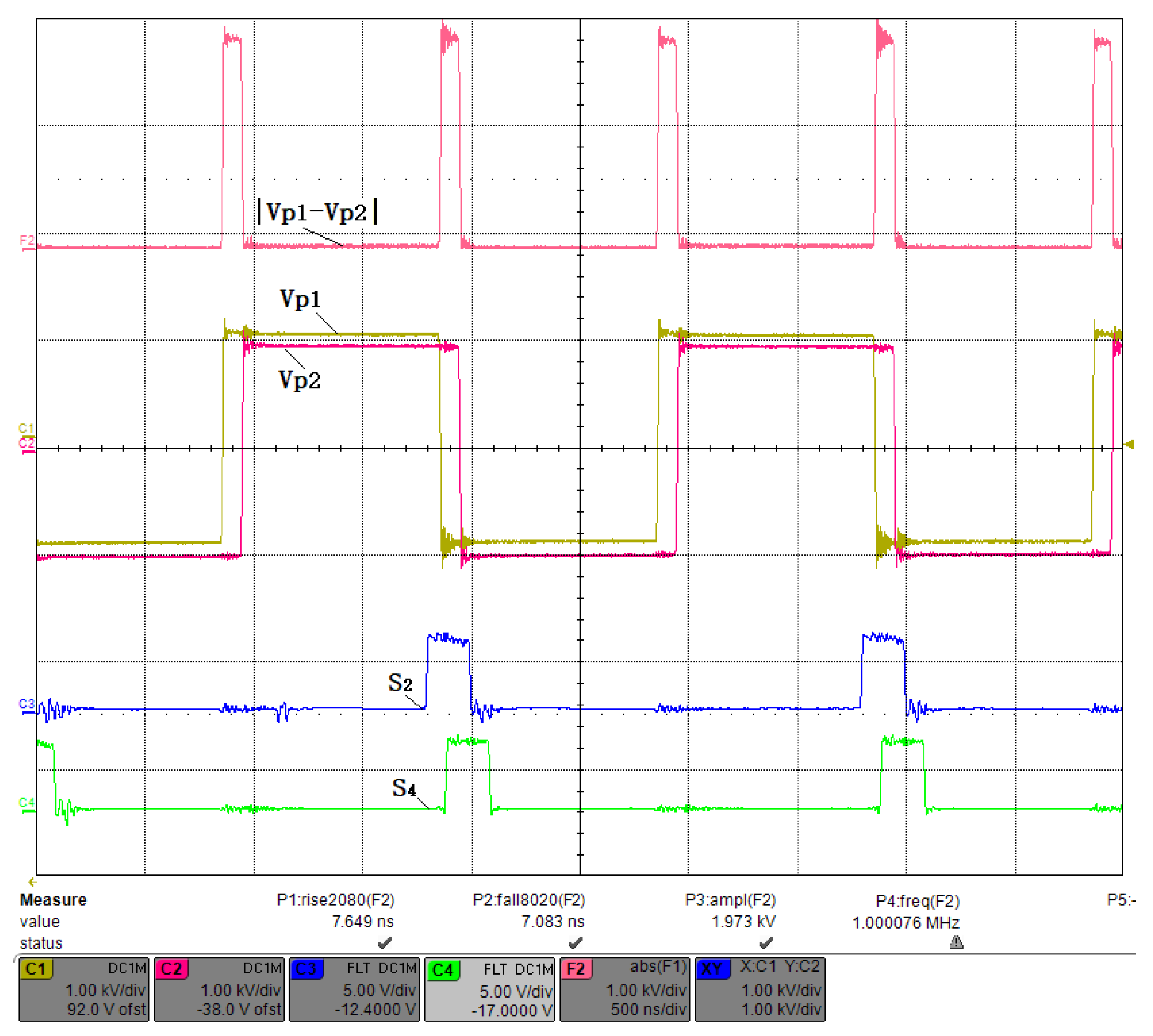

3.3. Fifty Percent Duty Cycle Test

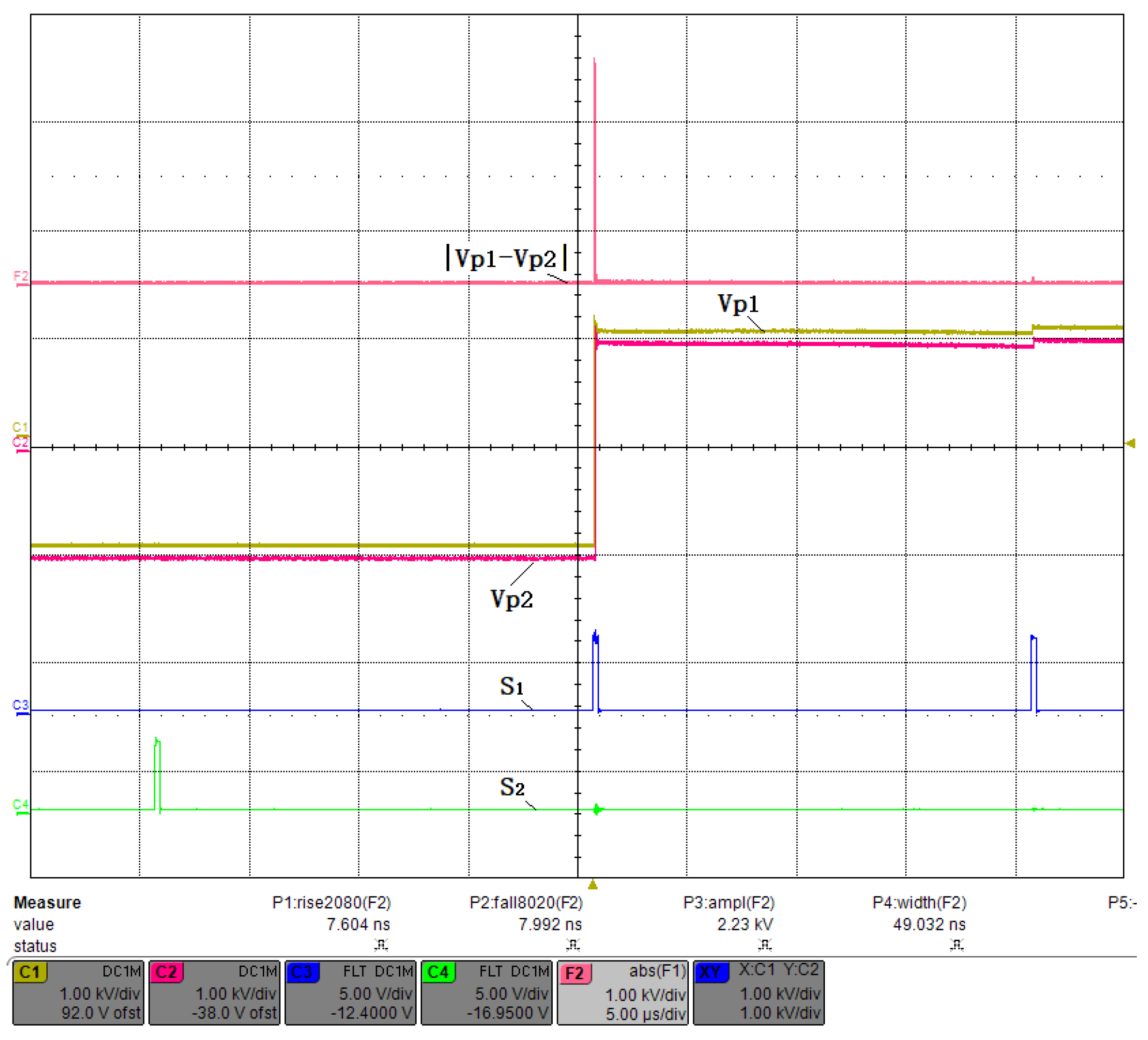

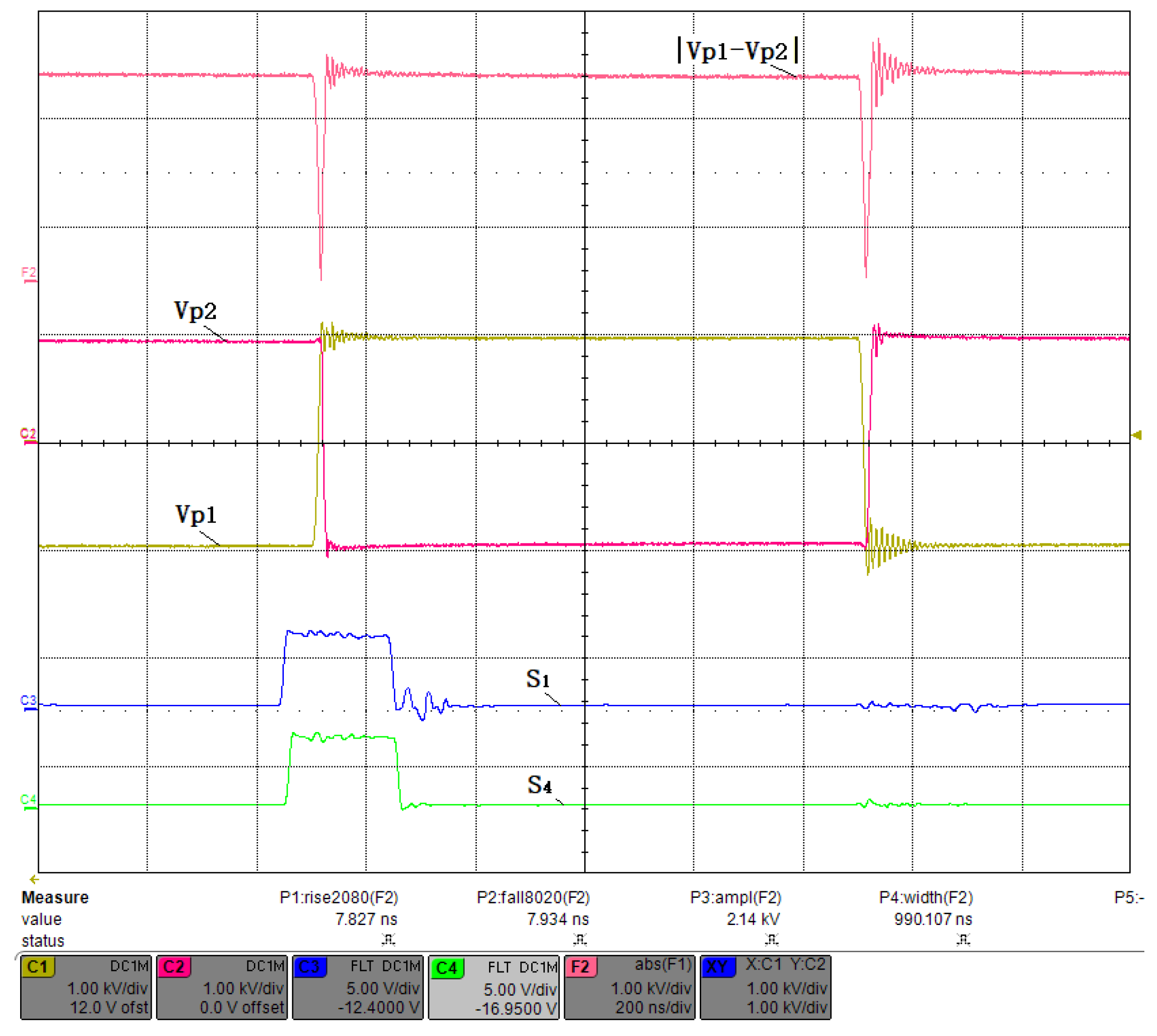

3.4. Large Duty Cycle Test

3.5. High-Repetition-Rate Test

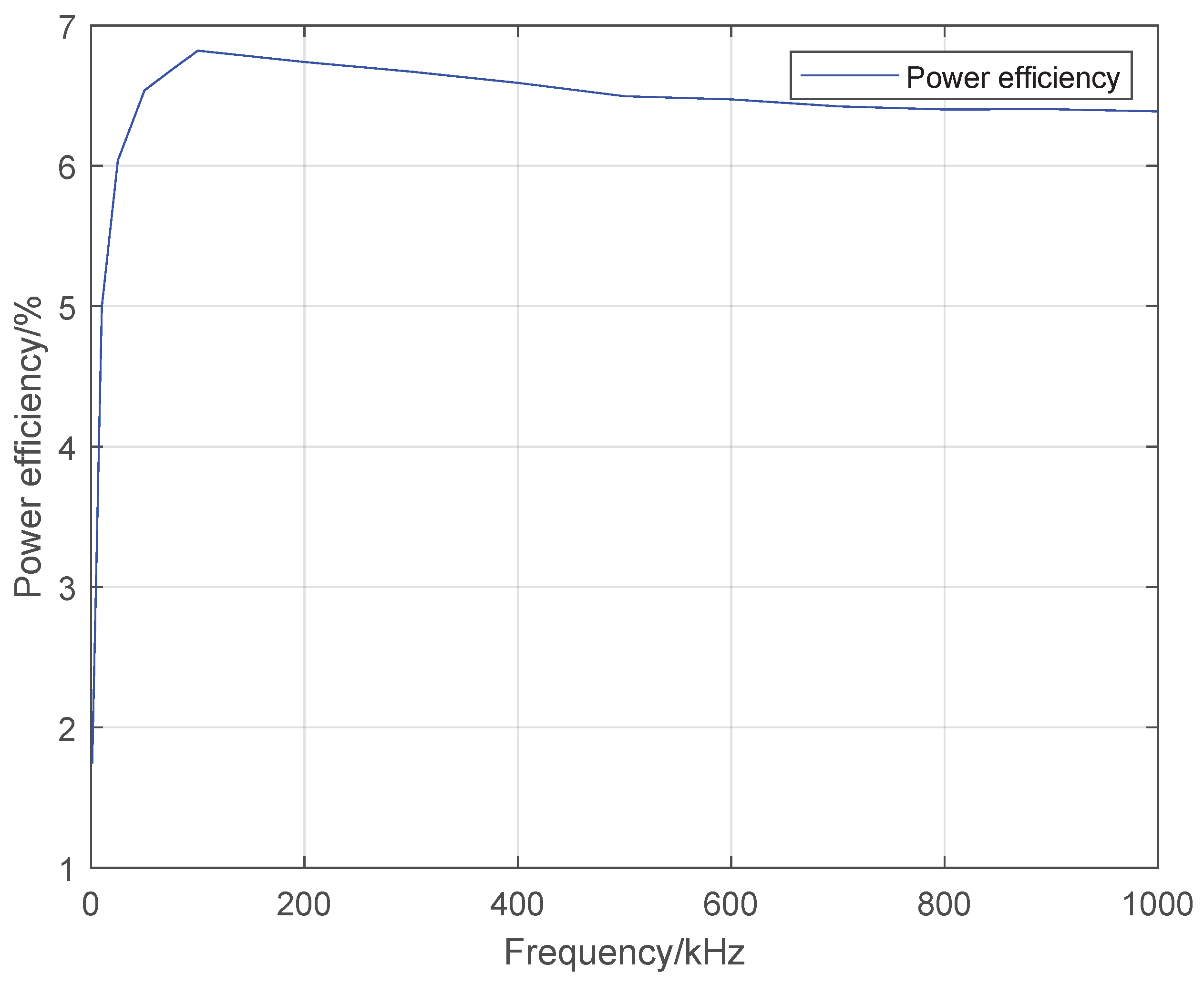

3.6. Power Loss Test

3.7. PCD Test in a Slab Laser

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Shimony, Y.; Burshtein, Z. Repetitive Q-switching of a CW Nd:YAG laser using Cr/sup 4+/:YAG saturable absorbers. IEEE J. Quantum Electron. 1996, 32, 305–310. [Google Scholar] [CrossRef]

- Linne, M.; Baer, T. Q-Switching of Diode Pumped Solid State Lasers. In Proceedings of the 1988 Los Angeles Symposium–O-E/LASE ’88, Los Angeles, CA, USA, 11–17 January 1988; pp. 110–114. [Google Scholar]

- Hnninger, C.; Paschotta, R.; Morier-Genoud, F.; Moser, M.; Keller, U. Q-switching stability limits of continuous-wave passive mode locking. J. Opt. Soc. Am. 1999, 16, 46–53. [Google Scholar] [CrossRef]

- Balzer, J.C.; Schlauch, T.; Hoffmann, T.; Klehr, A.; Erbert, G.; Hofmann, M.R. Modelocked semiconductor laser system with pulse picking for variable repetition rate. Electron. Lett. 2011, 47, 1387–1388. [Google Scholar] [CrossRef]

- Zhao, Z.; Mernick, K.; Costanzo, M.; Minty, M. An ultrafast laser pulse picker technique for high-average-current high-brightness photoinjectors. Nucl. Instrum. Methods Phys. Res. Sect. Accel. Spectrometers Detect. Assoc. Equip. 2020, 959, 163586.1–163586.5. [Google Scholar] [CrossRef]

- Xie, X.; Simon, J.D. High energy and tunable picosecond laser pulses at 1 kHz: Synchronously pumping a dye laser with a mode-locked, Q-switched and cavity dumped Nd:YAG laser system. Opt. Commun. 1989, 69, 303–307. [Google Scholar] [CrossRef]

- Kornev, A.F.; Pokrovskiy, V.P.; Gagarskiy, S.V.; Yu, F.Y.; Gnatyuk, P.A.; Kovyarov, A.S. 946nm Nd:YAG laser with cavity dumping. Opt. Lett. 2018, 43, 3457–3460. [Google Scholar] [CrossRef] [PubMed]

- Okishev, A.; Battaglia, D.; Begishev, I.; Zuegel, J. Highly stable, diode-pumped, cavity-dumped Nd:YLF regenerative amplifier for the OMEGA laser fusion facility. In Advanced Solid State Lasers; Optica Publishing Group: Washington, DC, USA, 2002; Volume 68, p. WB12. [Google Scholar] [CrossRef]

- Okishev, A.V.; Zuegel, J.D. Highly stable, all-solid-state Nd:YLF regenerative amplifier. Appl. Opt. 2004, 43, 6180–6186. [Google Scholar] [CrossRef]

- Murray, J.E.; Lowdermilk, W.H. ND:YAG regenerative amplifier. J. Appl. Phys. 1980, 51, 3548–3556. [Google Scholar] [CrossRef]

- Calendron, A.L.; Çankaya, H.; Kärtner, F.X. High-energy kHz Yb:KYW dual-crystal regenerative amplifier. Opt. Express 2014, 22, 24752–24762. [Google Scholar] [CrossRef] [PubMed]

- Melnikov, K. Electro-optic Q-switch driver design specifics. Proc. Soc. Photo-Opt. Instrum. Eng. 2011, 7822, 39–45. [Google Scholar]

- Plourde, B.; Mack, M.E.; Verro, E. Simple, fast rise time, high repetition rate Pockels cell driver. Rev. Sci. Instrum. 1980, 51, 549–550. [Google Scholar] [CrossRef]

- Mccaulay, J.; Byrne, H.; Dennis, W.M.; Shen, G.; Blau, W. Thyratron-based Pockels cell driver for single pulse switch-out in mode-locked lasers. Opt. Laser Technol. 1989, 21, 401–405. [Google Scholar] [CrossRef]

- Dharmadhikari, A.K.; Dharmadhikari, J.A.; Adhi, K.P.; Mehendale, N.Y.; Aiyer, R.C. Low cost fast switch using a stack of bipolar transistors as a pockel cell driver. Rev. Sci. Instrum. 1996, 67, 4399–4400. [Google Scholar] [CrossRef]

- Dharmadhikari, J.A.; Dharmadhikari, A.K.; Mehendale, N.Y.; Aiyer, R.C. Low cost Pockels cell driver for pulsed solid state lasers. Opt. Laser Technol. 1998, 30, 447–450. [Google Scholar] [CrossRef]

- Fulkerson, E.S.; Norman, D.C.; Booth, R. Driving pockels cells using avalanche transistor pulsers. In Proceedings of the Digest of Technical Papers. 11th IEEE International Pulsed Power Conference (Cat. No. 97CH36127), Baltimore, MD, USA, 29 June–2 July 1997; IEEE: Piscataway Township, NJ, USA, 1997; Volume 2, pp. 1341–1346. [Google Scholar]

- Bishop, A.I.; Barker, P.F. Subnanosecond Pockels cell switching using avalanche transistors. Rev. Sci. Instrum. 2006, 77, 3066. [Google Scholar] [CrossRef]

- Li, J.; Zhao, Z.; Sun, Y.; Liu, Y.; Ren, Z.; He, J.; Cao, H.; Zheng, M. A hybrid pulse combining topology utilizing the combination of modularized avalanche transistor Marx circuits, direct pulse adding, and transmission line transformer. Rev. Sci. Instrum. 2017, 88, 033507. [Google Scholar] [CrossRef]

- Rutten, T.P.; Wild, N.; Veitch, P.J. Fast rise time, long pulse width, kilohertz repetition rate Q-switch driver. Rev. Sci. Instrum. 2007, 78, 2940. [Google Scholar] [CrossRef]

- Baker, R.J.; Johnson, B.P. Series operation of power MOSFETs for high-speed, high-voltage switching applications. Rev. Sci. Instrum. 1993, 64, 1655–1656. [Google Scholar] [CrossRef]

- Melnikov, K.; Biryuchinskiy, S.; Melnikov, V. Improvement of Q-switch operation for medical solid-state laser systems. In Proceedings of the Business Engineering and Industrial Applications Colloquium (BEIAC), Langkawi, Malaysia, 7–9 April 2013; IEEE: Piscataway Township, NJ, USA, 2013; pp. 425–428. [Google Scholar]

- Sinkevicius, G.; Baskys, A.; Tamoauskas, G. Active Suppression of Piezoelectric Ringing in Pockels Cells for Laser Cavity Application. Multidiscip. Digit. Publ. Inst. 2021, 13, 677. [Google Scholar] [CrossRef]

- Kim, H.S.; Yu, C.H.; Jang, S.R.; Kim, G.H. Solid-State Pulsed Power Modulator with Fast Rising/Falling Time and High Repetition Rate for Pockels Cell Drivers. IEEE Trans. Ind. Electron. 2018, 66, 4334–4343. [Google Scholar] [CrossRef]

- Rutten, T.P.; Veitch, P.J.; Munch, J. Efficient Pulse Stretching of Q-Switched Lasers. IEEE J. Quantum Electron. 2008, 44, 911–915. [Google Scholar] [CrossRef]

- Kölbl, J.; Fröschl, M.; Seedsman, A.; Gao, Y.; Dawson, M. Fast switching pockels cell driver for SLR laser system. In Proceedings of the 16th International Workshop on Laser Ranging, Poznan, Poland, 12–17 October 2008; pp. 429–434. [Google Scholar]

- Xu, Y.; Chen, W.; Liang, H.; Li, Y.H.; Liang, F.T.; Shen, Q.; Liao, S.K.; Peng, C.Z. Megahertz high voltage pulse generator suitable for capacitive load. Aip Adv. 2017, 7, 115210. [Google Scholar] [CrossRef]

- Bernius, M.T.; Chutjian, A. Improved high-voltage, high-frequency square-wave generator. Rev. Sci. Instrum. 1990, 61, 925–927. [Google Scholar] [CrossRef]

- Feng, X.W.; Long, X.W.; Tan, Z.Q. Nanosecond square high voltage pulse generator for electro-optic switch. Rev. Sci. Instrum. 2011, 82, 075102. [Google Scholar] [CrossRef] [PubMed]

- Balogh, L. Fundamentals of MOSFET and IGBT Gate Driver Circuits; Application Report; Texas Instruments: Dallas, TX, USA, 2017. [Google Scholar]

| Switching Components | Breakdown Voltage | Switching Speed | Rising/Falling Time | Complexity |

|---|---|---|---|---|

| Vacuum tubes | high | low | medium | medium |

| Avalanche transistors | low | medium | fast | high |

| SiC MOSFETs | medium | fast | medium | low |

| Parameters | Values |

|---|---|

| Maximum pulse voltage | 2.0 kV |

| Rising/falling time | <10 ns |

| Maximum frequency | 1 MHz |

| Minimum pulse width | 10 ns |

| Maximum pulse width | no limitation |

| Adjustable pulse step | 10 ns |

| Parameters | Values |

|---|---|

| Vds (br) | 1200 V |

| Vgs (th) | 2.5 V |

| Qg | 19 nC |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, Y.; Liu, W.; Chen, J.; Sun, X.; Zhang, T. A Novel PWM Signal-Generation Strategy for Pockels Cell Drivers. Photonics 2023, 10, 866. https://doi.org/10.3390/photonics10080866

Wu Y, Liu W, Chen J, Sun X, Zhang T. A Novel PWM Signal-Generation Strategy for Pockels Cell Drivers. Photonics. 2023; 10(8):866. https://doi.org/10.3390/photonics10080866

Chicago/Turabian StyleWu, Yajun, Wenqing Liu, Jinxin Chen, Xinhui Sun, and Tianshu Zhang. 2023. "A Novel PWM Signal-Generation Strategy for Pockels Cell Drivers" Photonics 10, no. 8: 866. https://doi.org/10.3390/photonics10080866

APA StyleWu, Y., Liu, W., Chen, J., Sun, X., & Zhang, T. (2023). A Novel PWM Signal-Generation Strategy for Pockels Cell Drivers. Photonics, 10(8), 866. https://doi.org/10.3390/photonics10080866