Design and Validation of a Reduced Switching Components Step-Up Multilevel Inverter (RSCS-MLI)

Abstract

:1. Introduction

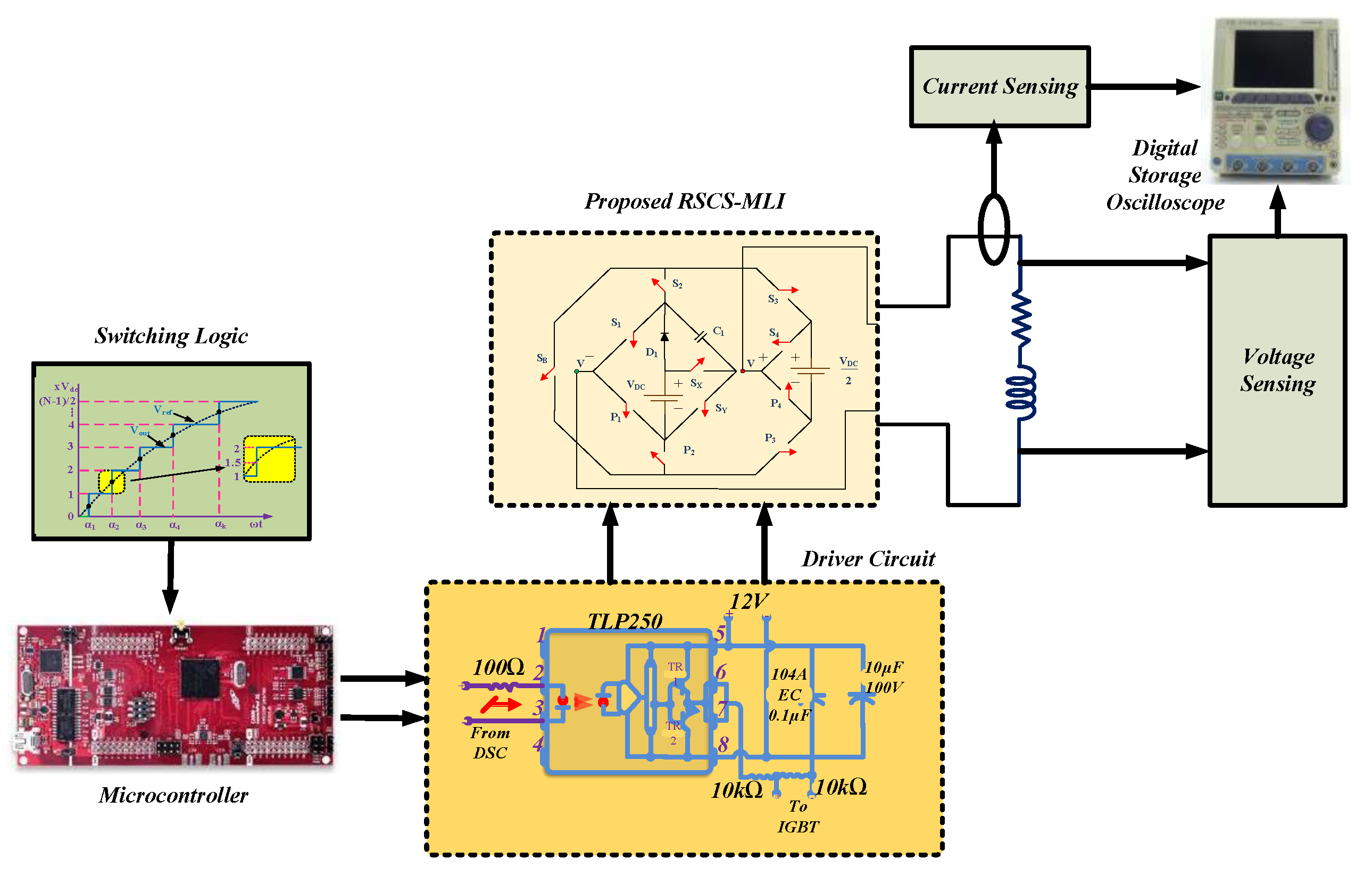

2. Proposed RSCS-MLI Circuit

2.1. Description and Operation

2.2. Total Standing Voltage

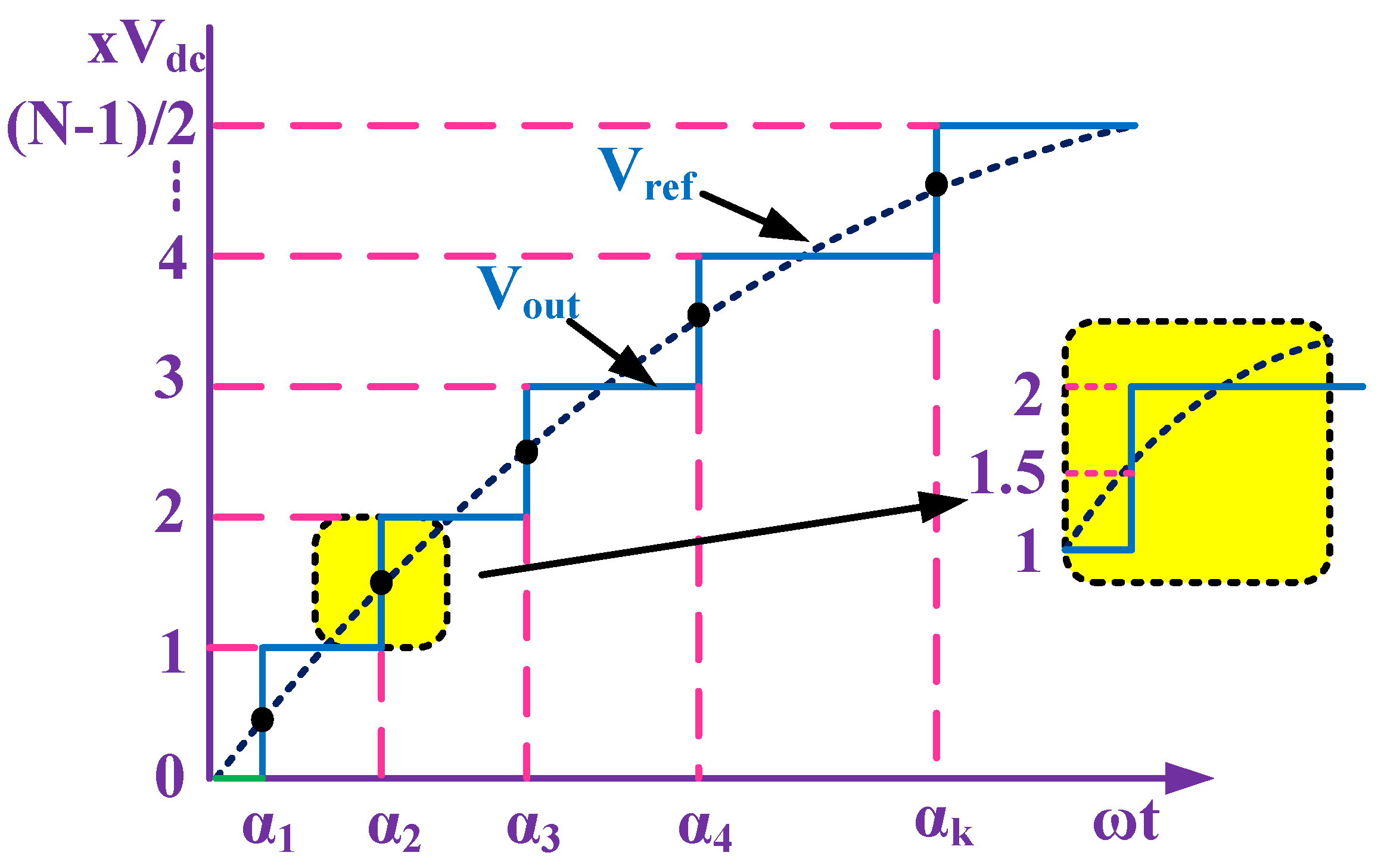

3. Modulation Technique

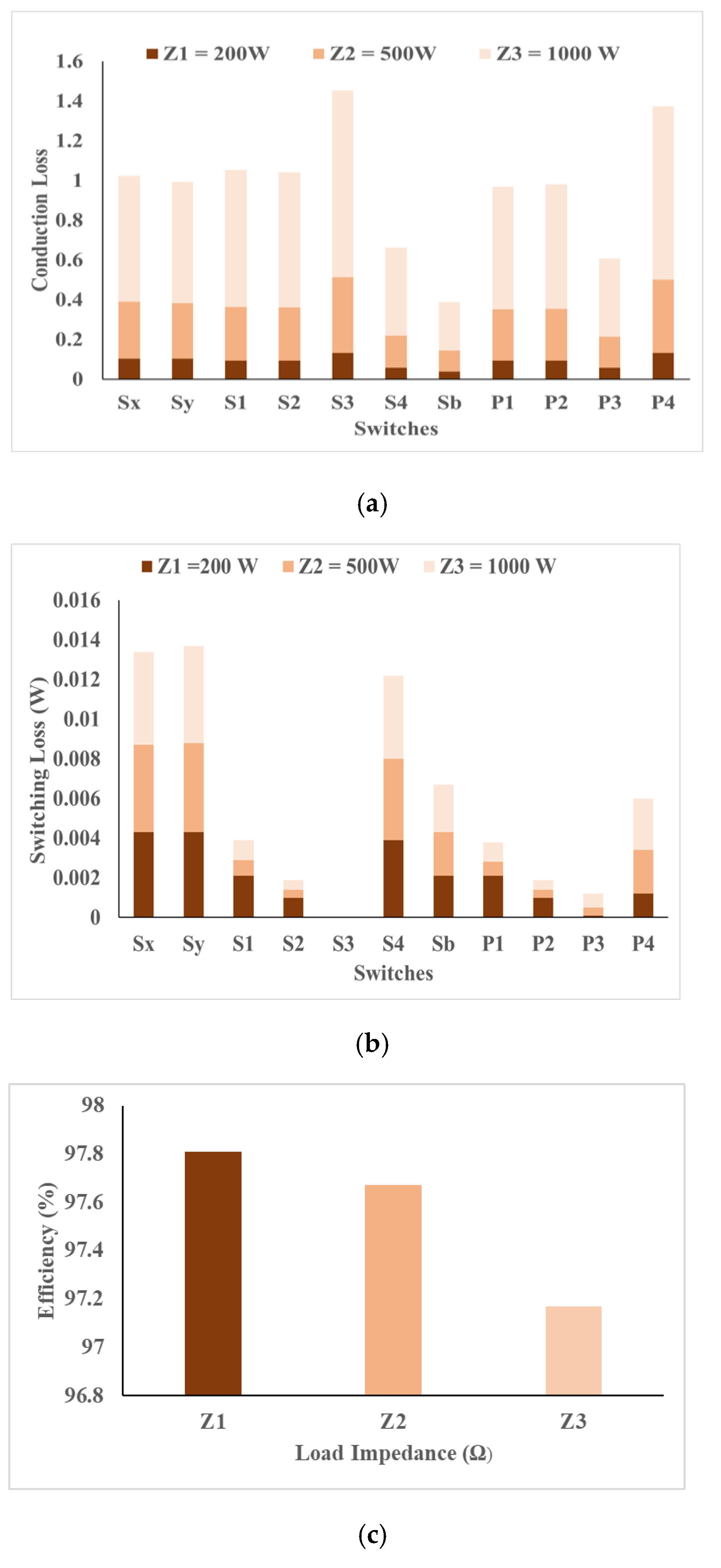

4. Power Loss Analysis

4.1. Conduction Losses

4.2. Switching Losses

5. Comparison with Different Topologies

6. Results and Analysis

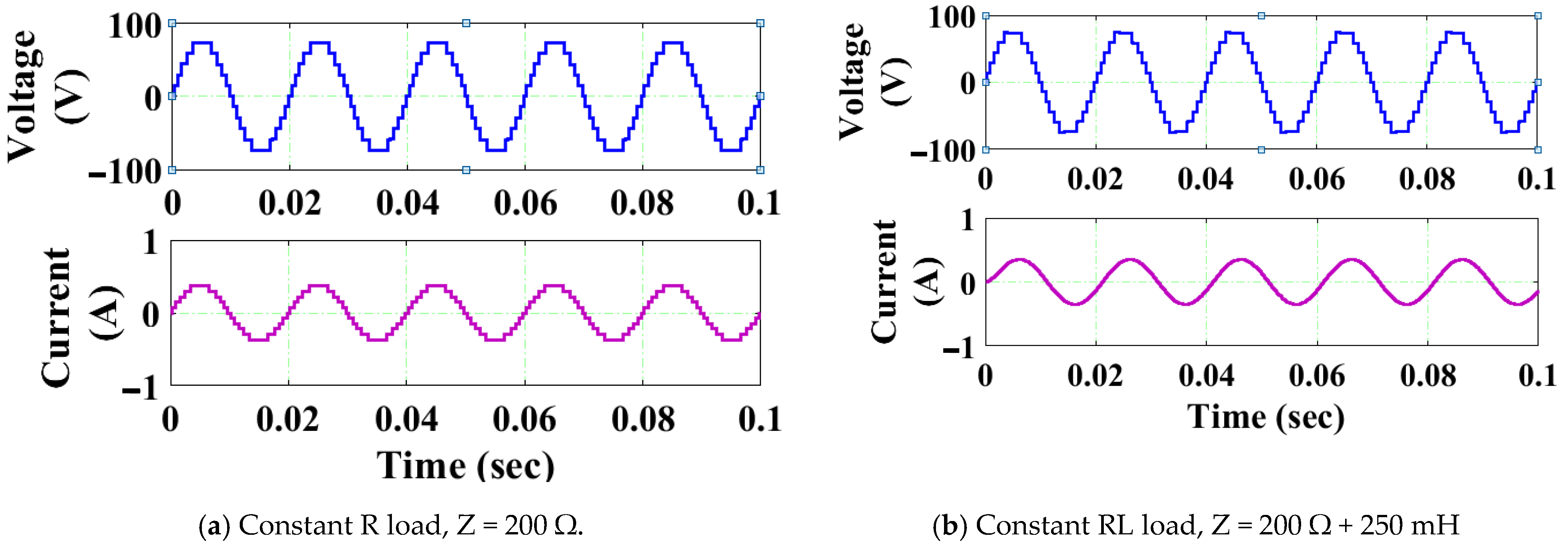

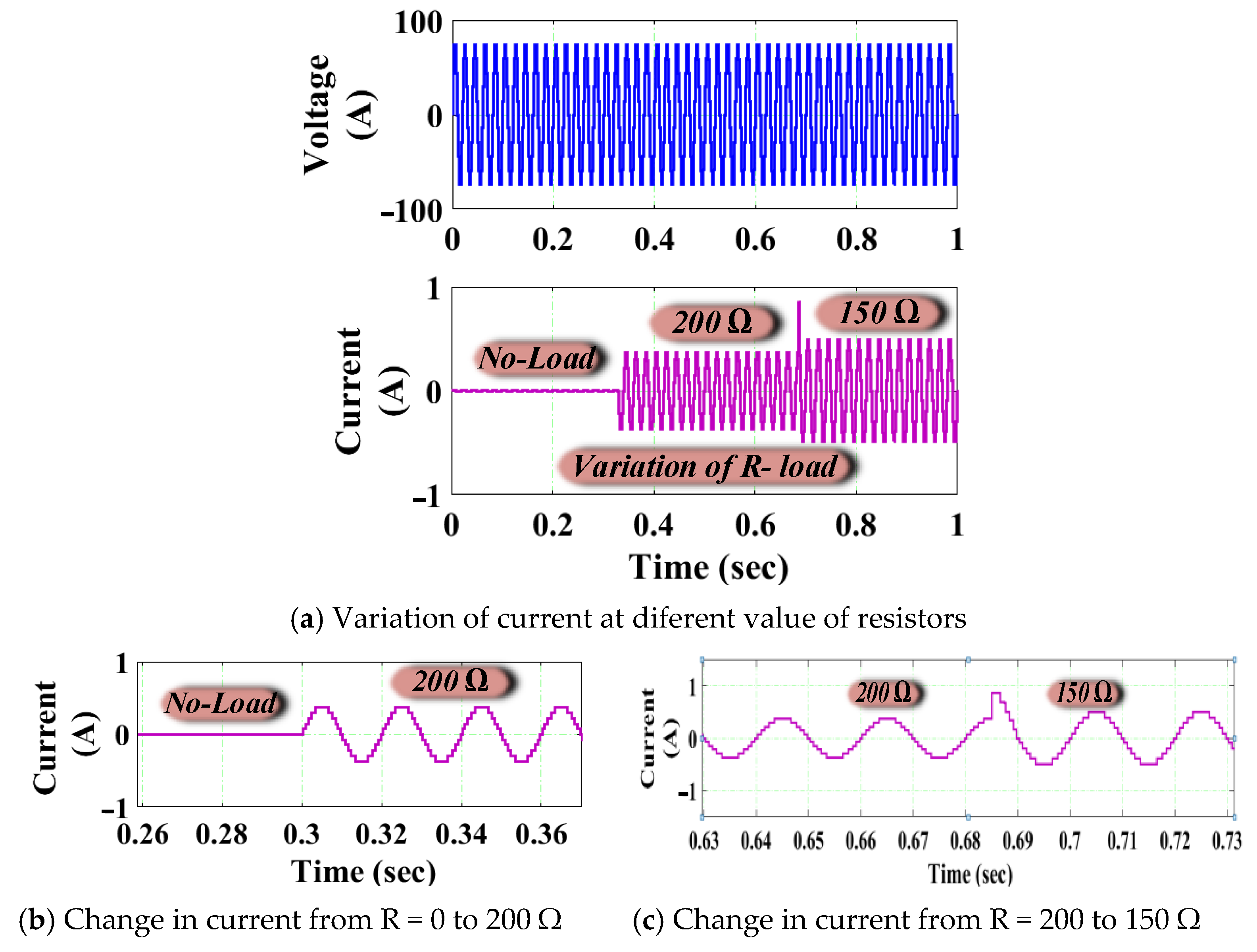

6.1. Simulation Outcomes

6.1.1. Constant R and RL Load

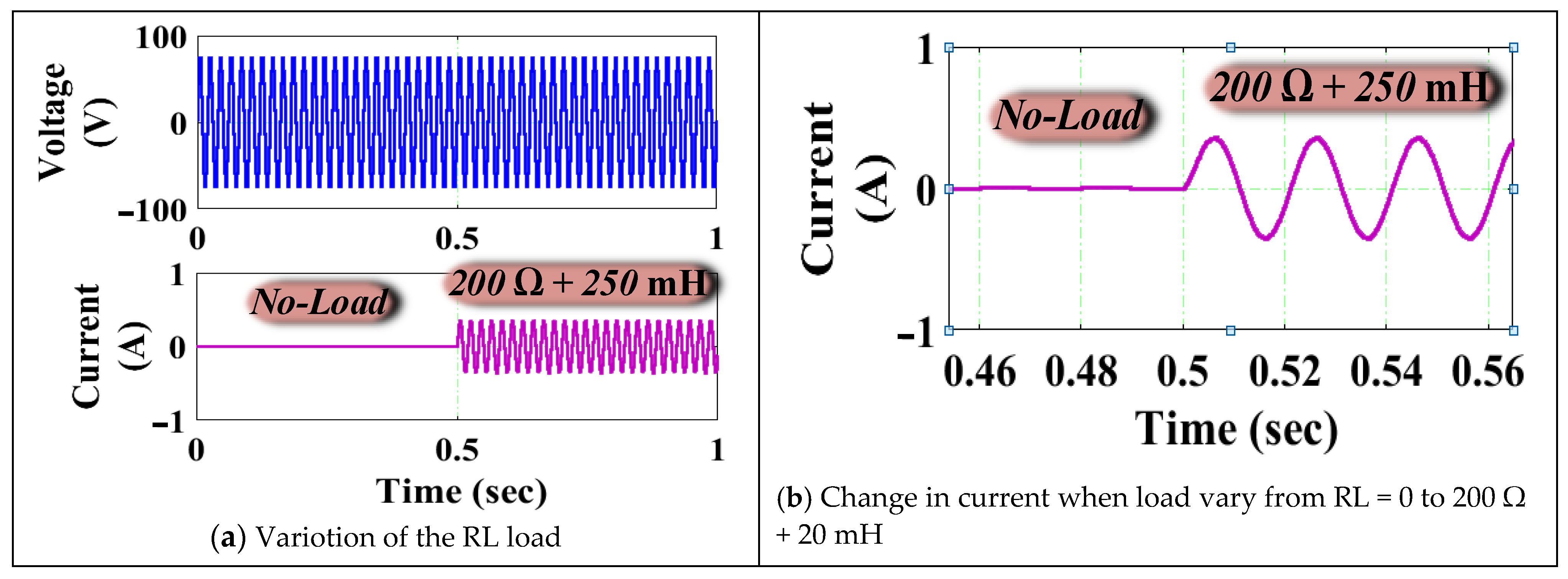

6.1.2. Variable R and RL Load

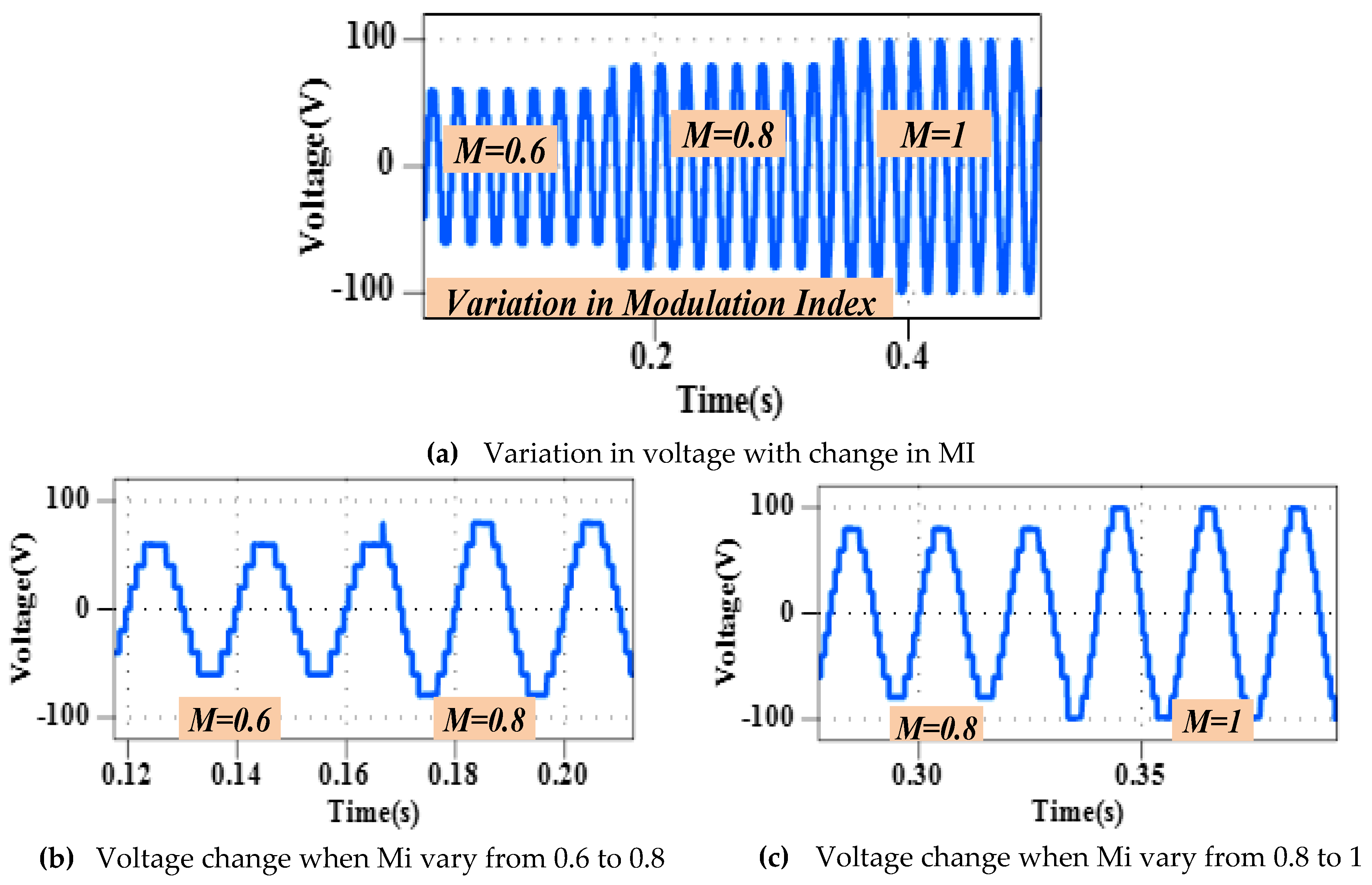

6.1.3. Variation in Modulation Index

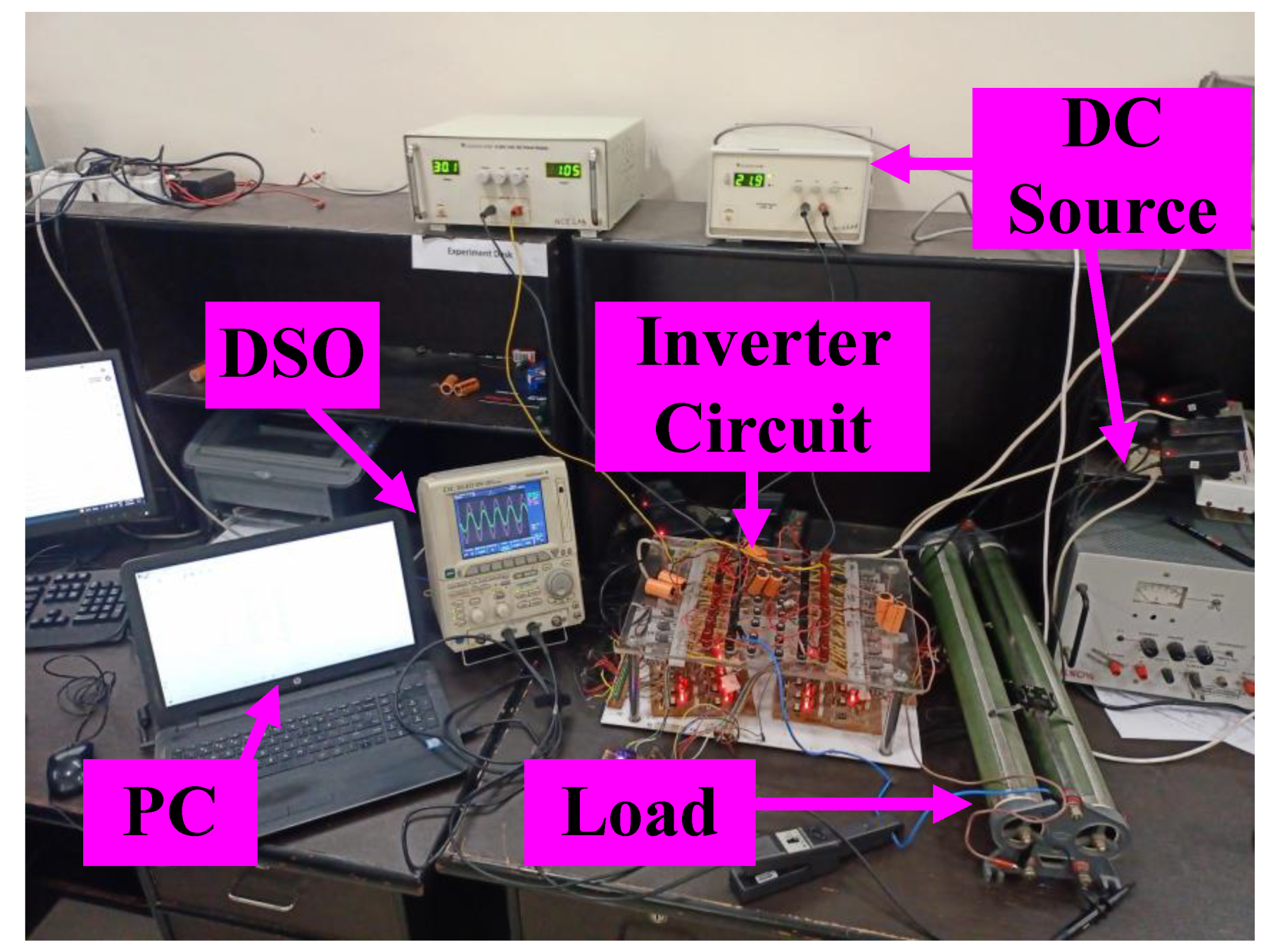

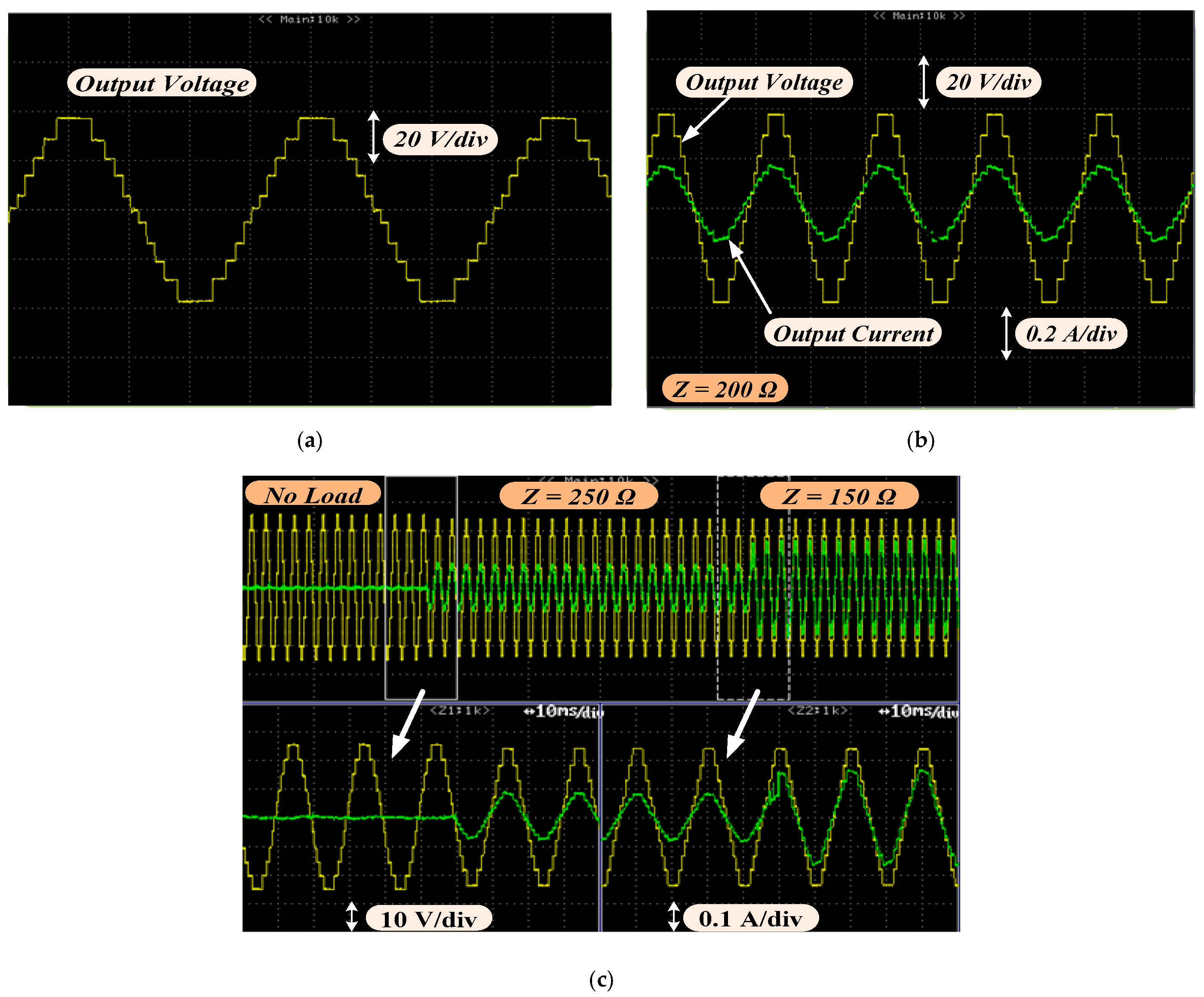

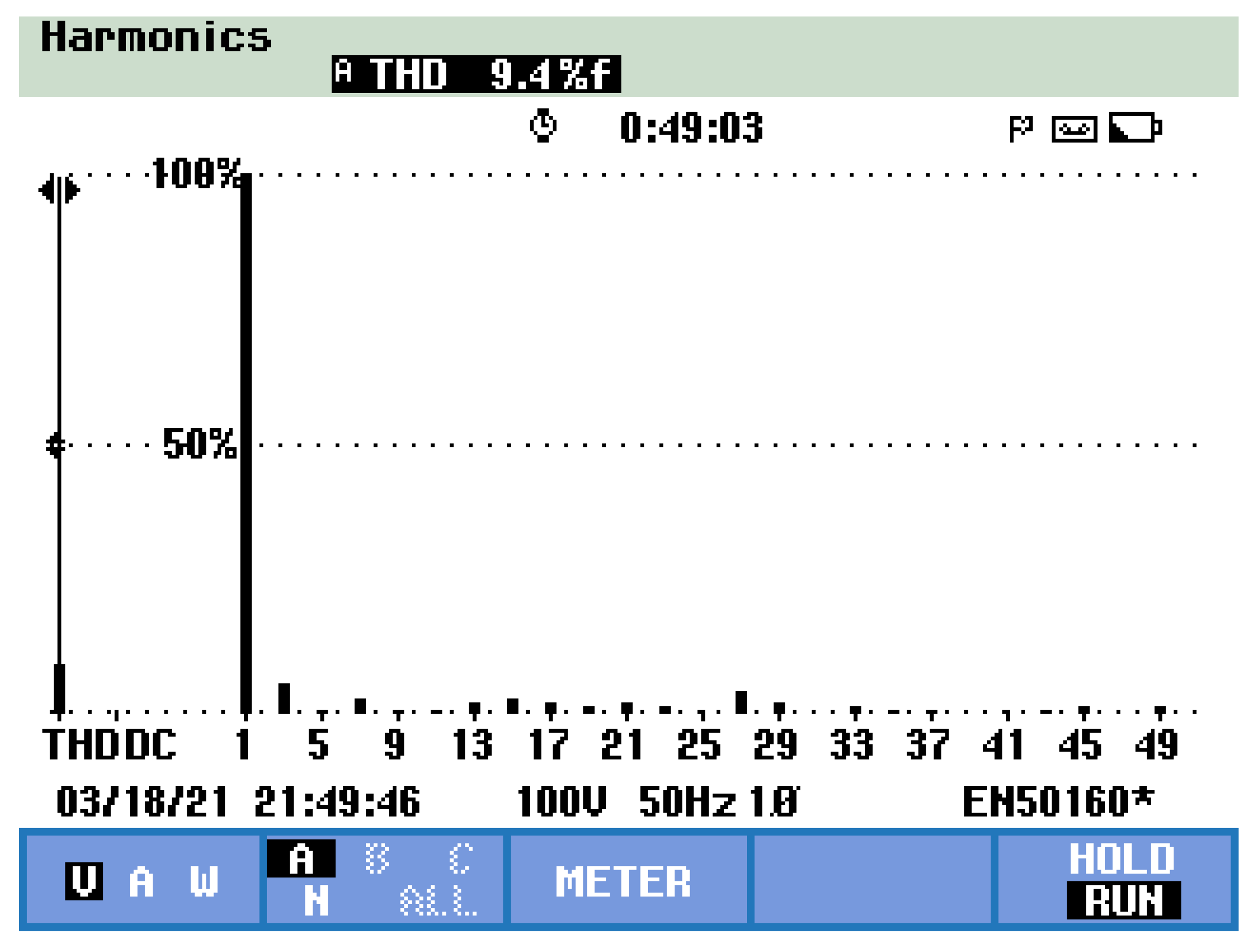

6.2. Hardware Implementation

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kumari, M.; Siddique, M.D.; Sarwar, A.; Mekhilef, S.; Tariq, M. A twice boost nine-level switched-capacitor multilevel (2B-9L-SCMLI) inverter with self-voltage balancing capability. Int. J. Circ. Theor. Appl. 2021, 49, 1–15. [Google Scholar] [CrossRef]

- Sarwer, Z.; Siddique, M.D.; Iqbal, A.; Sarwar, A.; Mekhilef, S. An improved asymmetrical multilevel inverter topology with reduced semiconductor device count. Int. Trans. Electr. Energ. Syst. 2020, 30, e12587. [Google Scholar] [CrossRef]

- Beig, A.R.; Ranganathan, V.T. Influence of placement of small space vectors on the performance of PWM techniques for three level inverters. In Proceedings of the IECON’03 29th Annual Conference of the IEEE Industrial Electronics Society, Roanoke, VA, USA, 2–6 November 2003; Volume 3, pp. 2764–2770. [Google Scholar] [CrossRef] [Green Version]

- Sathik, M.J.; Krishnasamy, V. An assessment of recent multilevel inverter topologies with reduced power electronics components for renewable applications. Renew. Sustain. Energy Rev. 2017, 82, 3379–3399. [Google Scholar]

- Prabaharan, N.; Palanisamy, K. A comprehensive review on reduced switch multilevel inverter topologies, modulation techniques and applications. Renew. Sustain. Energy Rev. 2017, 76, 1248–1282. [Google Scholar] [CrossRef]

- Kumari, M.; Siddique, M.D.; Sarwar, A.; Tariq, M.; Mekhilef, S.; Iqbal, A. Recent trends and review on switched-capacitor-based single-stage boost multilevel inverter. Int. Trans. Electr. Energ. Syst. 2021, 31, e12730. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K.; Dessaint, L.A. A novel six-band hysteresis control for the packed U cells seven-level converter: Experimental validation. IEEE Trans. Ind. Electron. 2012, 59, 3808–3816. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Rawa, M.; Wahyudie, A.; Chokaev, B.; Salamov, I. Extended Multilevel Inverter Topology with Reduced Switch Count and Voltage Stress. IEEE Access 2020, 8, 201835–201846. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Memon, M.A. Optimal Design of a New Cascaded Multilevel Inverter Topology with Reduced Switch Count. IEEE Access 2019, 7, 24498–24510. [Google Scholar] [CrossRef]

- Priyadarshi, A.; Kar, P.K.; Karanki, S.B. A Single Source Transformer-Less Boost Multilevel Inverter Topology with Self-Voltage Balancing. IEEE Trans. Ind. Appl. 2020, 56, 3954–3965. [Google Scholar] [CrossRef]

- Prasanth, S.R.; John, M.; Rao, S. 11-Level Multilevel Inverter with Reduced Number of Switches using Level Shift Modulation. Int. J. Mod. Trends Sci. Technol. 2017, 3, 53–58. [Google Scholar]

- Ganesan, R.G.; Shankar, R.; Bhaskar, M.; Narayanan, K. Switched Capacitor Based Multilevel Boost Inverter for Smart Grid Applications. In Proceedings of the 2019 IEEE Innovative Smart Grid Technologies-Asia (ISGT Asia), Chengdu, China, 21–24 May 2019; pp. 3902–3907. [Google Scholar] [CrossRef]

- Arif, M.S.B.; Mustafa, U.; Siddique, M.D.; Ahmad, S.; Iqba, A.; Ashique, R.H.; Ayob, S.b. An improved asymmetrical multi-level inverter topology with boosted output voltage and reduced components count. IET Power Electron. 2021, 14, 1–15. [Google Scholar] [CrossRef]

- Vasudevamurthy, S.; Somashekara, G. Simulation of 11-level Inverter with Reduced Number of Power Switches for R and RL load. IJAREEIE 2017, 6, 3458–3467. [Google Scholar]

- Khan, M.N.H.; Forouzesh, M.; Siwakoti, Y.P.; Li, L.; Blaabjerg, F. Switched Capacitor Integrated (2n + 1)-Level Step-Up Single-Phase Inverter. IEEE Trans. Power Electron. 2020, 35, 8248–8260. [Google Scholar] [CrossRef]

- Sarwer, Z.; Sarwar, A.; Zaid, M.; Tariq, M.; Ali, M.; Arif, M.S.B. A switched capacitor multilevel inverter with self voltage balancing capability. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 16–19 December 2020. [Google Scholar]

- Sarwer, Z.; Siddique, M.D.; Iqbal, A.; Sarwar, A.; Rahman, K.; Mekhilef, S. Seven-level switched-capacitor based multilevel inverter with lesser number of power electronic components and reduced voltage stress. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 16–19 December 2020. [Google Scholar]

- Mahdavi, A.; Abbaszadeh, K.; Mardakheh, N.A. A Boost Switched-Capacitor Multilevel Inverter with Self-Balance and Inductive-load Ability. In Proceedings of the 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 4–6 February 2020. [Google Scholar]

- Kumar, A.R.; Thangavelusamy, D. A modified nearest level modulation scheme for symmetric and asymmetric configurations of cascaded H-bridge inverter. Int. J. Electr. Eng. Educ. 2019, 32, 471–481. [Google Scholar] [CrossRef]

- Samadaei, E.; Kaviani, M.; Bertilsson, K. A 13-levels module (K-Type) with two DC sources for multilevel inverters. IEEE Trans. Ind. Electron. 2019, 66, 5186–5196. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Moradzadeh, M.; Zamiri, E.; Kojabadi, H.M.; Blaabjerg, F. A New Boost Switched-Capacitor Multilevel Converter with Reduced Circuit Devices. IEEE Trans. Power Electron. 2018, 33, 6738–6754. [Google Scholar] [CrossRef]

- Arun, N.M.; Noel, M. Crisscross switched multilevel inverter using cascaded semi-half-bridge cells. IET Power Electron. 2018, 11, 23–32. [Google Scholar] [CrossRef] [Green Version]

- Mokhberdoran, A.; Ajami, A. Symmetric and asymmetric design and implementation of new cascaded multilevel inverter topology. IEEE Trans. Power Electron. 2014, 29, 6712–6724. [Google Scholar] [CrossRef]

- Hussain, M.R.; Sarwar, A.; Siddique, M.D.; Mekhilef, S.; Ahmad, S.; Sharaf, M.; Zaindin, M.; Firdausi, M. A Novel Switched-Capacitor Multilevel Inverter Topology for Energy Storage and Smart Grid Applications. Electronics 2020, 9, 1703. [Google Scholar] [CrossRef]

- Siddique, M.D.; Iqbal, A.; Sathik, M.J.; Mekhilef, S.; Almakhles, D.J. Design and implementation of a new unity gain nine-level active neutral point clamped multilevel inverter topology. IET Power Electron. 2020, 13, 3204–3208. [Google Scholar] [CrossRef]

- Arif, M.S.B.; Mustafa, U.; Ayob, S.B.M.; Rodriguez, J.; Nadeem, A.; Abdelrahem, M. Asymmetrical 17-level Inverter Topology with Reduced Total Standing Voltage and Device Count. IEEE Access 2021, 9, 69710–69723. [Google Scholar] [CrossRef]

| Vo | SX | S1 | S2 | S3 | S4 | SB | SY | P1 | P2 | P3 | P4 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Positive Voltage Levels | 2.5 VDC | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 |

| 2 VDC | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | |

| 1.5 VDC | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | |

| VDC | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | |

| 0.5 VDC | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | |

| Zero Voltage Level | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| Negative Voltage Levels | −0.5 VDC | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| −VDC | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | |

| −1.5 VDC | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | |

| −2 VDC | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | |

| −2.5 VDC | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| Topology | Nswitch | Ndiode | NT | NL/NT | Nsource | Ncap | NL | TSVP.U. |

|---|---|---|---|---|---|---|---|---|

| [8] | 8 | 0 | 8 | 1.4 | 3 | 0 | 11 | 9.6 |

| [9] | 8 | 0 | 8 | 1.4 | 3 | 0 | 11 | 5.6 |

| [10] | 10 | 9 | 19 | 0.6 | 1 | 9 | 11 | 8 |

| [18] | 12 | 1 | 13 | 0.8 | 2 | 2 | 11 | 6.4 |

| [19] | 11 | 5 | 16 | 0.7 | 5 | 0 | 11 | 5 |

| [20] | 14 | 0 | 14 | 0.9 | 2 | 2 | 13 | 6.33 |

| [25] | 10 | 4 | 14 | 0.6 | 1 | 4 | 9 | 7 |

| Proposed | 11 | 1 | 12 | 0.9 | 2 | 1 | 11 | 5 |

| Components | Specification |

|---|---|

| DC voltage source (2) | 20V, 40V |

| Fundamental frequency | 50 Hz |

| Capacitor | 3000 µF |

| Load | R = 100 Ω, 200 Ω, L = 250 mH |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wasiq, M.; Sarwar, A.; Sarwer, Z.; Tariq, M.; Ahmad, S.; Al-Shayea, A.M.; Hossain, J. Design and Validation of a Reduced Switching Components Step-Up Multilevel Inverter (RSCS-MLI). Processes 2021, 9, 1948. https://doi.org/10.3390/pr9111948

Wasiq M, Sarwar A, Sarwer Z, Tariq M, Ahmad S, Al-Shayea AM, Hossain J. Design and Validation of a Reduced Switching Components Step-Up Multilevel Inverter (RSCS-MLI). Processes. 2021; 9(11):1948. https://doi.org/10.3390/pr9111948

Chicago/Turabian StyleWasiq, Mohammad, Adil Sarwar, Zeeshan Sarwer, Mohd Tariq, Shafiq Ahmad, Adel M. Al-Shayea, and Jahangir Hossain. 2021. "Design and Validation of a Reduced Switching Components Step-Up Multilevel Inverter (RSCS-MLI)" Processes 9, no. 11: 1948. https://doi.org/10.3390/pr9111948

APA StyleWasiq, M., Sarwar, A., Sarwer, Z., Tariq, M., Ahmad, S., Al-Shayea, A. M., & Hossain, J. (2021). Design and Validation of a Reduced Switching Components Step-Up Multilevel Inverter (RSCS-MLI). Processes, 9(11), 1948. https://doi.org/10.3390/pr9111948