Implementation of Unbalanced Ternary Logic Gates with the Combination of Spintronic Memristor and CMOS

Abstract

1. Introduction

- A flexible memristor-CMOS-based logic circuit was designed, which could perform the different ternary logic gates (i.e., the NAND, NOR, AND, and OR gates) by easily changing the polarities of the interconnected memristors.

- Due to the participation of the spintronic memristor, the logic states can be stored in the memristor. That is, the logic computation and data storage are integrated into the proposed logic circuit, which opens up a new path to explore the new intelligent computation systems, in contrast to the classical von Neumann system with separated computation and storage configuration.

- The CMOS switches installed in the reading circuit means the entire logic circuit has a sufficient load capacity, and the signal degradation issue can also be addressed effectively.

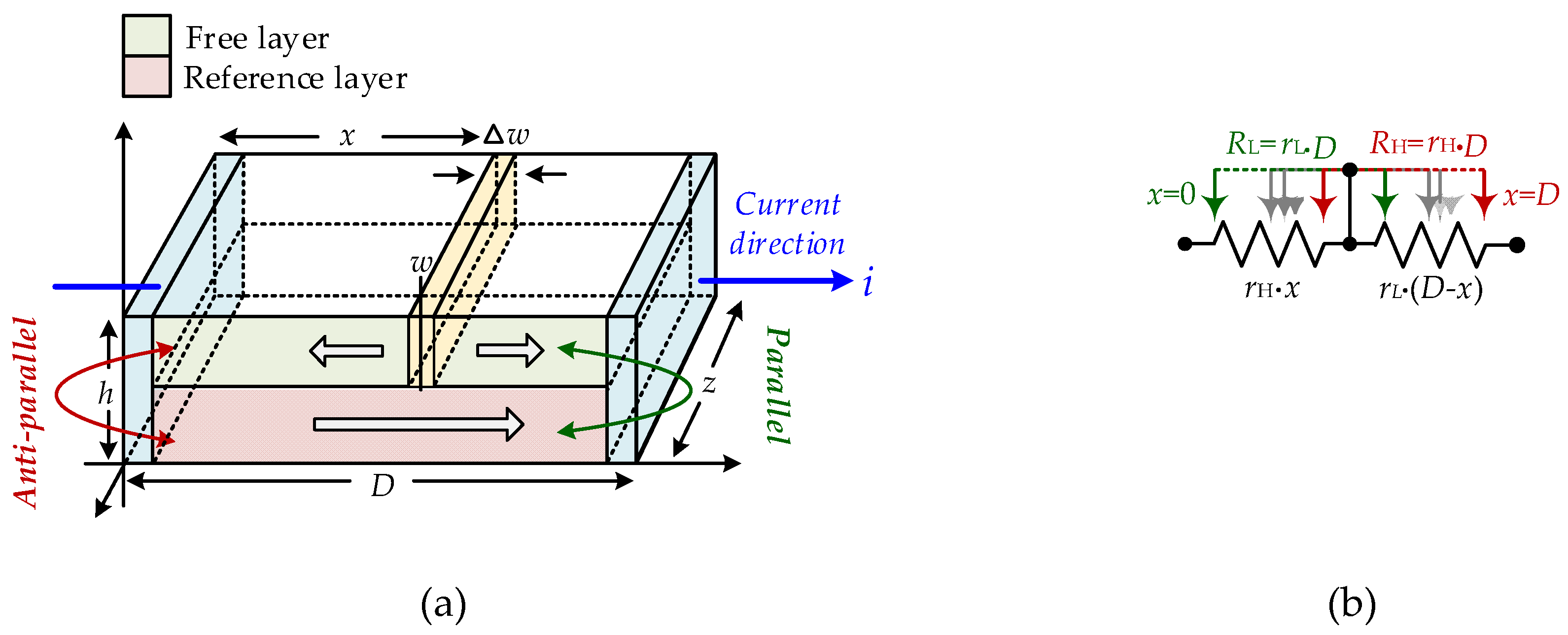

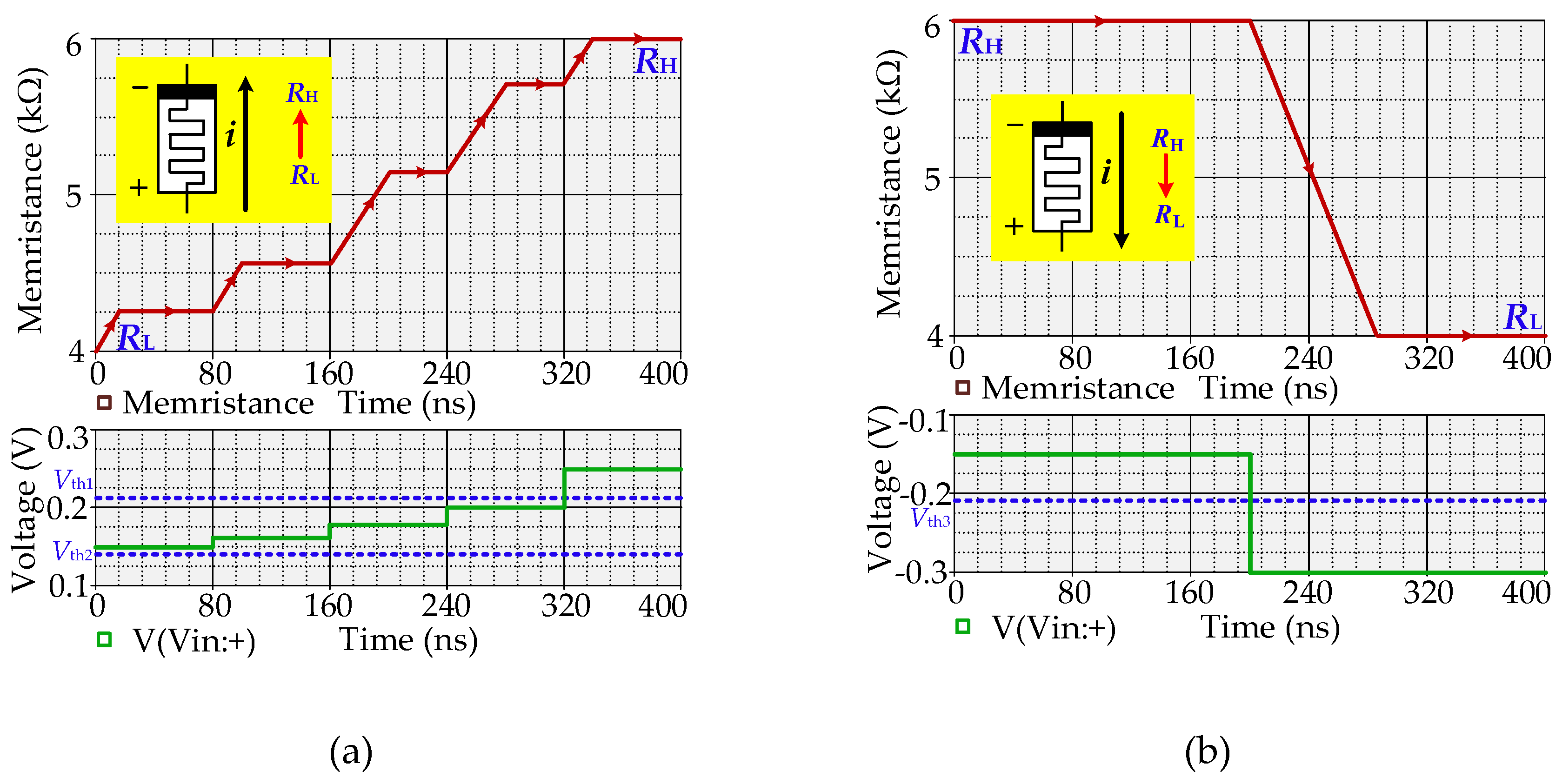

2. Spintronic Memristor

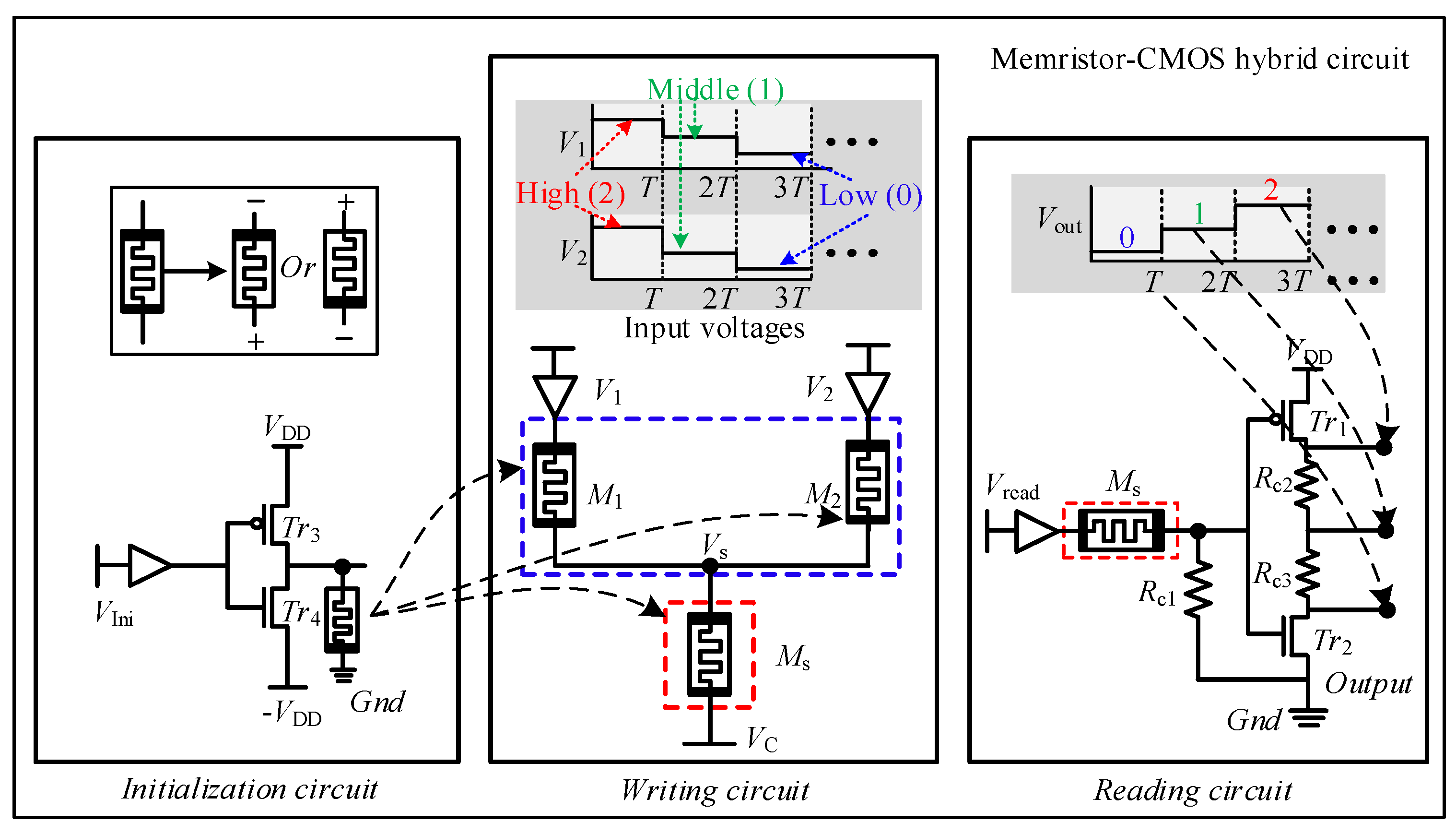

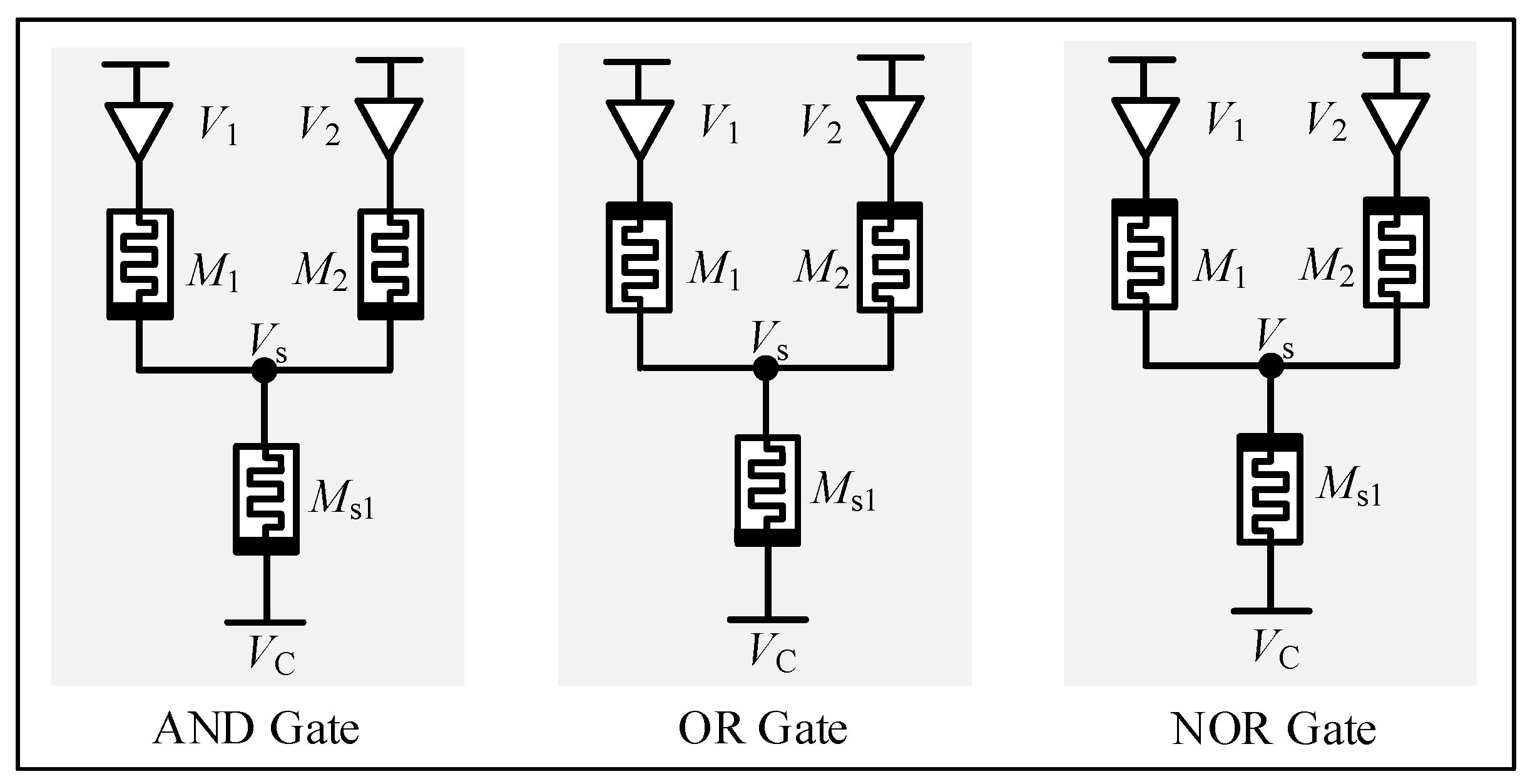

3. Implementation of Ternary Logic Gates

3.1. Memristor-CMOS Hybrid Circuit

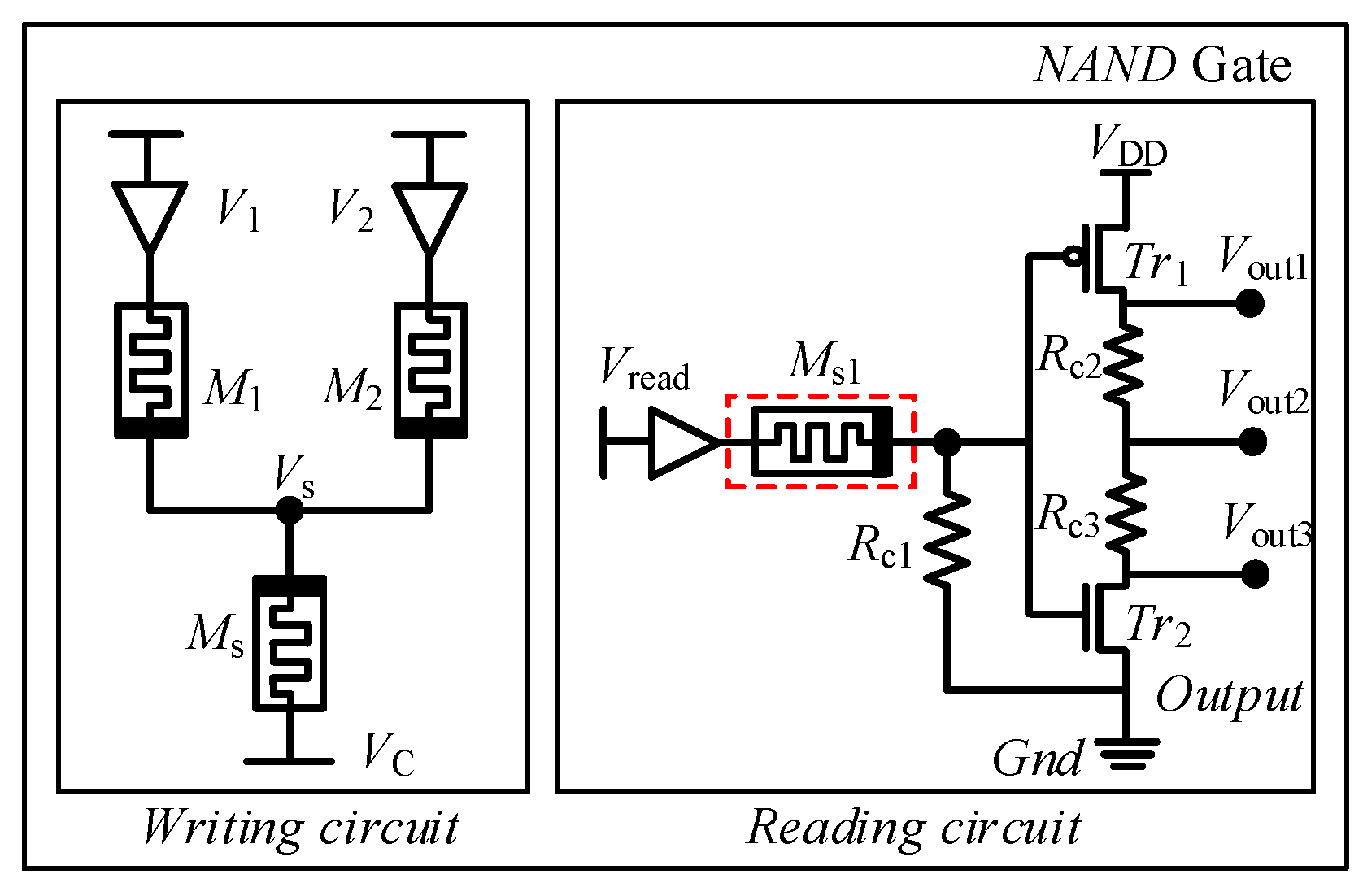

3.2. NAND Gate

- Case a: When V1 = V2 = VH (logic “2”), the node voltage Vs ≈ VH (From Equation (8)). The voltage applied to the load memristor Ms1 is equal to VH − Vc. Assuming VH − Vc > RMid·Icr, the load memristance Rs1 will go down to its lowest value RSL within a very short time.

- Case b: When V1 = V2 = VMid (logic “1”), the node voltage Vs ≈ VMid. The voltage applied to the load memristor Ms1 is equal to VMid – Vc. Assuming |VMid − Vc|≤ RMid·Icr, the load memristance Rs1 remains in the initial state RMid.

- Case c: When V1 = V2 = VL (logic “0”), the node voltage Vs ≈ VL. The voltage applied to the load memristor Ms1 is equal to Vc − VL. Assuming |Vc − VL| > RMid·Icr, the load memristance Rs1 will sharply increase to its highest value RSH.

- Case d: When V1 = VL and V2 = VH (or V1 = VH and V2 = VL), the node voltage Vs can be calculated using:

- Case e: When V1 = VL and V2 = VMid (or V1 = VMid and V2 = VL), the node voltage Vs can be calculated using:

- Case f: When V1 = VH and V2 = VMid (or V1 = VMid and V2 = VH), the node voltage Vs can be expressed as:

- Case I: When the load memristance Rs1 = RSH, the node voltage Vg can be calculated using:

- Case II: When the load memristance Rs1 = RMid, the node voltage Vg can be given as:

- Case III: When the load memristance Rs1 = RSL, The node voltage can be computed using:

3.3. Other Ternary Logic Gates

3.4. Comparison and Analysis

4. Circuit Simulations and Analysis

4.1. Experimental Environment

4.2. Parameter Selection

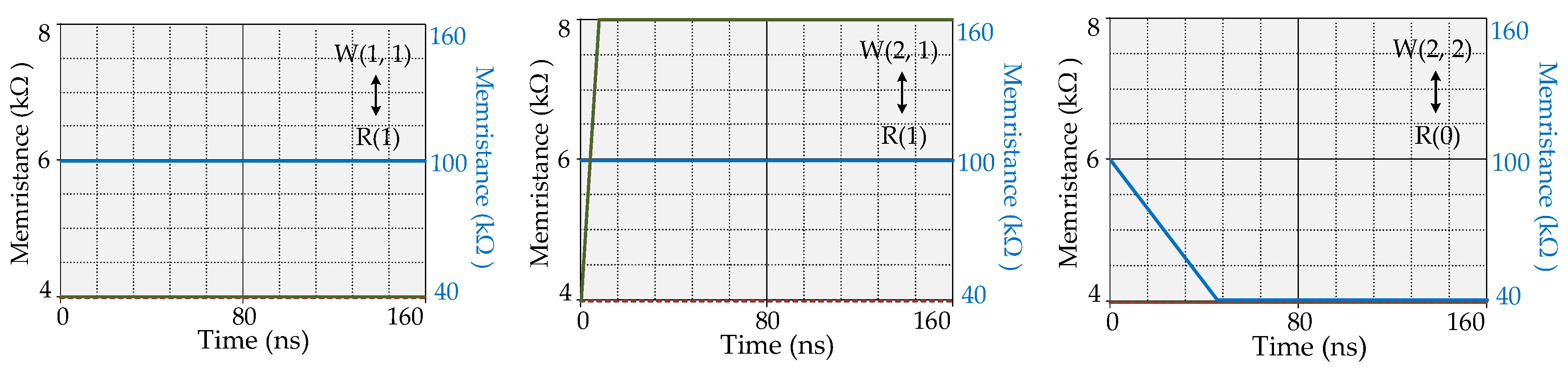

4.3. Simulation Results and Analysis

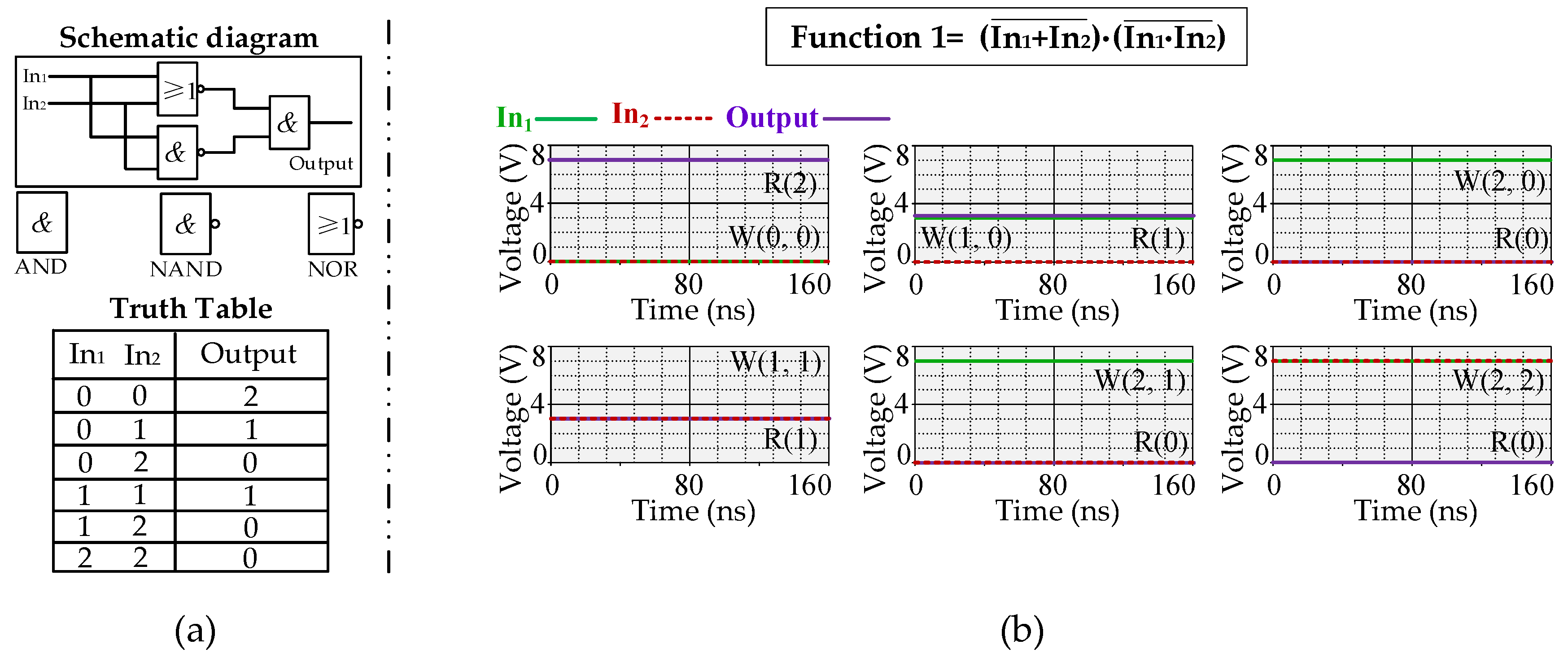

4.3.1. Case Study 1

4.3.2. Case Study 2

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Waldrop, M.M. The chips are down for Moore’s law. Nature News 2016, 530, 144. [Google Scholar] [CrossRef] [PubMed]

- Chua, L. Memristor-the missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef] [PubMed]

- Dong, Z.; Lai, C.S.; Qi, D.; Xu, Z.; Li, C.; Duan, S. A general memristor-based pulse coupled neural network with variable linking coefficient for multi-focus image fusion. Neurocomputing 2018, 308, 172–183. [Google Scholar] [CrossRef]

- Pi, S.; Li, C.; Jiang, H.; Xia, W.; Xin, H.; Yang, J.J.; Xia, Q. Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension. Nat. Nanotechnol. 2019, 14, 35–39. [Google Scholar] [CrossRef]

- Dong, Z.; Lai, C.S.; He, Y.; Qi, D.; Duan, S. Hybrid dual-complementary metal–oxide–semiconductor/memristor synapse-based neural network with its applications in image super-resolution. IET Circ. Device. Syst. 2019, 13, 1241–1248. [Google Scholar] [CrossRef]

- Yao, P.; Wu, H.; Gao, B.; Tang, J.; Zhang, Q.; Zhang, W.; Qian, H. Fully hardware-implemented memristor convolutional neural network. Nature 2020, 577, 641–646. [Google Scholar] [CrossRef] [PubMed]

- Wang, Z.; Li, C.; Song, W.; Rao, M.; Belkin, D.; Li, Y.; Strachan, J.P. Reinforcement learning with analogue memristor arrays. Nature Electron. 2019, 2, 115–124. [Google Scholar] [CrossRef]

- Cao, Y.; Wen, S.; Huang, T.; Zeng, Z. Passivity analysis of delayed reaction–diffusion memristor-based neural networks. Neural Netw. 2019, 109, 159–167. [Google Scholar] [CrossRef]

- Dong, Z.; He, Y.; Hu, X.; Qi, D.; Duan, S. Flexible memristor-based LUC and its network integration for Boolean logic implementation. IET Nanodiele. 2019, 2, 61–69. [Google Scholar] [CrossRef]

- Kvatinsky, S.; Belousov, D.; Liman, S.; Satat, G.; Wald, N.; Friedman, E.G.; Weiser, U.C. MAGIC—Memristor-aided logic. IEEE Trans. Circuits Syst. Brief. 2014, 61, 895–899. [Google Scholar] [CrossRef]

- Guckert, L.; Swartzlander, E.E. MAD gates—Memristor logic design using driver circuitry. IEEE Trans. Circuits Syst. Brief. 2016, 64, 171–175. [Google Scholar] [CrossRef]

- Kim, K.M.; Williams, R.S. A family of stateful memristor gates for complete cascading logic. IEEE Trans. Circuits Syst. Reg. 2019, 66, 4348–4355. [Google Scholar] [CrossRef]

- Zhou, G.; Ren, Z.; Wang, L.; Sun, B.; Duan, S.; Song, Q. Artificial and wearable albumen protein memristor arrays with integrated memory logic gate functionality. Mater. Horizons 2019, 6, 1877–1882. [Google Scholar] [CrossRef]

- El-Slehdar, A.A.; Fouad, A.H.; Radwan, A.G. Memristor-based balanced ternary adder. In Proceedings of the 25th International Conference on Microelectronics (ICM), Beirut, Lebanon, 15–18 December 2013; pp. 1–4. [Google Scholar]

- Khalid, M.; Singh, J. Memristor based unbalanced ternary logic gates. Analog Integr. Circ. S. 2016, 87, 399–406. [Google Scholar] [CrossRef]

- Balla, P.C.; Antoniou, A. Low power dissipation MOS ternary logic family. IEEE J. S-T Circ. 1984, 19, 739–749. [Google Scholar] [CrossRef]

- Lin, S.; Kim, Y.B.; Lombardi, F. A novel CNTFET-based ternary logic gate design. In Proceedings of the 52nd IEEE International Midwest Symposium on Circuits and Systems, Cancun, Mexico, 2–5 August 2009; pp. 435–438. [Google Scholar]

- Appenzeller, J.; Lin, Y.M.; Knoch, J.; Chen, Z.; Avouris, P. Comparing carbon nanotube transistors-the ideal choice: A novel tunneling device design. IEEE Trans. Electron Dev. 2005, 52, 2568–2576. [Google Scholar] [CrossRef]

- Soliman, N.S.; Fouda, M.E.; Radwan, A.G. Memristor-CNTFET based ternary logic gates. Microelectron. J 2018, 72, 74–85. [Google Scholar] [CrossRef]

- Wang, X.; Chen, Y.; Xi, H.; Li, H.; Dimitrov, D. Spintronic memristor through spin-torque-induced magnetization motion. IEEE Electron Dev. Lett. 2009, 30, 294–297. [Google Scholar] [CrossRef]

- Nafea, F.; Dessouki, A.A.S.; El-Rabaie, S.; Elnaghi, B.E.; Ismail, Y.; Mostafa, H. An accurate model of domain-wall-based spintronic memristor. Integration 2019, 65, 149–162. [Google Scholar] [CrossRef]

- Chen, Y.; Wang, X. Compact modeling and corner analysis of spintronic memristor. In Proceedings of the IEEE/ACM International Symposium on Nanoscale Architectures, San Francisco, CA, USA, 30–31 July 2009; pp. 7–12. [Google Scholar]

- Luo, S.; Xu, N.; Guo, Z.; Zhang, Y.; Hong, J.; You, L. Voltage-controlled skyrmion memristor for energy-efficient synapse applications. IEEE Electron Dev. Lett. 2019, 40, 635–638. [Google Scholar] [CrossRef]

- Berger, L. Exchange interaction between ferromagnetic domain wall and electric current in very thin metallic films. J. Appl. Phys. 1984, 55, 1954–1956. [Google Scholar] [CrossRef]

- Camley, E.; Barnaś, J. Theory of giant magnetoresistance effects in magnetic layered structures with antiferromagnetic couplin g. Phys. Rev. Lett. 1989, 63, 664–667. [Google Scholar] [CrossRef] [PubMed]

- Baker, R.J. CMOS: Circuit Design, Layout, and Simulation; John Wiley & Son: Hoboken, NJ, USA, 2019. [Google Scholar]

| *Spintronic Memristor |

|---|

| .SUBCKT Spintronic memristor Plus Minus Flux Charge PARAMS: +D=1000E-9 h=70E-10 z=10E-9 rl=4E9 rh=6E9 Jcr=5E11 Taov=1.3517E-11 ******* Differential equation modeling******* Gx 0 x value={if(abs(I(Emem)/(h*z))<Jcr,0,Taov*I(Emem)/(h*z))} Cx x 0 1 IC={0} Raux x 0 1T ******* Resistive port of the memristor******* Emem plus aux value={if(V(x)<=D, I(Emem)*V(x)*(rh-rl), I(Emem)*D*(rh-rl))} RH aux minus {rl*D}*******Flux computation ******* Eflux flux 0 value={SDT(V(plus, minus))} *******Charge computation ******* Echarge charge 0 value={SDT(I(Emem))} .ENDS spintronic memristor |

| Truth Table 1 | Writing Operation | Reading Operation | |||||||

|---|---|---|---|---|---|---|---|---|---|

| In1 | In2 | Out | Cases | V1 | V2 | Rs1 | Cases | Vout | Logic |

| 0 | 0 | 2 | Case c | VL | VL | RSH | Case I | VH | 2 |

| 1 | 0 | 2 | Case e | VMid | VL | RSH | Case I | VH | 2 |

| 2 | 0 | 2 | Case d | VH | VL | RSH | Case I | VH | 2 |

| 0 | 1 | 2 | Case e | VL | VMid | RSH | Case I | VH | 2 |

| 1 | 1 | 1 | Case b | VMid | VMid | RMid | Case II | VMid | 1 |

| 2 | 1 | 1 | Case f | VH | VMid | RMid | Case II | VMid | 1 |

| 0 | 2 | 2 | Case d | VL | VH | RSH | Case I | VH | 2 |

| 1 | 2 | 1 | Case f | VMid | VH | RMid | Case II | VMid | 1 |

| 2 | 2 | 0 | Case a | VH | VH | RSL | Case III | VL | 0 |

| Logic Functions | Truth Table | Initialization | Writing Operation | Reading Operation | |||||

|---|---|---|---|---|---|---|---|---|---|

| Input | Output | M1 (M2) | Ms1 | V1 | V2 | Rs1 | Vout | Logic 1 | |

| AND | 0 0 | 0 | RH | RMid | VL | VL | RSL | VL | 0 |

| 1 0 | 0 | RH | RMid | VMid | VL | RSL | VL | 0 | |

| 2 0 | 0 | RH | RMid | VH | VL | RSL | VL | 0 | |

| 1 1 | 1 | RH | RMid | VMid | VMid | RMid | VMid | 1 | |

| 2 1 | 1 | RH | RMid | VH | VMid | RMid | VMid | 1 | |

| 2 2 | 2 | RH | RMid | VH | VH | RSH | VH | 2 | |

| OR | 0 0 | 0 | RH | RMid | VL | VL | RSL | VL | 0 |

| 1 0 | 1 | RH | RMid | VMid | VL | RMid | VMid | 1 | |

| 2 0 | 2 | RH | RMid | VH | VL | RSH | VH | 2 | |

| 1 1 | 1 | RH | RMid | VMid | VMid | RMid | VMid | 1 | |

| 2 1 | 2 | RH | RMid | VH | VMid | RSH | VH | 2 | |

| 2 2 | 2 | RH | RMid | VH | VH | RSH | VH | 2 | |

| NOR | 0 0 | 2 | RH | RMid | VL | VL | RSH | VH | 2 |

| 1 0 | 1 | RH | RMid | VMid | VL | RMid | VMid | 1 | |

| 2 0 | 0 | RH | RMid | VH | VL | RSL | VL | 0 | |

| 1 1 | 1 | RH | RMid | VMid | VMid | RMid | VMid | 1 | |

| 2 1 | 0 | RH | RMid | VH | VMid | RSL | VL | 0 | |

| 2 2 | 0 | RH | RMid | VH | VH | RSL | VL | 0 | |

| Items | Method 1 1 | Method 2 | Method 3 | Method 4 | Method 5 | Method 6 |

|---|---|---|---|---|---|---|

| Circuit Structure | Fixed | Unfixed | Unfixed | Unfixed | Unfixed | Unfixed |

| Input and Output | Voltage | Voltage | Voltage | Voltage | Memristance | Memristance |

| Load Capacity | Sufficient | Sufficient | Sufficient | Sufficient | Insufficient | Insufficient |

| Cascaded Capacity | Good | Good | Good | Good | Not good | Not good |

| Initialization | Needed | Unneeded | Unneeded | Needed | Needed | Needed |

| Robustness | Strong | Median | Median | Median | Strong | Strong |

| Functionality | Strong | Median | Median | Strong | Strong | Strong |

| Device Parameters 1 | Stimulation Parameters | Constraint Conditions |

|---|---|---|

| rH = 8 × 109 Ω/m; rL = 4 × 109 Ω/m | VH = 7.0 V | |Vread| ≤ RSH·Icr2 |

| rSH = 16 × 1010 Ω/m; rSL = 4 × 1010 Ω/m | VMid = 3.0 V | |0.5·Vread| ≤ RMid·Icr2 |

| Jcr1 = 5 × 1011; Jcr2 = 2.5 × 1011; | VL = 0 V | |VH − Vc| > RMid·Icr2 |

| H = 7 × 10−9 m; z = 10 × 10−9 m | VC = 3.0 V | |VMid − Vc| ≤ RMid·Icr2 |

| Γv = 1.3517 × 10−11; D = 10 × 10−6 m | Vread = 2.5 V | RSH·Icr2 ≤ |Vc − VL| |

| RMid = Rs1 = 100 kΩ | T = 160 ns | |VMid| > RL· Icr |

| Rs2 = Rs3 = 10 Ω | / | |VH − VMid | > RL·Icr |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, H.; Zhang, Z.; Gao, M.; Luo, L.; Duan, S.; Dong, Z.; Lin, H. Implementation of Unbalanced Ternary Logic Gates with the Combination of Spintronic Memristor and CMOS. Electronics 2020, 9, 542. https://doi.org/10.3390/electronics9040542

Zhang H, Zhang Z, Gao M, Luo L, Duan S, Dong Z, Lin H. Implementation of Unbalanced Ternary Logic Gates with the Combination of Spintronic Memristor and CMOS. Electronics. 2020; 9(4):542. https://doi.org/10.3390/electronics9040542

Chicago/Turabian StyleZhang, Haifeng, Zhaowei Zhang, Mingyu Gao, Li Luo, Shukai Duan, Zhekang Dong, and Huipin Lin. 2020. "Implementation of Unbalanced Ternary Logic Gates with the Combination of Spintronic Memristor and CMOS" Electronics 9, no. 4: 542. https://doi.org/10.3390/electronics9040542

APA StyleZhang, H., Zhang, Z., Gao, M., Luo, L., Duan, S., Dong, Z., & Lin, H. (2020). Implementation of Unbalanced Ternary Logic Gates with the Combination of Spintronic Memristor and CMOS. Electronics, 9(4), 542. https://doi.org/10.3390/electronics9040542