Multiple Modulation Strategy of Flying Capacitor DC/DC Converter

Abstract

:1. Introduction

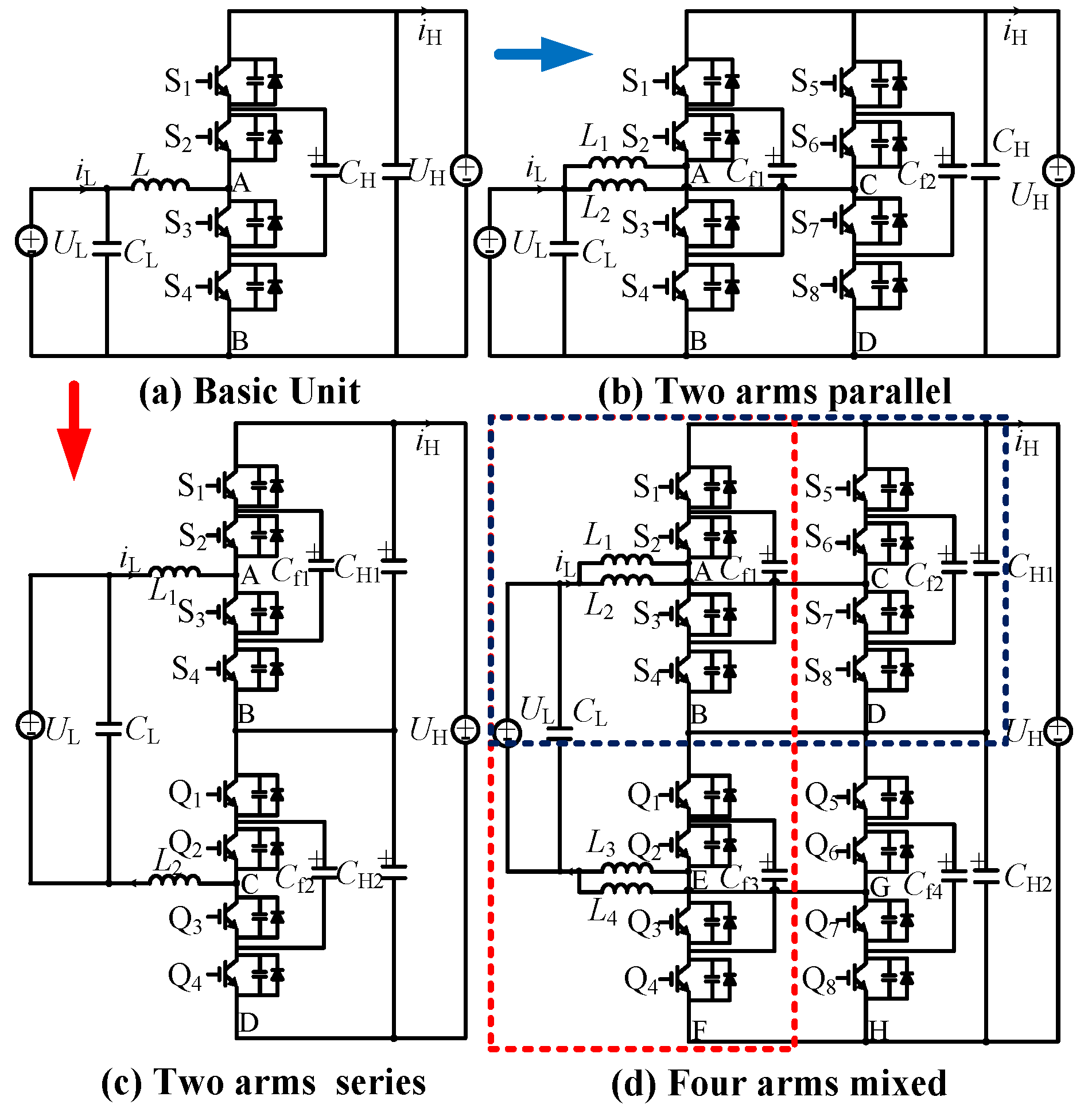

2. Flying Capacitor Type Three-level DC-DC Basic Unit

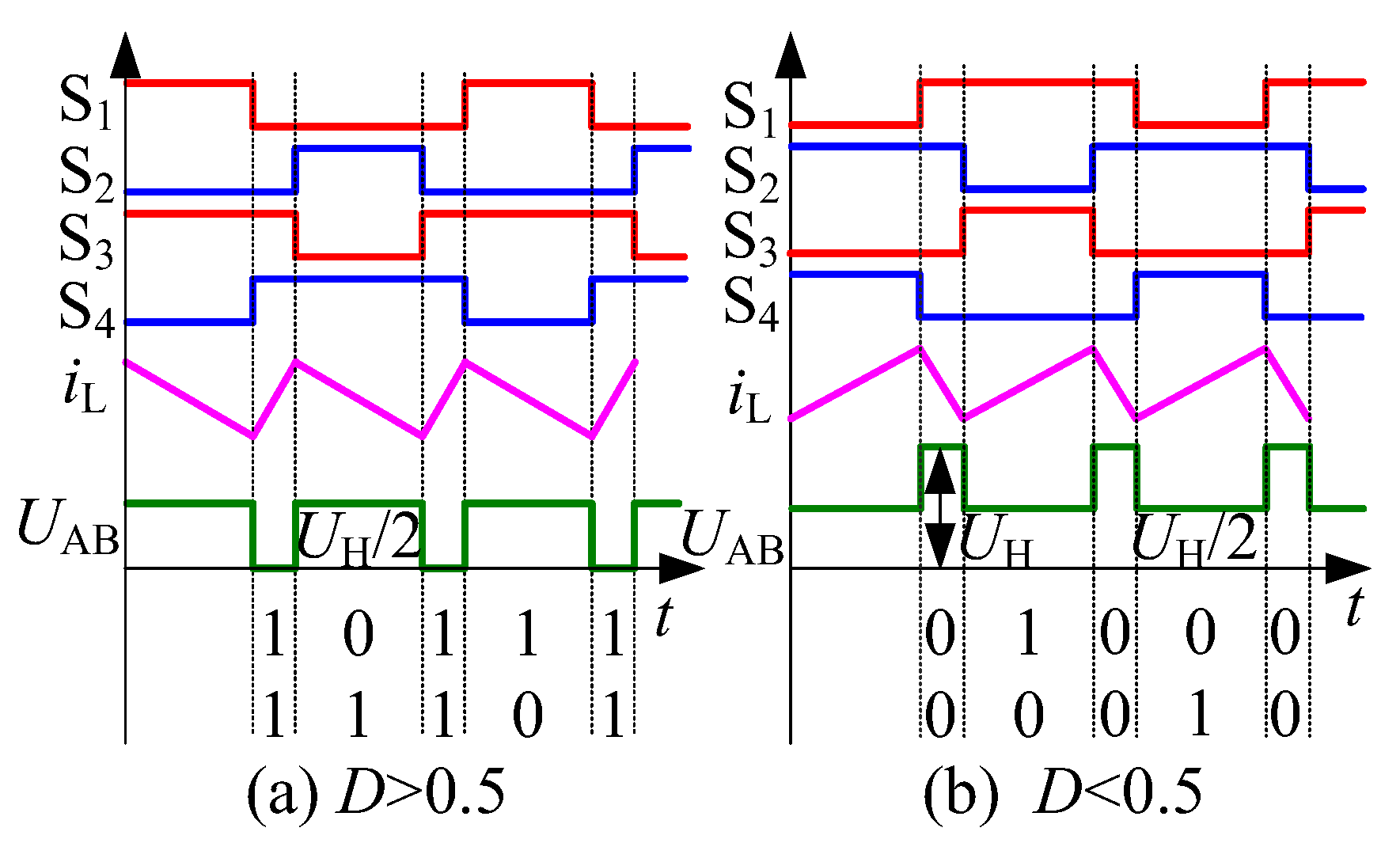

2.1. Operational Modal Analysis D > 0.5

- Mode M3 = 11, S1 and S2 are turned off, S3 and S4 are turned on, S1 and S2 voltage stress are UH/2, the voltage of AB two-point is UAB = 0, the inductor voltage across L1 is UL, and iL flows to the high-voltage side and linearly increases:

- Mode M1 = 01, S1 and S3 turn off, S2 and S4 turn on, the S1 and S3 voltage stresses are UH/2, the flying capacitor Cf1 charge according to the differential equation Cf1 dUf1/dt = Ic, that is ΔUf1=t2Ic/Cf1 = Qc/Cf1, UAB = Uf1 = UH/2, the inductor L1 is UL - UAB < 0, the inductor current iL decreases linearly, and the average inductor current is IL = Ic.

- Mode M3 = 11, S1 and S2 are turned off, S3 and S4 are turned on, the S1 and S2 voltage stresses are UH/2, the voltage of the two-point of AB is UAB=0, the voltage of the inductance L1 is UL, and iL flows to high voltage side and linearly increase, as shown in Equation (2).

- Mode M2 = 10, S2 and S4 are turned off, S1 and S3 are turned on, the S2 and S4 voltage stresses are UH/2, flying capacitor Cf1 is discharged, UAB = UH − Uf1 = UH/2, the voltage across inductor L1 is UL − UAB < 0, and iL flows to the high-pressure side and decreases linearly. The column differential equation can be obtained as:

2.2. Operational Modal Analysis D < 0.5

- Mode M0 = 00, S3 and S4 are turned off, S1 and S2 are turned on, the voltage of AB is UAB = UH, S3 and S4 voltage stress are UH/2, the voltage of inductance L1 is UL − UH, iL flows to the high-voltage side and decreases linearly, and the corresponding differential equation can be expressed as:

- Mode M2 = 10, S2 and S4 are turned off, S1 and S3 are turned on, S2 and S4 voltage stress are UH/2, Cf1 is discharging, UAB = UH − Uf1 = UH/2, the voltage across inductor L1 is UL − UAB>0, iL flows to the high-voltage side and increases linearly, and the differential equation can be expressed as Equation (4).

- Mode M0 = 00, S3 and S4 are turned off, S1 and S2 are turned on, the voltage of AB is UAB = UH, S3 and S4 voltage stress are UH/2, inductance L1 voltage is UL − UH, iL flow to high voltage side and the linearity is reduced, and the differential equation can be expressed as Equation (7).

- Mode M1 = 01, S1 and S3 are turned off, S2 and S4 are turned on, S1 and S3 voltage stresses are UH/2, flying capacitor Cf1 is charging, UAB = Uf1 = UH/2, the inductor voltage across L1 is UL − UAB > 0, iL flows to the high-voltage side and increases linearly, and the differential equation can be expressed as Equation (3). According to the duty cycle definition, each mode action time can be expressed as:

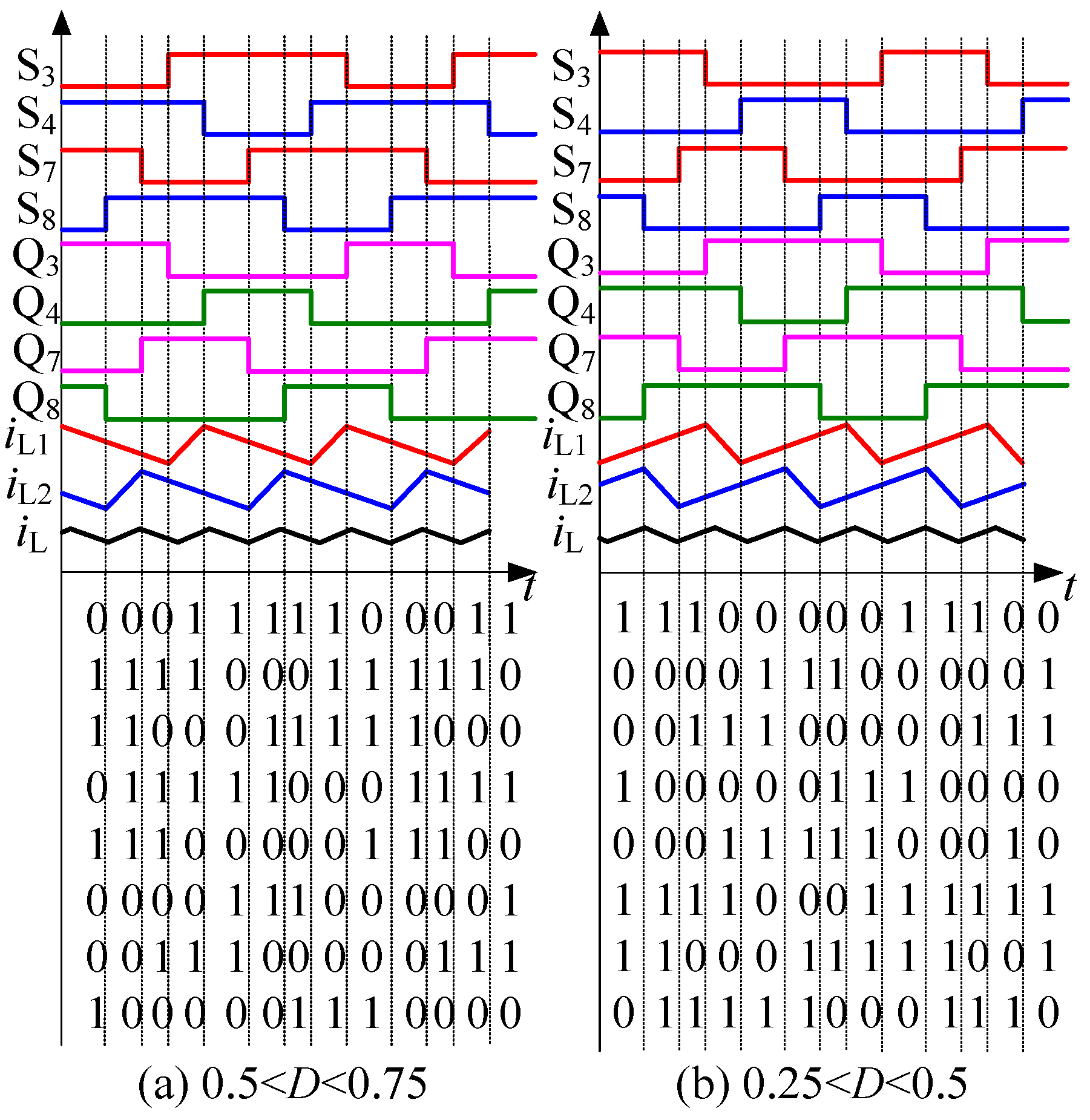

3. Multiple Modulation Technique

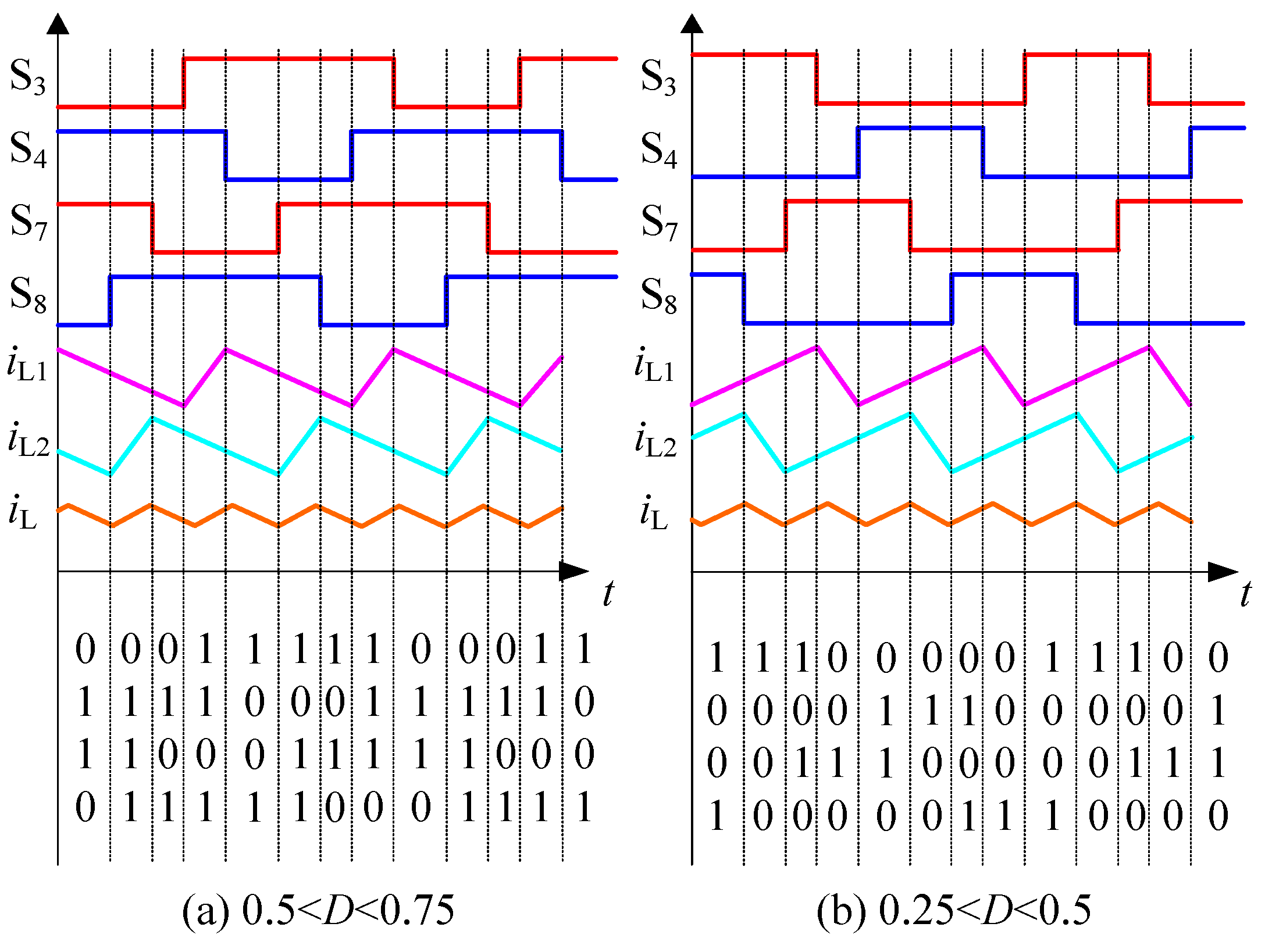

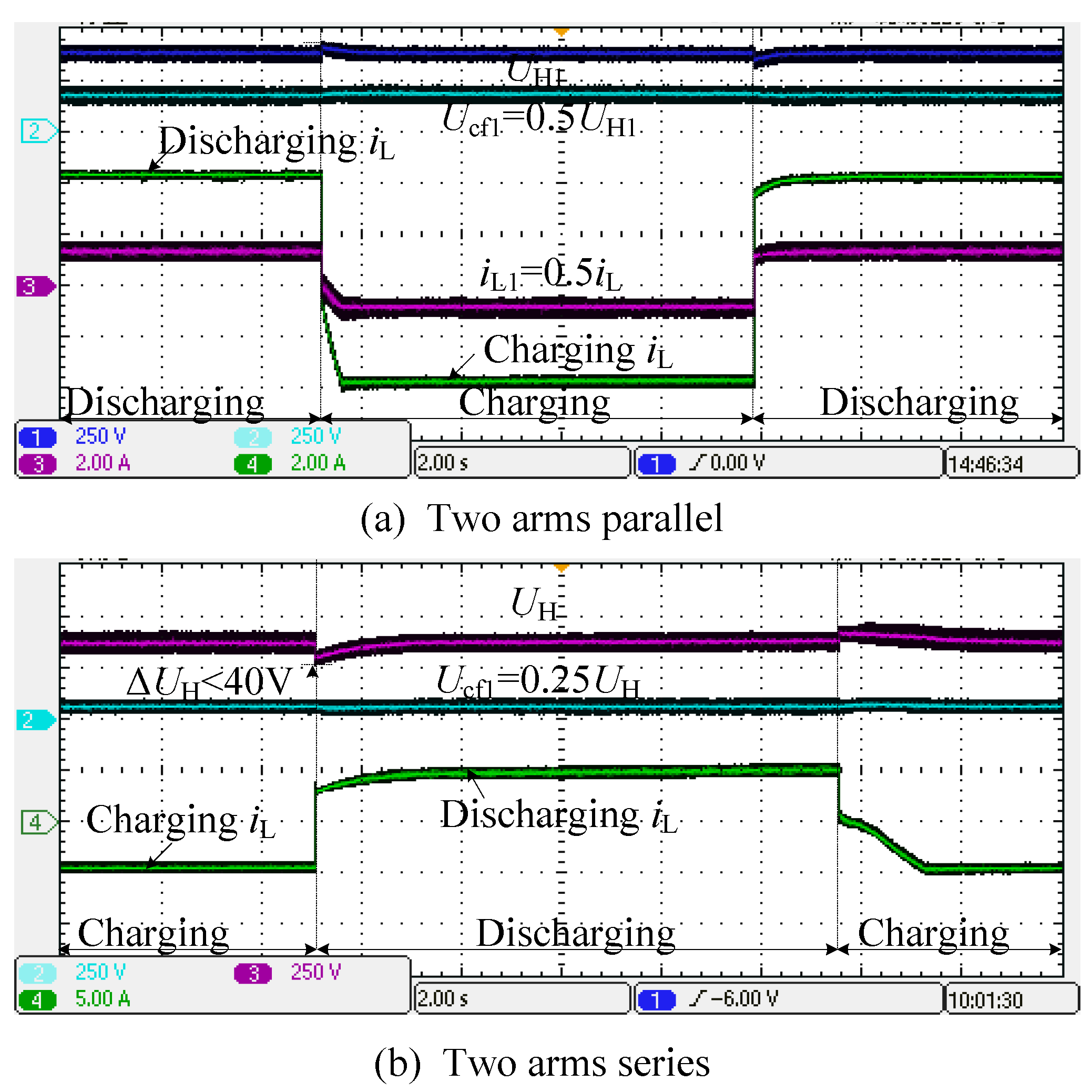

3.1. Two Arms Interleaved Parallel Modulation

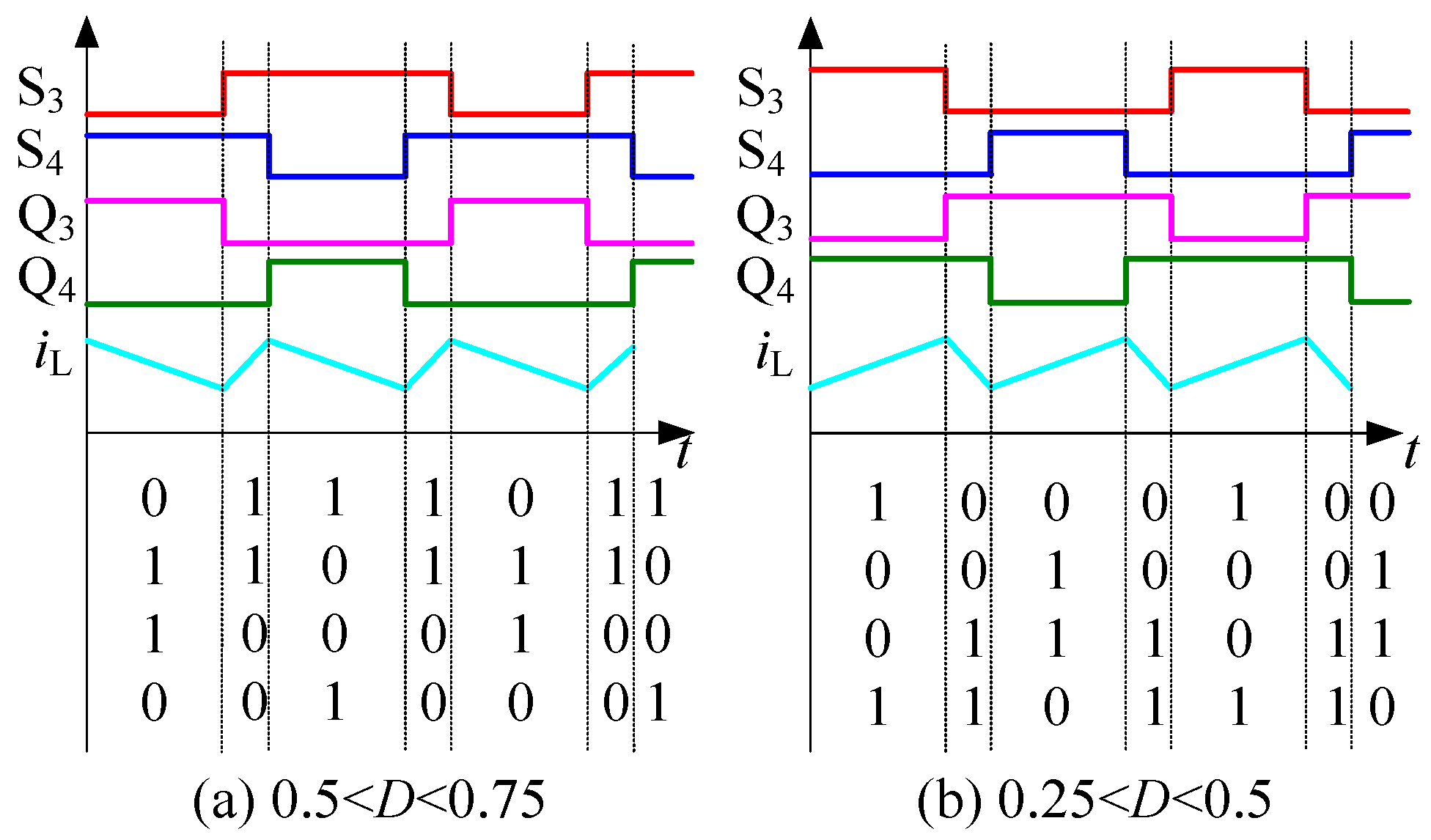

3.2. Two Arms Complementary Series Modulation

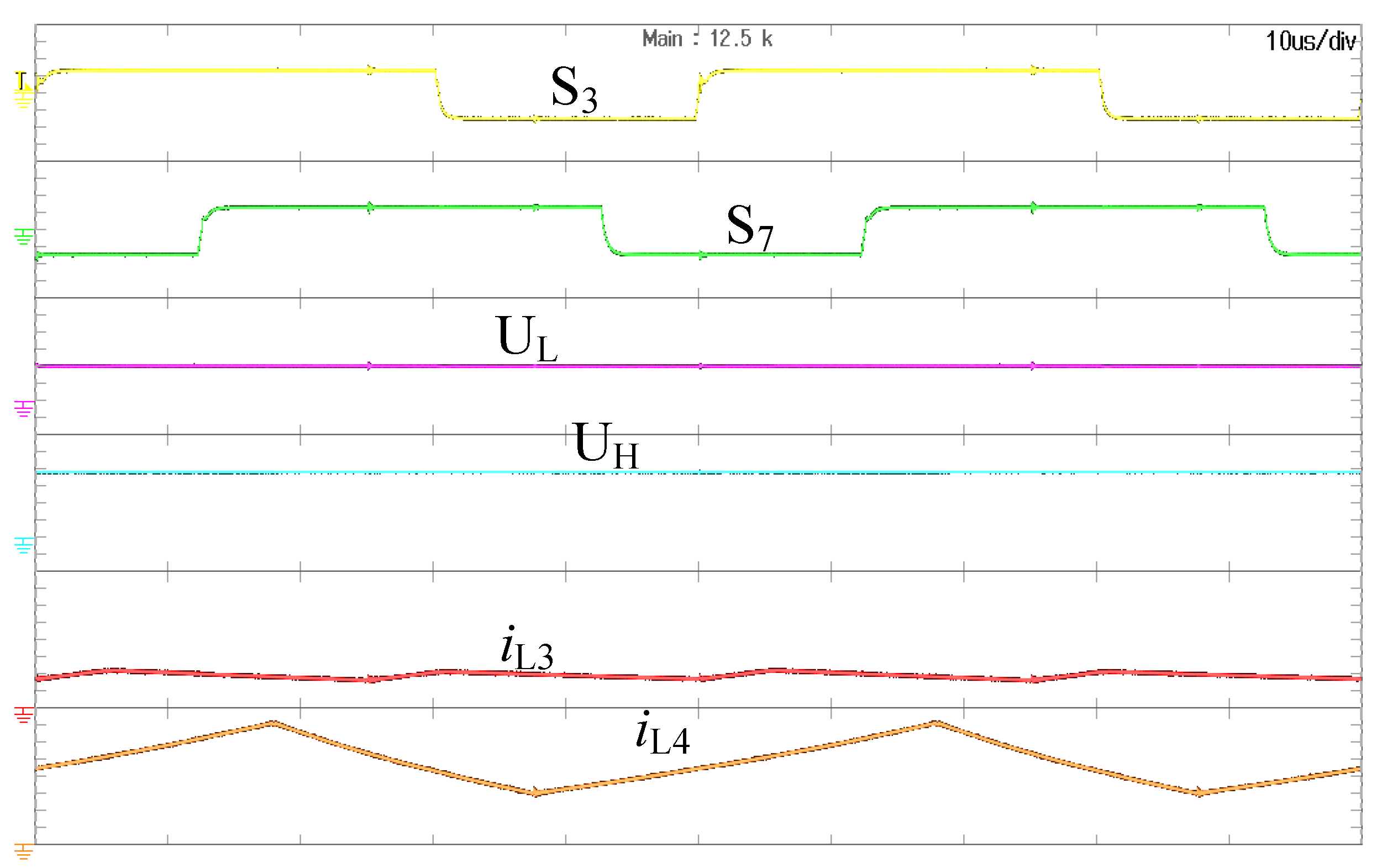

3.3. Four Arms Mixed Modulation

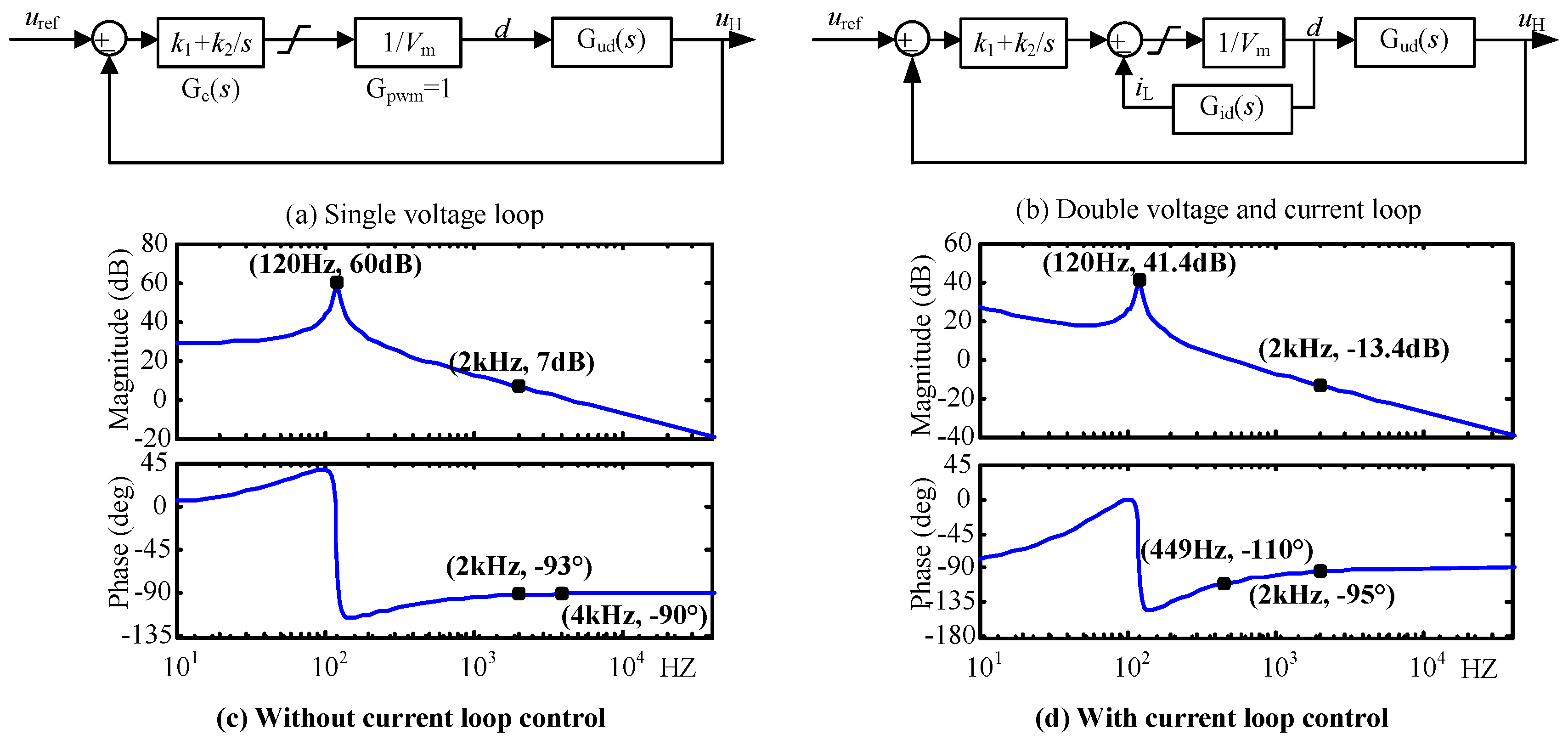

4. Controller design

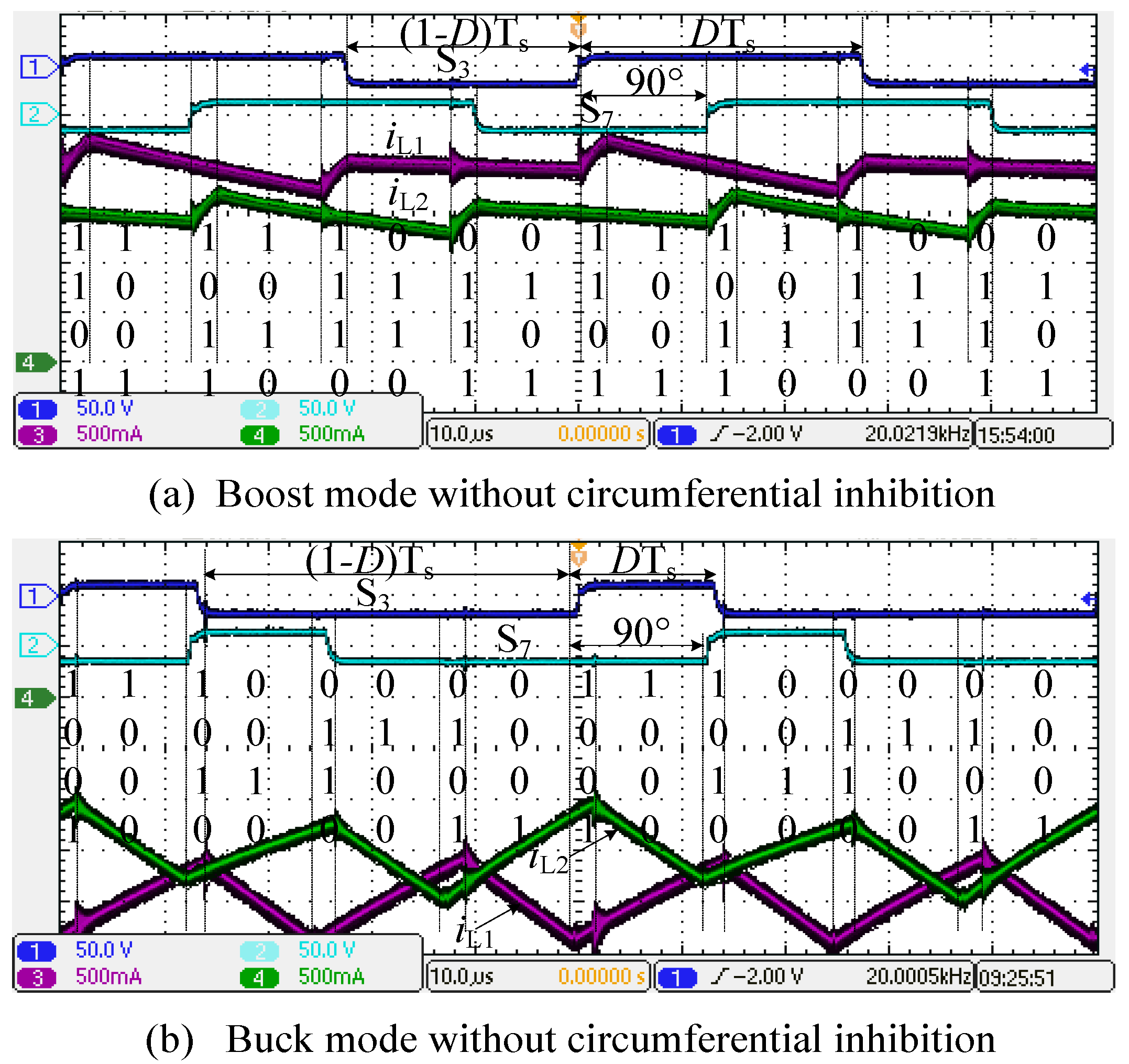

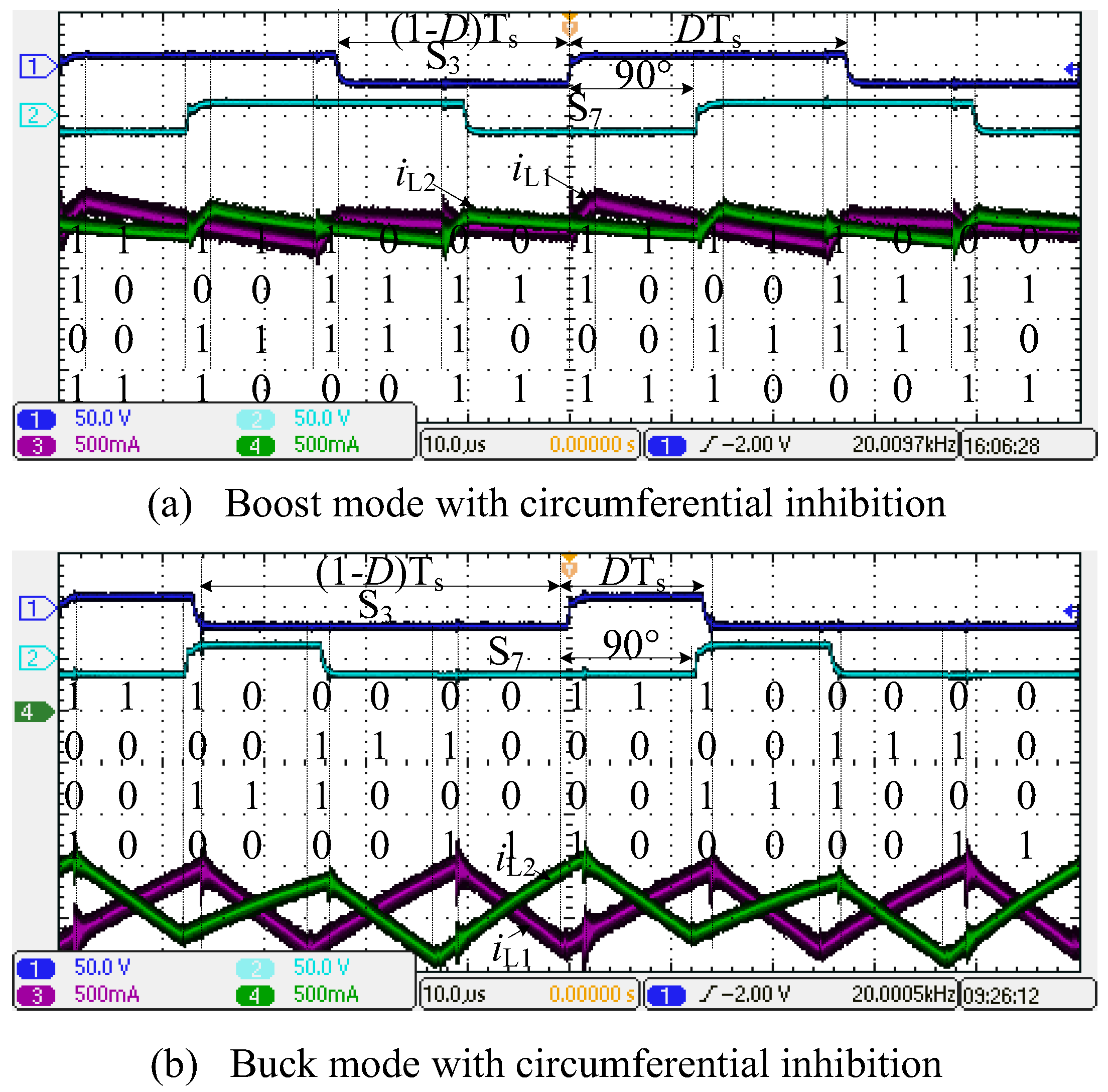

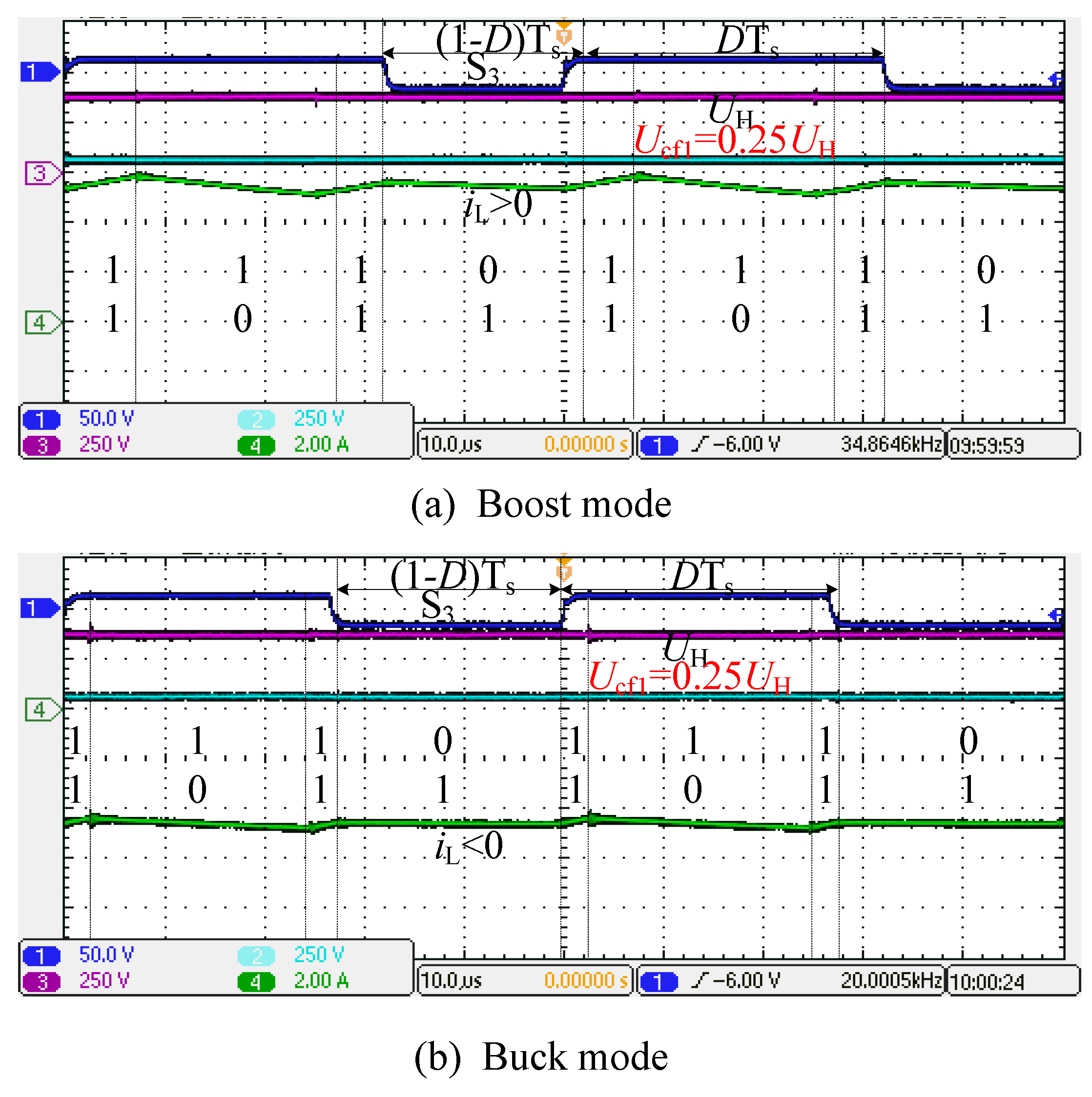

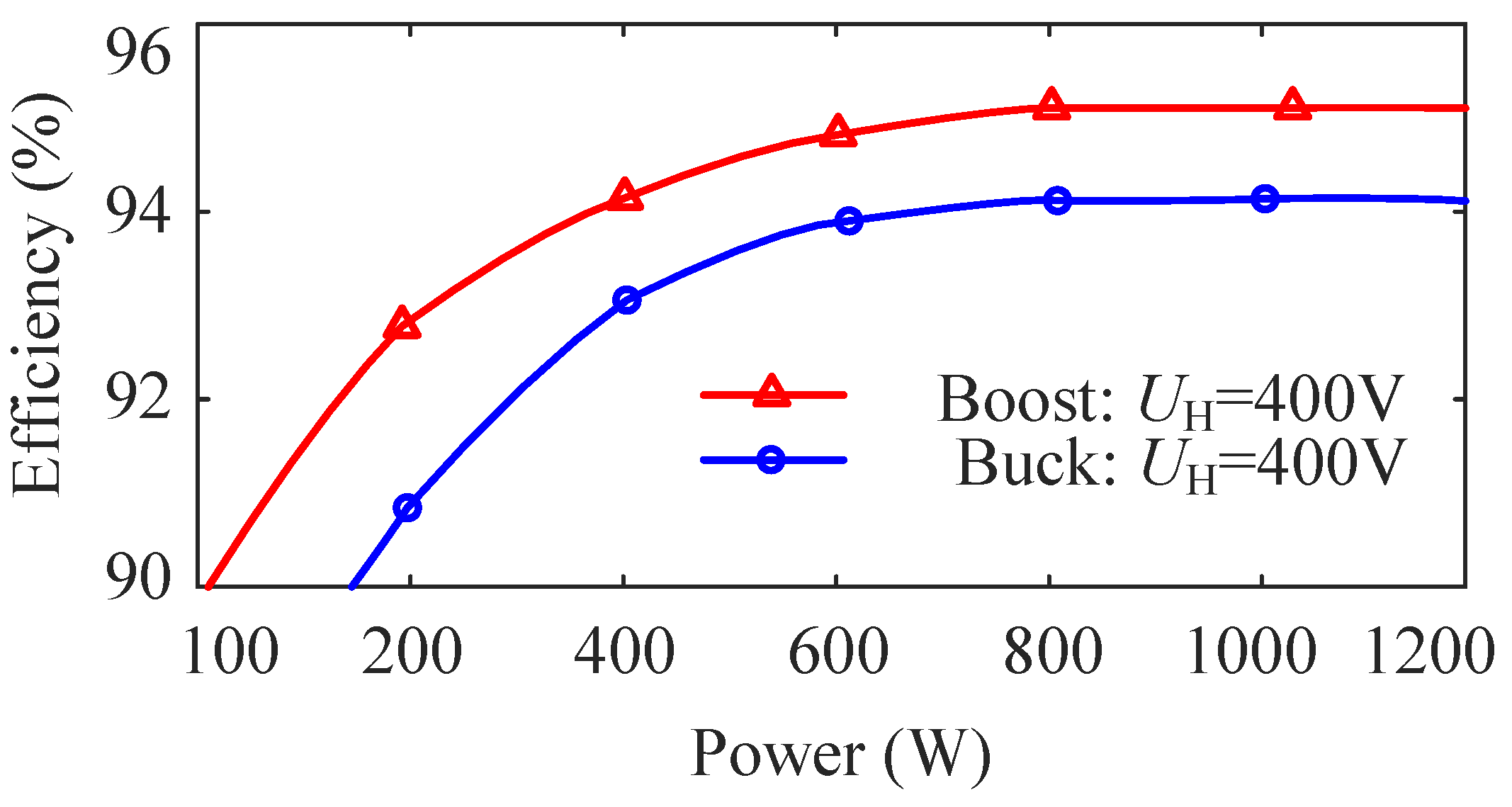

5. Experimental result

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ji, Y.; Yang, Y.; Zhou, J.; Ding, H.; Guo, X.; Padmanaban, S. Control Strategies of Mitigating Dead-time Effect on Power Converters: An Overview. Electronics 2019, 8, 196. [Google Scholar] [CrossRef]

- Guo, X.; Jia, X. Hardware-based cascaded topology and modulation strategy with leakage current reduction for transformerless PV systems. IEEE Trans. Ind. Electron. 2016, 62, 7823–7832. [Google Scholar] [CrossRef]

- Guo, X.; Yang, R.Y.; He, R.; Wang, B.; Blaabjerg, F. Transformerless Z-source four-leg PV inverter with leakage current reduction. IEEE Trans. Power Electron. 2019, 34, 4343–4352. [Google Scholar] [CrossRef]

- Mahmoudi, M.A.H.; Ahmadi, R. Modulated model predictive control of three level flying capacitor buck converter. In Proceedings of the IEEE Power and Energy Conference at Illinois (PECI), Champaign, IL USA, 23–24 February 2017; pp. 1–5. [Google Scholar]

- Jin, K.; Yang, M.; Ruan, X.; Xu, M. Three-Level Bidirectional Converter for Fuel-Cell/Battery Hybrid Power System. IEEE Trans. Ind. Electron. 2010, 57, 1976–1986. [Google Scholar] [CrossRef]

- Zhang, C.; Li, P.; Kan, Z.; Chai, X.; Guo, X. Integrated Half Bridge CLLC Bidirectional Converter for Energy Storage Systems. IEEE Trans. Ind. Electron. 2018, 65, 3879–3889. [Google Scholar] [CrossRef]

- Li, P.; Zhang, C.; Kan, Z.; Fu, Y. An Interleaving 90° Three-Level DC-DC Converter and Current Sharing Control. In Proceedings of the 2nd IEEE International Power Electronics and Application Conference and Exposition, Shenzhen, China, 4–7 November 2018. [Google Scholar]

- Dragičević, T.; Guerrero, J.M.; Vasquez, J.C.; Škrlec, D. Supervisory Control of an Adaptive-Droop Regulated DC Microgrid with Battery Management Capability. IEEE Trans. Power Electron. 2014, 29, 695–706. [Google Scholar] [CrossRef]

- Huang, X.; Lee, F.C.; Li, Q.; Du, W. High-Frequency High-Efficiency GaN-Based Interleaved CRM Bidirectional Buck/Boost Converter with Inverse Coupled Inductor. IEEE Trans. Power Electron. 2016, 31, 4343–4352. [Google Scholar] [CrossRef]

- Xiao, G.; Zhou, J.; He, R.; Jia, X.; Rojas, C.A. Leakage current attenuation of a three-phase cascaded inverter for transformerless grid-connected pv systems. IEEE Trans. Ind. Electron. 2018, 65, 676–686. [Google Scholar]

- Chen, W.; Ruan, X.; Yan, H.; Tse, C.K. DC/DC Conversion Systems Consisting of Multiple Converter Modules: Stability, Control, and Experimental Verifications. IEEE Trans. Power Electron. 2009, 24, 1463–1474. [Google Scholar] [CrossRef]

- Jin, L.; Liu, B.Y.; Duan, S.X. ZVS Operation Range Analysis of Three-Level Dual Active Bridge DC-DC Converter with Phase-Shift Control. In Proceedings of the 2017 Thirty Second Annual IEEE Applied Power Electronics Conference and Exposition (Apec), Tampa, FL, USA, 26–30 March 2017. [Google Scholar]

- Wang, Y.; Yuan, Z.; Fu, J.; Li, Y.; Zhao, Y. A feasible coordination protection strategy for MMC-MTDC systems under DC faults. Int. J. Electr. Power Energy Syst. 2017, 90, 103–111. [Google Scholar] [CrossRef]

- Kakigano, H.; Miura, Y.; Ise, T. Low-Voltage Bipolar-Type DC Microgrid for Super High-Quality Distribution. IEEE Trans. Power Electron. 2010, 25, 3066–3075. [Google Scholar] [CrossRef]

- Xiao, G.; Yang, Y.; Wang, B.; Blaabjerg, F. Leakage Current Reduction of Three-phase Z-source three-level four-leg inverter for transformerless PV system. IEEE Trans. Power Electron. 2019, 34, 6299–6308. [Google Scholar]

- Dusmez, S.; Khaligh, A.; Hasanzadeh, A. A Zero-Voltage-Transition Bidirectional DC/DC Converter. IEEE Trans. Ind. Electron. 2015, 62, 3152–3162. [Google Scholar] [CrossRef]

- Guo, Z.; Chai, X.; Li, P.; Zhang, C. A new balance control method of three-level converter NPP. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Piscataway, NJ, USA, 22–26 May 2016; pp. 2356–2361. [Google Scholar]

- Singh, S.N. Selection of non-isolated DC-DC converters for solar photovoltaic system. Renew. Sustain. Energy Rev. 2017, 76, 1230–1247. [Google Scholar]

- Do, H.L. A Soft-Switching DC/DC Converter with High Voltage Gain. IEEE Trans. Power Electron. 2010, 25, 1193–1200. [Google Scholar]

- Zhang, X.S.; Yuan, Y.; Hua, L.; Cao, Y.; Qian, K.J. On Generation Schedule Tracking of Wind Farms with Battery Energy Storage Systems. IEEE Trans. Sustain. Energy 2017, 8, 341–353. [Google Scholar] [CrossRef]

- Naderi, R.; Sadigh, A.K.; Smedley, K.M. Dual Flying Capacitor Active-Neutral-Point-Clamped Multilevel Converter. IEEE Trans. Power Electron. 2016, 31, 6476–6484. [Google Scholar] [CrossRef]

- Mohammadi, F. Power Management Strategy in Multi-Terminal VSC-HVDC System. In Proceedings of the 4th National Conference on Applied Research in Electrical, Mechanical, Computer and IT Engineering, Tehran, Iran, 5 January 2018. [Google Scholar]

- Uno, M. High Step-Down Converter Integrating Switched Capacitor Converter and PWM Synchronous Buck Converter. In Proceedings of the 35th International Telecommunications Energy Conference, Hamburg, Germany, 13–17 October 2013. [Google Scholar]

- Li, X.; Zhang, W.; Li, H.; Xie, R.; Xu, D. Design and control of bi-directional DC/DC converter for 30kW fuel cell power system. In Proceedings of the 8th International Conference on Power Electronics-ECCE Asia, Jeju, Korea, 30 May–3 June 2011; pp. 1024–1030. [Google Scholar]

| 0~0.25 | D = 0.25 | 0.25~0.5 | D = 0.5 | 0.5~0.75 | D = 0.75 | 0.75~1 |

|---|---|---|---|---|---|---|

| 0000 | 0010 | 1010 | 1010 | 0101 | 1101 | 1111 |

| 0010 | 0010 | 0010 | 1010 | 1101 | 1101 | 1101 |

| 0000 | 0100 | 0110 | 0110 | 1001 | 1011 | 1111 |

| 0100 | 0100 | 0100 | 0110 | 1011 | 1011 | 1011 |

| 0000 | 0001 | 0101 | 0101 | 1010 | 1110 | 1111 |

| 0001 | 0001 | 0001 | 0101 | 1110 | 1110 | 1110 |

| 0000 | 1000 | 1001 | 1001 | 0110 | 0111 | 1111 |

| 1000 | 1000 | 1000 | 1001 | 0111 | 0111 | 0111 |

| 0~0.25 | 0.25 | 0.25~0.5 | 0.5 | 0.5~0.75 | 0.75 | 0.75~1 |

|---|---|---|---|---|---|---|

| 00/11 | 00/11 | 00/11 | 01/10 | 11/00 | 11/00 | 11/00 |

| 01/10 | 01/10 | 01/10 | 10/01 | 10/01 | 10/01 | 10/01 |

| 00/11 | 00/11 | 00/11 | 01/10 | 11/00 | 11/00 | 11/00 |

| 10/01 | 10/01 | 10/01 | 10/01 | 01/10 | 01/10 | 01/10 |

| 0~0.25 | D = 0.25 | 0.25~0.5 | D = 0.5 | 0.5~0.75 | D = 0.75 | 0.75~1 |

|---|---|---|---|---|---|---|

| 0000/1111 | 0010/1101 | 1010/0101 | 1010/0101 | 0101/1010 | 1101/0010 | 1111/0000 |

| 0010/1101 | 0010/1101 | 0010/1101 | 1010/0101 | 1101/0010 | 1101/0010 | 1101/0010 |

| 0000/1111 | 0100/1011 | 0110/1001 | 0110/1001 | 1001/0110 | 1011/0100 | 1111/0000 |

| 0100/1011 | 0100/1011 | 0100/1011 | 0110/1001 | 1011/0100 | 1011/0100 | 1011/0100 |

| 0000/1111 | 0001/1110 | 0101/1010 | 0101/1010 | 1010/0101 | 1110/0001 | 1111/0000 |

| 0001/1110 | 0001/1110 | 0001/1110 | 0101/1010 | 1110/0001 | 1110/0001 | 1110/0001 |

| 0000/1111 | 1000/0111 | 1001/0110 | 1001/0110 | 0110/1001 | 0111/1000 | 1111/0000 |

| 1000/0111 | 1000/0111 | 1000/0111 | 1001/0110 | 0111/1000 | 0111/1000 | 0111/1000 |

| (a) Comparison in terms of passive component and out gain, inductor ripple current and switching frequency. | |||||

| Proposed | Number of Elements | Gain of Voltage | ΔiL | ||

| SC [23] | C = 3 S = 4 L = 1 | fs | |||

| Double Buck/Boost [24] | C = 3 S = 4 L = 2 | 2fs | |||

| Basic FC [5] | C = 3 S = 4 L = 1 | 2fs | |||

| Interleaved FC [7] | C = 4 S = 8 L = 2 | 4fs | |||

| Complementary FC [21] | C = 5 S = 8 L = 2 | 2fs | |||

| This paper | C = 7 S = 16 L = 4 | 4fs | |||

| (b) Comparison in terms of out capacitor, flying capacitor voltage, voltage across switch, inductor current and fault tolerant capabilities | |||||

| Proposed. | Output Capacitor Voltage | Flying capacitor voltage | Switch Voltage | Inductor Current | Fault Tolerance |

| SC [23] | 2 UL/(1-D) | 0.5 UH | 0.5 UH | IL | Weak |

| Double Buck/Boost [24] | UL/(1-D) | No | 0.5 UH | IL | Weak |

| Basic FC [5] | UL/(1-D) | 0.5 UH | 0.5 UH | IL | Weak |

| Interleaved FC [7] | UL/(1-D) | 0.5 UH | 0.5 UH | 0.5 IL | Average |

| Complementary FC [21] | UL/(2-2D) | 0.25 UH | 0.25 UH | IL | Average |

| This paper | UL/(2-2D) | 0.25 UH | 0.25 UH | 0.5 IL | Strong |

| Parameters | Value | Parameters | Value |

|---|---|---|---|

| UL/V | 150~220 | CL/μF | 220 |

| UH/V | 400 | CH/μF | 110 |

| Po/kW | 1 | Cf1/μF | 110 |

| L1~L2/mH | 2 | Cf2/μF | 110 |

| rL/Ω | 0.2 | fs/kHz | 20 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, P.; Zhang, C.; Padmanaban, S.; Zbigniew, L. Multiple Modulation Strategy of Flying Capacitor DC/DC Converter. Electronics 2019, 8, 774. https://doi.org/10.3390/electronics8070774

Li P, Zhang C, Padmanaban S, Zbigniew L. Multiple Modulation Strategy of Flying Capacitor DC/DC Converter. Electronics. 2019; 8(7):774. https://doi.org/10.3390/electronics8070774

Chicago/Turabian StyleLi, Pengcheng, Chunjiang Zhang, Sanjeevikumar Padmanaban, and Leonowicz Zbigniew. 2019. "Multiple Modulation Strategy of Flying Capacitor DC/DC Converter" Electronics 8, no. 7: 774. https://doi.org/10.3390/electronics8070774

APA StyleLi, P., Zhang, C., Padmanaban, S., & Zbigniew, L. (2019). Multiple Modulation Strategy of Flying Capacitor DC/DC Converter. Electronics, 8(7), 774. https://doi.org/10.3390/electronics8070774