A 30–40 GHz CMOS Receiver Front-End with 5.9 dB NF and 16.5 dB Conversion Gain for Broadband Spectrum Sensing Applications

Abstract

:1. Introduction

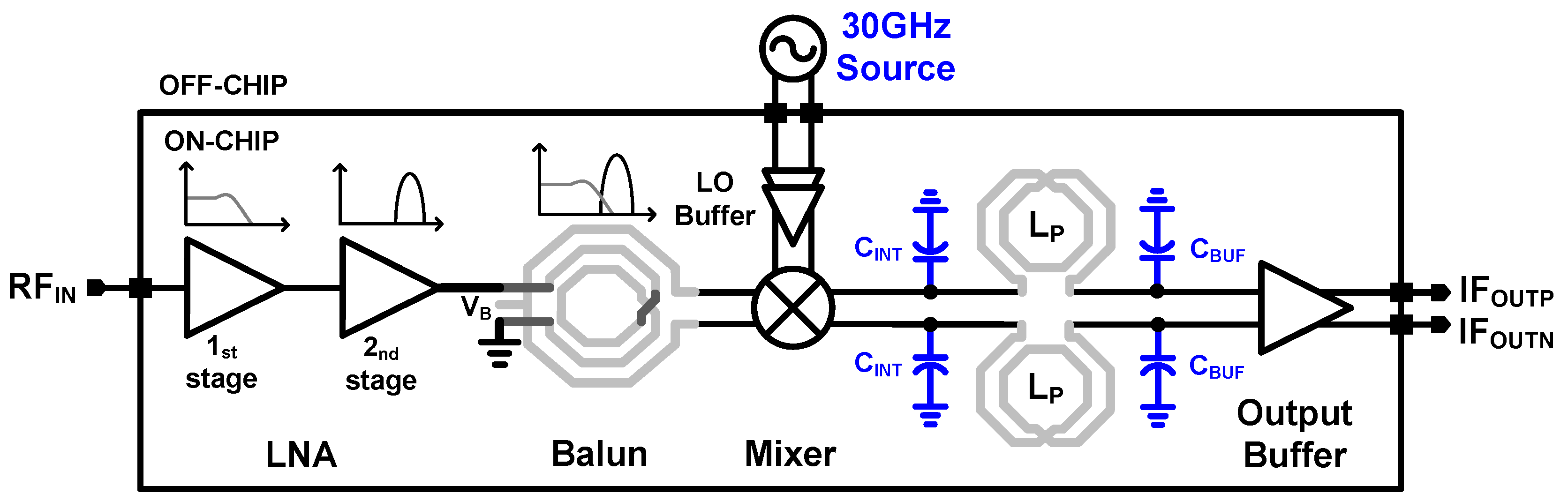

2. Overall RF Front-End System

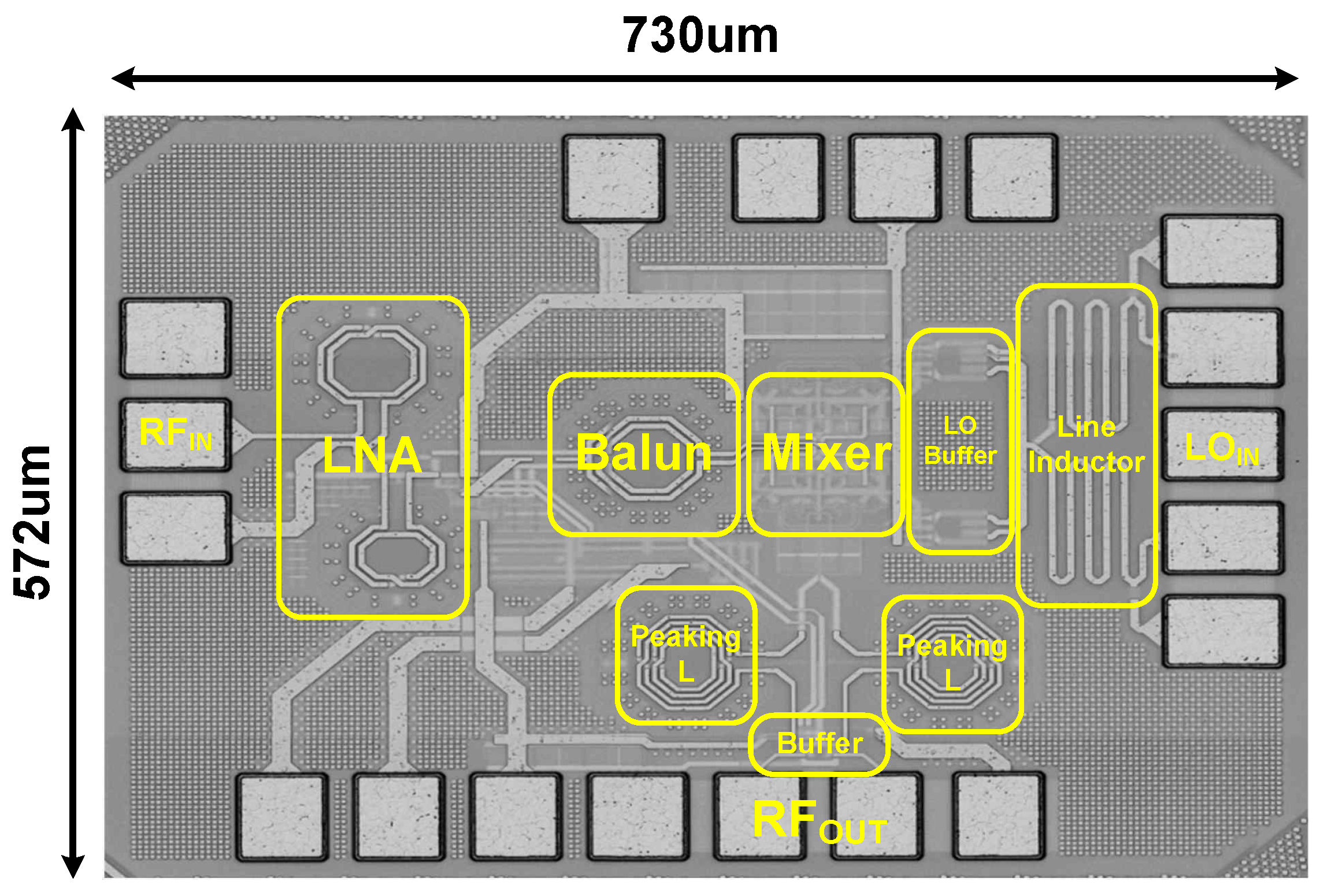

3. Building Blocks Designs

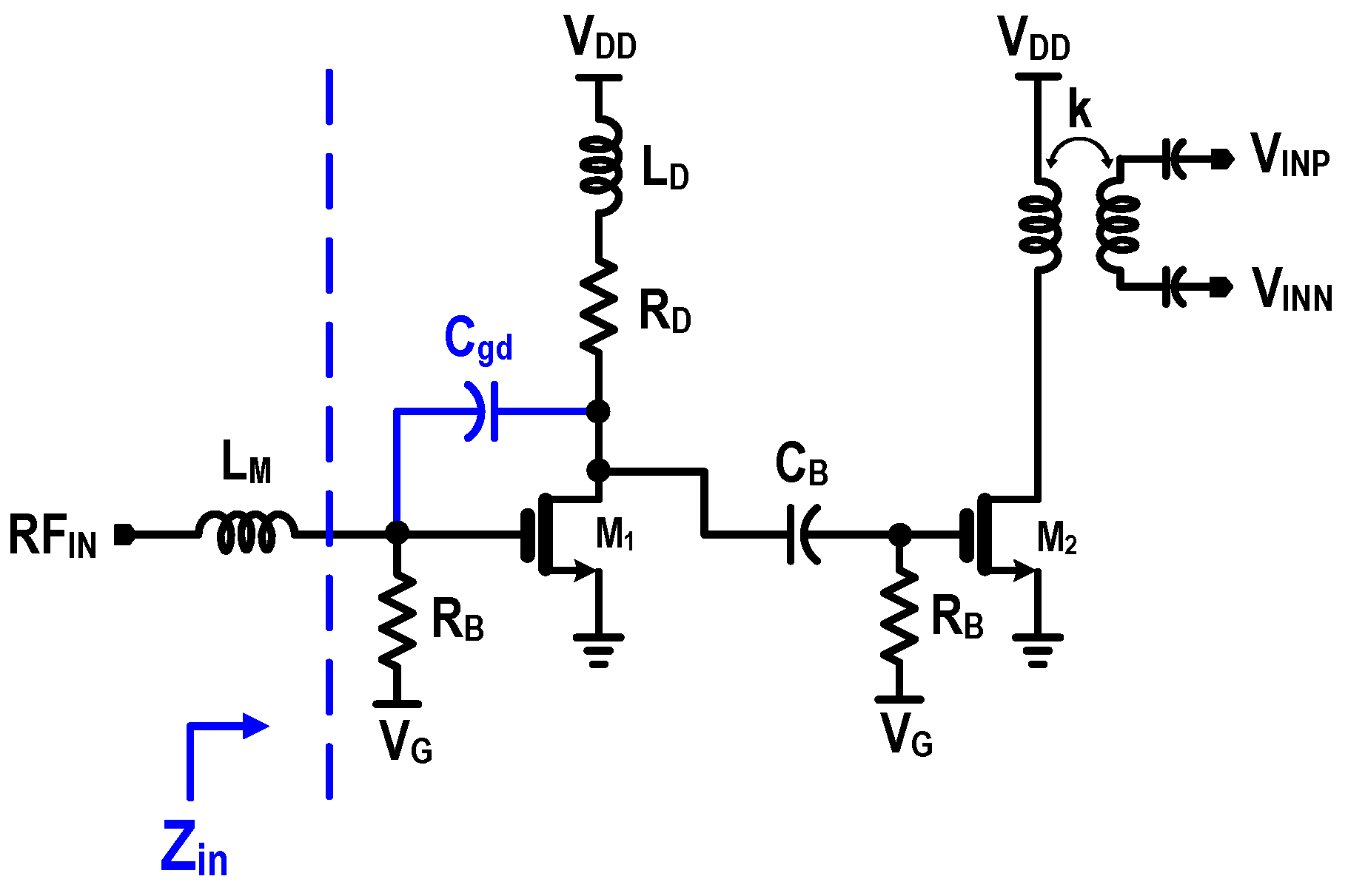

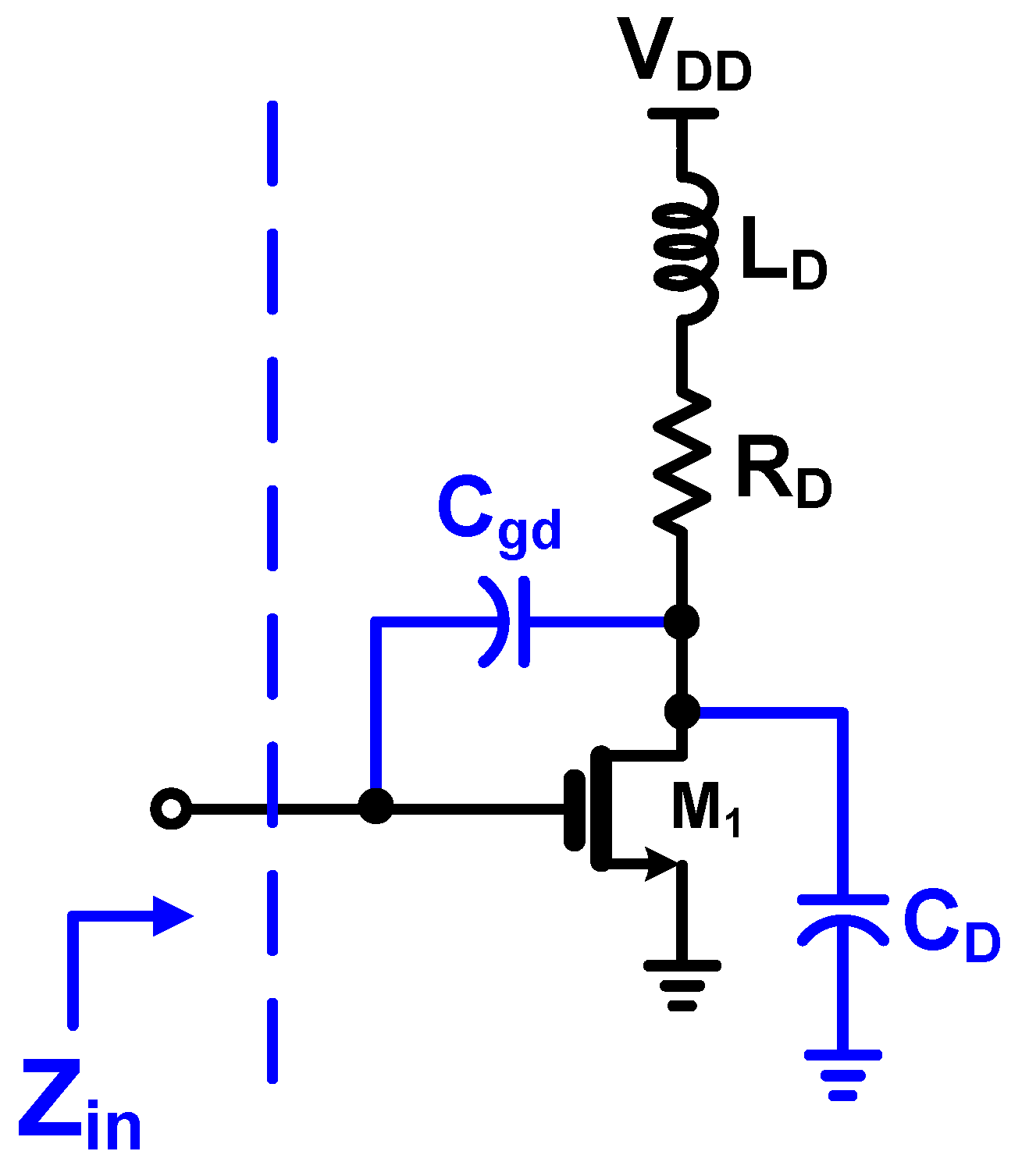

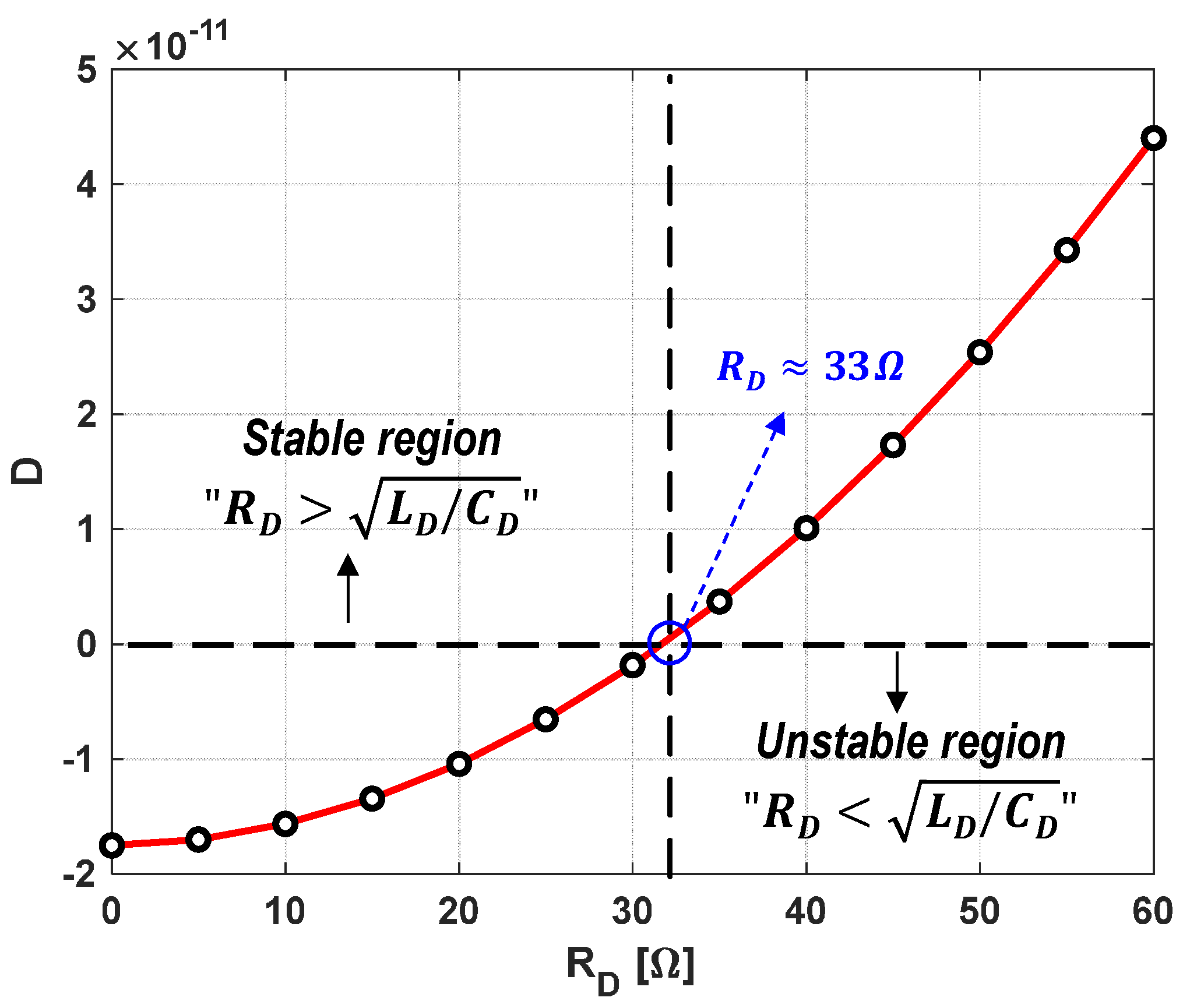

3.1. Low Noise Amplifier (LNA)

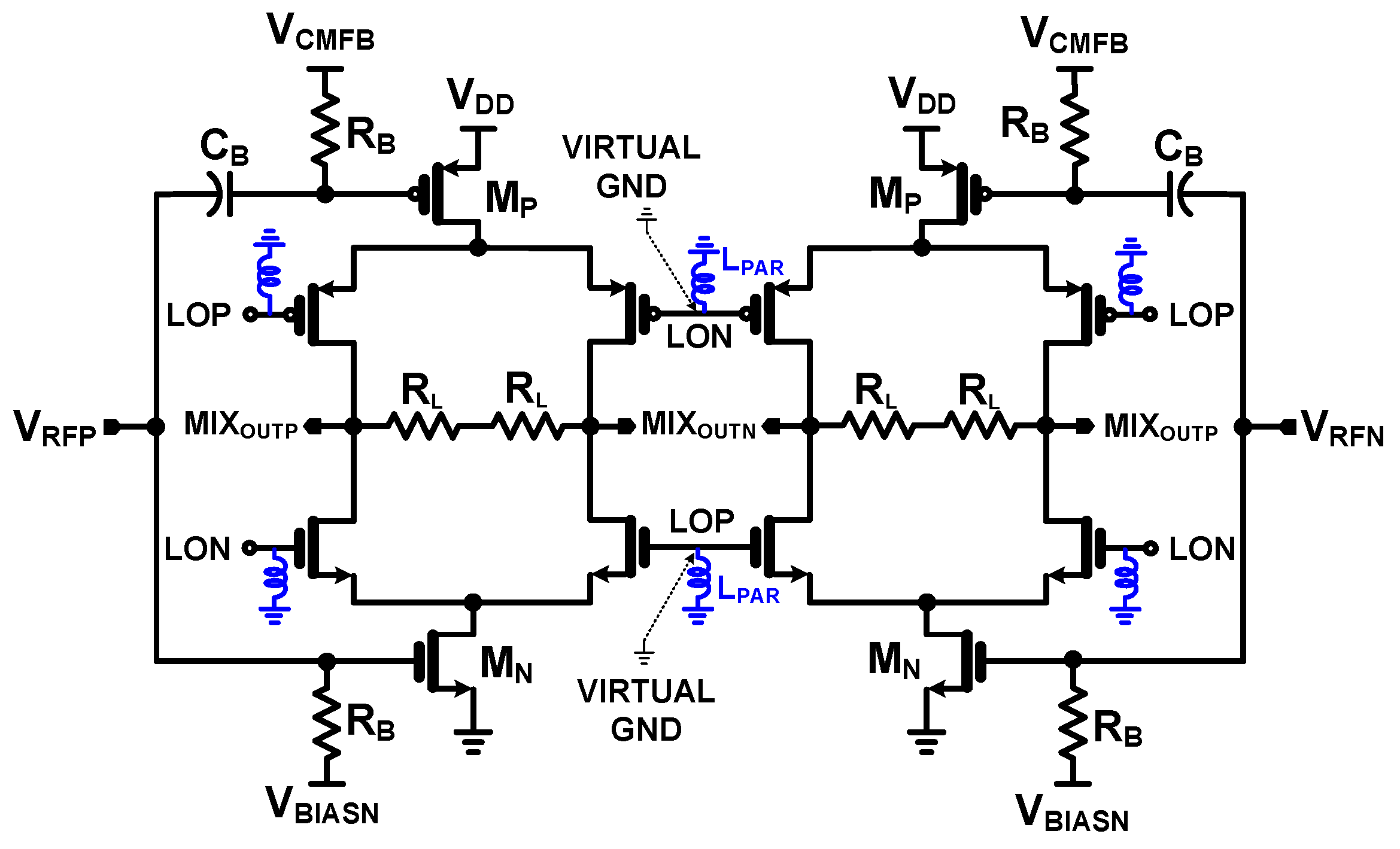

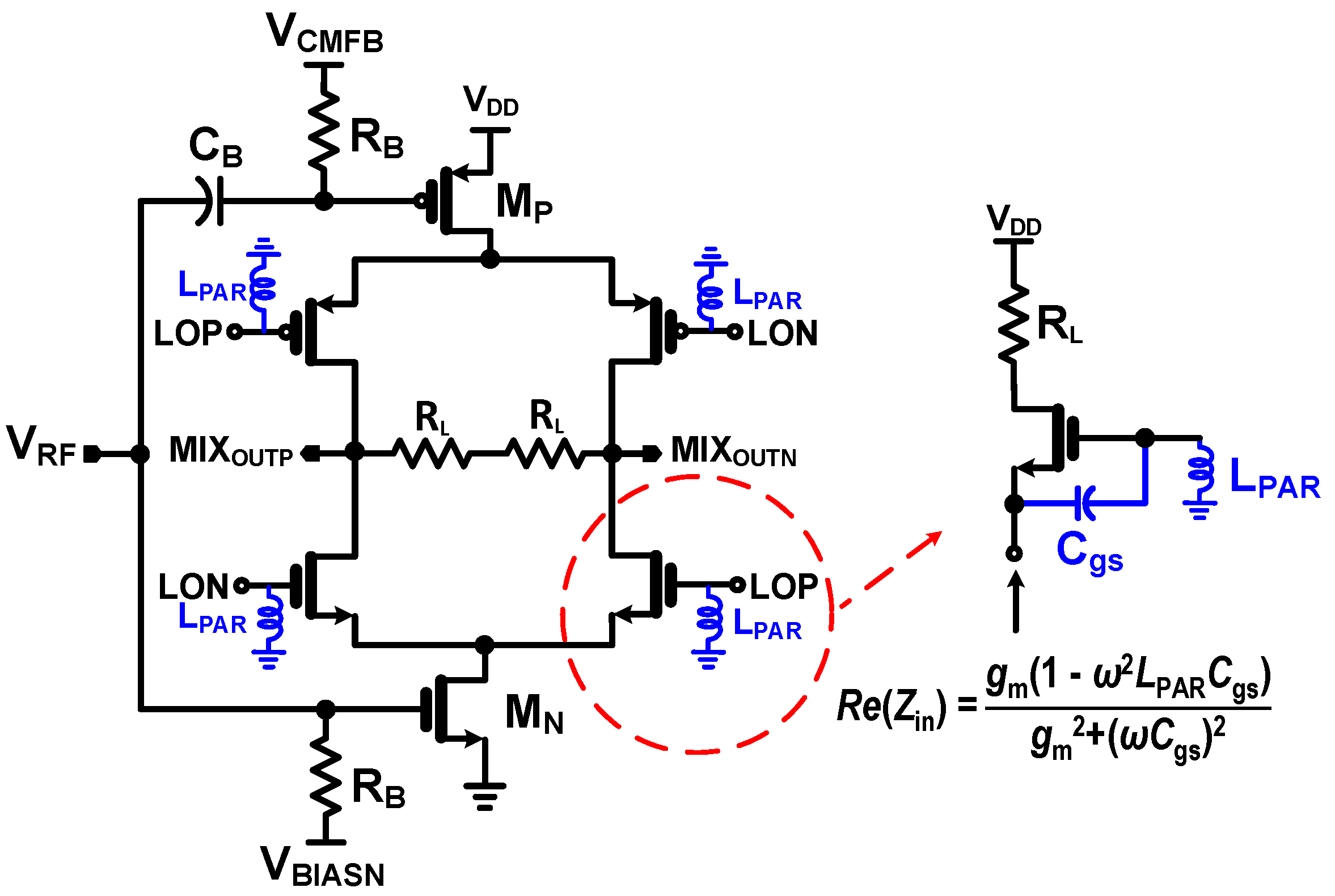

3.2. Down-Conversion Mixer

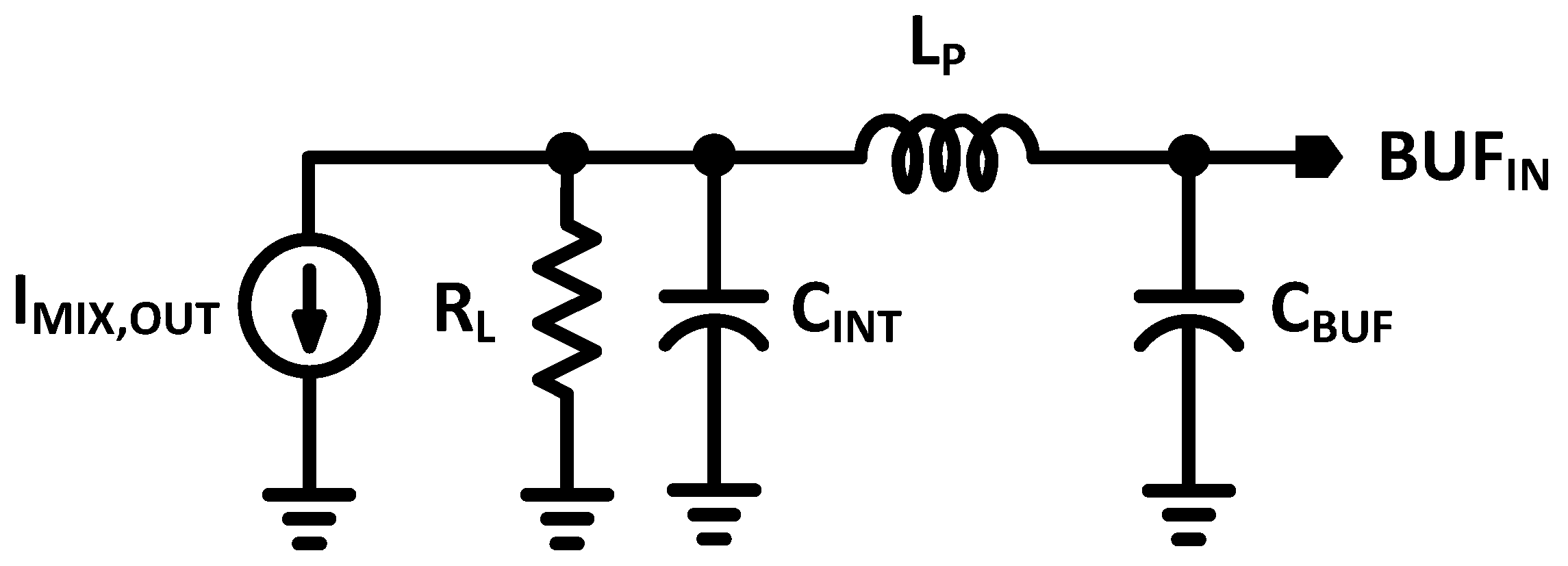

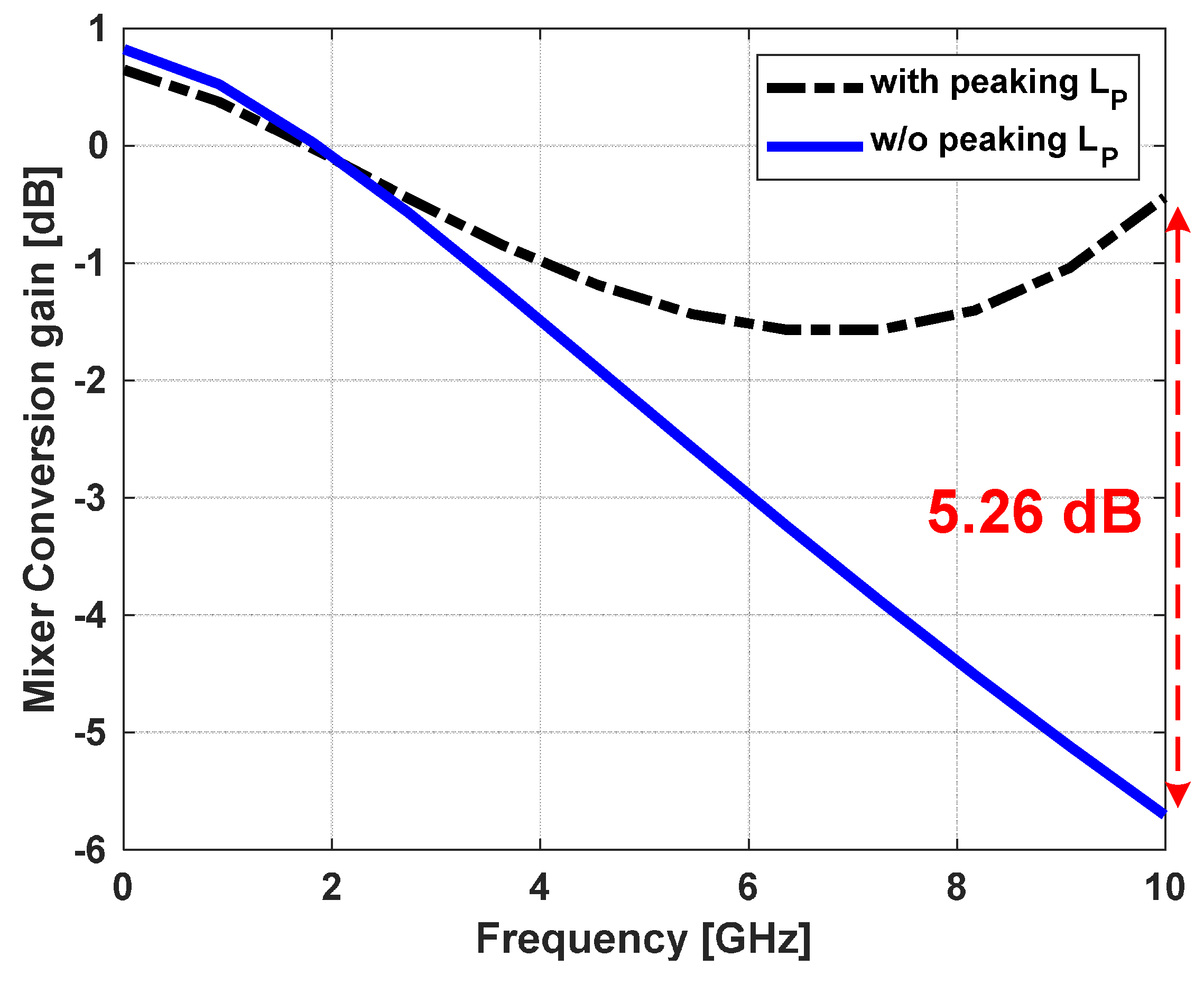

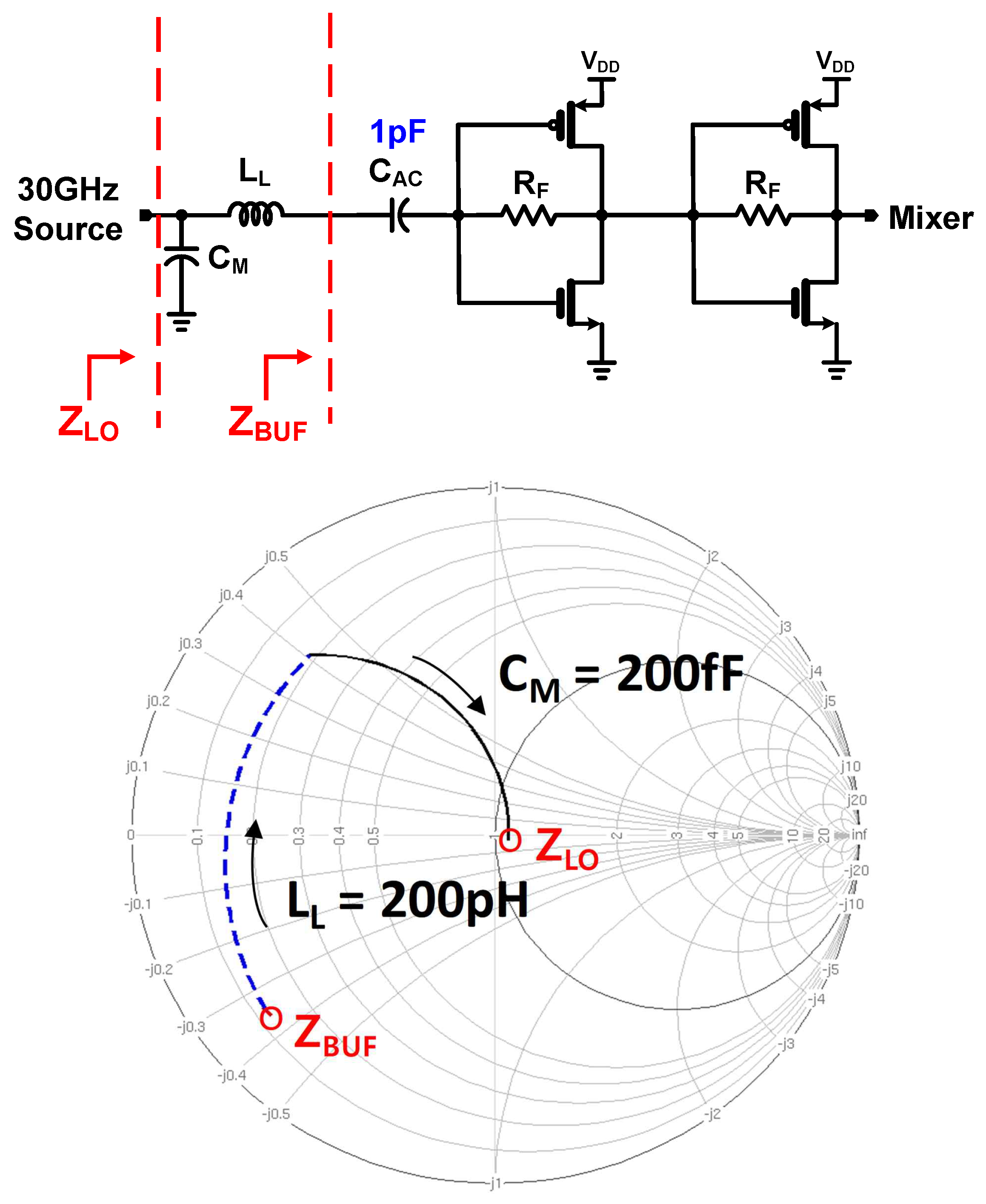

3.3. Third-Order LC Ladder Filter and LO Buffer

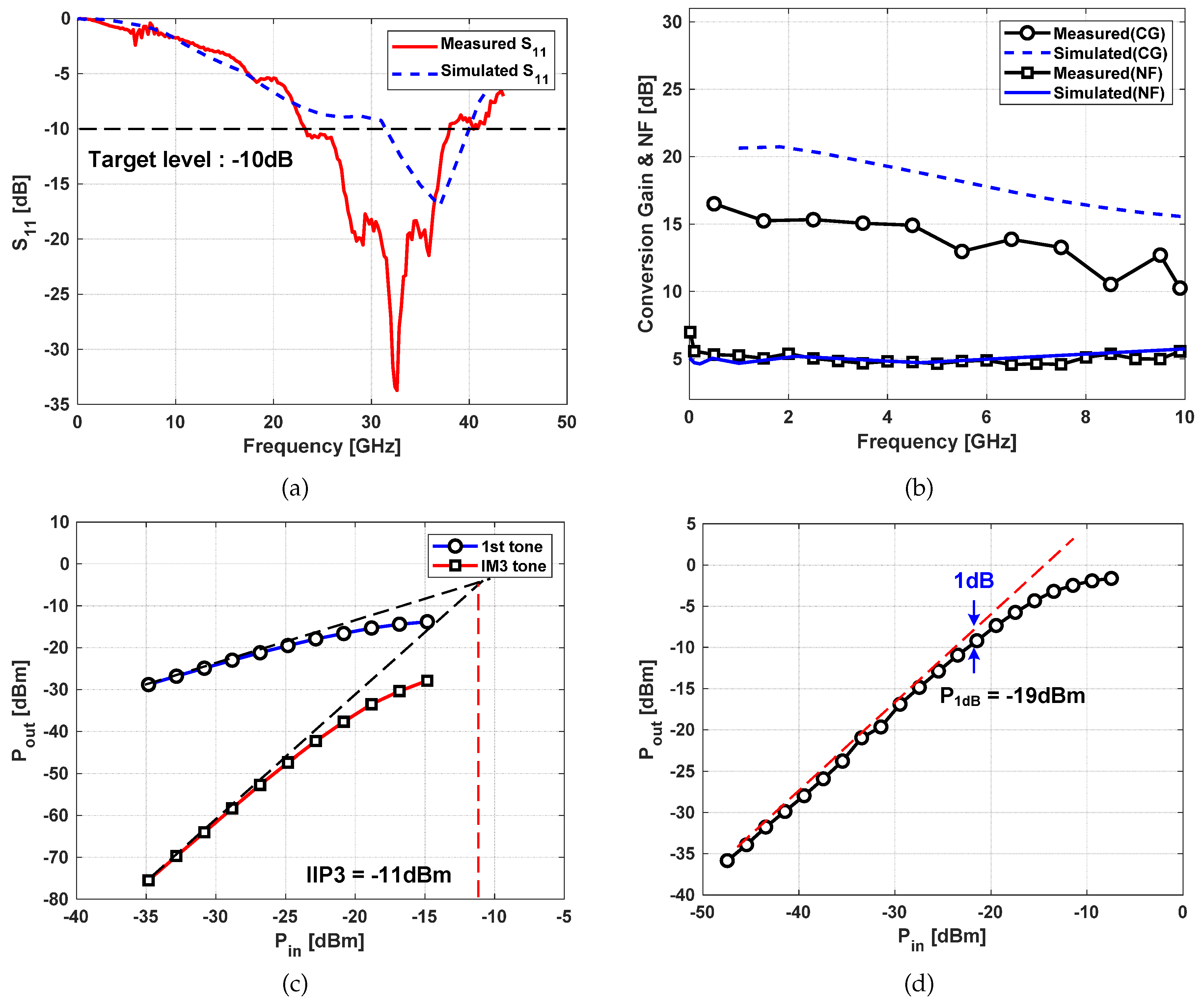

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Haykin, S. Cognitive radio, brain-empowered wireless communications. IEEE J. Sel. Areas Commun. 2005, 23, 201–220. [Google Scholar] [CrossRef]

- Joseph, M.; Gerald, Q.M. Cognitive radio: Making software radios more personal. IEEE Pers. Commun. 1999, 6, 13–18. [Google Scholar]

- Kim, J.; Utomo, D.R.; Dissanayake, A.; Han, S.K.; Lee, S.G. The Evolution of channelization receiver architecture: Principles and design challenges. IEEE Access. 2017, 5, 25385–25395. [Google Scholar] [CrossRef]

- Min, B.-W.; Rebeiz, G.M. Single-ended and differential Ka-band BiCMOS phased array front-ends. IEEE J. Solid-State Circuits 2008, 43, 2239–2250. [Google Scholar] [CrossRef]

- El-Nozahi, M.; Amer, A.; Sanchez-Sinencio, E.; Entesari, K. A Millimeter-Wave (24/31-GHz) Dual-Band Switchable Harmonic Receiver in 0.18-μm SiGe Process. IEEE Trans. Microw. Theory Tech. 2010, 58, 2717–2730. [Google Scholar] [CrossRef]

- Kodak, U.; Rebeiz, G.M. A 42 mW 26–28 GHz phased-array receive channel with 12 dB gain, 4 dB NF and 0 dBm IIP3 in 45 nm CMOS SOI. In Proceedings of the 2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Francisco, CA, USA, 22–24 May 2016. [Google Scholar]

- Yeh, Y.S.; Walker, B.; Balboni, E.; Floyd, B. A 28-GHz Phased-Array Receiver Front End With Dual-Vector Distributed Beamforming. IEEE J. Solid-State Circuits 2017, 52, 1230–1244. [Google Scholar] [CrossRef]

- Jain, V.; Sundararaman, S.; Heydari, P. A 22–29-GHz UWB pulse radar receiver fornt-end in 0.18-μm CMOS. IEEE Trans. Microw. Theory Tech. 2009, 57, 1903–1914. [Google Scholar] [CrossRef]

- Lin, Y.S.; Lee, J.H.; Huang, S.L.; Wang, C.H.; Wang, C.C.; Lu, S.S. Design and Analysis of a 21–29-GHz Ultra- Wideband Receiver Front-End in 0.18 μm CMOS Technology. IEEE Trans. Microw. Theory Tech. 2012, 60, 2590–2604. [Google Scholar] [CrossRef]

- Deng, Z.; Chen, J.; Tsai, J.; Niknejad, A. A CMOS Ku-band single conversion low-noise block front-end for satellite receivers. In Proceedings of the 2009 IEEE Radio Frequency Integrated Circuits Symposium, Boston, MA, USA, 7–9 June 2009. [Google Scholar]

- Jong, G.d.; Leenaerts, D.; van der Heijden, E. A fully integrated Ka-Band VSAT Down-Converter. IEEE J. Solid-State Circuits 2013, 48, 1651–1658. [Google Scholar] [CrossRef]

- Jung, H.; Utomo, D.R.; Shin, S.; Han, S.K.; Lee, S.G.; Kim, J. Ka-band RF Front-End with 5 dB NF and 16 dB conversion gain in 45 nm CMOS technology. In Proceedings of the IEEE International SoC Design Conference, Daegu, Korea, 12–15 November 2018. [Google Scholar]

- Shaeffer, D.K.; Lee, T.H. A 1.5-V, 1.5-GHz CMOS low noise amplifier. IEEE J. Solid-State Circuits 1997, 32, 745–759. [Google Scholar] [CrossRef]

- Nguyen, T.K.; Kim, C.H.; Ihm, G.J.; Yang, M.S.; Lee, S.G. CMOS low-noise amplifier design optimization techniques. IEEE Trans. Microw. Theory Tech. 2004, 52, 1433–1442. [Google Scholar] [CrossRef]

- Wu, C.C.; Chou, M.F.; Wuen, W.S.; Wen, K.A. A low power CMOS low noise amplifier for ultra-wideband wireless applications. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Kobe, Japan, 23–26 May 2005. [Google Scholar]

- Liu, Y.H.; Huang, X.; Vidojkovic, M.; Ba, A.; Harpe, P.; Dolmans, G.; de Groot, H. A 1.9 nJ/b 2.4 GHz multistandard (Bluetooth Low Energy/Zigbee/IEEE802. 15.6) transceiver for personal/body-area networks. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 17–21 February 2013. [Google Scholar]

- Van Valkenburg, M.E. Analog Filter Design, 2nd ed.; Holt, Rinehart, and Winston: New York, NY, USA, 1982. [Google Scholar]

- Behzad, R. RF Microelectronics, 2nd ed.; Prentice Hall: Upper Saddle River, NJ, USA, 1998; ISBN 978-0-13-713473-1. [Google Scholar]

- Li, C.H.; Kuo, C.N.; Kuo, M.C. A 1.2-V 5.2-mW 20–30-GHz Wideband Receiver Front-End in 0.18-μm CMOS. IEEE Trans. Microw. Theory Tech. 2012, 60, 3502–3512. [Google Scholar]

- Wang, P.Y.; Shen, Y.C.; Chou, M.C.; Wu, T.L.; Chang, Y.C.; Chang, D.C.; Hsu, S.S.H. A BiCMOS Monolithic Ka-Band Down-Converter for Satellite Communication Systems. In Proceedings of the IEEE MTT-S International Microwave Symposium (IMS), Phoenix, AZ, USA, 17–22 May 2015. [Google Scholar]

- Ding, B.; Yuan, S.; Zhao, C.; Tao, L.; Tian, T. A Ka band FMCW Transceiver front-end with 2GHz bandwidth in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 212–216. [Google Scholar] [CrossRef]

| Parameter | Value | Description |

|---|---|---|

| g | 76.2 mS | transconductance of M |

| L | 230 pH | load inductor |

| R | 44 | load resistor |

| C | 20 fF | parasitic capacitance between gate and drain |

| C | 200 fF | parasitic gate capacitance of M |

| Specification | This Work | TMTT 12 [19] | IMS 15 [20] | JSSC 17 [7] | TICAS-II 19 [21] |

|---|---|---|---|---|---|

| RF Frequency [GHz] | 30–40 | 20–30 | 18.2–21.4 | 28–32 | 33.6–36.3 |

| IF Bandwidth [GHz] | 10 | 0.3 | 1.35 | 4 | 2.3 |

| Gain [dB] | 16.5 | 18.7 | 49 | 10.5 | 30.9 |

| NF [dB] | 5.9 | 7.1–14.2 | 5.25–6.25 | 5.6–8.6 | 5.9–7.5 |

| IIP3 [dBm] | −11 | >−7.6 | >−33.5 | >−10.6 | N/A |

| P [dBm] | −19 | >−17.9 | >−43.3 | >−16.8 | −23 |

| P [mW] | 96 | 5.2 | 80 | 136.5 | 135/27.6 |

| Technology | CMOS 45 nm | CMOS 180 nm | SiGe 180 nm | SiGe 130 nm | CMOS 65 nm |

| Area [mm] | 0.42/0.21 | 0.18 | 0.4/0.24 | 1.08 | 2.16 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jung, H.; Utomo, D.R.; Shin, S.; Han, S.-K.; Lee, S.-G.; Kim, J. A 30–40 GHz CMOS Receiver Front-End with 5.9 dB NF and 16.5 dB Conversion Gain for Broadband Spectrum Sensing Applications. Electronics 2019, 8, 593. https://doi.org/10.3390/electronics8050593

Jung H, Utomo DR, Shin S, Han S-K, Lee S-G, Kim J. A 30–40 GHz CMOS Receiver Front-End with 5.9 dB NF and 16.5 dB Conversion Gain for Broadband Spectrum Sensing Applications. Electronics. 2019; 8(5):593. https://doi.org/10.3390/electronics8050593

Chicago/Turabian StyleJung, Hyunki, Dzuhri Radityo Utomo, Saebyeok Shin, Seok-Kyun Han, Sang-Gug Lee, and Junsung Kim. 2019. "A 30–40 GHz CMOS Receiver Front-End with 5.9 dB NF and 16.5 dB Conversion Gain for Broadband Spectrum Sensing Applications" Electronics 8, no. 5: 593. https://doi.org/10.3390/electronics8050593

APA StyleJung, H., Utomo, D. R., Shin, S., Han, S.-K., Lee, S.-G., & Kim, J. (2019). A 30–40 GHz CMOS Receiver Front-End with 5.9 dB NF and 16.5 dB Conversion Gain for Broadband Spectrum Sensing Applications. Electronics, 8(5), 593. https://doi.org/10.3390/electronics8050593