Effect of lateral Gate Design on the Performance of Junctionless Lateral Gate Transistors

Abstract

1. Introduction

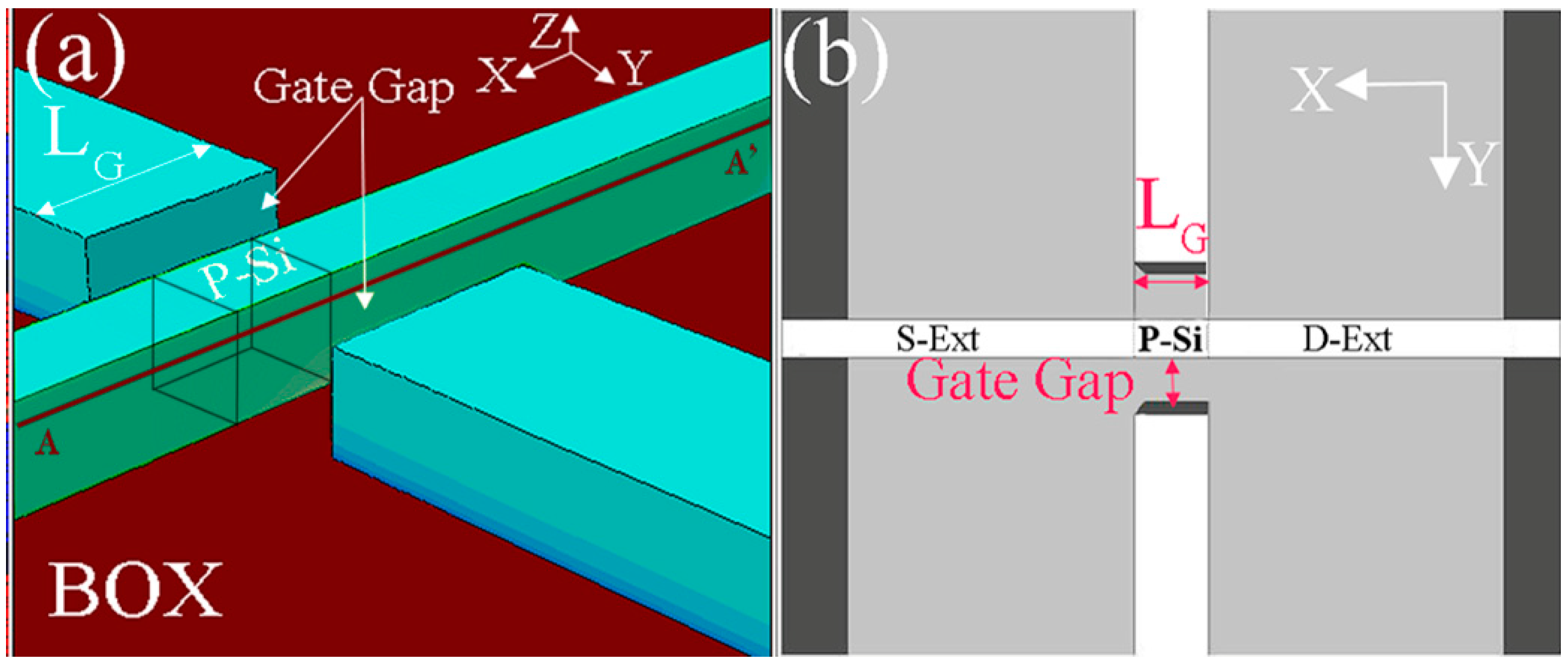

2. Device Structure and Simulation Methodology

3. Results

3.1. Principle of Operation

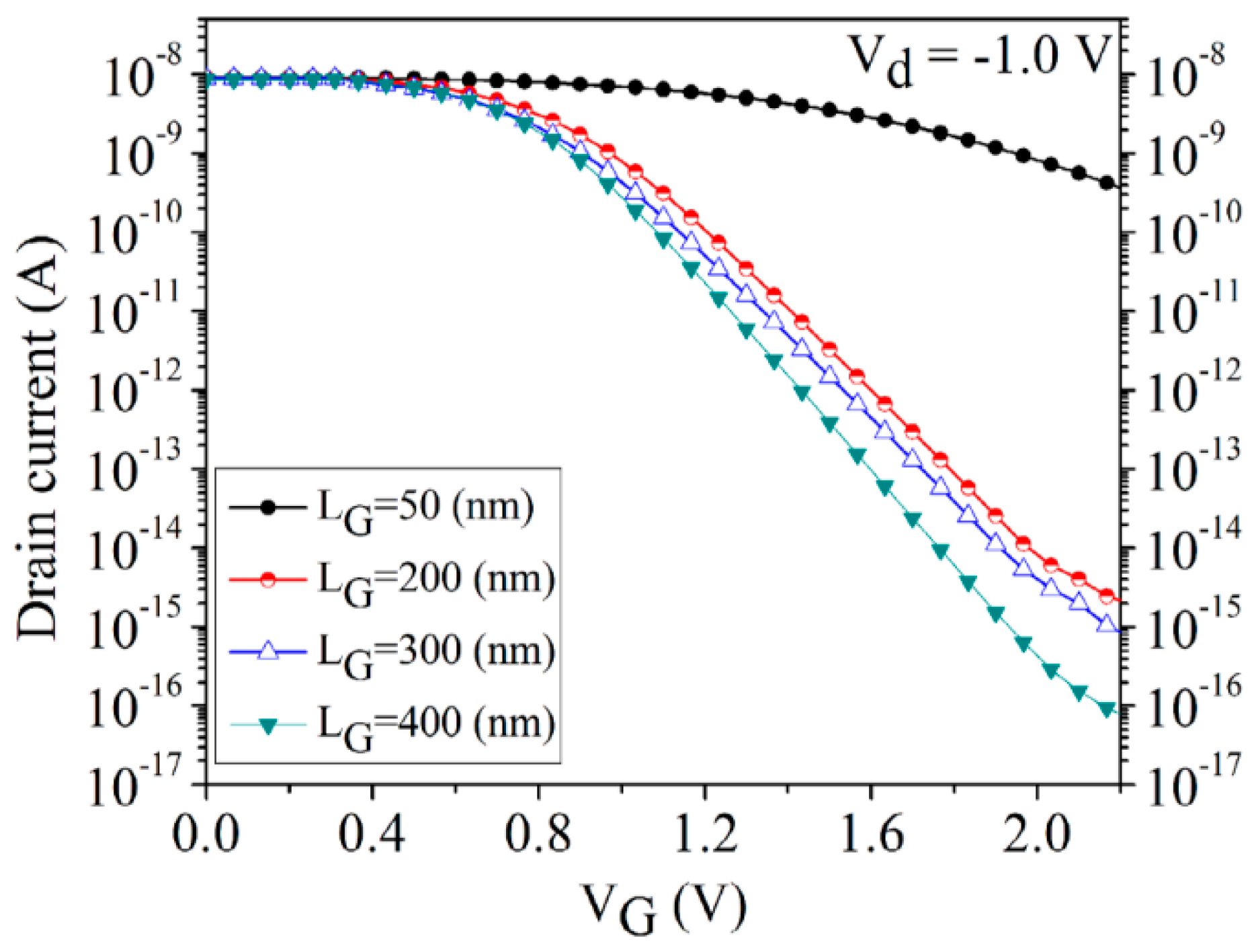

3.2. Effect of Lateral Gate Length (LG) Variation

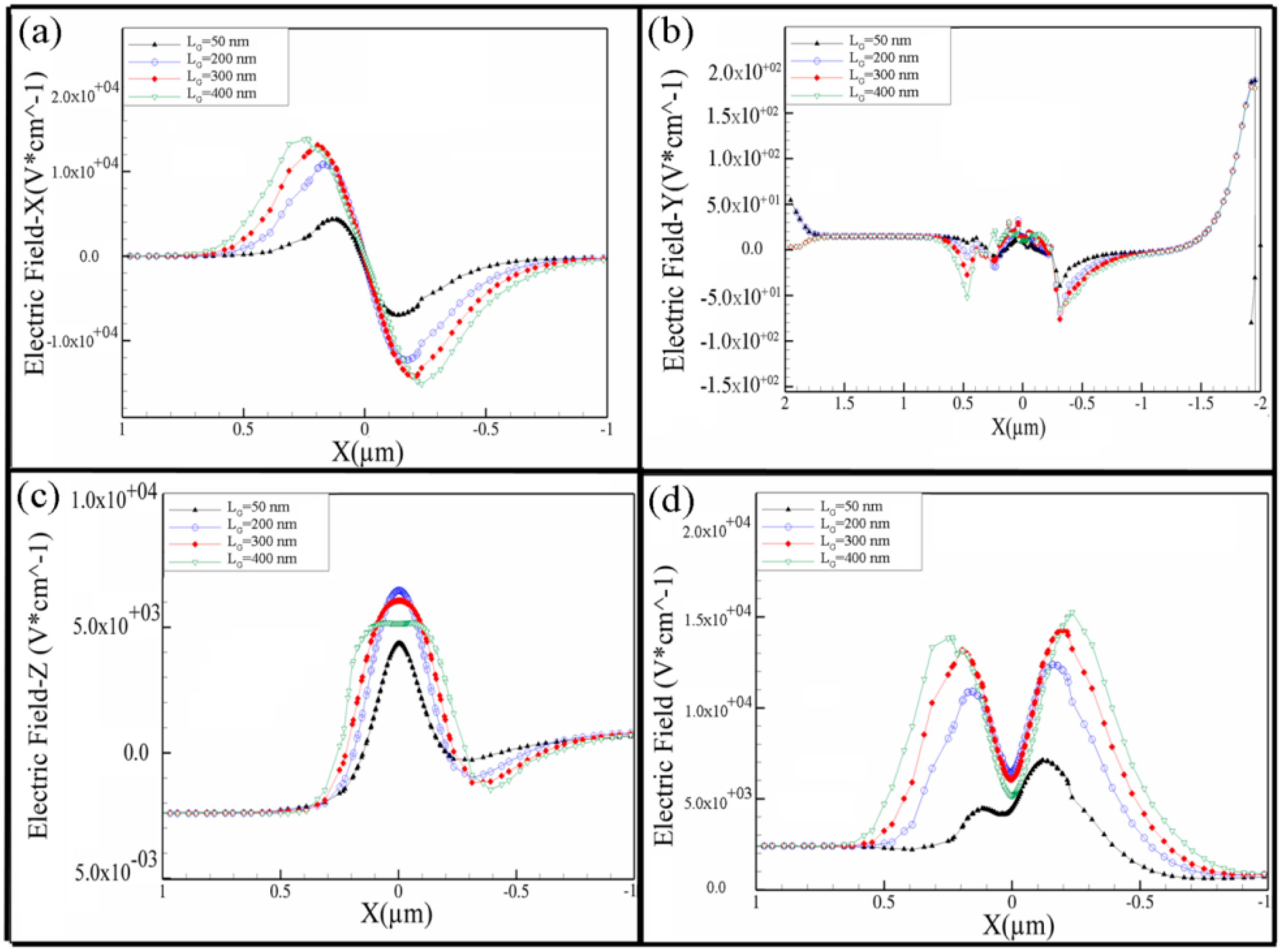

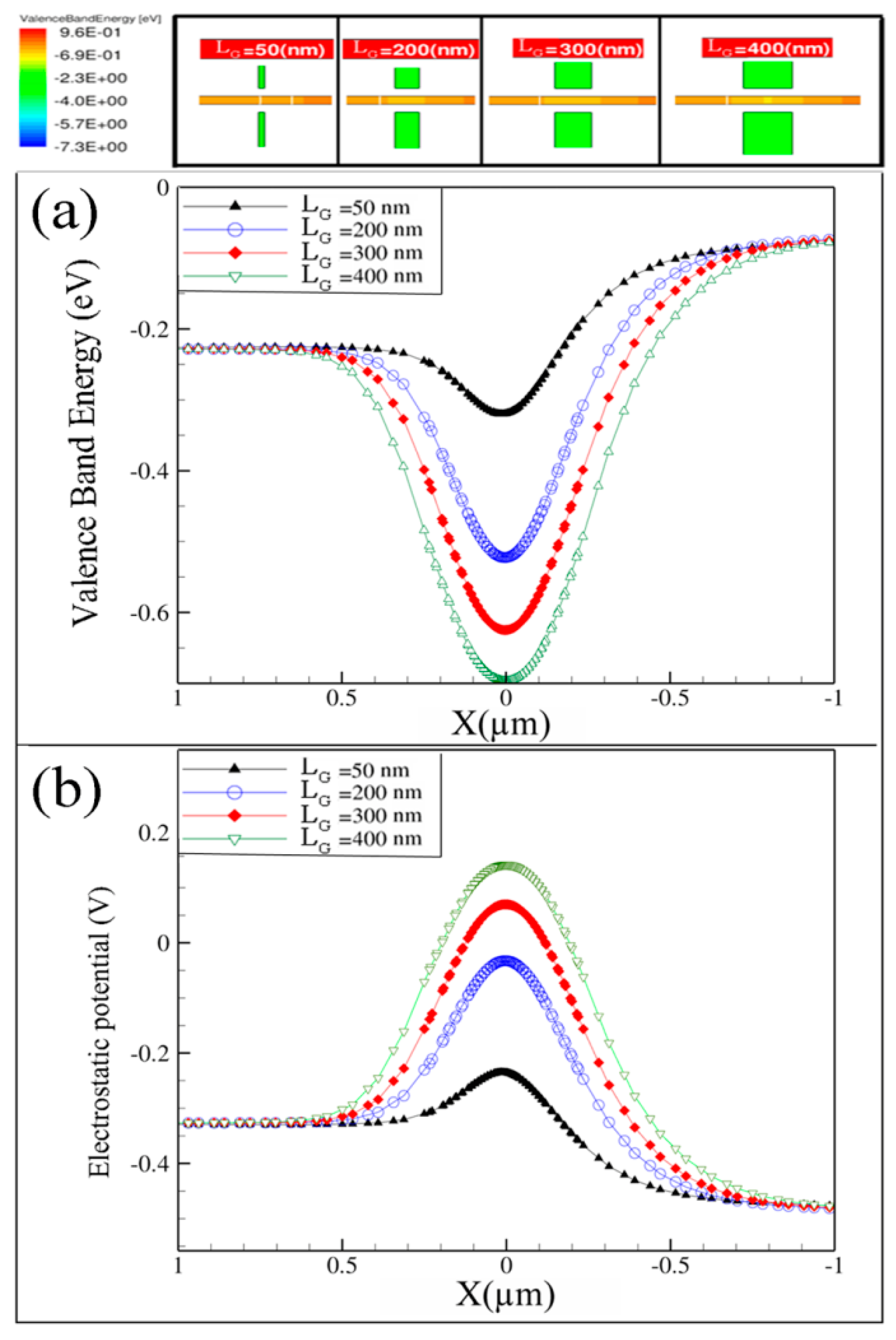

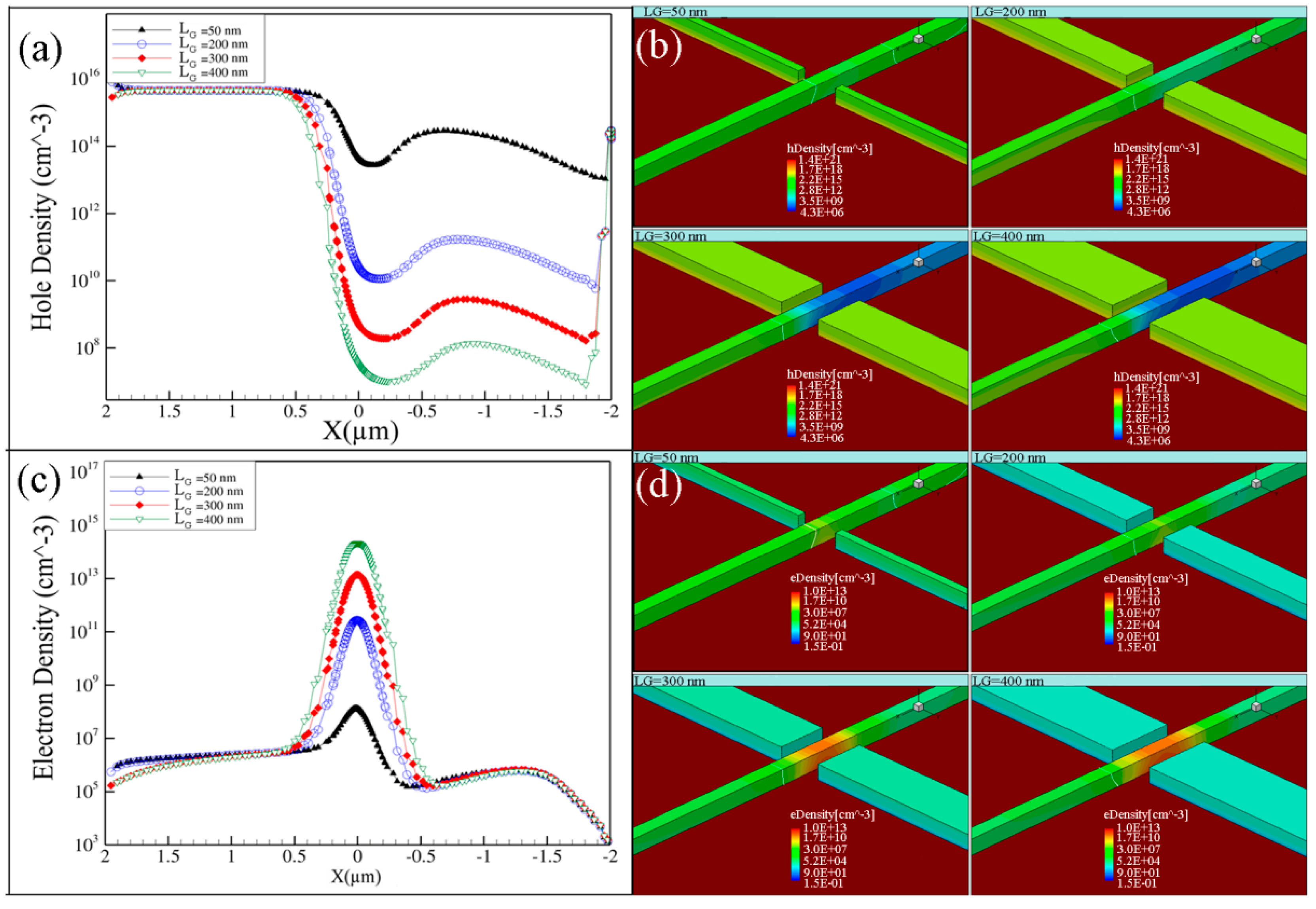

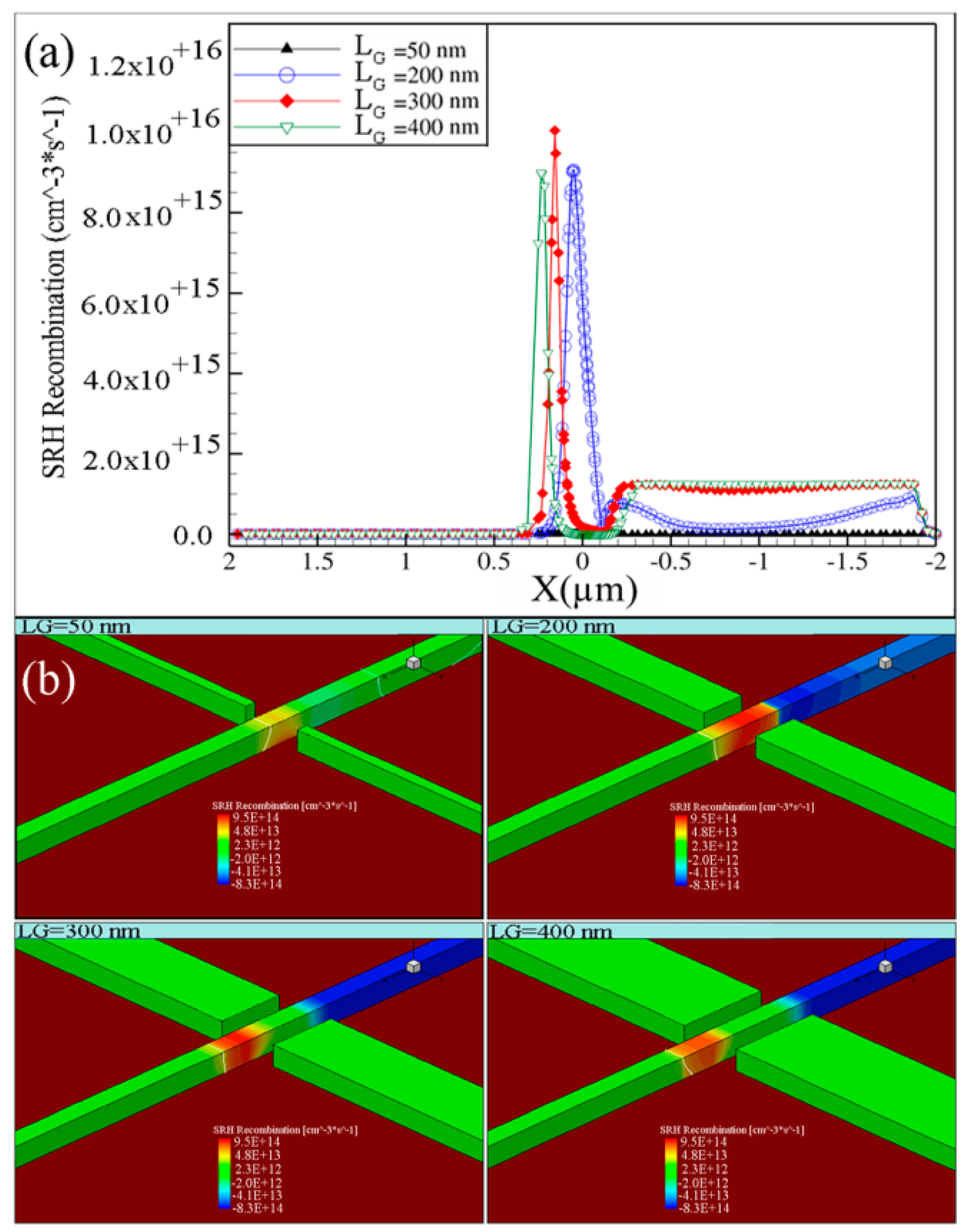

3.2.1. Depletion Regime

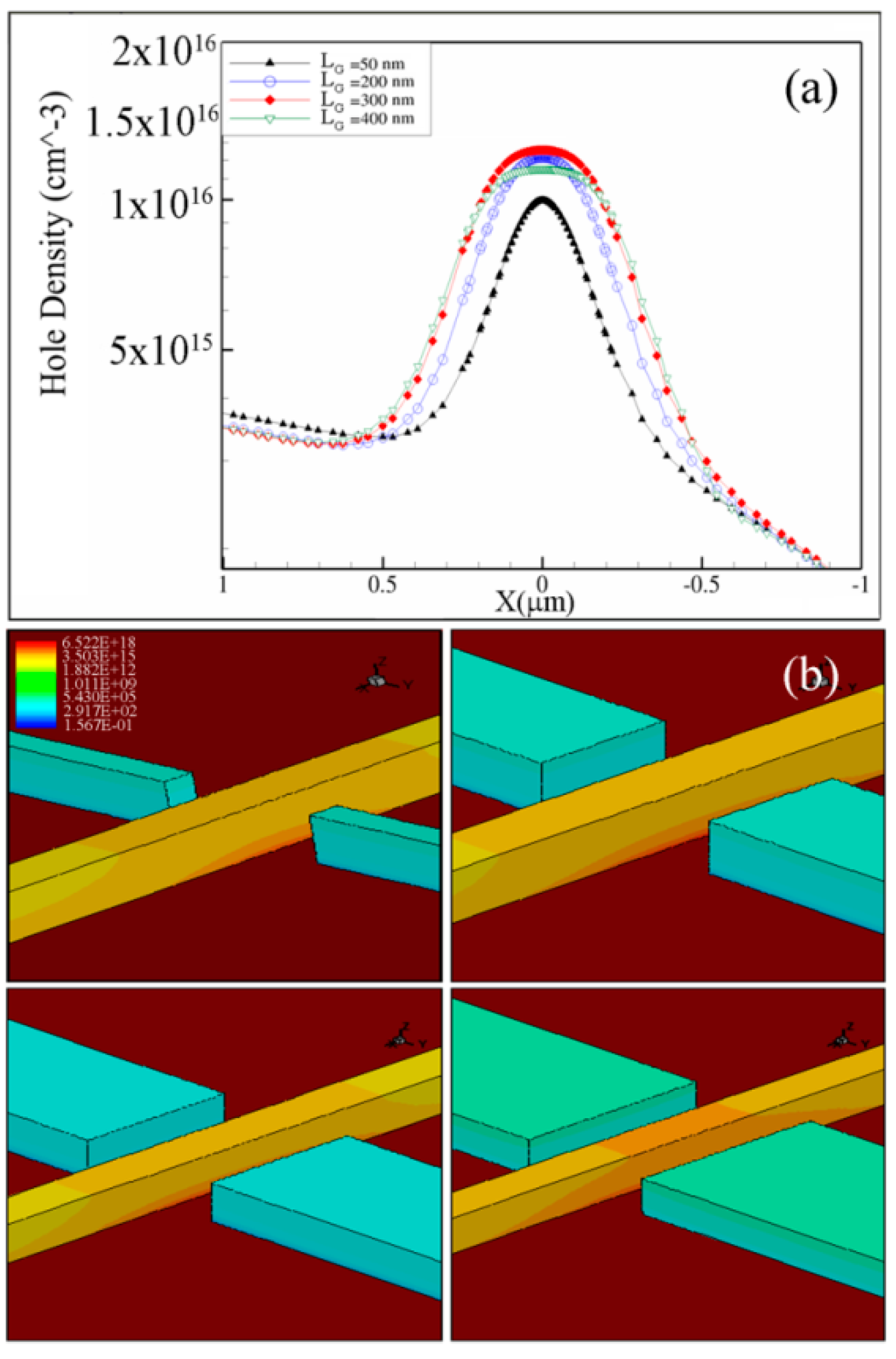

3.2.2. Accumulation Regime

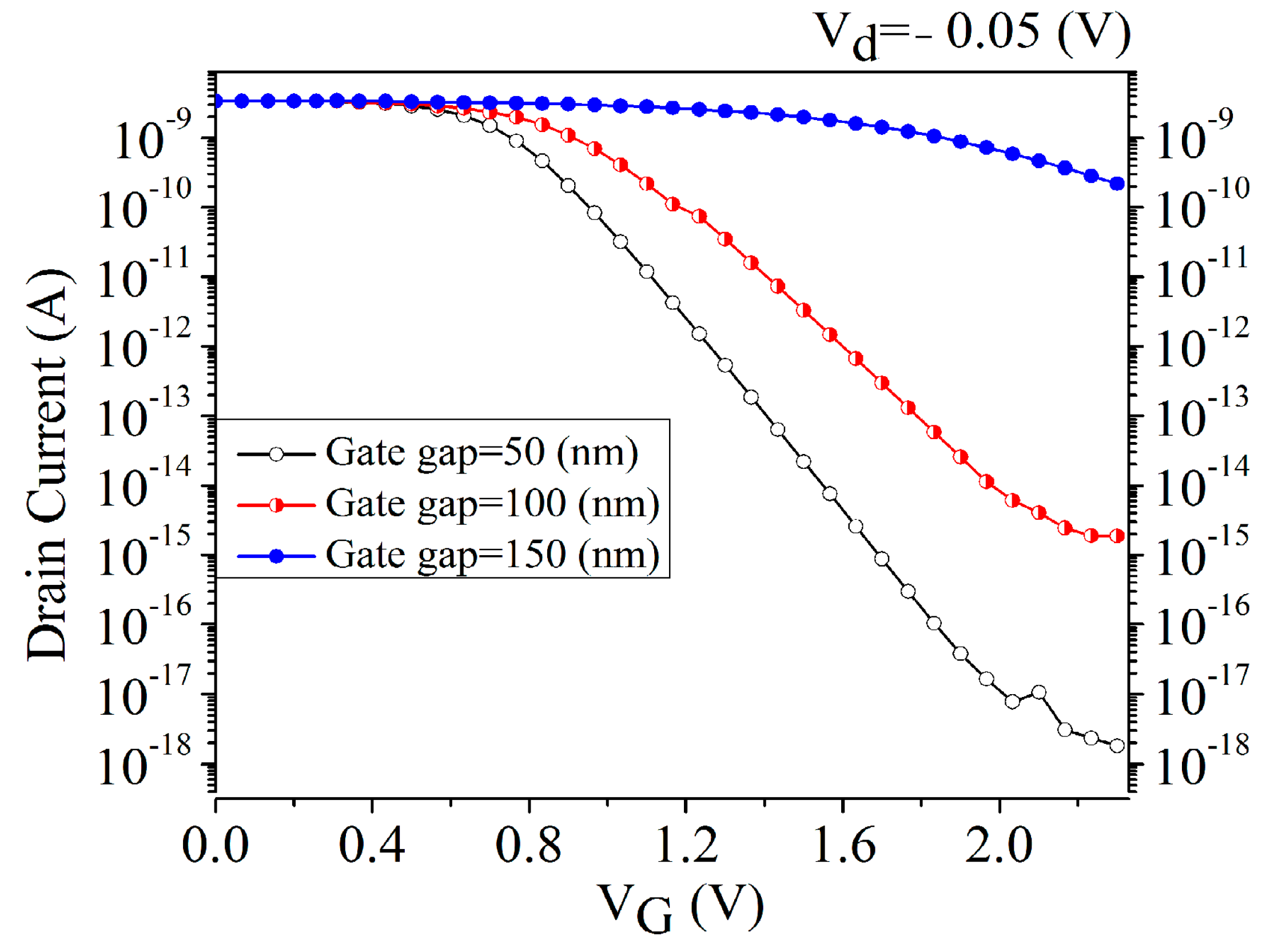

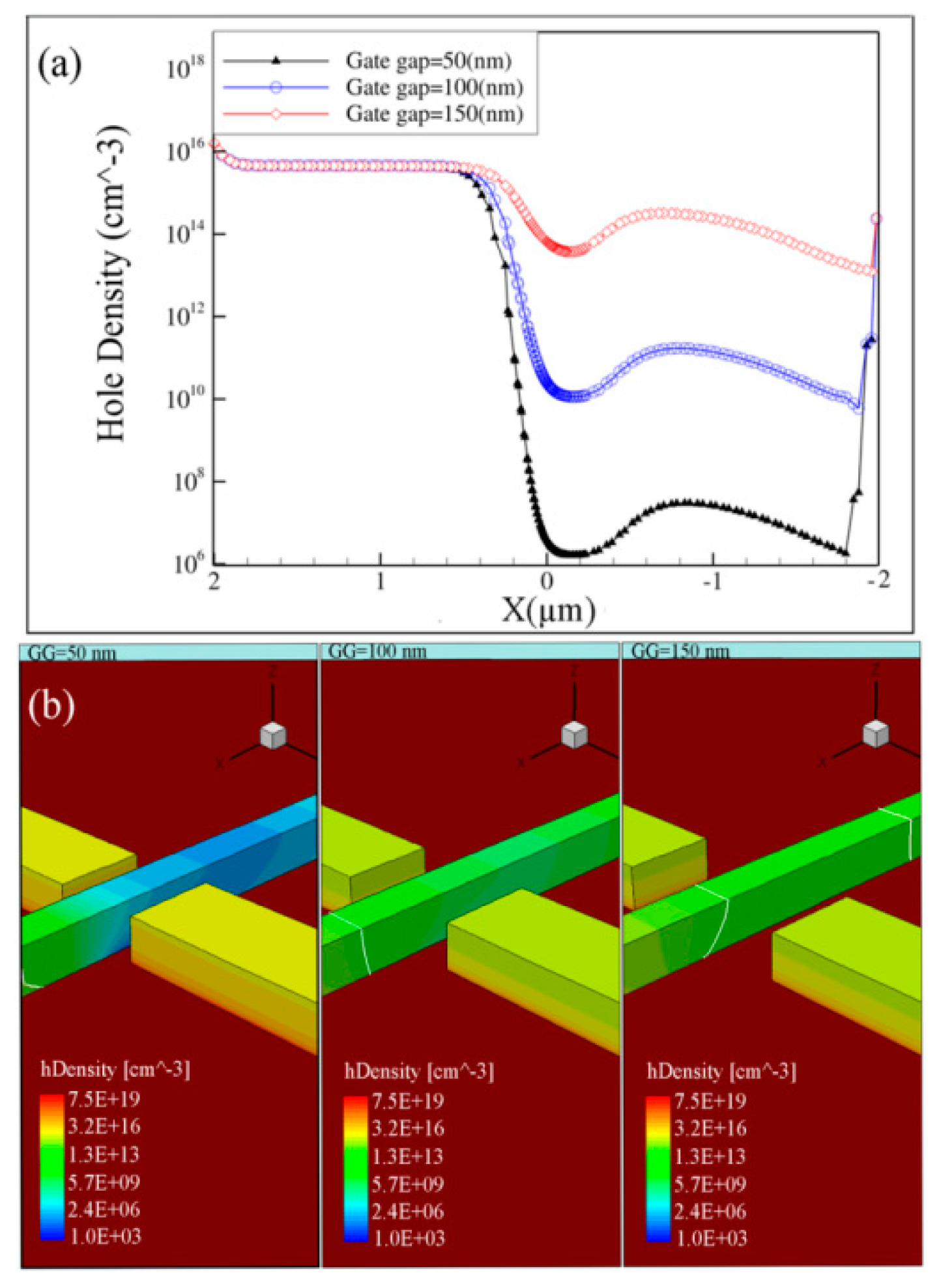

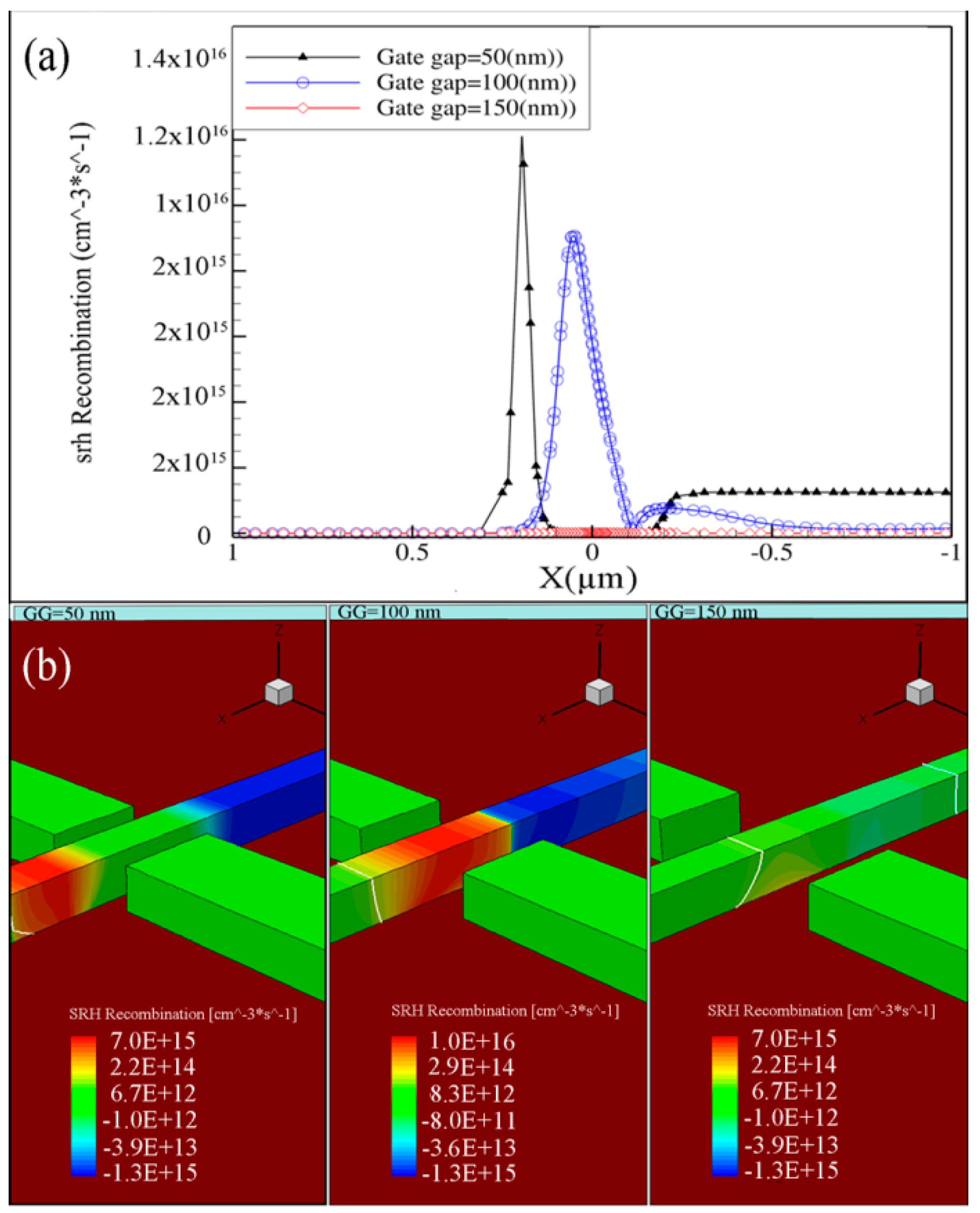

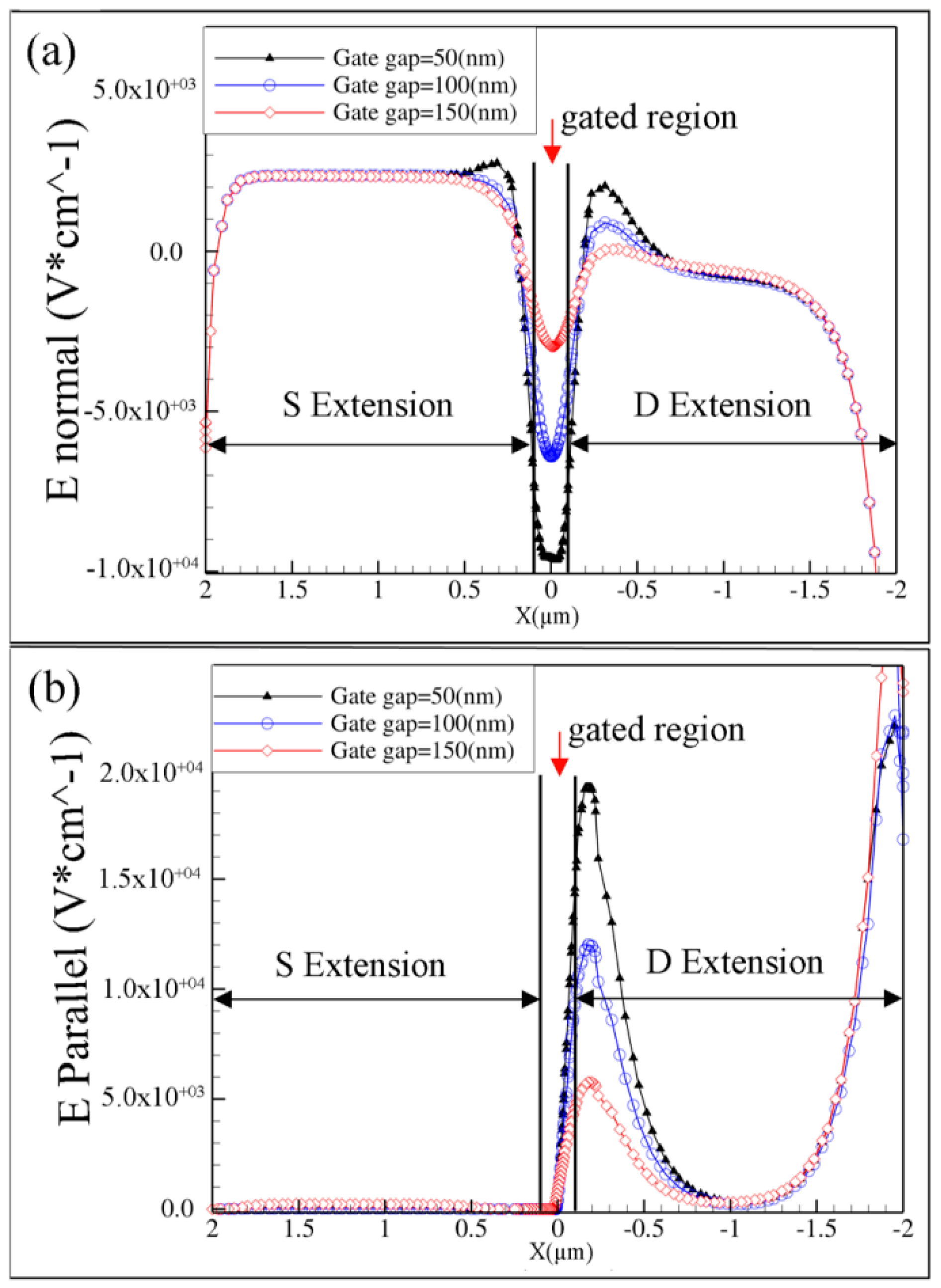

3.3. Effect of Gate Gap Variation

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Lee, C.W.; Afzalian, A.; Akhavan, N.D.; Yan, R.; Ferain, I.; Colinge, J.P. Junctionless multigate field-effect transistor. Appl. Phys. Lett. 2009, 94, 053511–053511-2. [Google Scholar] [CrossRef]

- Colinge, J.P.; Lee, C.W.; Afzalian, A.; Akhavan, N.D.; Yan, R.; Ferain, I.; Razavi, P.; O’Neill, B.; Blake, A.; White, M. Nanowire transistors without junctions. Nat. Nanotechnol. 2010, 5, 225–229. [Google Scholar] [CrossRef] [PubMed]

- Doria, R.T.; Trevisoli, R.; de Souza, M.; Pavanello, M.A. Low-frequency noise and effective trap density of short channel p-and n-types junctionless nanowire transistors. Solid-State Electron. 2014, 96, 22–26. [Google Scholar] [CrossRef]

- Colinge, J.P.; Ferain, I.; Kranti, A.; Lee, C.W.; Akhavan, N.D.; Razavi, P.; Yan, R.; Yu, R. Junctionless Nanowire Transistor: Complementary Metal-Oxide-Semiconductor Without Junctions. Sci. Adv. Mater. 2011, 3, 477–482. [Google Scholar] [CrossRef]

- Jang, D.; Lee, J.W.; Lee, C.W.; Colinge, J.P.; Montès, L.; Lee, J.I.; Kim, G.T.; Ghibaudo, G. Low-frequency noise in junctionless multigate transistors. Appl. Phys. Lett. 2011, 98, 133502. [Google Scholar] [CrossRef]

- Han, M.-H.; Chang, C.-Y.; Chen, H.-B.; Wu, J.-J.; Cheng, Y.-C.; Wu, Y.-C. Performance comparison between bulk and SOI junctionless transistors. IEEE Electron Device Lett. 2013, 34, 169–171. [Google Scholar] [CrossRef]

- Gundapaneni, S.; Konar, A.; Bajaj, M.; Murali, K. Improved Performance of Junctionless Tunnel FETs with Source/Channel Heterostructure. In Physics of Semiconductor Devices; Springer: Berlin/Heidelberg, Germany, 2014; pp. 289–290. [Google Scholar]

- Colinge, J.; Kranti, A.; Yan, R.; Lee, C.; Ferain, I.; Yu, R.; Akhavan, N.D.; Razavi, P. Junctionless nanowire transistor (JNT): Properties and design guidelines. Solid-State Electron. 2011, 65, 33–37. [Google Scholar] [CrossRef]

- Chung, C.C.-C.; Shen, C.-H.; Lin, J.-Y.; Chin, C.-C.; Chao, T.-S. Vertically stacked cantilever n-type poly-Si junctionless nanowire transistor and its series resistance limit. IEEE Trans. Electron Devices 2018, 65, 756–762. [Google Scholar] [CrossRef]

- Ma, L.; Han, W.; Wang, H.; Yang, X.; Yang, F. Observation of degenerate one-dimensional subbands in single n-channel junctionless nanowire transistors. IEEE Electron Device Lett. 2015, 36, 941–943. [Google Scholar]

- Konar, A.; Mathew, J.; Nayak, K.; Bajaj, M.; Pandey, R.K.; Dhara, S.; Murali, K.; Deshmukh, M.M. Carrier transport in high mobility InAs nanowire junctionless transistors. Nano Lett. 2015, 15, 1684–1690. [Google Scholar] [CrossRef]

- Chen, L.; Cai, F.; Otuonye, U.; Lu, W.D. Vertical Ge/Si core/shell nanowire junctionless transistor. Nano Lett. 2015, 16, 420–426. [Google Scholar] [CrossRef] [PubMed]

- Cao, W.; Kang, J.; Banerjee, K. Junction-Less Monolayer MoS2 FETs. arXiv 2015, arXiv:1509.00561. [Google Scholar]

- Mirabelli, G.; Duffy, R.; Hurley, P.; Monaghan, S.; Cherkaoui, K.; Schmidt, M.; Sheehan, B.; Povey, I.M.; McCarthy, M.; Nagle, R. Mo-Based Transition-Metal-Dichalcogenide Junctionless Field-Effect-Transistors; Meeting Abstracts; The Electrochemical Society: San Diego, CA, USA, 2016; p. 1289. [Google Scholar]

- Faraji, M.; Ghoreishi, S.S.; Yousefi, R. Gate structural engineering of MOS-like junctionless Carbon nanotube field effect transistor (MOS-like J-CNTFET). Int. J. Nano Dimens. 2018, 9, 32–40. [Google Scholar]

- Cheng, P.-H.; Wang, C.-Y.; Chang, T.-J.; Shen, T.-H.; Cai, Y.-S.; Chen, M.-J. Room-temperature field effect transistors with metallic ultrathin TiN-based channel prepared by atomic layer delta doping and deposition. Sci. Rep. 2017, 7, 875. [Google Scholar] [CrossRef] [PubMed]

- Narang, R.; Saxena, M.; Gupta, M. Investigation of dielectric modulated (DM) double gate (DG) junctionless MOSFETs for application as a biosensors. Superlattices Microstruct. 2015, 85, 557–572. [Google Scholar]

- Pratap, Y.; Kumar, M.; Kabra, S.; Haldar, S.; Gupta, R.; Gupta, M. Analytical modeling of gate-all-around junctionless transistor based biosensors for detection of neutral biomolecule species. J. Comput. Electron. 2018, 17, 288–296. [Google Scholar] [CrossRef]

- Chen, X. Biodegradable Junctionless Transistors with Extremly Simple Structure. IEEE Electron Device Lett. 2015, 36, 908–910. [Google Scholar]

- Bartsch, S.T.; Arp, M.; Ionescu, A.M. Junctionless Silicon Nanowire Resonator. IEEE J. Electron Devices Soc. 2014, 2, 8–15. [Google Scholar] [CrossRef]

- Vaurette, F.; Leturcq, R.; Lepilliet, S.; Grandidier, B.; Stiévenard, D. Confinement-modulated junctionless nanowire transistors for logic circuits. Nanoscale 2014, 6, 13446–13450. [Google Scholar] [CrossRef]

- Roudsari, A.F.; Khodadadzadeh, I.; Saini, S.S.; Anantram, M. Junction-less nanowire based photodetector: Role of nanowire width. arXiv 2017, arXiv:1707.07892. [Google Scholar]

- Chang, M.S.; Cheung, R.W. Method of Decreased Interlayer Dielectric Constant in a Multilayer Interconnect Structure to Increase Device Speed Performance. US5559055A, 24 September 1996. [Google Scholar]

- Kocon, C.B.; Elbanhawy, A. Method and Apparatus for Improved MOS Gating to Reduce Miller Capacitance and Switching Losses. US6870220B2, 22 March 2005. [Google Scholar]

- Park, J.M. Improving CMOS Speed and Switching Power with Air-Gap Structures; No. UCB/EECS-2011-84; UC Berkeley: Berkeley, CA, USA, 2011. [Google Scholar]

- Rabaey, J.M.; Pedram, M. Low Power Design Methodologies; Spring Science + Business Media: New York, NY, USA, 1996. [Google Scholar]

- Grill, A.; Gates, S.M.; Ryan, T.E.; Nguyen, S.V.; Priyadarshini, D. Progress in the development and understanding of advanced low k and ultralow k dielectrics for very large-scale integrated interconnects—State of the art. Appl. Phys. Rev. 2014, 1, 011306. [Google Scholar] [CrossRef]

- Triyoso, D.; Mulfinger, G.; Hempel, K.; Tao, H.; Koehler, F.; Kang, L.; Kumar, A.; McArdle, T.; Holt, J.; Child, A. Characterization of atomic layer deposited low-k spacer for FDSOI high-k metal gate transistor. In Proceedings of the 2017 IEEE International Conference on IC Design and Technology (ICICDT), Austin, TX, USA, 23–25 May 2017; pp. 1–4. [Google Scholar]

- Yang, T.; Mehta, J.S.; Mativetsky, J.M. An air gap moderates the performance of nanowire array transistors. Nanotechnology 2017, 28, 125204. [Google Scholar] [CrossRef]

- Mativetsky, J.; Yang, T.; Mehta, J. Impact of the air gap in nanowire array transistors. In Proceedings of the APS Meeting Abstracts, 2017, New Orleans, LA, USA, 13–17 March 2017. [Google Scholar]

- Shin, S.-H.; Ji, S.; Choi, S.; Pyo, K.-H.; An, B.W.; Park, J.; Kim, J.; Kim, J.-Y.; Lee, K.-S.; Kwon, S.-Y. Integrated arrays of air-dielectric graphene transistors as transparent active-matrix pressure sensors for wide pressure ranges. Nat. Commun. 2017, 8, 14950. [Google Scholar] [CrossRef] [PubMed]

- Abadeer, W.W.; Chatty, K.V.; Gauthier, R.J., Jr.; Rankin, J.H.; Tonti, W.R.; Shi, Y. Field Effect Transistor with Air Gap Dielectric. US8349697B2, 18 October 2012. [Google Scholar]

- Sachid, A.B.; Huang, Y.-M.; Chen, Y.-J.; Chen, C.-C.; Lu, D.D.; Chen, M.-C.; Hu, C. FinFET withencased air-gap spacers for high-performance and low-energy circuits. IEEE Electron Device Lett. 2017, 38, 16–19. [Google Scholar] [CrossRef]

- Dehzangi, A.; Abdullah, A.M.; Larki, F.; Hutagalung, S.D.; Saion, E.B.; Hamidon, M.N.; Hassan, J.; Gharayebi, Y. Electrical property comparison and charge transmission in p-type double gate and single gate junctionless accumulation transistor fabricated by AFM nanolithography. Nanoscale Res. Lett. 2012, 7, 1–9. [Google Scholar] [CrossRef] [PubMed]

- Larki, F.; Dehzangi, A.; Saion, E.B.; Abedini, A.; Hutagalung, S.D.; Abdullah, A.M.; Hamidon, M.N. Simulation of transport in laterally gated junctionless transistors fabricated by local anodization with an atomic force microscope. Phys. Status Solidi A 2013, 210, 1914–1919. [Google Scholar] [CrossRef]

- Dehzangi, A.; Larki, F.; Hutagalung, S.D.; Naseri, M.G.; Majlis, B.Y.; Navasery, M.; Hamid, N.A.; Noor, M.M. Impact of Parameter Variation in Fabrication of Nanostructure by Atomic Force Microscopy Nanolithography. PLoS ONE 2013, 8, e65409. [Google Scholar] [CrossRef] [PubMed]

- Larki, F.; Dehzangi, A.; Ali, S.H.M.; Jalar, A.; Islam, M.S.; Hamidon, M.N.; Majlis, B.Y. Effect of Geometric Parameters on the Performance of P-Type Junctionless Lateral Gate Transistors. PLoS ONE 2014, 9, e95182. [Google Scholar] [CrossRef]

- Larki, F.; Dehzangi, A.; Abedini, A.; Abdullah, A.M.; Saion, E.; Hutagalung, S.D.; Hamidon, M.N.; Hassan, J. Pinch-off mechanism in double-lateral-gate junctionless transistors fabricated by scanning probe microscope based lithography. Beilstein J. Nanotechnol. 2012, 3, 817–823. [Google Scholar] [CrossRef]

- Dehzangi, A.; Larki, F.; Md Ali, S.H.; Hutagalung, S.D.; Islam, S.; Hamidon, M.N.; Menon, S.; Jalar, A.; Hassan, J.; Yeop Majlis, B. Study of the side gate junctionless transistor in accumulation region. Microelectron. Int. 2016, 33, 61–67. [Google Scholar] [CrossRef]

- Larki, F.; Dehzangi, A.; Islam, M.S.; Ali, S.H.M.; Abedini, A.; Majlis, B. Effect of Channel Width Variation on Electrical Characteristics of Double Lateral Gate Junctionless Transistors; A Numerical Study. Silicon 2018, 10, 1305–1314. [Google Scholar] [CrossRef]

- Sentaurus, T. User Guide; Synopsys Inc.: Mountain View, CA, USA, 2010. [Google Scholar]

- Tsai, M.-J.; Chiang, Y.-Y.; Lin, Y.-R.; Kurniawan, E.D.; Wu, Y.-C. Hybrid N-Type Poly-Si Ultra-Thin Nanowire Shell Channel with P-Substrate Structure by Electron Beam Lithography Adjustment for Junctionless Field-Effect Transistors. ECS J. Solid State Sci. Technol. 2018, 7, Q201–Q205. [Google Scholar] [CrossRef]

- Liu, C.; Cheng, C.-H.; Lin, M.-H.; Shih, Y.-J.; Hung, Y.-W.; Fan, C.-C.; Chen, H.-H.; Chen, W.-H.; Hsu, C.-C.; Shih, B.-Y. Improved Thermal Stability and Stress Immunity in Highly Scalable Junctionless FETs Using Enhanced-Depletion Channels. ECS J. Solid State Sci. Technol. 2018, 7, Q242–Q245. [Google Scholar] [CrossRef]

- Cho, W.-J. Characterizations of interface-state density between top silicon and buried oxide on Nano-SOI substrate by using pseudo-MOSFETs. JSTS J. Semicond. Technol. Sci. 2005, 5, 83–88. [Google Scholar]

- Pai, C.-Y.; Lin, J.-T.; Wang, S.-W.; Lin, C.-H.; Kuo, Y.-S.; Eng, Y.-C.; Lin, P.-H.; Fan, Y.-H.; Tai, C.-H.; Chen, H.-H. Numerical study of performance comparison between junction and junctionless thin-film transistors. In Proceedings of the 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, 1–4 November 2010; pp. 1410–1412. [Google Scholar]

- Powell, M. Charge trapping instabilities in amorphous silicon-silicon nitride thin-film transistors. Appl. Phys. Lett. 1983, 43, 597–599. [Google Scholar] [CrossRef]

- Deane, S.; Wehrspohn, R.; Powell, M. Unification of the time and temperature dependence of dangling-bond-defect creation and removal in amorphous-silicon thin-film transistors. Phys. Rev. Ser. B 1998, 58, 12625–12628. [Google Scholar] [CrossRef]

- Larki, F.; Dehzangi, A.; Ali, S.H.M.; Jalar, A.; Islam, M.; Majlis, B.Y.; Saion, E.B.; Hamidon, M.N.; Hutagalung, S.D. Dependency of electrical characteristics on nano gap variation in pinch off lateral gate transistors. In Proceedings of the 2014 IEEE International Conference on Semiconductor Electronics (ICSE), Kuala Lumpur, Malaysia, 27–29 August 2014; pp. 170–173. [Google Scholar]

| Parameter | Value |

|---|---|

| Gate length (LG) | 50, 200, 300, 400 nm |

| Gate Gap (GG) | 50, 100, 150 nm |

| Contact work function | 5.12 eV |

| Gate voltage | −2 V to +2 V |

| Drain Voltage | −0.05 V to −1 V |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Larki, F.; Islam, M.S.; Dehzangi, A.; Tariqul Islam, M.; Wong, H.Y. Effect of lateral Gate Design on the Performance of Junctionless Lateral Gate Transistors. Electronics 2019, 8, 538. https://doi.org/10.3390/electronics8050538

Larki F, Islam MS, Dehzangi A, Tariqul Islam M, Wong HY. Effect of lateral Gate Design on the Performance of Junctionless Lateral Gate Transistors. Electronics. 2019; 8(5):538. https://doi.org/10.3390/electronics8050538

Chicago/Turabian StyleLarki, Farhad, Md Shabiul Islam, Arash Dehzangi, Mohammad Tariqul Islam, and Hin Yong Wong. 2019. "Effect of lateral Gate Design on the Performance of Junctionless Lateral Gate Transistors" Electronics 8, no. 5: 538. https://doi.org/10.3390/electronics8050538

APA StyleLarki, F., Islam, M. S., Dehzangi, A., Tariqul Islam, M., & Wong, H. Y. (2019). Effect of lateral Gate Design on the Performance of Junctionless Lateral Gate Transistors. Electronics, 8(5), 538. https://doi.org/10.3390/electronics8050538