Dependable Control for Wireless Distributed Control Systems

Abstract

:1. Introduction

2. Related Work

2.1. Wireless Networks for Industrial Control

2.2. Packet Loss Compensation

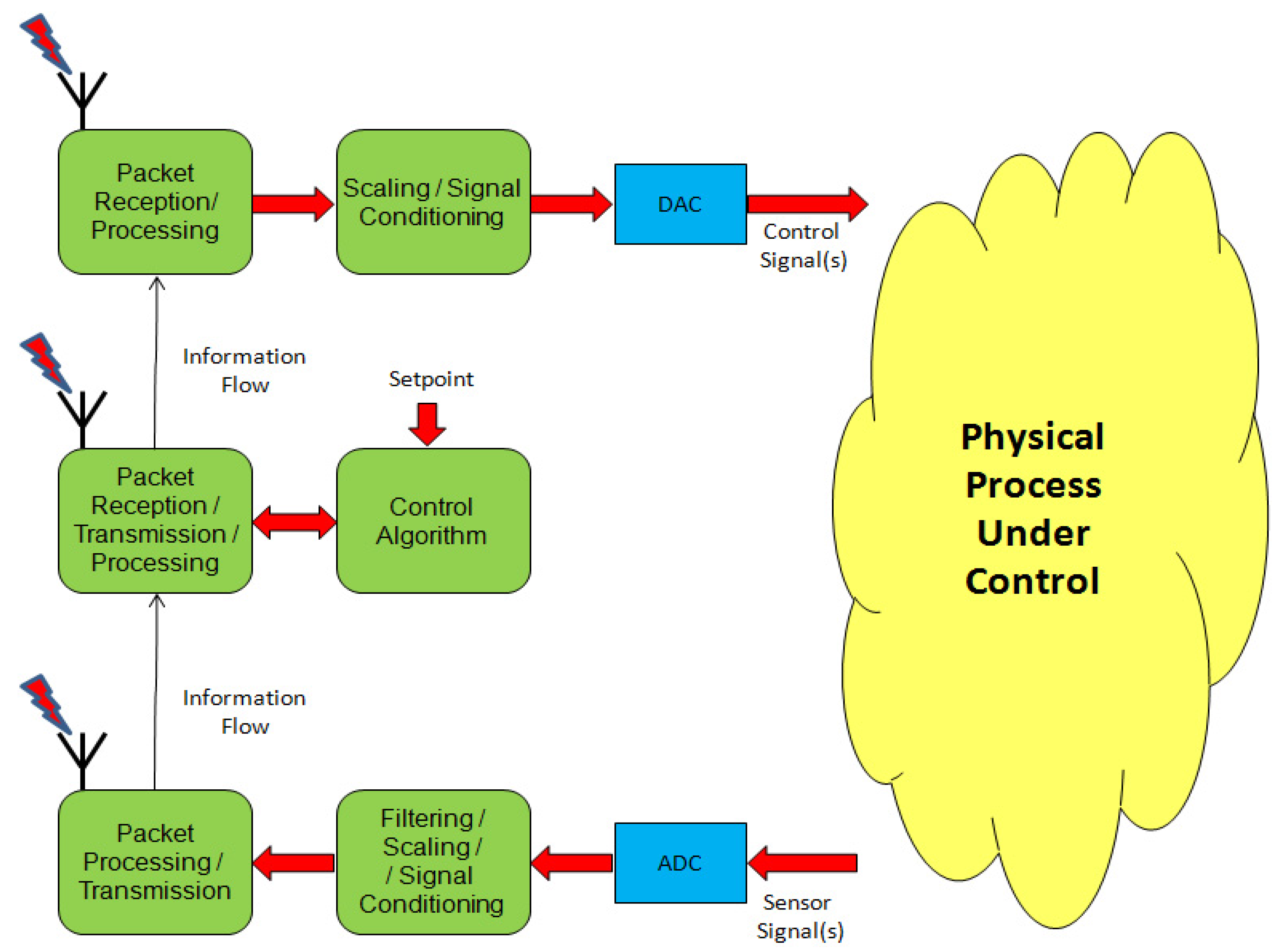

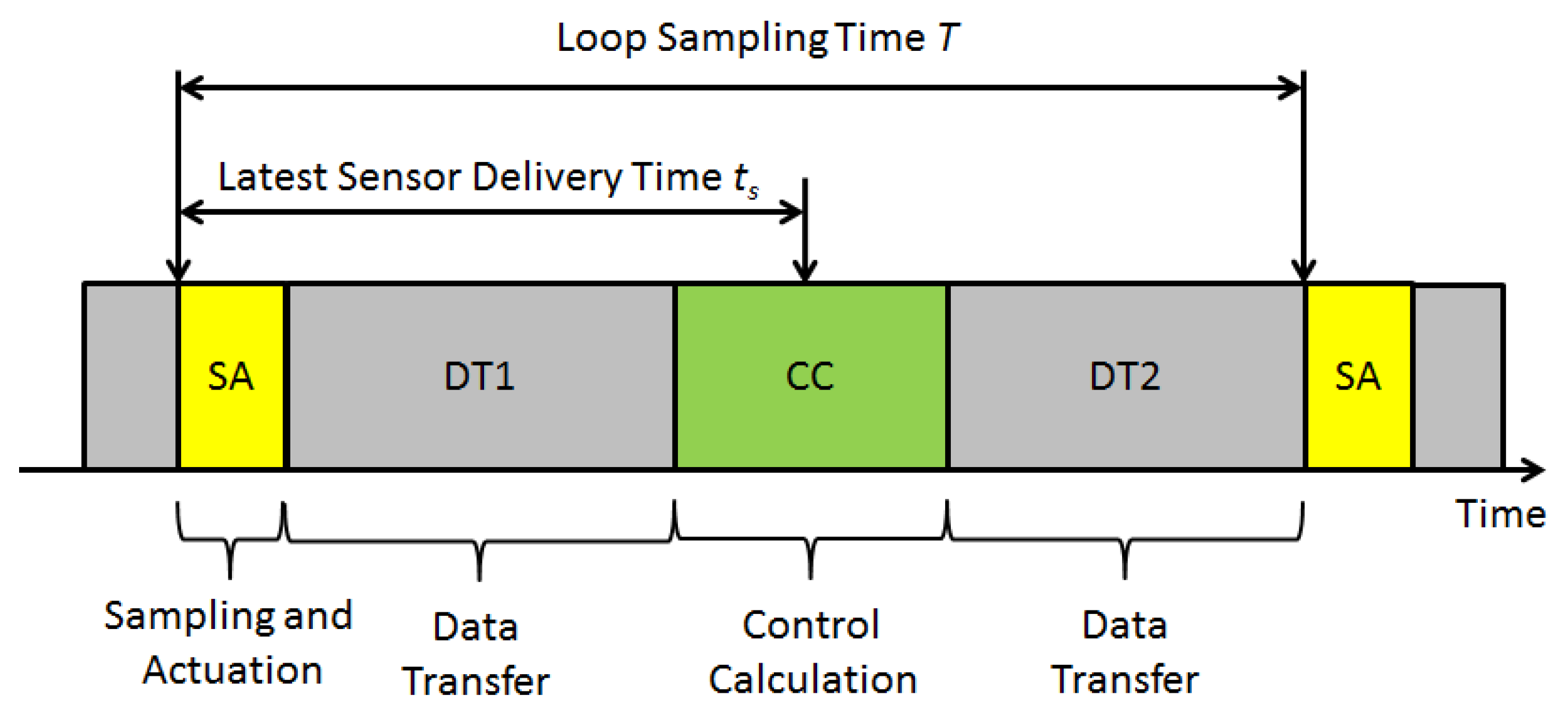

3. General Configuration and Assumptions

4. Sensor Packet Loss Compensation

4.1. Principle

4.2. CARIMA Process Model

4.3. Packet Loss Compensation

4.4. Adaptive Parameter Updating

4.5. Practical Industrial Process Model

5. Controller Packet Loss Compensation

5.1. Principle

5.2. Adaptive Digital PID-Like Control Law

5.3. Integrating Processes

6. Computational Study

6.1. Test Facility

6.2. Experimental Design

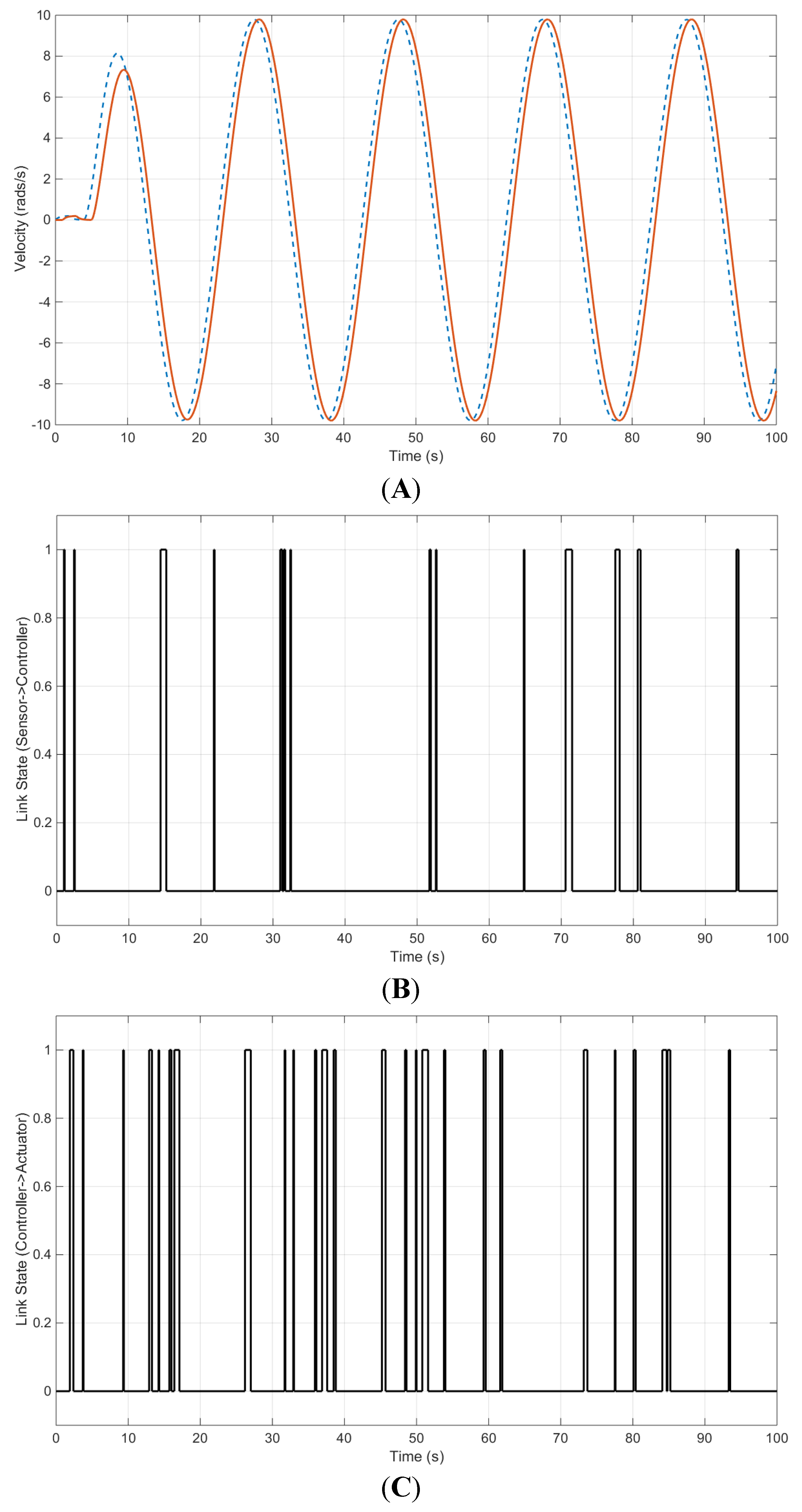

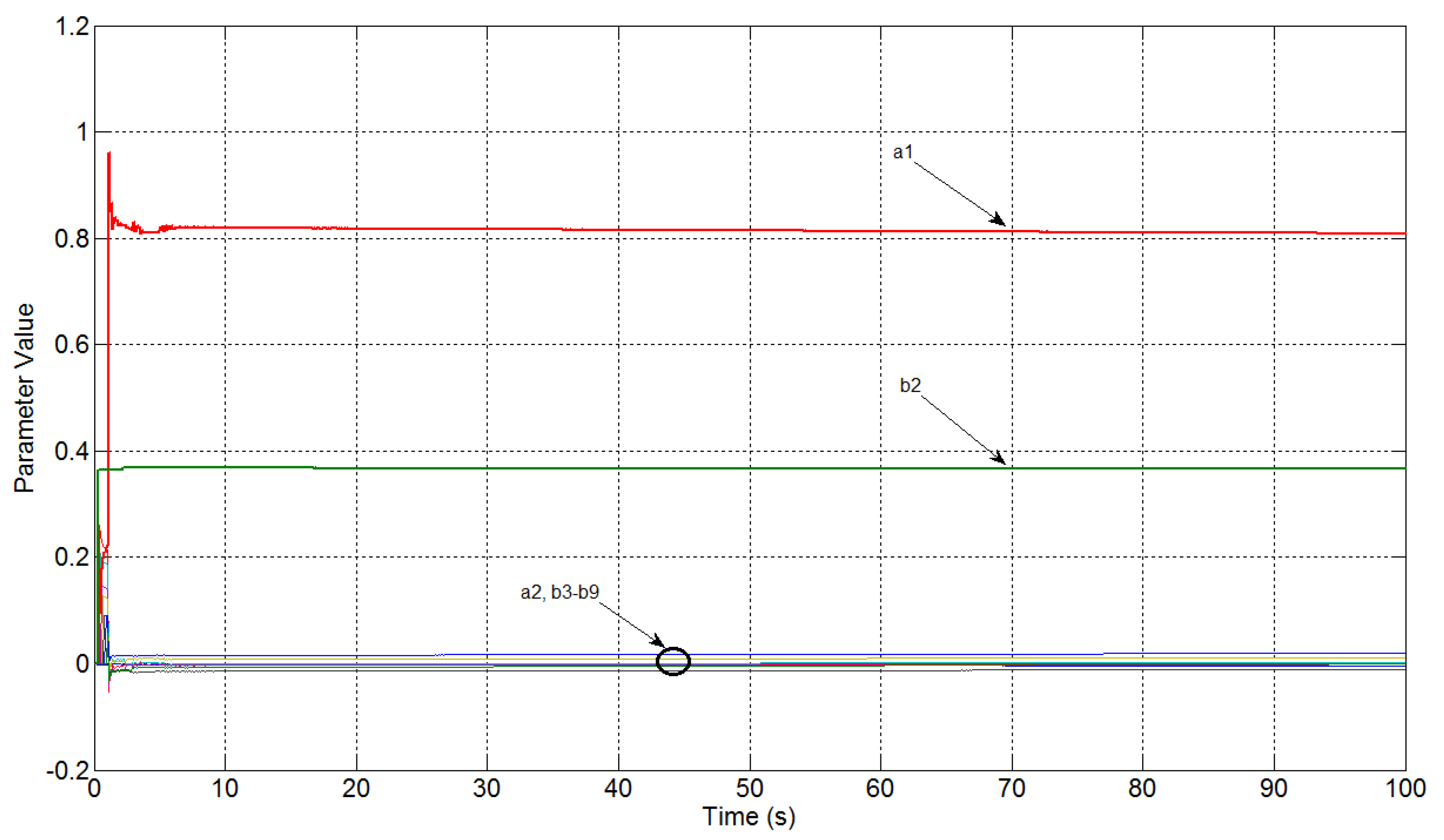

6.3. Experimental Results

| Method | ISE Ratio (%) | Exec Time (ms) |

|---|---|---|

| RC Method | 677.024 | 61.345 |

| PC Method | 319.087 | 0.268 |

7. Conclusions and Further Work

Author Contributions

Conflicts of Interest

References

- Flammini, A.; Ferrari, P.; Marioli, D.; Sissini, E.; Taroni, A. Wired and wireless sensor networks for industrial applications. Microelectron. J. 2009, 40, 1322–1336. [Google Scholar] [CrossRef]

- Thompson, H.A. Wireless and Internet communications technologies for monitoring and control. Control Eng. Pract. 2004, 12, 781–791. [Google Scholar] [CrossRef]

- Munir, S.; Lin, S.; Hoque, E.; Nirjon, S.M.S.; Stankovic, J.A.; Whitehouse, K. Addressing burstiness for reliable communication and latency bound generation in wireless sensor networks. In Proceedings of the 9th ACM/IEEE International Conference on Information Processing in Sensor Networks (IPSN), Stockholm, Sweden, 12–15 April 2010; pp. 303–314.

- Ikram, W.; Thornhill, N.F. Wireless communication in process automation: A survey of opportunities, requirements, concerns and challenges. In Proceedings of the 8th UK Automatic Control Conference (UKACC), Coventry, UK, 7–10 September 2010.

- Oliver, R.S.; Fohler, G. Timeliness in wireless sensor networks: Common misconceptions. In Proceedings of the 9th International Workshop on Real-Time Networks (RTN), Brussels, Belgium, 6 July 2010.

- Ghostine, R.; Thiriet, J.M.; Aubry, J.F. Variable delays and message losses: Influence on the reliability of a control loop. Reliab. Eng. Syst. Saf. 2011, 96, 160–171. [Google Scholar] [CrossRef]

- Rothmensen, S. The reality of wireless real-time: Wireless networks in industrial automation. In Proceedings of the Keynote Speech at the 9th International Workshop on Real-Time Networks (RTN), Brussels, Belgium, 6 July 2010.

- Suriyachai, P.; Brown, J.; Roedig, U. Time-critical data delivery in wireless sensor networks. In Proceedings of the International Conference on Distributed Computing in Sensor Systems (DCOSS10), Santa Barbara, CA, USA, 21–23 June 2010; pp. 216–229.

- Gamba, G.; Tramarin, F.; Willig, A. Retransmission strategies for cyclic polling over wireless channels in the presence of interference. IEEE Trans. Ind. Inform. 2010, 6, 405–415. [Google Scholar] [CrossRef]

- Gobriel, S.; Cleric, R.; Mosse, D. Adaptations of TDMA scheduling for wireless sensor networks. In Proceedings of the 7th International Workshop on Real-Time Networks, Prague, Czech Republic, 1 July 2009.

- Costa, R.; Portugal, P.; Vasques, F.; Moraes, R. A TDMA-based mechanism for real-time communication in IEEE 802.11e networks. In Proceedings of the 15th IEEE International Conference on Emerging Technologies and Factory Automation, Bilbao, Spain, 14–17 September 2010.

- Boggia, G.; Camarda, P.; Grieco, L.A.; Zacheo, G. Toward wireless networked control systems: An experimental study on real-time communications in 802.11 WLANs. In Proceedings of the 2008 IEEE Workshop on Factory Communications Systems, Dresden, Germany, 21–23 May 2008; pp. 149–155.

- Jonsson, M.; Kunert, K. Towards reliable wireless industrial communication with real-time guarantees. IEEE Trans. Ind. Inform. 2009, 5, 429–442. [Google Scholar] [CrossRef]

- Short, M.; Abrar, U.; Abugchem, F. Application level compensation for burst errors in wireless control networks. In Proceedings of the 17th IEEE International Conference on Emerging Technology & Factory Automation, Krakow, Poland, 17–21 September 2012.

- Bennett, S. Real-Time Computer Control: An Introduction; Pearson Education Limited: New York, NY, USA, 1988. [Google Scholar]

- Vasyutynskyy, V.; Kabitzsch, K. Event-based control: Overview and generic model. In Proceedings of the 2010 IEEE Workshop on Factory Communications Systems, Nancy, France, 21–23 May 2010; pp. 271–279.

- Chen, D.; Nixon, M.; Mok, A. WirelessHART: Real-Time Mesh Network for Industrial Automation; Springer-Verlag: London, UK, 2010. [Google Scholar]

- Ferreira, J.; Oliveira, A.; Fonseca, P.; Fonseca, J.A. An experiment to assess bit error rate in CAN. In Proceedings of the 3rd International Workshop on Real-Time Networks (RTN), Catania, Sicily, Italy, 30 June 2004.

- Wang, C.X.; Xu, W. Packet-level error models for digital wireless channels. In Proceedings of the IEEE International Conference on Communications, Seoul, Korea, 16–20 May 2005; pp. 2184–2189.

- Willig, A. A new class of packet- and bit-level error models for wireless channels. In Proceedings of the IEEE International Symposium on Personal, Indoor & Mobile Radio Communications, Lisbon, Portugal, 15–18 September 2002.

- Chaloub, G.; Diab, R; Mission, M. HMC-MAC protocol for high data rate wireless sensor networks. Electronics 2015, 4, 359–379. [Google Scholar] [CrossRef]

- Tian, Y.C.; Levy, D. Compensation for control packet dropout in networked control systems. Inf. Sci. 2008, 178, 1263–1278. [Google Scholar] [CrossRef] [Green Version]

- Short, M.; Dawood, M.; Insaurralde, C. Fault-tolerant generator telecontrol over a microgrid IP network. In Proceedings of the 20th IEEE International Conference on Emerging Technologies and Factory Automation, Luxembourg City, Luxembourg, 8–11 September 2015.

- Li, J.N.; Er, M.J.; Tan, Y.K.; Yu, H.B.; Zeng, P. Adaptive sampling rate control for networked systems based on statistical characteristics of packet disordering. ISA Trans. 2015, in press. [Google Scholar] [CrossRef] [PubMed]

- Årzén, K.E.; Cervin, A.; Eker, J.; Sha, L. An introduction to control and scheduling co-design. In Proceedings of the 39th IEEE Conference on Decision & Control, Sydney, Australia, 12–15 December 2000; pp. 4865–4870.

- Honarbacht, A.; Kummert, A. WSDP: Efficient, yet reliable, transmission of real-time sensor data over wireless networks. EWSN 2004. [Google Scholar] [CrossRef]

- Astrom, K.J.; Wittenmark, B. Adaptive Control, 2nd ed.; Addison-Wesley Publishing: Reading, MA, USA, 1995. [Google Scholar]

- Fortescue, T.R.; Kershenbaum, K.R.; Yidstie, B.E. Implementation of self-tuning regulators with variable forgetting factors. Automatica 1981, 17, 831–835. [Google Scholar] [CrossRef]

- Camacho, E.F.; Bordons, C. Model Predictive Control, 2nd ed.; Springer-Verlag: London, UK, 2003. [Google Scholar]

- Vogel, E.F.; Edgar, T.F. Application of an adaptive pole-zero placement controller to chemical processes with variable dead time. In the Proceeding of the American Control Conference, Arlington, VA, USA, 14–16 June 1982; pp. 536–544.

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Short, M.; Abugchem, F.; Abrar, U. Dependable Control for Wireless Distributed Control Systems. Electronics 2015, 4, 857-878. https://doi.org/10.3390/electronics4040857

Short M, Abugchem F, Abrar U. Dependable Control for Wireless Distributed Control Systems. Electronics. 2015; 4(4):857-878. https://doi.org/10.3390/electronics4040857

Chicago/Turabian StyleShort, Michael, Fathi Abugchem, and Usama Abrar. 2015. "Dependable Control for Wireless Distributed Control Systems" Electronics 4, no. 4: 857-878. https://doi.org/10.3390/electronics4040857

APA StyleShort, M., Abugchem, F., & Abrar, U. (2015). Dependable Control for Wireless Distributed Control Systems. Electronics, 4(4), 857-878. https://doi.org/10.3390/electronics4040857