A 12 dBm B1dB N-Path Notch Filter for Transmitter Leakage Suppression in Wideband Receiver

Abstract

1. Introduction

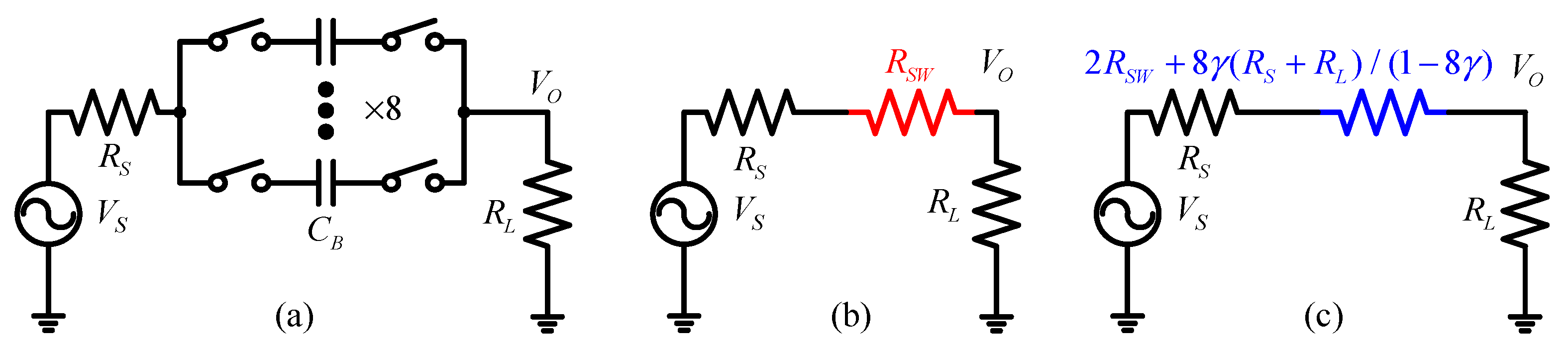

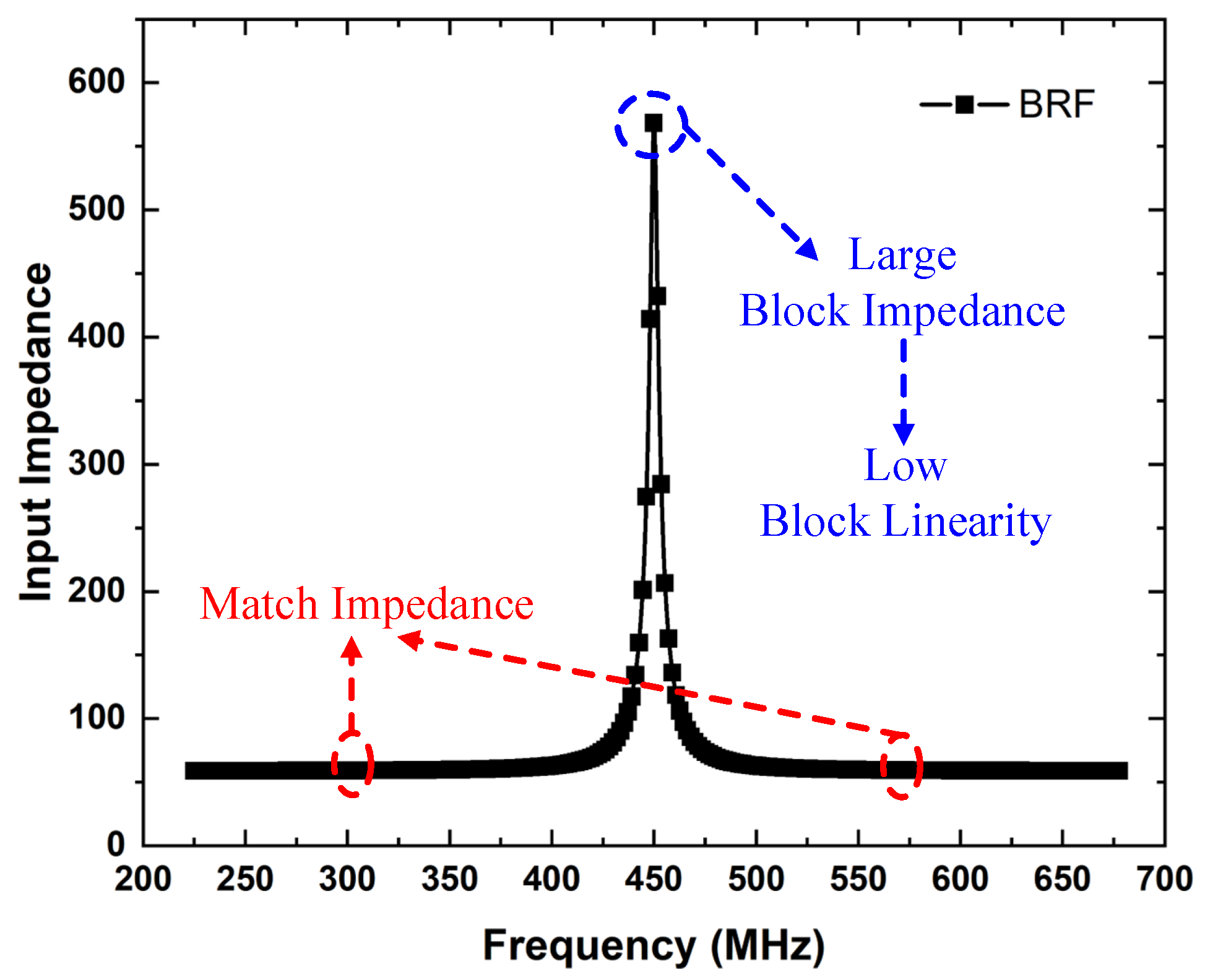

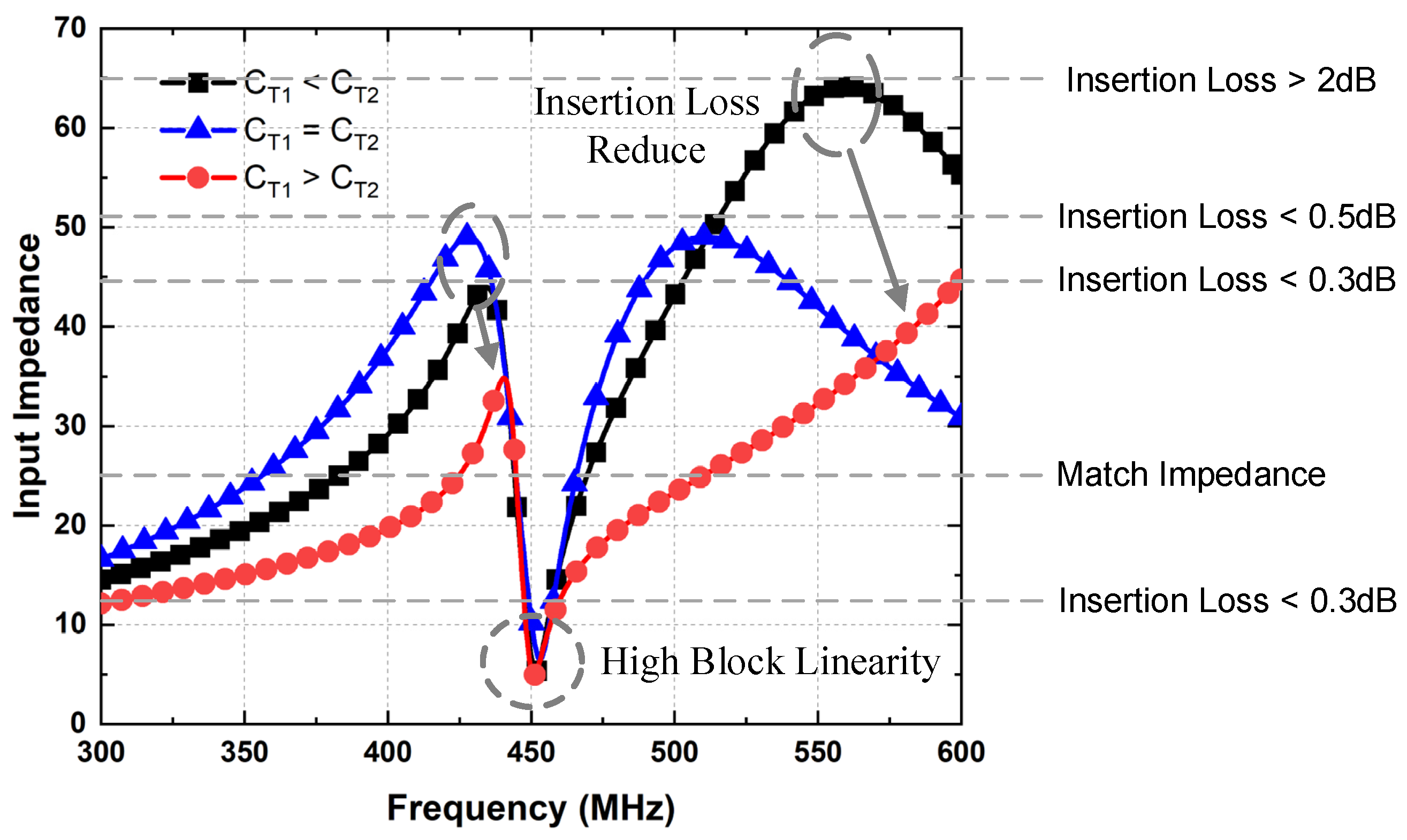

2. Basic Design of N-Path Notch Filter

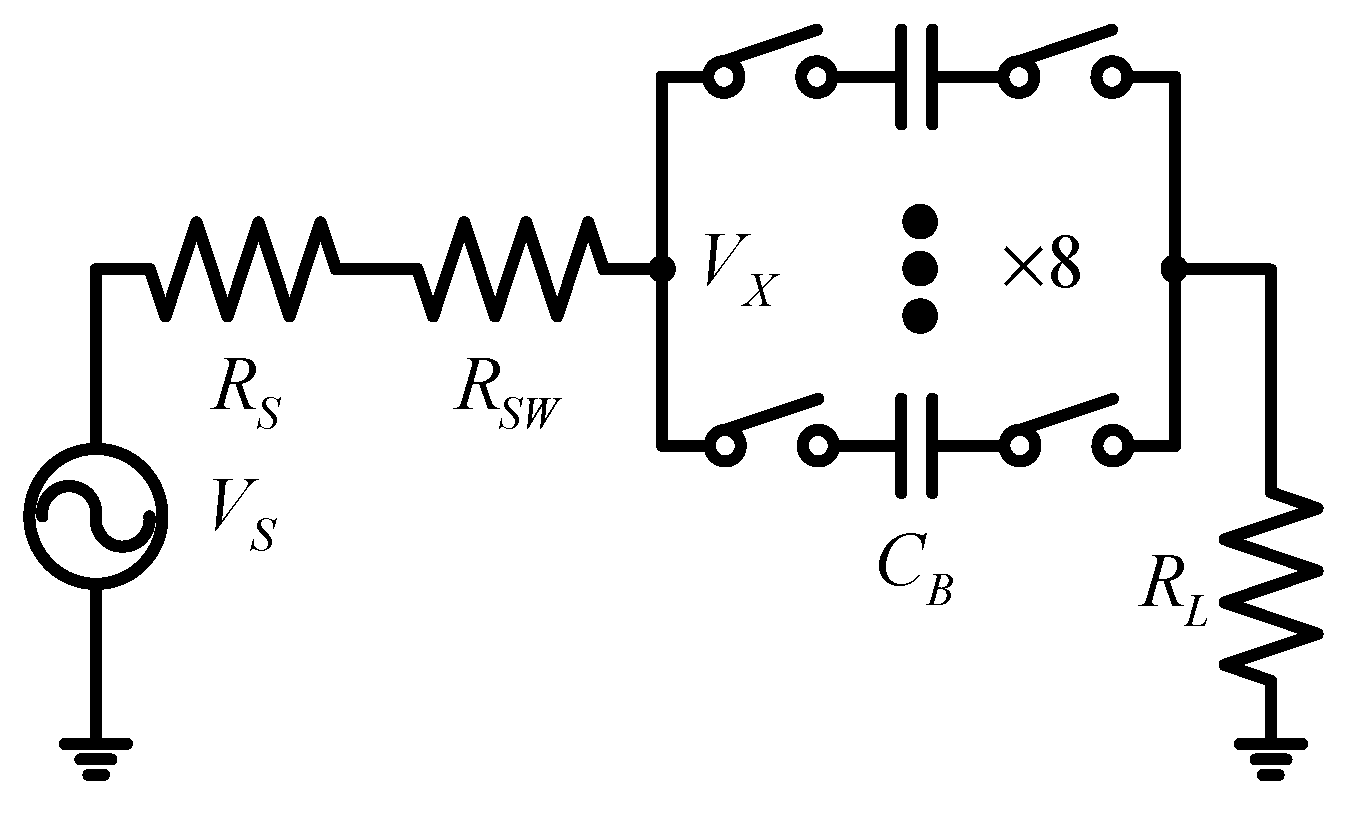

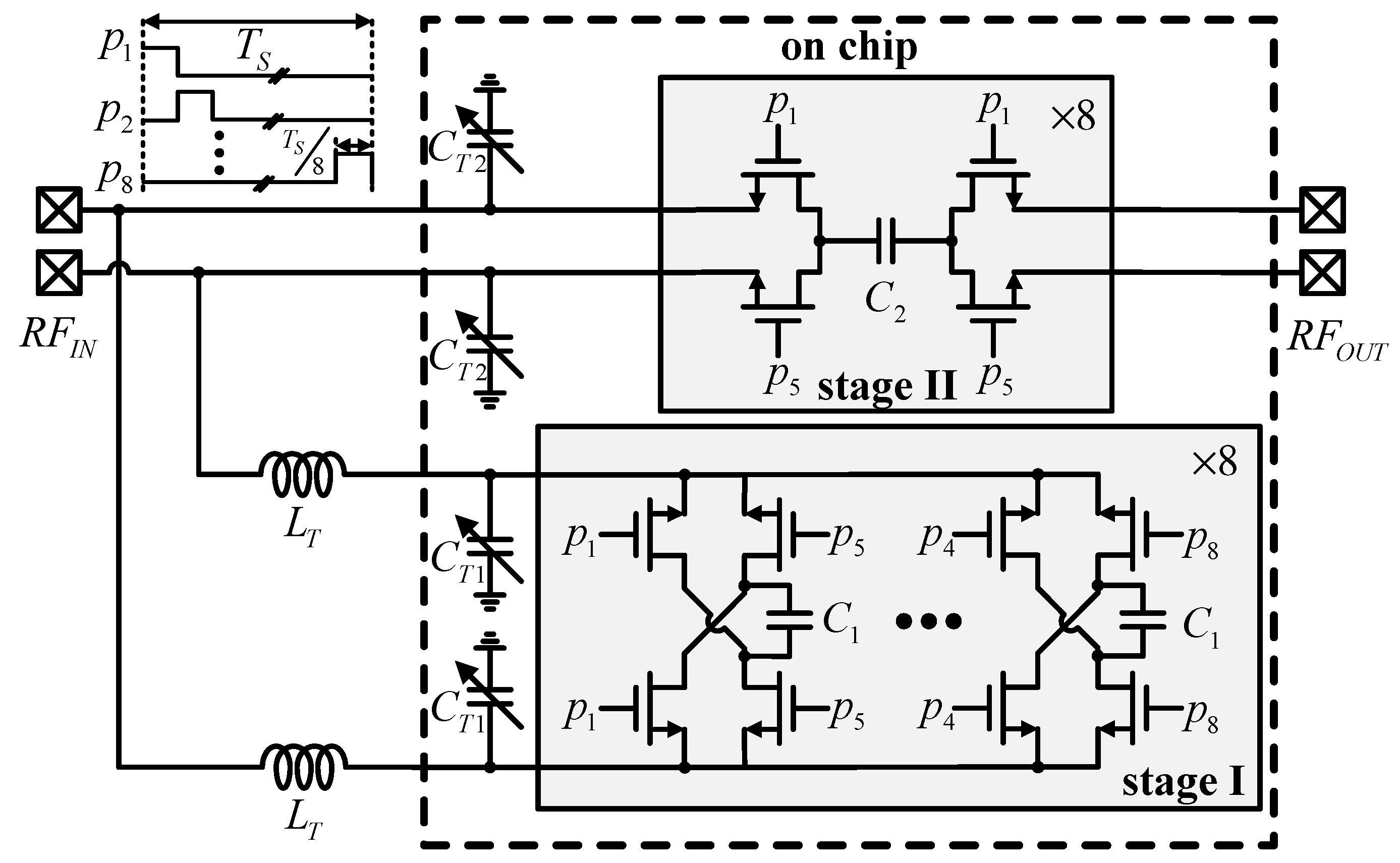

3. Proposed N-Path Notch Filter Architecture

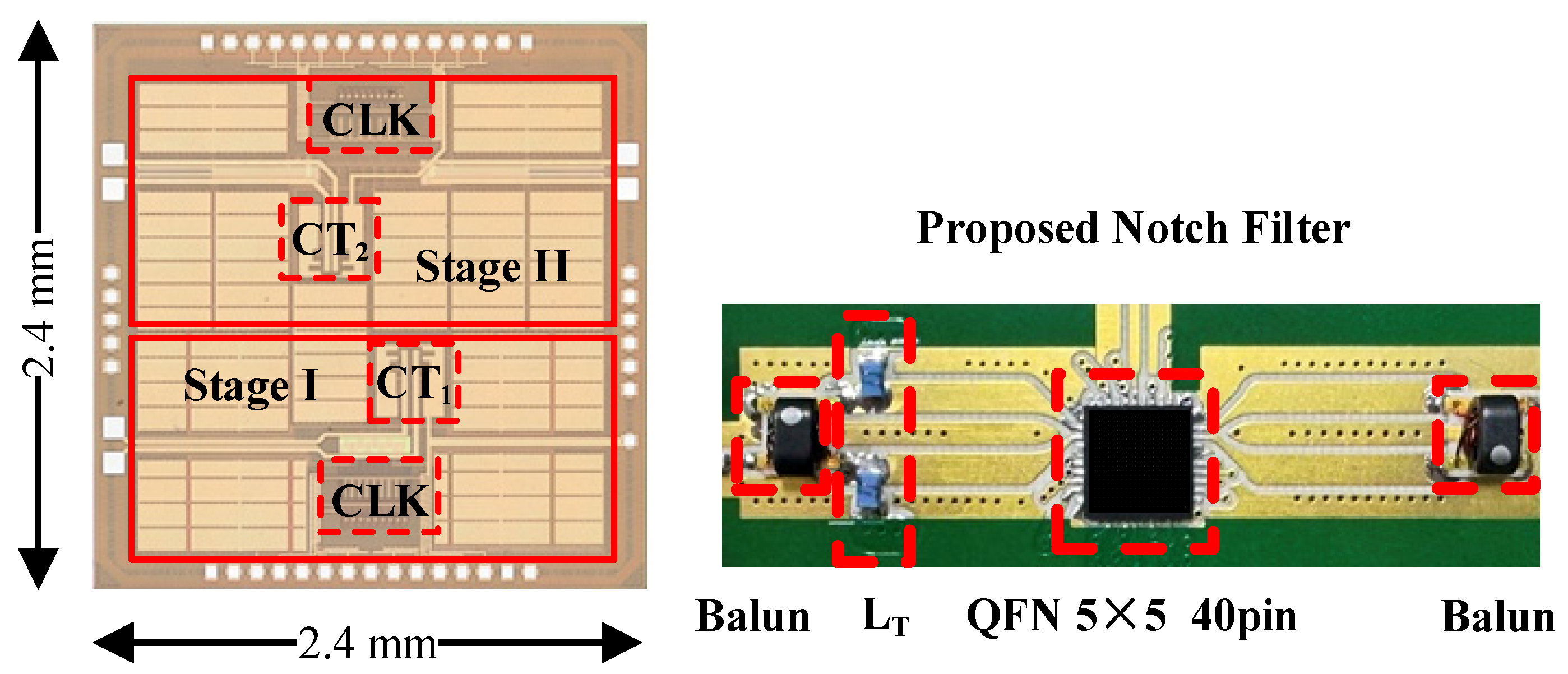

4. Circuit Implementation

4.1. N-Path Filter Architecture of Stage I and Stage II

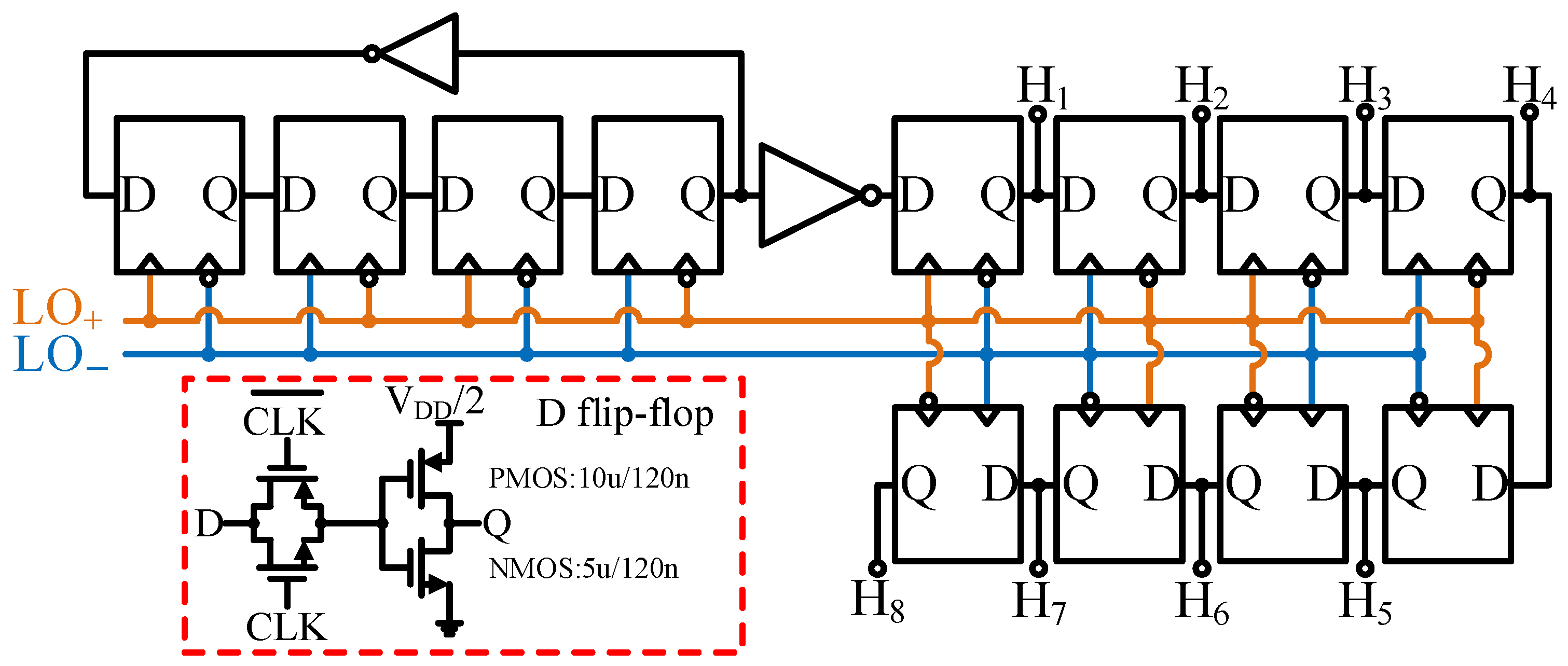

4.2. Eight-Phase 12.5% Duty Cycle Clock Generator

4.2.1. Divider

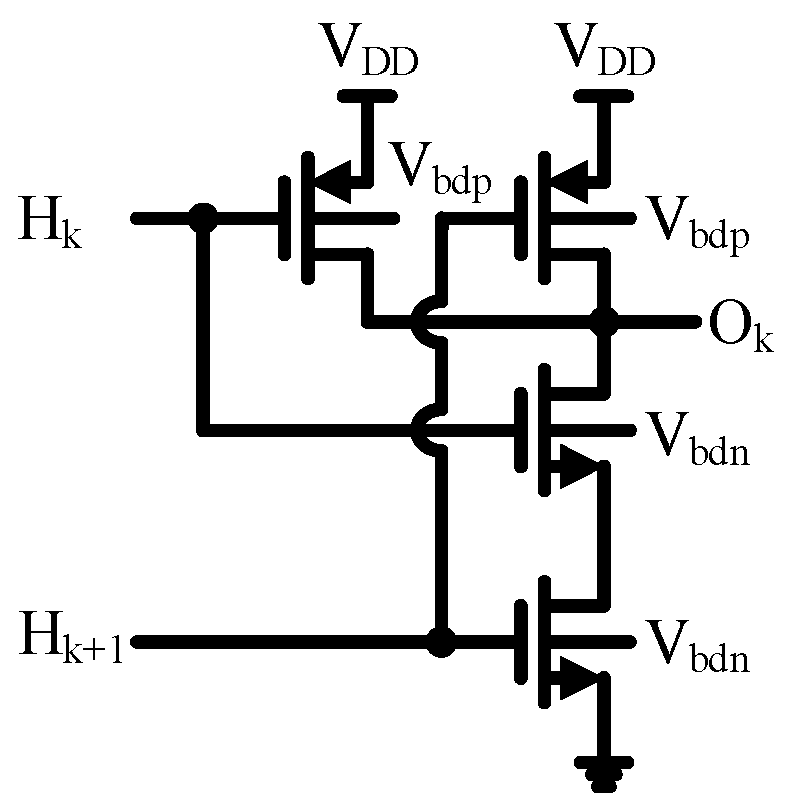

4.2.2. NAND and Duty Cycle Calibration

4.3. Off-Chip LC Equivalent Model

5. Measurement Results

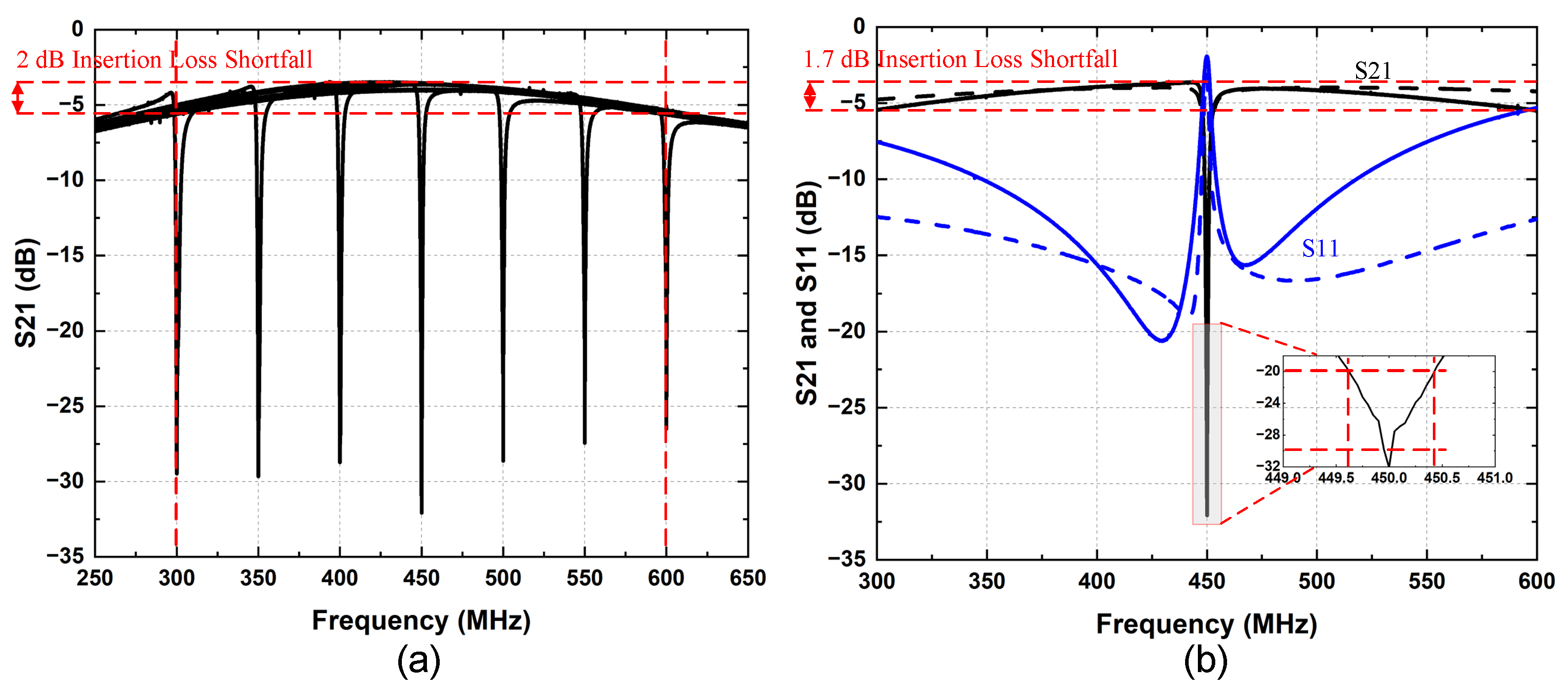

5.1. S-Parameters

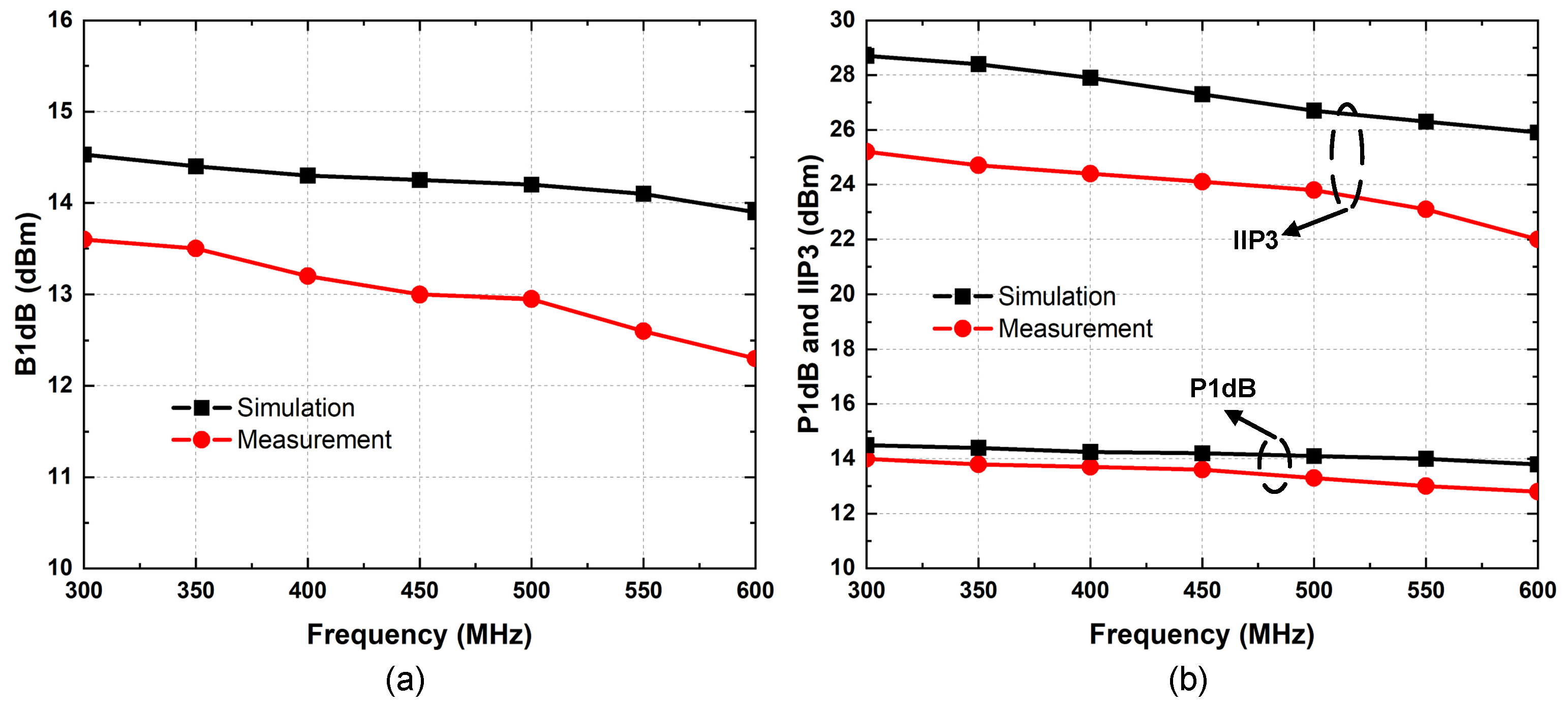

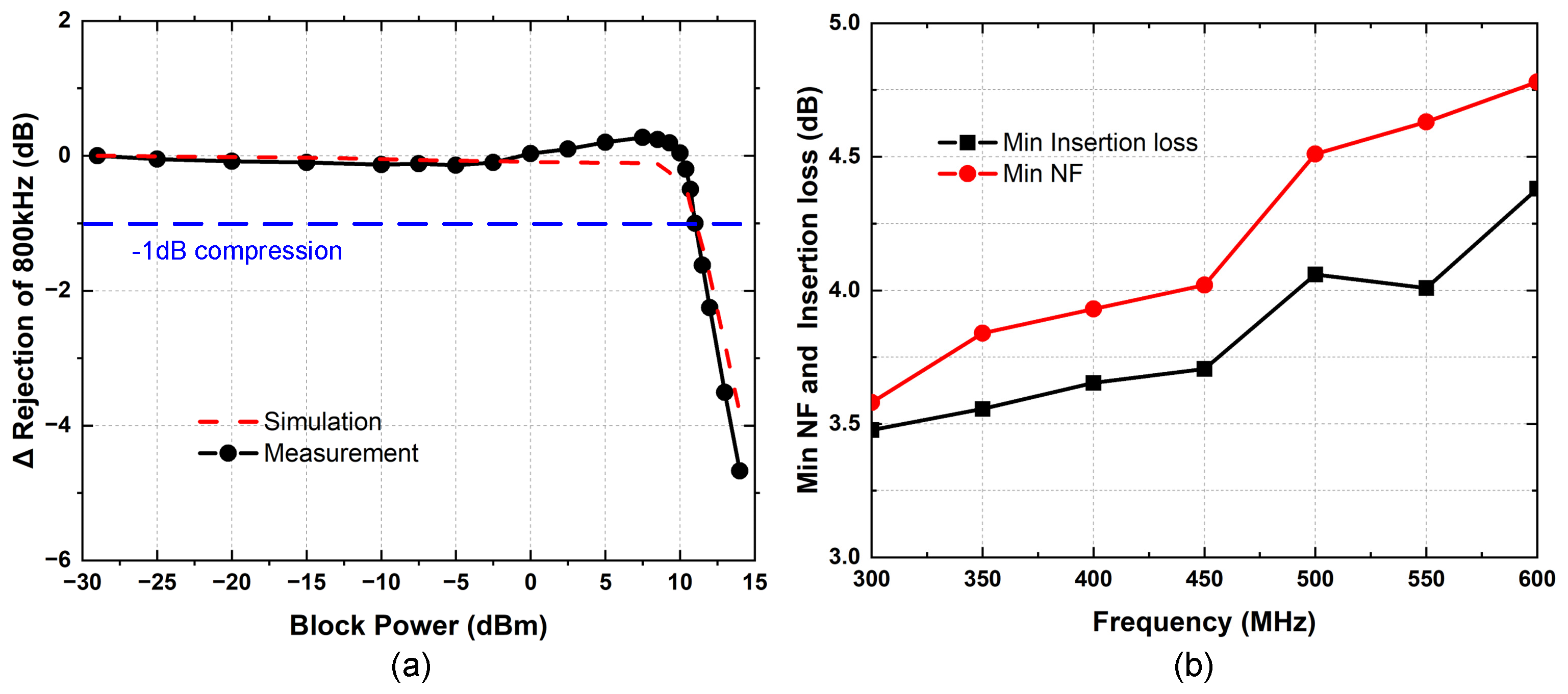

5.2. Linearity and NF

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| TX | Transmitter |

| RX | Receiver |

| B1dB | Blocker 1 dB compression point |

| P1dB | 1 dB compression point |

| IIP3 | Third-order input intercept point |

| SAW | Surface acoustic wave |

| BAW | Bulk acoustic wave |

| SC | Switched capacitor |

| BRF | Band reject filters |

| BPF | Bandpass filter |

| LO | Local oscillator |

| Vgs | Gate-to-source voltage |

| PCB | Printed circuit board |

| NF | Noise figure |

| BNF | Blocker noise figure |

References

- Gao, C.; Zheng, Y.; Li, H.; Ren, Y.; Gu, X.; Huang, X.; Wang, Y.; Qu, Y.; Liu, Y.; Cai, Y.; et al. Design and Fabrication of a Film Bulk Acoustic Wave Filter for 3.0 GHz–3.2 GHz S-Band. Sensors 2024, 24, 2939. [Google Scholar] [CrossRef] [PubMed]

- Li, G.; Xu, W.; Nan, J.; Gao, M. Design of Efficient Concurrent Dual-Frequency Doherty Power Amplifier Based on Step Impedance Low-Pass Filter. Electronics 2023, 12, 4092. [Google Scholar] [CrossRef]

- Lin, Y.-S.; Huang, C.-Y.; Huang, C.-T.; Chang, J.-F.; Tien, N.-W.; Chuang, Y.-H. Design and Analysis of Complementary Metal–Oxide–Semiconductor Single-Pole Double-Throw Switches for 28 GHz 5G New Radio. Electronics 2023, 12, 4156. [Google Scholar] [CrossRef]

- Chen, R.; Sheng, Q.; Zhou, L.; Chen, C.; Zhang, H. High-Q Bandpass-to-Bandstop Reconfigurable Filter Based on SAW Resonators. In Proceedings of the 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 4–6 August 2020; pp. 123–126. [Google Scholar]

- Darabi, H. A Blocker Filtering Technique for SAW-Less Wireless Receivers. IEEE J. Solid-State Circuits 2007, 42, 2766–2773. [Google Scholar] [CrossRef]

- Safarian, A.; Shameli, A.; Rofougaran, A.; Rofougaran, M.; de Flaviis, F. Integrated Blocker Filtering RF Front Ends. In Proceedings of the 2007 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Honolulu, HI, USA, 3–5 June 2007; pp. 13–16. [Google Scholar]

- Ghaffari, A.; Klumperink, E.A.M.; Nauta, B. Tunable N-Path Notch Filters for Blocker Suppression: Modeling and Verification. IEEE J. Solid-State Circuits 2013, 48, 1370–1382. [Google Scholar] [CrossRef]

- Lin, Z.; Mak, P.-I.; Martins, R.P. Analysis and Modeling of a Gain-Boosted N-Path Switched-Capacitor Bandpass Filter. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 2560–2568. [Google Scholar] [CrossRef]

- Qi, G.; Mak, P.-I. A 0.5-to-1.5 GHz BW-Extended Gain-Boosted N-Path Filter Using a Switched gm−C Network Achieving 50 MHz BW and 18.2dBm OB-IIP3. In Proceedings of the 2023 IEEE Asian Solid-State Circuits Conference (A-SSCC), Haikou, China, 5–8 November 2023; pp. 1–3. [Google Scholar]

- Klumperink, E.A.M.; Westerveld, H.J.; Nauta, B. N-path filters and mixer-first receivers: A review. In Proceedings of the 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 30 April–3 May 2017; pp. 1–8. [Google Scholar]

- Haq, T.; Koziel, S.; Pietrenko-Dabrowska, A. Resonator-Loaded Waveguide Notch Filters with Broad Tuning Range and Additive-Manufacturing-Based Operating Frequency Adjustment Procedure. Electronics 2023, 12, 4486. [Google Scholar] [CrossRef]

- Luo, C.-K.; Gudem, P.S.; Buckwalter, J.F. A 0.2–3.6-GHz 10-dBm B1dB 29-dBm IIP3 Tunable Filter for Transmit Leakage Suppression in SAW-Less 3G/4G FDD Receivers. IEEE Trans. Microw. Theory Tech. 2015, 63, 3514–3524. [Google Scholar] [CrossRef]

- Dougherty, C.M.; Xue, L.; Pulskamp, J.; Bedair, S.; Polcawich, R.; Morgan, B. A 10 V Fully-Integrated Switched-Mode Step-up Piezo Drive Stage in 0.13 um CMOS Using Nested-Bootstrapped Switch Cells. IEEE J. Solid-State Circuits 2016, 51, 1475–1486. [Google Scholar] [CrossRef]

- Hasan, M.N.; Saeedi, S.; Gu, Q.J.; Sigmarsson, H.H.; Liu, X. Design Methodology of N-Path Filters with Adjustable Frequency, Bandwidth, and Filter Shape. IEEE Trans. Microw. Theory Tech. 2018, 66, 2775–2790. [Google Scholar] [CrossRef]

- Qi, G.; Mak, P.-I.; Martins, R.P. A 0.038-mm2 SAW-Less Multiband Transceiver Using an N-Path SC Gain Loop. IEEE J. Solid-State Circuits 2017, 52, 2055–2070. [Google Scholar] [CrossRef]

- Andrews, C.; Molnar, A.C. Implications of Passive Mixer Transparency for Impedance Matching and Noise Figure in Passive Mixer-First Receivers. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 3092–3103. [Google Scholar] [CrossRef]

- Reiskarimian, N.; Krishnaswamy, H. Design of all-passive higher-order CMOS N-path filters. In Proceedings of the 2015 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Phoenix, AZ, USA, 17–19 May 2015; pp. 83–86. [Google Scholar]

- AlShammary, H.; Hill, C.; Hamza, A.; Buckwalter, J.F. A λ/4-lnverted N-path Filter in 45-nm CMOS SOI for Transmit Rejection with Code Selective Filters. In Proceedings of the 2018 IEEE/MTT-S International Microwave Symposium—IMS, Philadelphia, PA, USA, 10–15 June 2018; pp. 1370–1373. [Google Scholar]

- Pourbagheri, S.; Mayaram, K.; Fiez, T.S. A self-clocked blocker-filtering technique for SAW-less wireless applications. In Proceedings of the 2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Francisco, CA, USA, 22–24 May 2016; pp. 250–253. [Google Scholar]

- Khorshidian, M.; Reiskarimian, N.; Krishnaswamy, H. 29.4 High-Performance Isolators and Notch Filters Based on N-Path Negative Transresistance. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 446–448. [Google Scholar]

- Lee, D.; Yun, S.; Kwon, K. IIP2-Enhanced Receiver Front-End with Notch-Filtered Low-Noise Transconductance Amplifier for 5G New Radio Cellular Applications. In Proceedings of the 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Diego, CA, USA, 11–13 June 2023; pp. 25–28. [Google Scholar]

- Kim, H.; Jo, S.; Kwon, K. Channel-Selection LNA Using High-Order N-Path Feedforward Blocker Cancellation Path with Complex Poles for Advanced 5G NR FDD RX. IEEE Trans. Microw. Theory Tech. 2024, 72, 6821–6832. [Google Scholar] [CrossRef]

| With 12 dBm TX Leakage | Frequency = 0.3 GHz | Frequency = 0.6 GHz |

|---|---|---|

| Clock Balun | 7.2 | 9.1 |

| Divider | 5.1 | 8.5 |

| NANDs and Duty Cycle Calibration | 26.5 | 28.6 |

| Buffers | 147.2 | 195.8 |

| Total | 186 | 242 |

| Reference | [19] | [20] | [21] | [22] | [12] | [16] | This Work |

|---|---|---|---|---|---|---|---|

| Technology | 65 nm CMOS | 65 nm CMOS | 65 nm CMOS | 65 nm CMOS | 45 nm SOI | 45 nm SOI | 130 nm SOI |

| Topology | N-path LNA + Shunt Notch | N-path Neg. Trans-Res. Notch | LNTA + Dual-Band LC Notch | CS-LNA BPF+ FF Blocker Cancelling Notch | N-path BPF + Series Notch | N-path Inv. Shunt Notch | N-path Adjustable Inv. Shunt Notch + Series Notch |

| RF Range/GHz | 1 to 1.6 | 0.2 to 1 | 0.7 to 2.2 | 1.35 to 2.7 | 0.2 to 3.6 | 0.9 to 1.1 | 0.3 to 0.6 |

| BW/MHz | N/A | 28 (20 dB BW) | N/A | >48 | >80 | 12 to 25 (3 dB BW) | 3.5 to 4 (3 dB BW) 0.8 (20 dB BW) |

| B1dB/dBm | −10 # | 5 to 7 | −18 to −6 # | >7.5 | 10 # | N/A | 12.3 to 13.6 |

| P1dB/dBm | N/A | N/A | >−40 | N/A | 4 # | >−10 | 12.8 to 14 |

| IB IIP3/dBm | N/A | 17 to 21.5 | −14.5 | 4.8 to 5.8 | 22 | 22.6 * | 22 to 25.2 |

| Insertion Loss Shortfall/dB | <1 # | >4 # | >3 # | N/A | 2 # | >3 # | 1.7 to 2 |

| DSB NF/dB | 5 | 1 to 4 | 3.5 to 4.4 | 4.4 to 4.6 | 2.8 to 4.5 | 4 to 5 | 3.58 to 4.78 |

| Max Rejection/dB | 19 | >50 | >25 | >23.8 | 41 | 23 | 27 to 32 |

| Power Con./mW | 30 | 17 to 21.5 | 11.7 | 21.2 | 183.3 to 303.5 ‡ | 6.18 | 186 to 242 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Luo, X.; Qi, S.; Xu, S.; Zhang, H.; Xu, Q.; Wu, G.; Zhan, L. A 12 dBm B1dB N-Path Notch Filter for Transmitter Leakage Suppression in Wideband Receiver. Electronics 2025, 14, 854. https://doi.org/10.3390/electronics14050854

Luo X, Qi S, Xu S, Zhang H, Xu Q, Wu G, Zhan L. A 12 dBm B1dB N-Path Notch Filter for Transmitter Leakage Suppression in Wideband Receiver. Electronics. 2025; 14(5):854. https://doi.org/10.3390/electronics14050854

Chicago/Turabian StyleLuo, Xujia, Shihao Qi, Shang Xu, Haotian Zhang, Qinfen Xu, Guoan Wu, and Lamin Zhan. 2025. "A 12 dBm B1dB N-Path Notch Filter for Transmitter Leakage Suppression in Wideband Receiver" Electronics 14, no. 5: 854. https://doi.org/10.3390/electronics14050854

APA StyleLuo, X., Qi, S., Xu, S., Zhang, H., Xu, Q., Wu, G., & Zhan, L. (2025). A 12 dBm B1dB N-Path Notch Filter for Transmitter Leakage Suppression in Wideband Receiver. Electronics, 14(5), 854. https://doi.org/10.3390/electronics14050854