A 5-Transistor CMOS Voltage Reference with Double Supply-Regulation

Abstract

1. Introduction

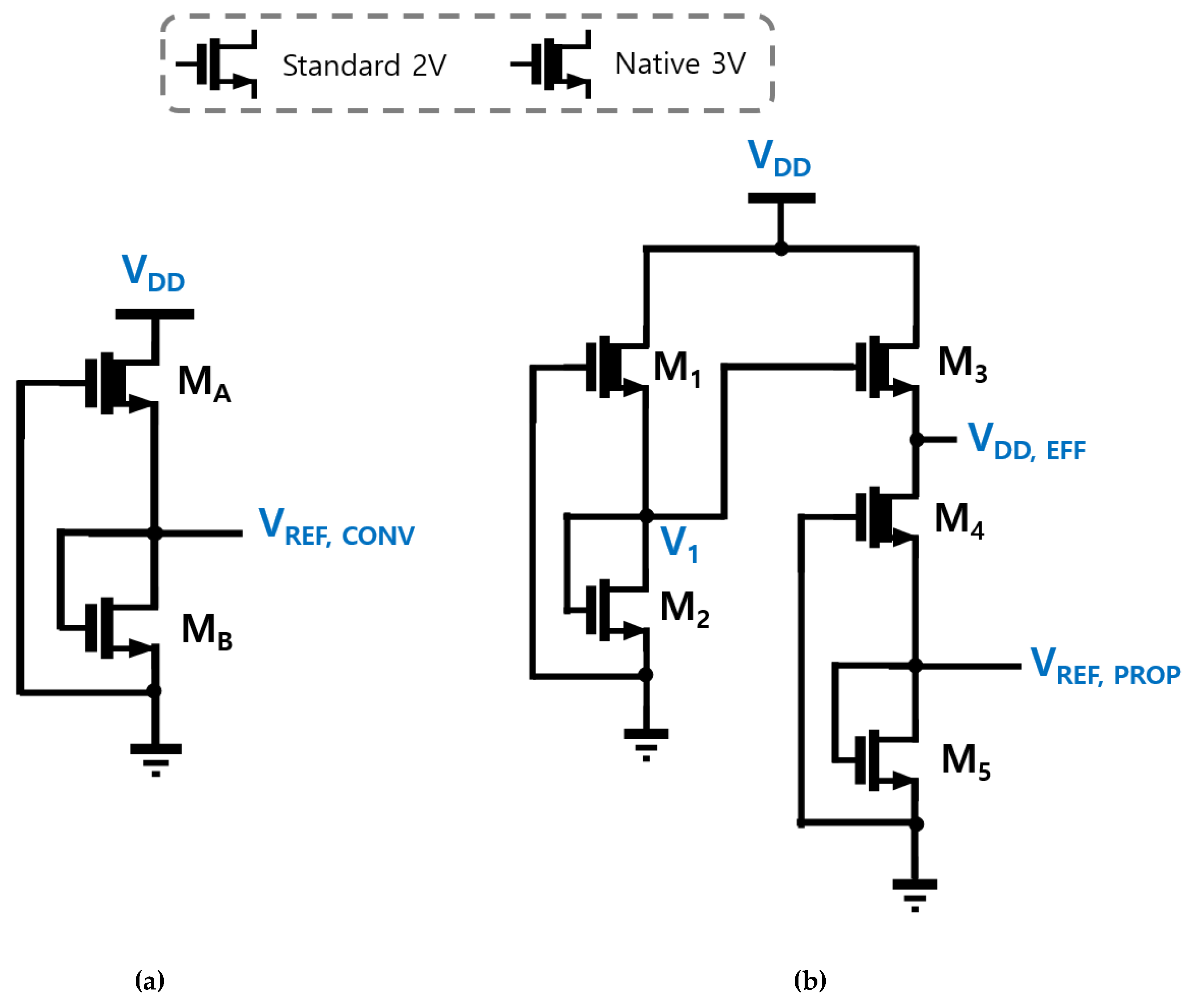

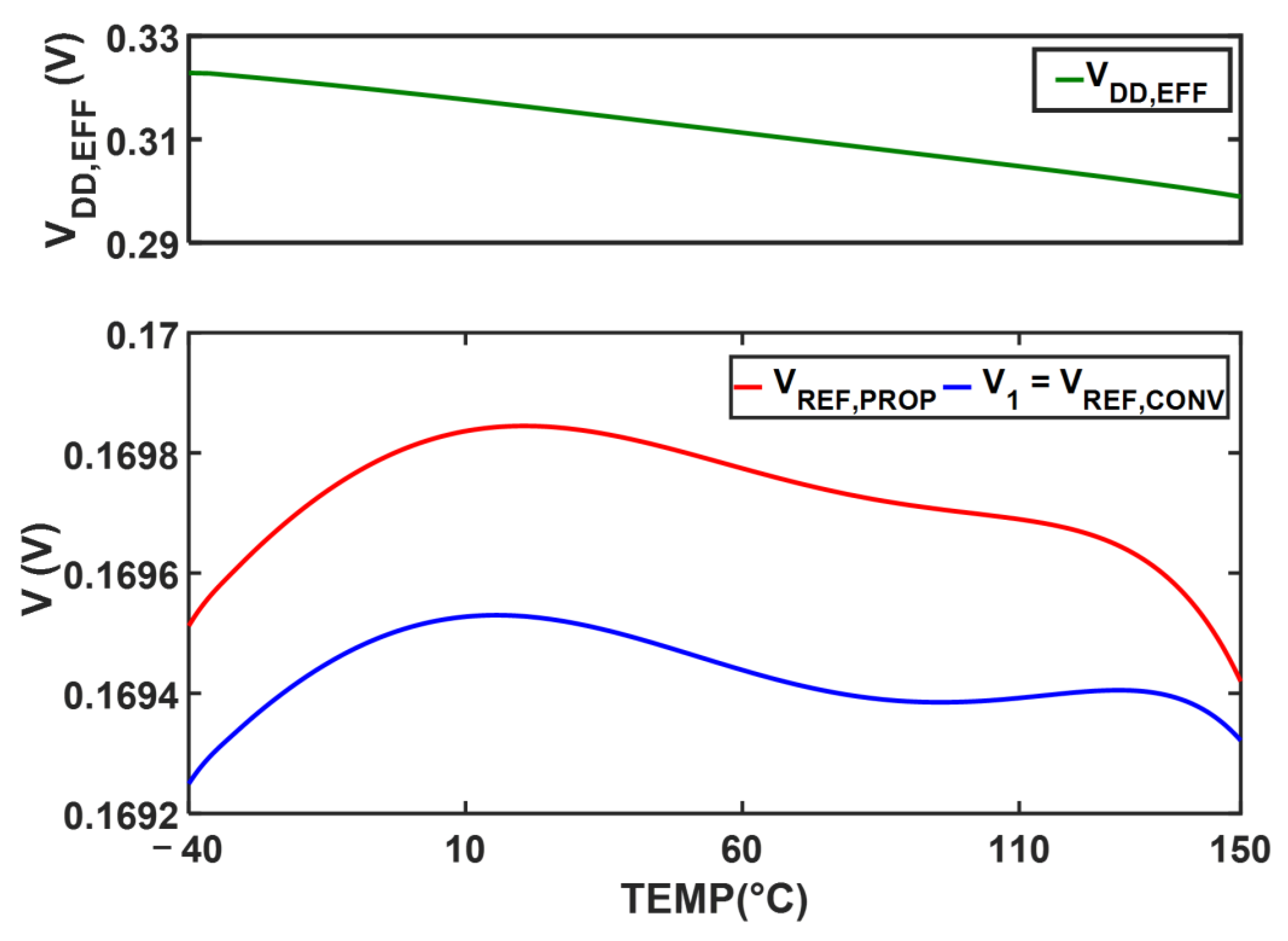

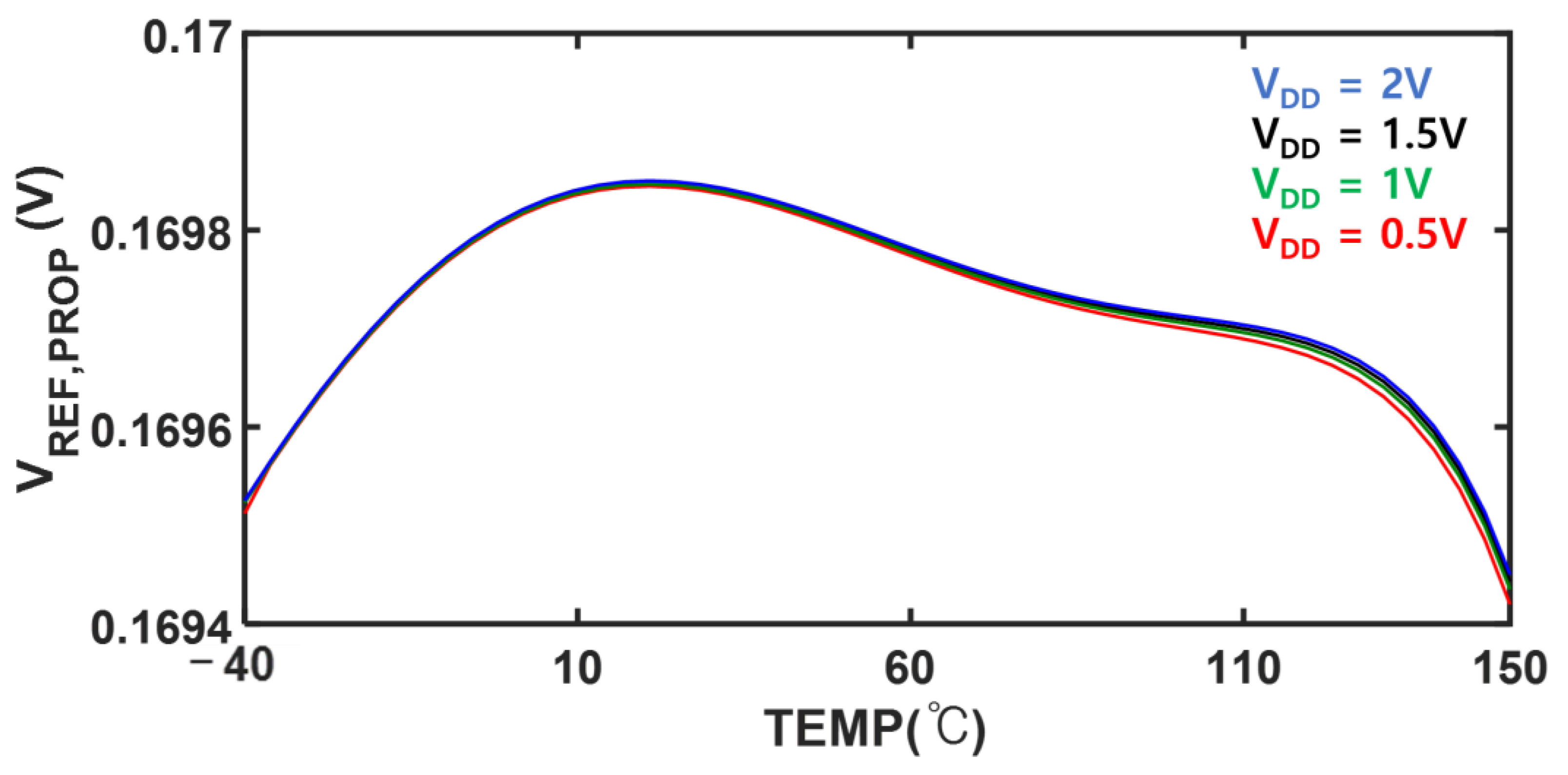

2. Proposed CR with Double Supply Regulation and Post-Layout Simulation Results on Supply Variations

3. Post-Layout Simulation Results on Process and Temperature Variations

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chen, K.; Petruzzi, L.; Hulfachor, R.; Onabajo, M. A 1.16-V 5.8-to-13.5-ppm/°C Curvature-Compensated CMOS Bandgap Reference Circuit with a Shared Offset-Cancellation Method for Internal Amplifiers. IEEE J. Solid-State Circuits 2021, 56, 267–276. [Google Scholar] [CrossRef]

- Kim, M.; Cho, S. A Single BJT Bandgap Reference with Frequency Compensation Exploiting Mirror Pole. IEEE J. Solid-State Circuits 2021, 56, 2902–2912. [Google Scholar] [CrossRef]

- Ji, Y.; Lee, J.; Kim, B.; Park, H.J.; Sim, J.Y. A 192-pW Voltage Reference Generating Bandgap-Vth with Process and Temperature Dependence Compensation. IEEE J. Solid-State Circuits 2019, 54, 3281–3291. [Google Scholar] [CrossRef]

- Lee, I.; Blaauw, D. A 31 pW-to-113 nW Hybrid BJT and CMOS Voltage Reference with 3.6% ±3σ-inaccuracy from 0 °C to 170 °C for Low-Power High-Temperature IoT Systems. In Proceedings of the Symposium on VLSI Circuits, Kyoto, Japan, 9–14 June 2019; pp. C142–C143. [Google Scholar] [CrossRef]

- Seok, M.; Kim, G.; Blaauw, D.; Sylvester, D. A Portable 2-Transistor Picowatt Temperature-Compensated Voltage Reference Operating at 0.5 V. IEEE J. Solid-State Circuits 2012, 47, 2534–2545. [Google Scholar] [CrossRef]

- Lee, I.; Sylvester, D.; Blaauw, D. A Subthreshold Voltage Reference with Scalable Output Voltage for Low-Power IoT Systems. IEEE J Solid-State Circuits 2017, 52, 1443–1449. [Google Scholar] [CrossRef]

- Huang, C.J.; Lai, Y.J.; Yang, Y.J.O.; Chen, H.W.; Kuo, C.C.; Chen, K.H.; Lin, Y.H.; Lin, S.R.; Tsai, T.Y. A 4.2 nW and 18 ppm/°C Temperature Coefficient Leakage-Based Square Root Compensation (LSRC) CMOS Voltage Reference. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 728–732. [Google Scholar] [CrossRef]

- Lin, J.; Wang, L.; Zhan, C.; Lu, Y. A 1-nW Ultra-Low Voltage Subthreshold CMOS Voltage Reference with 0.0154%/V Line Sensitivity. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1653–1657. [Google Scholar] [CrossRef]

- Wang, Y.; Sun, Q.; Luo, H.; Wang, X.; Zhang, R.; Zhang, H. A 48 pW, 0.34 V, 0.019%/V Line Sensitivity Self-Biased Subthreshold Voltage Reference with DIBL Effect Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 611–621. [Google Scholar] [CrossRef]

- Azimi, M.; Habibi, M.; Crovetti, P. A Two-Stage Sub-Threshold Voltage Reference Generator Using Body Bias Curvature Compensation for Improved Temperature Coefficient. Electronics 2024, 13, 1390. [Google Scholar] [CrossRef]

- Bialek, H.; Johnston, M.L.; Natarajan, A. A 6-Transistor Ultra-Low Power CMOS Voltage Reference with 232 0.02%/V Line Sensitivity. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), Boston, MA, USA, 22–25 March 2020; pp. 1–4, 233. [Google Scholar] [CrossRef]

- Huang, Y.; Luo, Y.; Zeng, Y. Picowatt Dual-Output Voltage Reference Based on Leakage Current Compensation and Diode-Connected Voltage Divider. Electronics 2024, 13, 3533. [Google Scholar] [CrossRef]

| Transistor | Width(μm) | Length(μm) | Current(pA) |

|---|---|---|---|

| M1 = MA | 1.1 | 18 | 628 |

| M2 = MB | 15 | 18 | 628 |

| M3 | 0.42 | 14 | 633 |

| M4 | 1.13 | 18 | 633 |

| M5 | 15 | 18 | 633 |

| Transistor | gm (nS) | ro (GΩ) |

|---|---|---|

| M1 = MA | 20.98 | 27.9 |

| M2 = MB | 17.35 | 25.2 |

| M3 | 20.51 | 18.9 |

| M4 | 21.18 | 8.34 |

| M5 | 17.51 | 25.1 |

| This Work | [5] | [6] | [7] | [8] | [9] | [10] | [11] | [12] | |

|---|---|---|---|---|---|---|---|---|---|

| Technology (nm) | 180 | 180 | 180 | 180 | 130 | 40 | 180 | 65 | 65 |

| VDD (V) | 0.5–2 | 0.5–3 | 1.4–3.6 | 0.4–1.8 | 0.5–1.8 | 0.9–1.5 | 0.5–2.1 | 0.5–1.8 | 0.4–2.5 |

| VREF (V) | 0.17 | 0.18 | 1.25 | 0.15 | 0.18 | 0.58 | 0.19 | 0.26 | 0.28 |

| Temp. Range (°C) | −40~150 | −20~80 | 0~100 | −40~150 | −20~80 | −40~150 | 0~100 | 0~100 | −10~155 |

| TC (ppm/°C) | 12 | 16.9 | 23 | 89.8 | 29* | 18* | 26.7 | 78.4 | 15.9 * |

| LS (%/V) | 0.0027 | 0.033 | 0.31 | 0.163 | 0.036 | 0.23 | 17.1 | 0.02 | 0.08 |

| PSRR (dB) Freq. (Hz) | −100.5 @100 | −53 @100 | −41 @100 | −55 @100 | −50.5 @10 | −72 @1M | −72 @10 | N/A N/A | −76.7 @100 |

| Power (pW) | 630 | 2.22 | 35 | 1000 | 2.2 | 4200 | 28.8 | 14.3 | 53.8 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jung, M.; Min, K.; Son, H.; Ji, Y. A 5-Transistor CMOS Voltage Reference with Double Supply-Regulation. Electronics 2025, 14, 588. https://doi.org/10.3390/electronics14030588

Jung M, Min K, Son H, Ji Y. A 5-Transistor CMOS Voltage Reference with Double Supply-Regulation. Electronics. 2025; 14(3):588. https://doi.org/10.3390/electronics14030588

Chicago/Turabian StyleJung, Minji, Kyeongmin Min, Hyunwoo Son, and Youngwoo Ji. 2025. "A 5-Transistor CMOS Voltage Reference with Double Supply-Regulation" Electronics 14, no. 3: 588. https://doi.org/10.3390/electronics14030588

APA StyleJung, M., Min, K., Son, H., & Ji, Y. (2025). A 5-Transistor CMOS Voltage Reference with Double Supply-Regulation. Electronics, 14(3), 588. https://doi.org/10.3390/electronics14030588