1. Introduction

Simultaneous Wireless Information and Power Transfer (SWIPT) has attracted a plethora of attention in the recent literature as a mechanism used for powering up and communicating with standalone devices such as Internet-of-Things (IoT), biomedical implants, electric vehicles, and underwater applications [

1,

2,

3,

4,

5,

6]. This concept brings about removing power and data wired connectivity, improving flexibility, and removing the need for batteries for the system. SWIPT is based on the combination of two technologies. The first is Wireless Power Transfer (WPT), which transfers RF power wirelessly from a dedicated source or ambience to the receiver, from which the RF power is converted to DC to power up said receiver. This power transfer can be performed in the near field using inductive links or radiative fields using antennas. The second is Wireless Information Transfer (WIT), which is based on the modulation and demodulation of the RF signal to transfer data wirelessly. This combination can be in a separate-channel scheme where the power and data are orthogonal to each other, which would make them unimpacted by one another at the expense of increased area of implementation, or it can be in a shared-channel scheme, which improves compactness at the cost of performance reduction [

2,

3].

Communication schemes can be categorized in a shared-channel SWIPT system as single modulation or double modulation. Amplitude Shift Keying (ASK), On–Off Keying (OOK), Frequency Shift Keying (FSK), and Phase Shift Keying (PSK) are all examples of single modulation category. In ASK, the modulating carrier is shifted high and low according to the data bits at the input of the modulator. This modulated signal can be demodulated in a coherent (synchronous) way using clock-generating circuitry and a Phase-Locked Loop (PLL) at the receiver side or in a noncoherent (asynchronous) way using an envelope detector, which removes the need for the clock generation and PLL circuitries [

7]. Noncoherent ASK in SWIPT brings the advantages of low complexity, low power consumption, and the removal of phase detection. However, the disadvantages are impacted performance due to the continuously varying power envelope of the RF power, which would impact the power transfer efficiency and low data rate compared to FSK and PSK [

8]. OOK is similar to ASK but with a modulation index of 100%. This scheme simplifies the receiver structure even more compared to ASK due to the wide range between bits “1” and “0”, but for WPT purposes, it is inefficient since during data transmission of bit “0”, power is discontinued from the receiver. FSK and PSK are based on digitally changing the frequency and phase of the modulating signal to change the data bits. Both FSK and PSK require phase detection and clock-generating circuitries, which would increase the power consumption, area utilization, and receiver complexity. Also, FSK and PSK are usually incorporated with Gaussian filtering and differential signaling, respectively, adding to the receiver’s complexity, area utilization, and power consumption [

9]. FSK and PSK have high data rates and constant power envelope advantages, whereas the latter advantage is suitable for WPT. However, the cons of FSK and PSK outweigh the pros in terms of WPT performance.

Instead of a single modulation scheme, a double modulation scheme can be used to gain more advantages, such as asynchronous clock extraction and improved receiver functionality [

10]. This led to an emerging double-modulation scheme in the recent literature used heavily in short-range SWIPT systems for biomedical applications: Amplitude Shift Keying with Pulse Width Modulation (ASK-PWM). Instead of using ASK for data decoding, the ASK signal is demodulated to extract the asynchronous clock from the ASK-PWM signal. At the same time, the PWM is decoded to extract the data based on the digital pulse width of the decoded ASK signal. ASK-PWM maintains the advantages of noncoherent ASK demodulation regarding receiver complexity, area reduction, and power consumption. Also, when limiting the ASK modulation index within 5–10% of the RF power envelope, the RF power envelope will not change drastically in a way that would impact power efficiency and would also maintain a good room for demodulating the ASK signal, reducing the Bit Error Rate (BER) [

11].

Earlier work in the literature has utilized ASK-PWM SWIPT, primarily focusing on Integrated Circuit (IC) implementation for biomedical applications. In [

11], an 11 μW transceiver was presented for powering and communicating with implantable devices. The IC was fabricated using a 65 nm process and utilized ASK-PWM at a reconfigurable data rate between 4 and 20 Mbps; it also used an off-chip antenna at the frequency of 1.32 GHz at a separation of 3.5 cm from a 125 mW transmitting antenna. In [

12], a 13.56 MHz inductively coupled WPT system was presented. It used a hybrid organic/metal oxide process to achieve a bit rate of 75 bits/s using ASK-PWM with a size of 11 × 11 cm for organic applications. A 4.5 μW 3-channel wireless intra-cardiac acquisition system was presented in [

13]. The system was implemented using a 180 nm process, inductively coupled WPT at 13.56 MHz with a data rate of 88.3 Kbps. In [

14], an implantable device capable of locomotion in a fluid medium was implemented using a 65 nm process. It received 500 μW power from a 2 W source at a frequency of 1.86 GHz with a separation distance of 5 cm at a data rate of 2.5–25 Mbps using ASK-PWM. A Silicon-on-Chip (SoC) WPT using magnetic induction with ASK-PWM scheme for the flexible dithering feature is presented in [

15]. They used a 180 nm process to implement the system with a power consumption of 50 mW. In [

16], a comparator-less ASK-PWM design for inductive coupling WPT was implemented. It used a frequency divider, frequency multiplier, and data sampler for clock and data recovery of ASK-PWM realized using a 180 nm process at a data rate of 2 Mbps. A cochlear implant system for stimulation using an 8-channel inductive link with ASK-PWM was presented in [

17]. A custom chip was designed for the receiver part with a data rate of 120 Kbps at a total current consumption of 105 mA. A 900 MHz, inductively coupled ASK-PWM system with a 10 Mbps data rate is presented for brain implant purposes [

18]. The system was composed of 32 ICs manufactured using a 65 nm process. A 180 nm SoC near field resonant inductive link with ASK-PWM at 40.68 MHz is presented in [

19]. The system enabled up to 16 implantable stimulators at an 8 cm separation with a data rate of 10 Kbps, consuming 27 μW of power from a 2 W transmitter.

As seen from the state-of-the-art review, the focus was mainly on implementing an inductively coupled ASK-PWM WPT system implemented on an IC for biomedical applications. Although IC realization brings the advantages of miniaturization and high integration, it increases complexity, costs, inflexibility, and development time. For example, producing a PCB prototype typically requires 2–3 weeks, whereas an IC prototype takes 24–48 weeks. These disadvantages can be avoided by implementing the system entirely on PCB using commercially available discrete components. As of this date, no work has been conducted to achieve such an option. The state-of-the-art did not present a detailed design approach for the energy harvester with an ASK-PWM decoder.

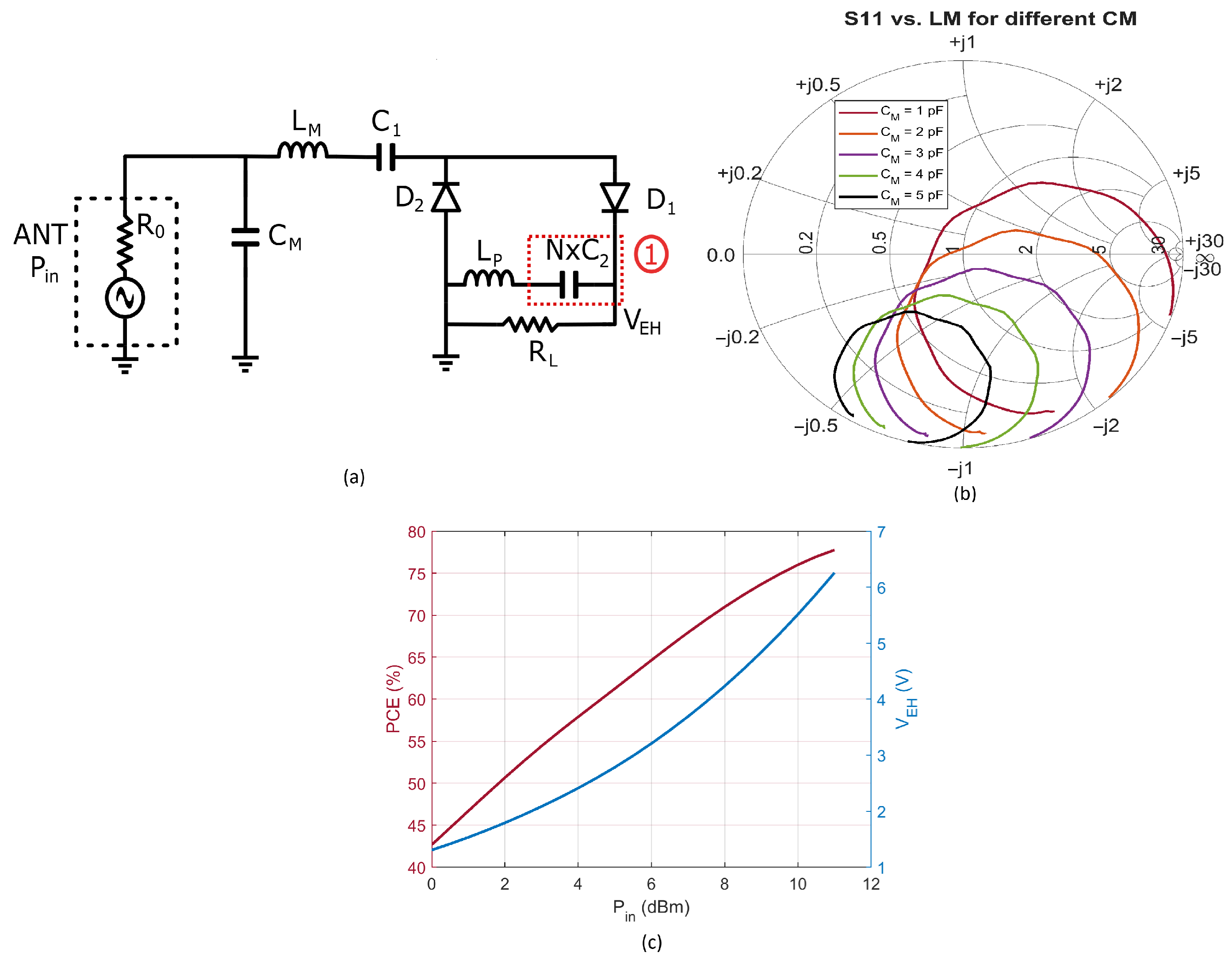

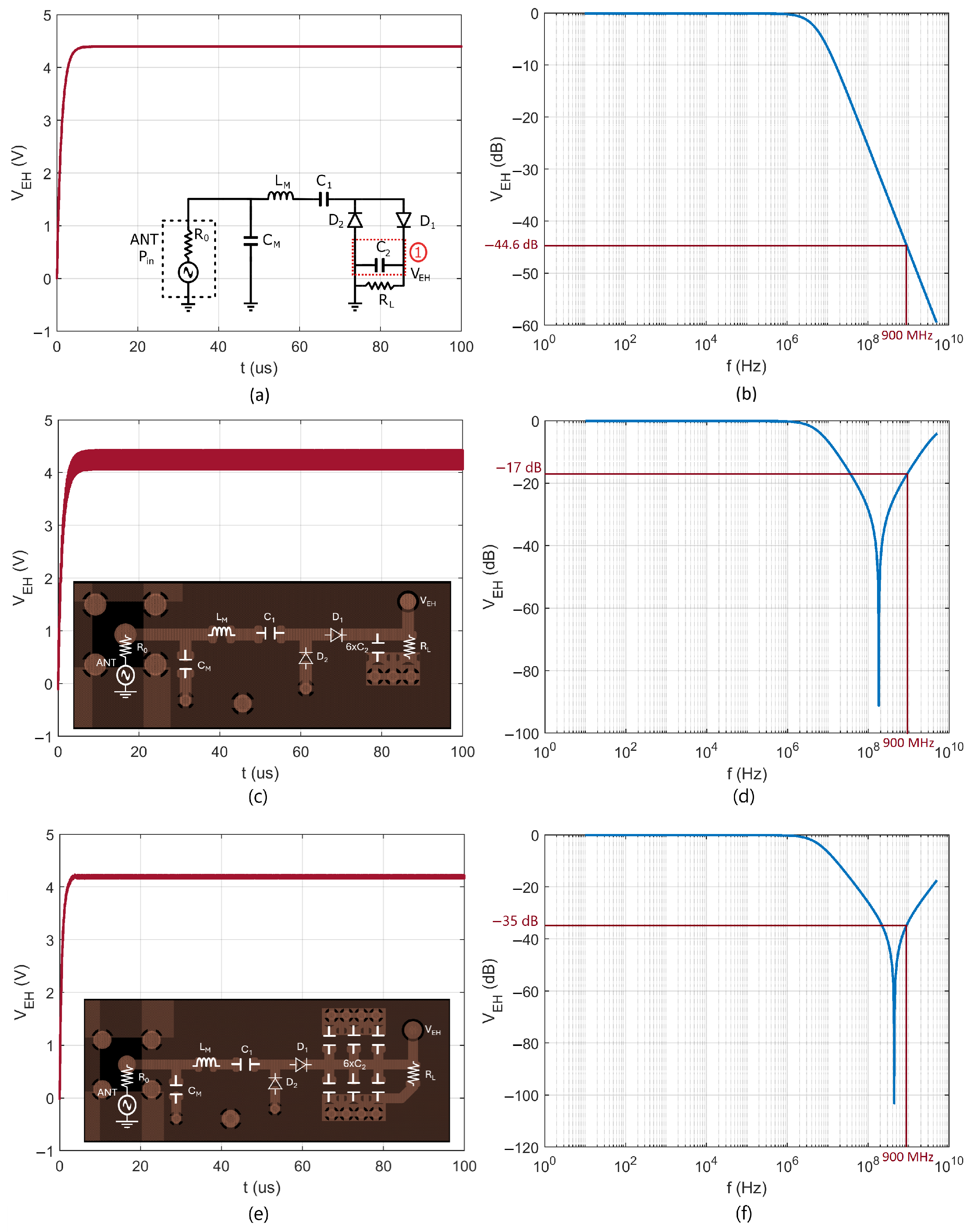

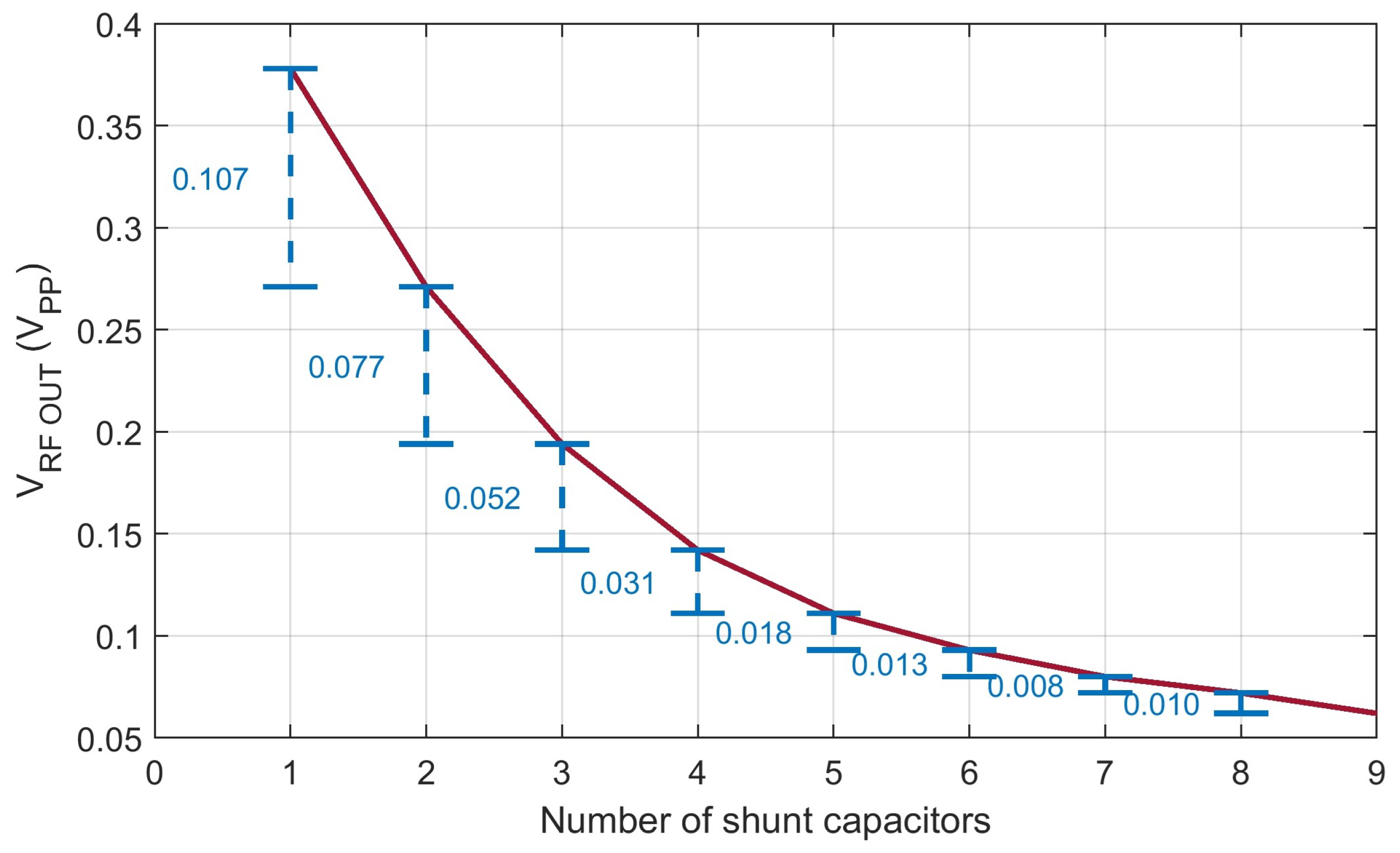

Three challenges were faced when attempting to realize this system in a discrete fashion. The first was the parasitic inductor that existed at the output of the rectifier’s filter, which caused the RF to leak into the output regardless of the rectification capacitor’s value. The second challenge is that the Power Conversion Efficiency () value was impacted by the load resistance value at the output of the communication rectifier, which reduced the flexibility in changing the time constant of the communication filter. The last challenge was the inflexibility of changing the aspect ratio of the inverter’s discrete P-Field Effect Transistor (P-FET) in the PWM decoder to achieve the skewing operation necessary for successful data decoding. The first two solutions improve the performance of the discrete implementation, while the third one is critical to realize the system in a discrete fashion.

In this work, we implemented a fully discrete ASK-PWM energy harvesting system using commercially available components. The PCB is an FR-4 substrate of size 5 cm × 4 cm × 0.6 cm and harvests energy at the 924 MHz ISM frequency, while the ASK-PWM bit rate is at 15 Kbps. The contributions are highlighted in the complete discrete implementation of the system on PCB, its detailed design approach, and the solutions to the challenges exhibited in implementing such a system in a discrete format. These solutions and improvements are described as follows:

The impact of the inductive parasitic effects was solved by splitting the big rectification capacitor at the output of the rectification filter into multiple smaller capacitors. This reduced the inductive contribution to a large extent, leading to a smoother DC output;

A lossy resistor was added in series with the communication’s path rectifier to drop the amount of current in this path to a minimal value. This allowed the of the harvester’s path to remain at an almost constant value regardless of changes in the load value of the communication rectifier, adding flexibility in tuning the time constant of the communication filter;

The aspect ratio inflexibility for the skewing operation was solved by adding a potentiometer between the P-FET drain terminal and the inverter output. The potentiometer controls and increases the time constant to achieve and set the correct level of the skewing operation.

Furthermore, commercial antennas were used to harvest radiative energy so that more applications can be targeted using this system other than biomedical applications, such as beamforming control systems, Wireless Sensor Networks (WSNs) powering, and wireless actuator control. The system was tested with an antenna separation distance of 6–12 cm.

The paper is structured as follows:

Section 2 is the proposed circuit structure, and

Section 3 contains the design approach split into four phases, including the proposed solutions and improvements.

Section 4 presents the complete system’s PCB and its measurements under radiative-field operation for validating harvesting, data, and clock recovery.

Section 5 is the conclusion.

2. Proposed Circuit Structure

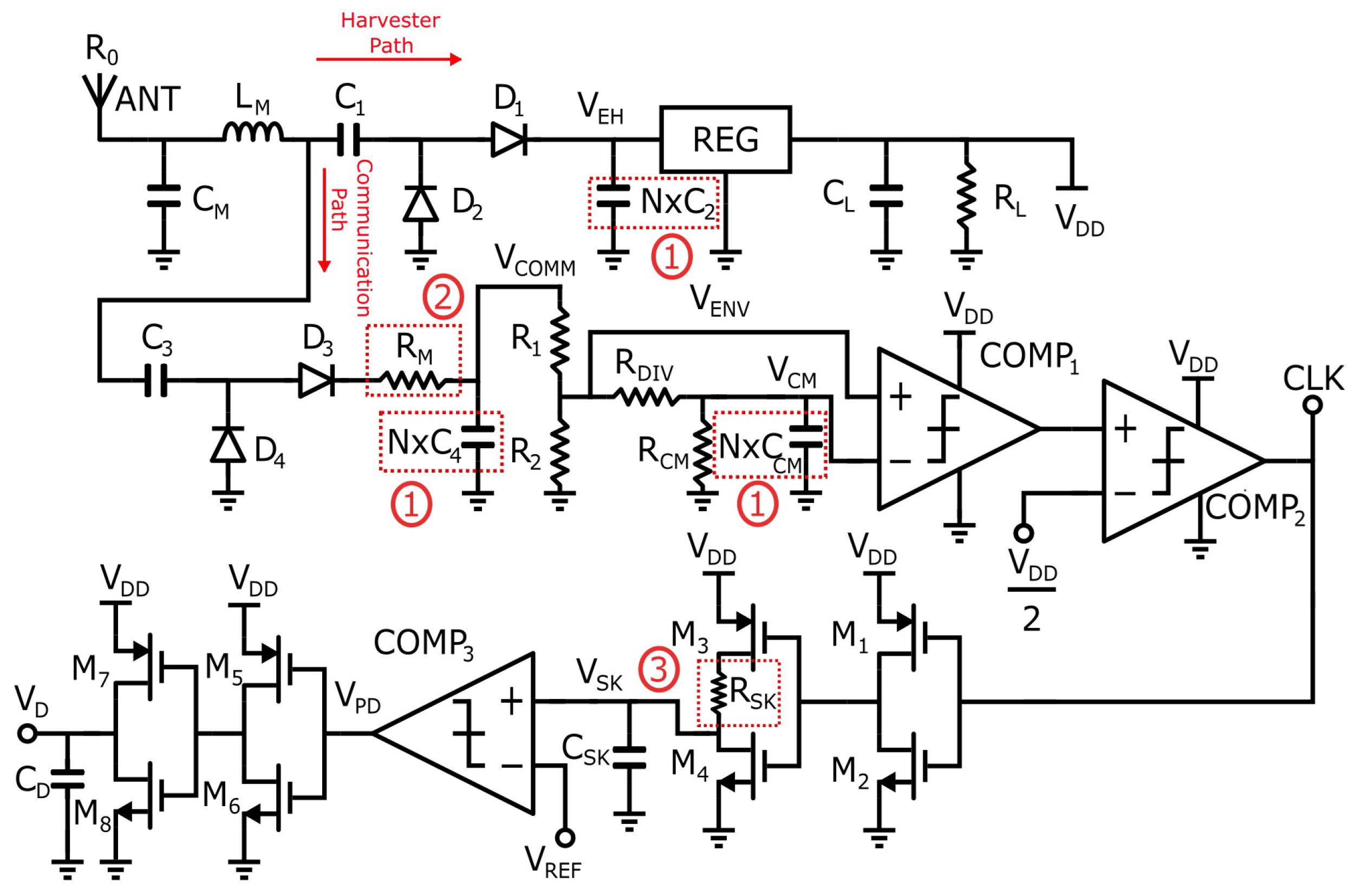

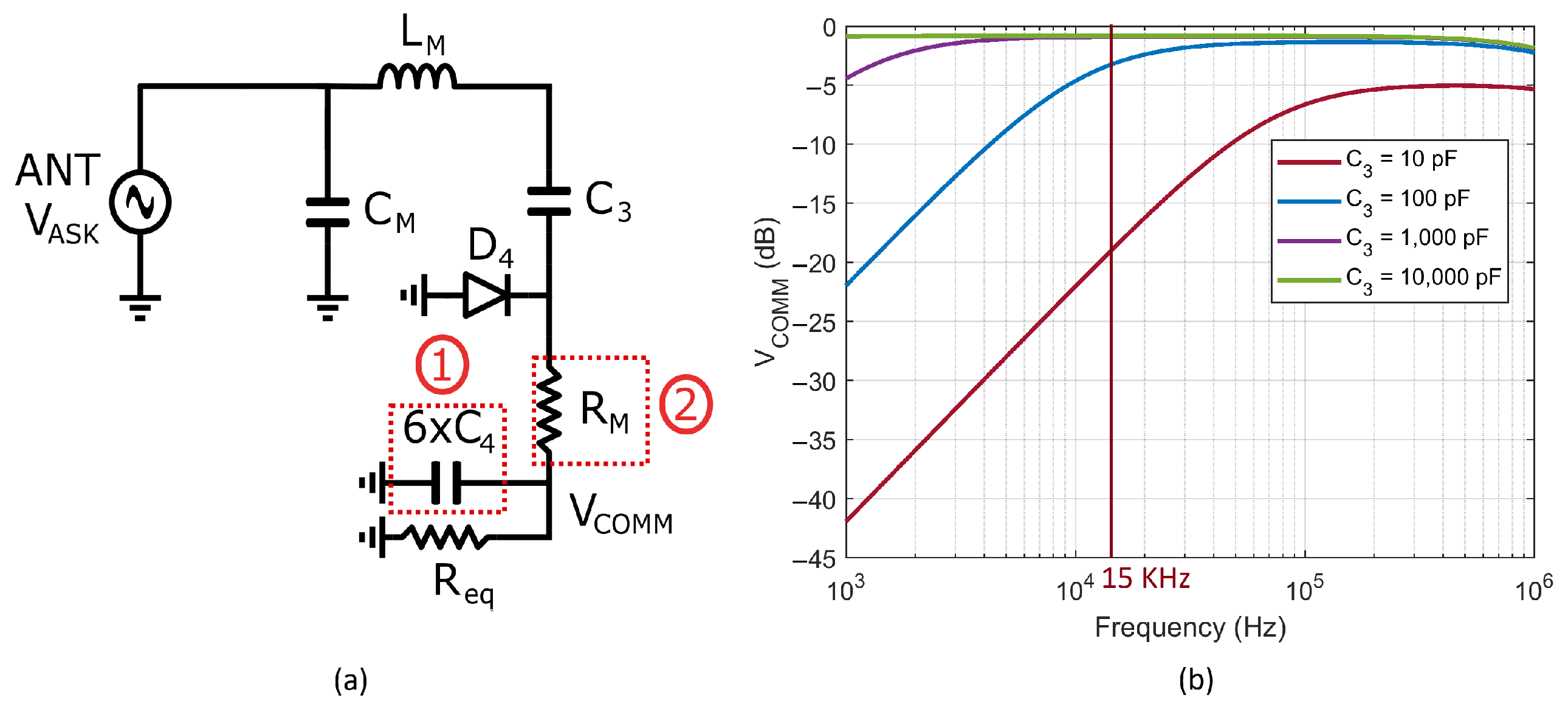

The complete circuit structure of the energy harvesting ASK-PWM system implemented using discrete components on PCB is shown in

Figure 1. Also, the figure annotates with dashed lines the proposed solutions and improvements highlighted in the list of the previous section with their corresponding numbers. The structure comprises four main blocks: the receive antenna (ANT), the matching network, the harvesting path, and the communication path.

The receive antenna here collects the RF power and the ASK-PWM modulation signal. This antenna has a characteristic resistance . The matching network here was chosen to be a shunt capacitor series inductor , which does not perturb the low-frequency ASK-PWM signal. This network provides good matching between and the input impedance of the harvester path. here also provides resonance peaking for the RF voltage suitable for controlling the location of the peak efficiency of the harvesting rectifier.

Secondly, the harvester path contains a voltage doubler structure

,

,

,

, a voltage regulator

, load capacitance

, load resistance

, and regulated supply output

. Here, the voltage doubler should convert the RF input power into a DC voltage

that is higher than the necessary regulated output voltage

; additionally,

should be given enough room for the modulation of ASK in such a way that the minimum peak voltage is higher than the regulated output voltage.

, here, should be large enough to allow the input reactance to be dominated by

and

; hence, this capacitor does not block RF power.

N×

combines

N capacitors in a shunt to make a large capacitor (item ①). The main reason for this shunt combination is to reduce the inductive parasitic effects to improve the DC output smoothness;

Section 3 will provide more details. The regulator provides a stabilized DC voltage that is not impacted by the ASK-PWM and switching noises from the system. It also powers up

and supplies a stable voltage

to power up the system’s comparators and inverters.

should be very large to filter any noises at the regulator’s output and help with the regulator’s frequency stability.

The communication path is composed of an ASK-PWM demodulator and decoder. It contains a voltage doubler , , , , , a voltage divider , , an ASK filter comprising , , , comparators , , a PWM decoder containing an inverter made out of , , a skewing inverter made out of , , , , comparator , a delay buffer comprising , , , , and . In this communication path, is chosen to be in the nanofarad range to provide Alternating Current (AC) coupling. with the help of and is used to drop down the voltage of the voltage doubler to a value suitable for (within the range of its input common-mode range ). Additionally, (item ②) provides isolation between the loading of the communication rectifier and the harvester rectifier by reducing the amount of current passing through it. This ensures the is unimpacted by the changes in the loading of the communication rectifier and, hence, adds additional flexibility in tuning the time constants. This voltage doubler produces the communication voltage , an ASK-PWM modulated signal.

As for the ASK filter,

N×

is made out of several parallel capacitors to reduce inductive effects, and it results in a time constant

, which can be approximated assuming

is in the megaohm range and the remaining resistors in the filter in the kiloohm range as:

where

and

are used mainly to set up

with

and divide the voltage even further for the filter. This combination produces the envelope voltage

. The voltage division

and

with

are used to establish the second time constant

, which can be approximated to:

This combination produces the common-mode voltage . here should be designed to be smaller than to give enough voltage swing at the ASK-PWM frequency to be amplified by ; is designed to be about 100 times larger than to reduce the ASK-PWM modulation. This is achieved by having in the lower sub 10 picofarad range while is two orders of magnitudes larger (since , , and are in the 100 s kiloohms range). should be in the megaohm range, and hence, the division between and should be small. This is used to achieve two goals. The first is that by having such a small voltage division, would be centered between the two peaks of , causing to act as the average of and, hence, biases as a common-mode DC voltage. The second goal is to never allow to cross either peaks of during steady-state operation (i.e., during constant harvesting with no data transmission). As a result, would amplify the difference between the two peaks of with the bias of , and then it would go into to maximize the voltage swing into square waves with a reference voltage . The output of produces the recovered clock signal demodulated from the ASK modulation.

Moving on to the PWM decoder, after the inversion (through and ) of the signal containing the PWM modulation, it passes through the skewed inverter (, , (item ③), ) followed by to extract the pre-data . The skewing inverter with is used to distinguish between bits “0” and “1” based on the pulse width of the signal. If the pulse has a narrow-width high signal, it will be decoded as a “0”; if it has a wide-width high signal, it will be decoded as “1”. This is achieved by making the charging time for the skewing inverter long and by making the discharging time as fast as possible, after which outputs a high signal only when its skewed input crosses its reference voltage , outputting bit “1”. Finally, output from goes through a buffer (–) that adds a small delay using producing the final data output . This delay is necessary to synchronize the negative edge-trigger of with so that the data can be stored and digitally processed for the designed application.

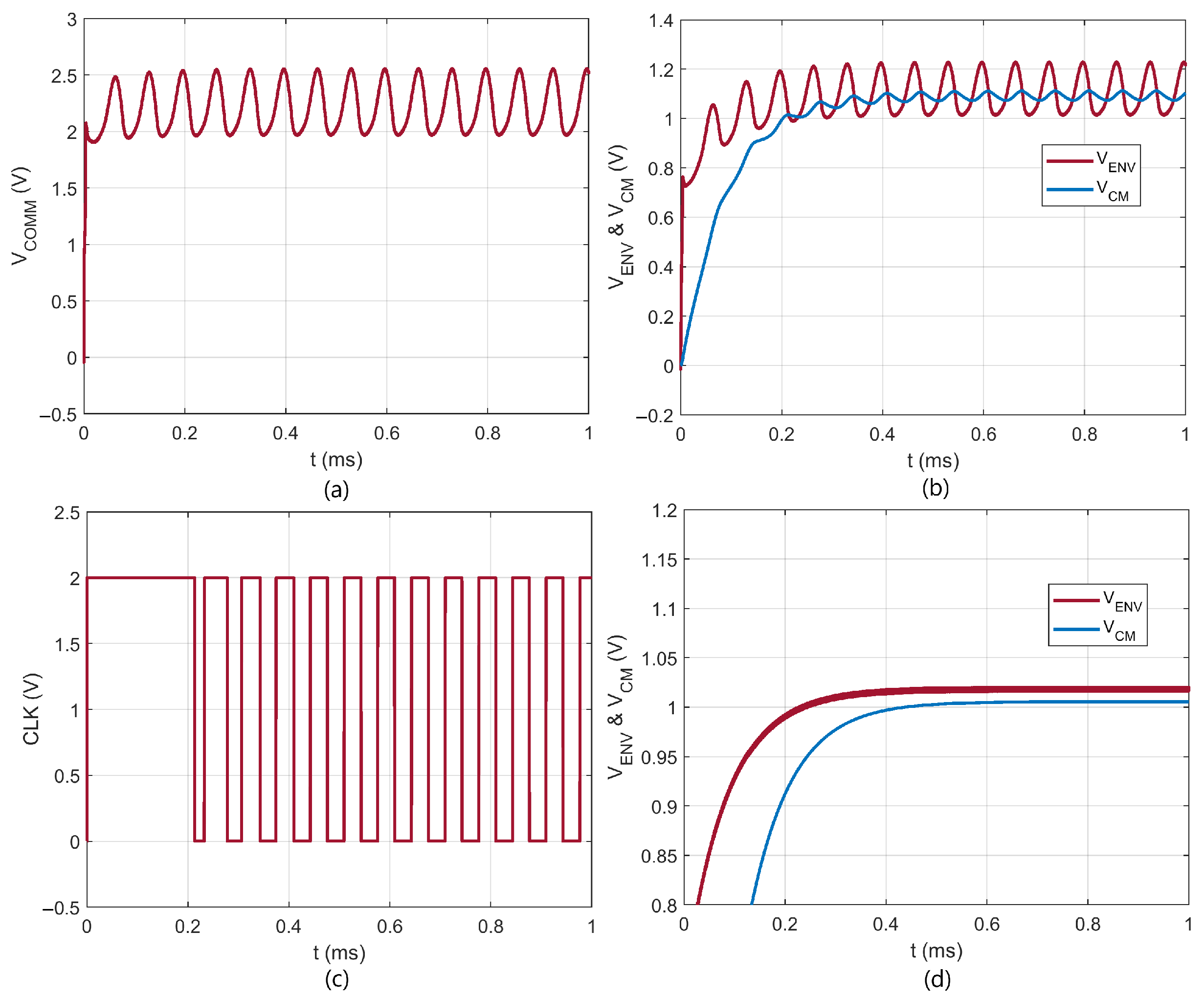

Figure 2 shows illustrative plots of the working principles of the ASK-PWM demodulator by modulating the RF power with the bit pattern “0010”. The plots show the voltage received by the antenna

, and they also show

,

,

,

,

,

, and

. The plots also highlight the synchronization between

and

with red dashed lines, as discussed.

4. Complete PCB Measurement and Validation

To validate the implementation of such a system in discrete format with the proposed solutions and improvements, we implemented the system entirely on a two-layer FR4 substrate of size 5 cm × 4 cm × 0.6 cm. An FR4 substrate was chosen to minimize the cost and production time without compromising significant performance, which lines up with the objectives of this work. The first layer contains all the components and interconnects, while the second layer is the ground plane. The PCB is shown in

Figure 12a with the annotated circuit blocks.

is an RF inductor from Murata LQW15AN5N2B80D sourced from Kyoto, Japan. The inductor has a value of 5.2 nH and a Q factor of 70 at 900 MHz. This inductor’s Self-Resonance Frequency

is 8 GHz, which is about 9 times higher than the harvesting frequency. The diode is SMS3922-079LF from Skyworks in Irvine, CA, USA: a Schottky diode with a low turn-on voltage, series resistance, and junction capacitance. The breakdown voltage is 8 V, which is suitable for the maximum voltage level in our design. The regulator used is a TLV70220PDBVR manufactured by Texas Instruments in Dallas, TX, USA. This part regulates the voltage at 2 V, draws a bias current of 35 μA only, which makes it suitable for harvesting applications, and has a Power Supply Rejection Ratio

of 68 dB at 1 kHz. Stabilization for this regulator was achieved by making

= 100 nF and 6 ×

= 600 pF. As for the comparator, BU5265HFV-TR was chosen from Rohm Semiconductor in Japan, which has full input swing and can operate at a

range from 1.8 to 5.5 V, suitable for our 2 V regulator. The supply current of this comparator is at a low value of 22 μA, making it ideal for harvesting. The maximum clock frequency for such a comparator is 14.28 MHz, which is more than enough for the bitrate of our system. It is critical to note that these comparators are CMOS and, hence, do not load the ASK filter, especially with the 8 M

resistor

shunted with the input of the comparator. The inverters are made out of bsh103bk NMOS and bsh205g2 PMOS, which are made by Nexperia in USA. The NMOS has a typical threshold voltage of 1 V, while the PMOS has a typical threshold voltage of −0.7 V. Both are suitable for a 2 V supply. The maximum switching frequencies for the NMOS and PMOS are 166.67 MHz and 33.33 MHz, respectively, higher than the designed data rate. The dynamic power consumption of these inverters is at 3 μW at a switching frequency of 15 KHz, 100 pF loading and 2 V supply power, which are reasonable for harvesting. The total power consumption of the system was 355 μW.

here is made out of a potentiometer to tune

to control the peak of the skewing output voltage of different bits. As a result, by adjusting the potentiometer, successful bit decoding can be ensured when re-configuring the bit rate for the system.

The measurement setup of radiative field harvesting is shown in

Figure 12b. A signal generator SME 06 from Rhode & Schwarz was used to produce an ASK-PWM modulated wave. The output power of the signal generator was set at 16 dBm (calibrated to output 12 dBm) at a frequency of 924 MHz. Although the SME 06 is capable of digital modulation, it does not perform ASK modulation directly. To solve this problem, we controlled the digitally controlled attenuator using a bit pattern at a switching rate of 30 KHz to achieve ASK-PWM modulation. We assigned a 99 μs wide-high pulse followed by a 33 μs of narrow-low pulse for bit “1”, and assigned a 33 μs narrow-high pulse followed by a 33 μs of narrow-low pulse for bit “0”. The signal generator was connected to an 8 dBi HG908PCR Right-Half Circular Polarized (RHCP) commercial antenna. Another antenna was connected to the PCB. Both antennas were characterized using a Vector Network Analyzer (VNA), presenting close to 50 ohms impedances near the 924 MHz frequency. Hence, we operated at that frequency. The separation distance between the antennas was kept at 8 cm. However, the system operated correctly from 6 cm up to 12 cm. The PCB contained several test points connected to the hlRTB2004 Rhode & Schwarz oscilloscope to obtain waveform measurements. The regulator powered up all the inverters and comparators in the PCB; hence, no power supply was needed. All the required references for the comparators were set by voltage division with respect to the regulator voltage. The regulator’s enable pin was connected to

, which needs to be maintained above 2 V to keep the regulator in normal operating condition.

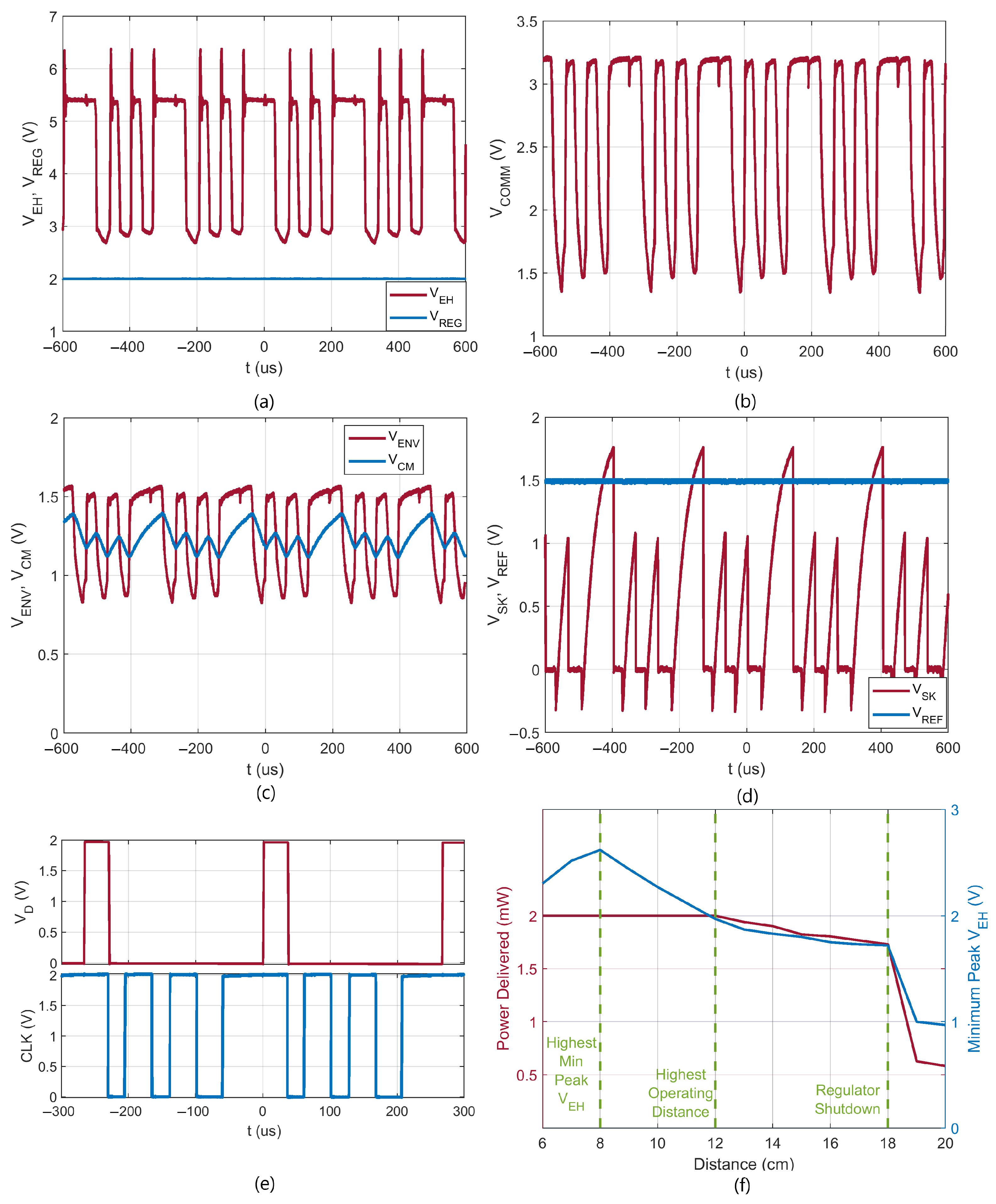

Figure 13 shows the most critical measurements of the PCB in

Figure 12a.

Figure 13a shows the harvested voltage

and regulated voltage

. A bit pattern of “100” was transmitted repeatedly, as shown in the red wave in the figure. The voltage swung from 5.2 V to 2.9 V, centered at 4.2 V. The voltage was never below 2 V, keeping the regulator at the correct normal operating condition. The blue wave shows the regulator output voltage was constant at 2 V regardless of variations in the harvested voltage due to modulation. This 2 V was applied to an

of 2 k

, hence delivering a power of 2 mW at a total receiver efficiency of 12.5%.

Figure 13b shows

being dropped by

down to 2.31 V, swinging up to a maximum of 3 V and a minimum of 1.32 V.

and

dropped this voltage by half, as seen by the blue wave in

Figure 13c, producing

. We can note that the

range was between 1.5 V and 0.73 V, within the

of

.

is also shown as the blue line in

Figure 13c.

Figure 13d presents the output of the proposed skewing inverter (red) and the reference voltage (blue) used to distinguish between a wide- and a narrow-high pulse.

Figure 13e shows the data output

(red) correctly presenting bit “1” for a wide pulse and bit “0” for a narrow pulse. Also, shown in the same plot, the

was produced from

,

,

, and

. The system performed correct data and clock recovery even with different data bits transmitted due to the asynchronous extraction of both voltages. As for the separation distance validation, a plot showing the relationship between both the minimum peak

and power delivered by the regulator vs. the separation distance between the antennas is shown in

Figure 13f. We can note three critical regions on the plot: The first is at 8 cm where efficient polarization was achieved and, hence, the highest minimum peak

was achieved. The second is after 12 cm where minimum peak

dropped below 2 V, which caused the regulator voltage to drop below 2 V. The last region is after the 18 cm mark, where the internal reference inside the regulator collapsed completely and the power plummeted. As a result, the system operated correctly and provided a constant 2 mW power at a separation distance between 6 cm and 12 cm. Finally, The synchronization between

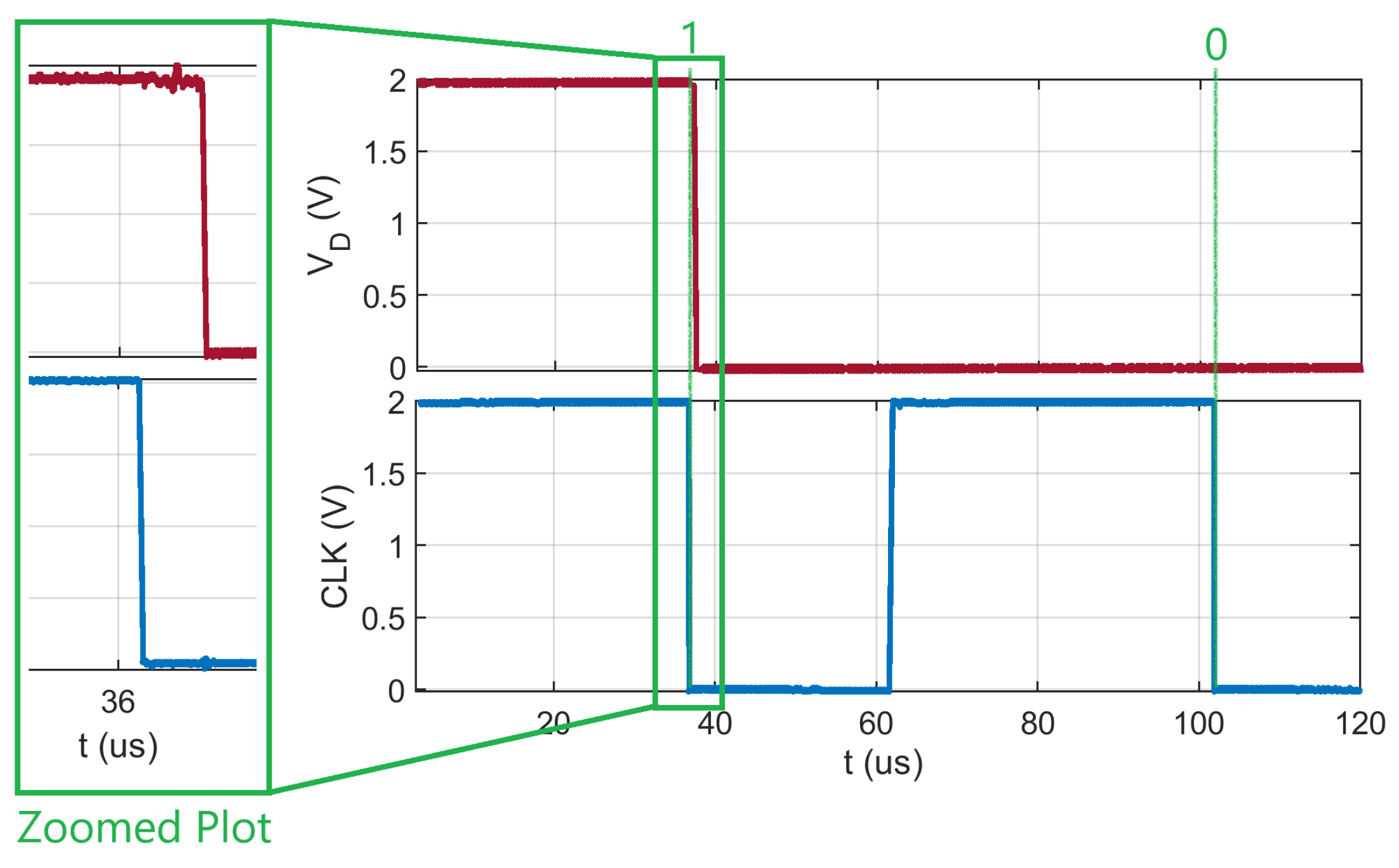

and

is shown in

Figure 14. For bit “1”, the

signal dropped before

; hence, a bit “1” would be stored in a shift register with a negative edge trigger. When the

triggered negatively and there was no high signal, it would record a bit “0”.

A comparison between this work and the previous literature is shown in

Table 1. We can note that this work is the only work that implemented an ASK-PWM harvesting system on an FR4 substrate using discrete components only. Additionally, the separation distance is the largest at a 12 cm distance.