Efficiency Analysis of Bridgeless Three-Level PFC Circuits Based on Modal Segment Integration Method

Abstract

1. Introduction

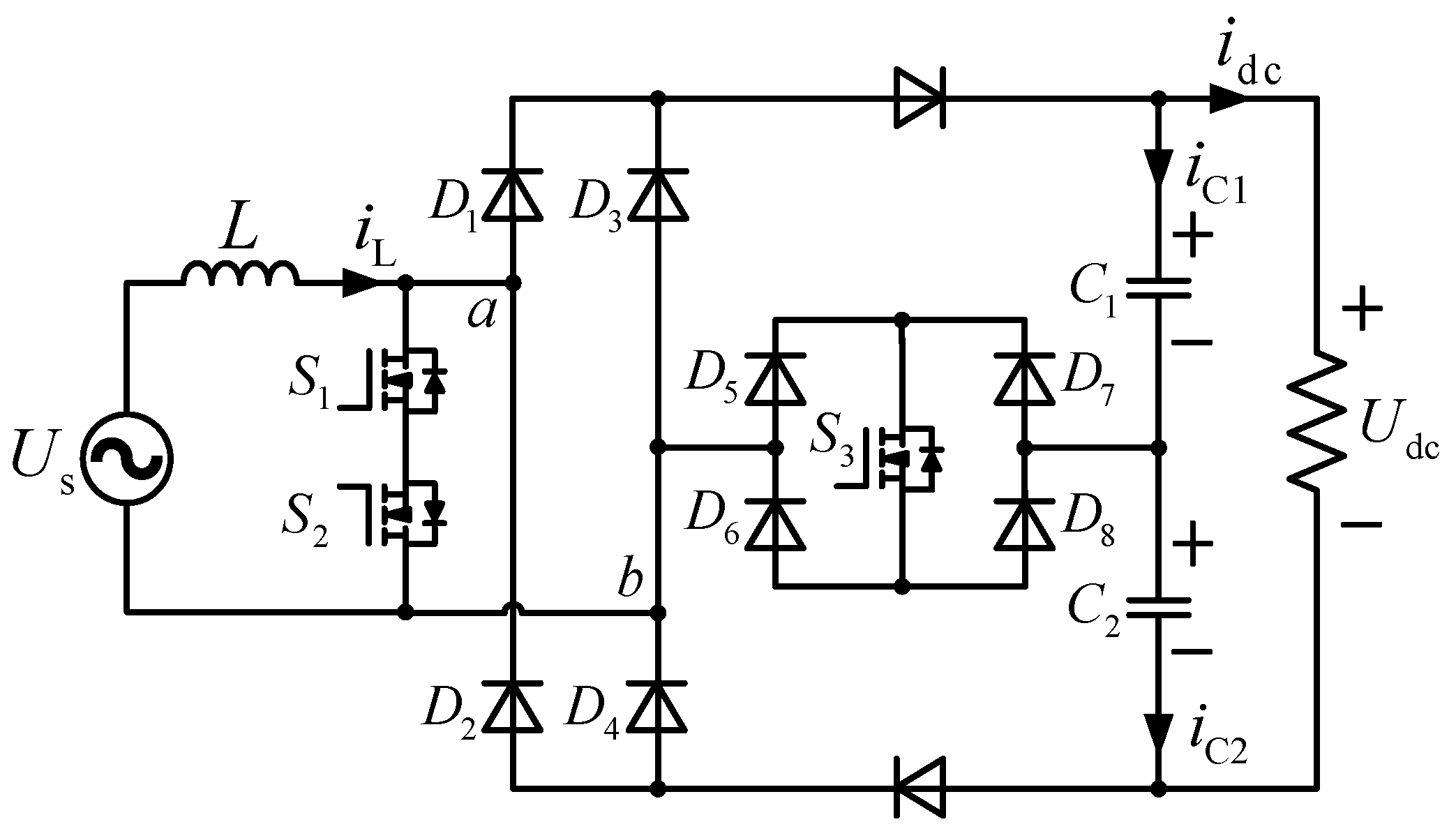

2. Analysis of Topology and Its Working Process

2.1. Circuit Topology

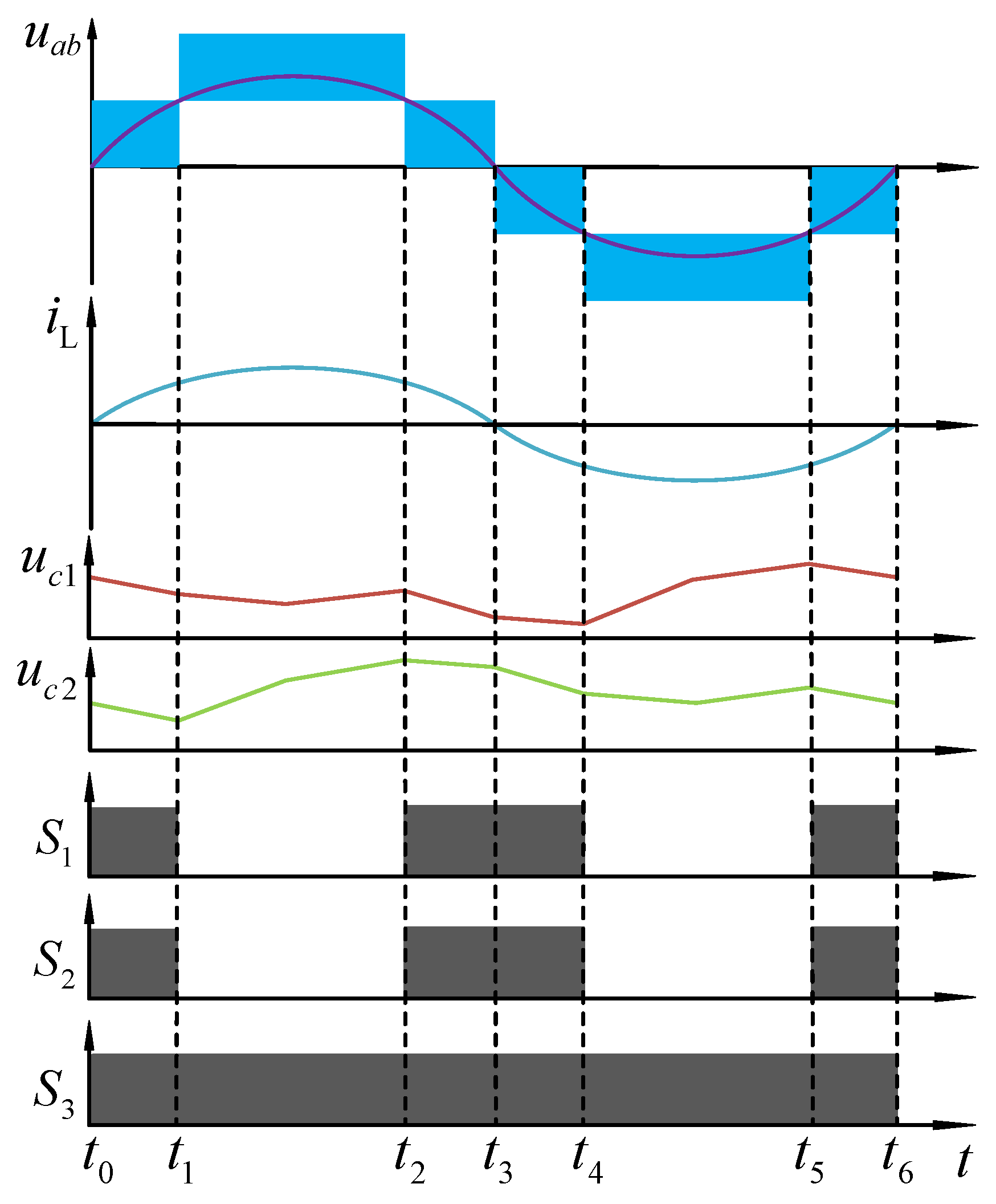

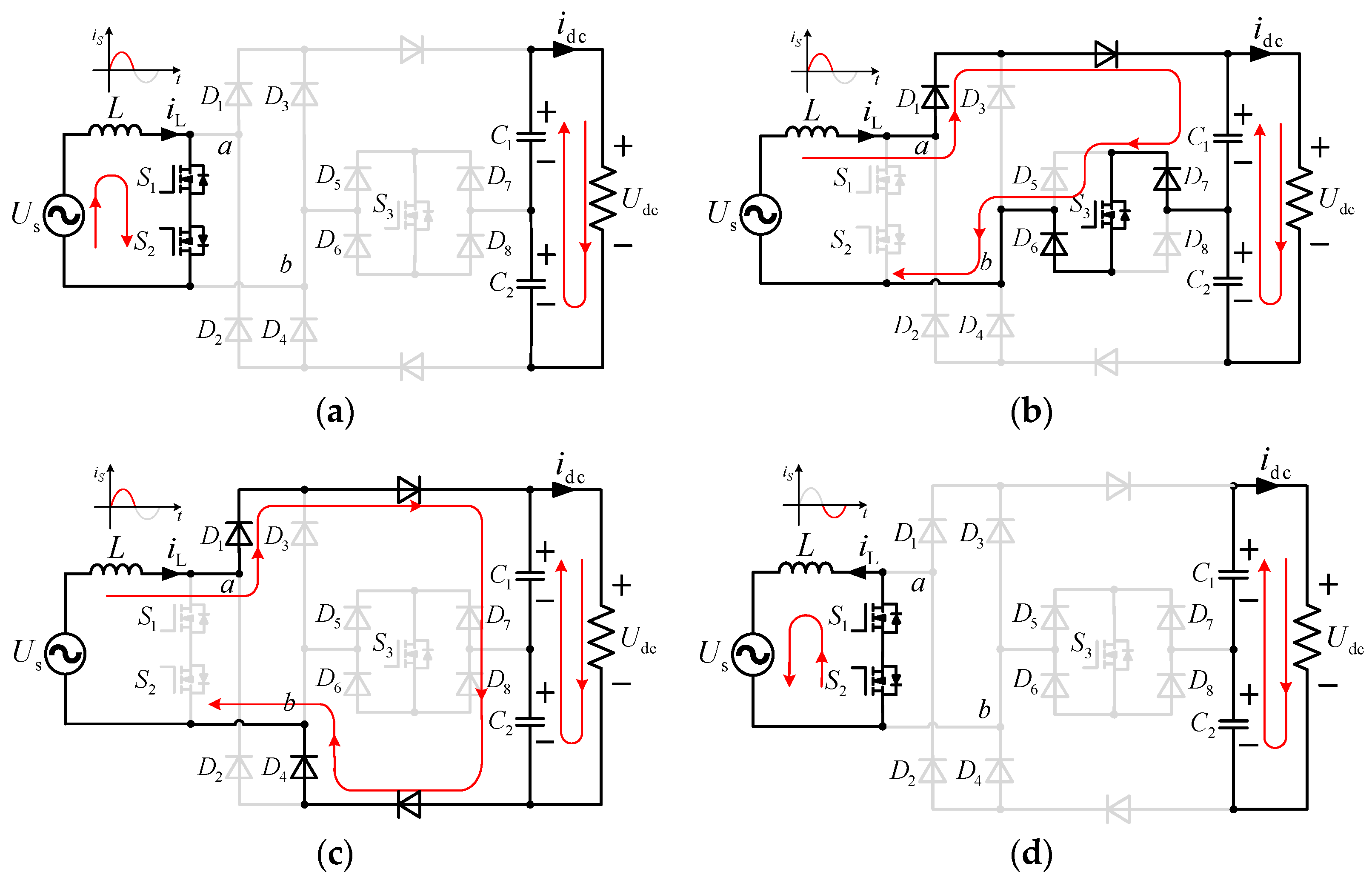

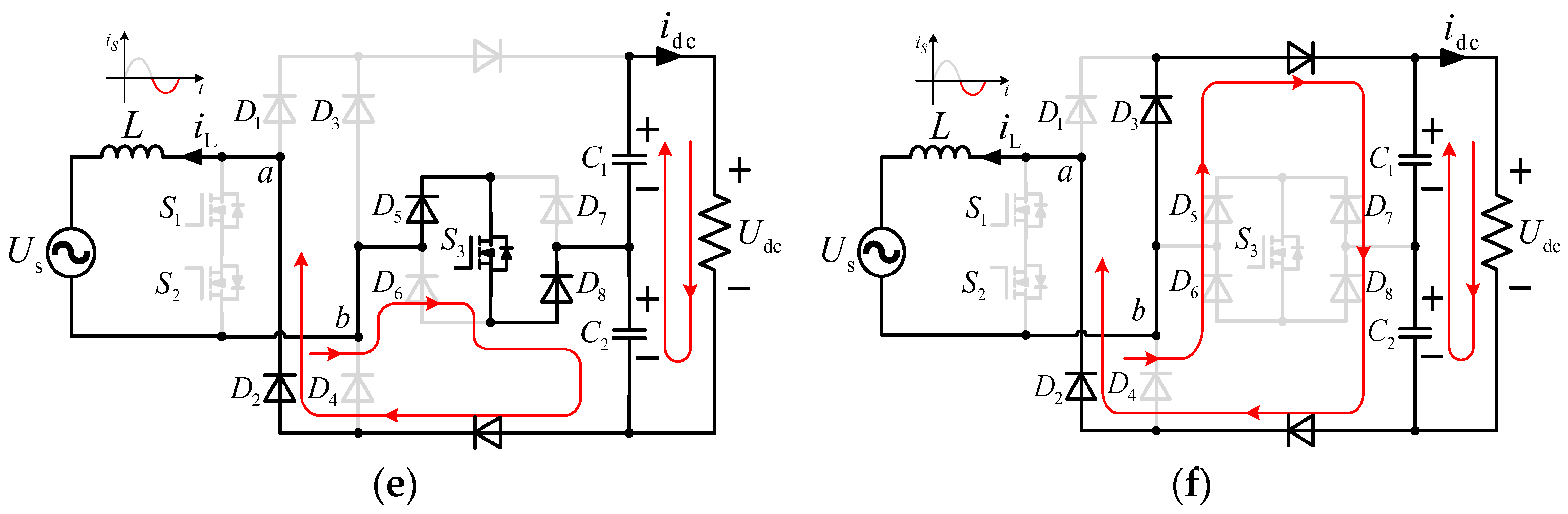

2.2. Analysis of Work Processes

3. Loss Analysis and Efficiency Estimation

3.1. Diode Loss Analysis

3.2. Loss Analysis of Power Switching Devices

3.3. Estimation of Efficiency

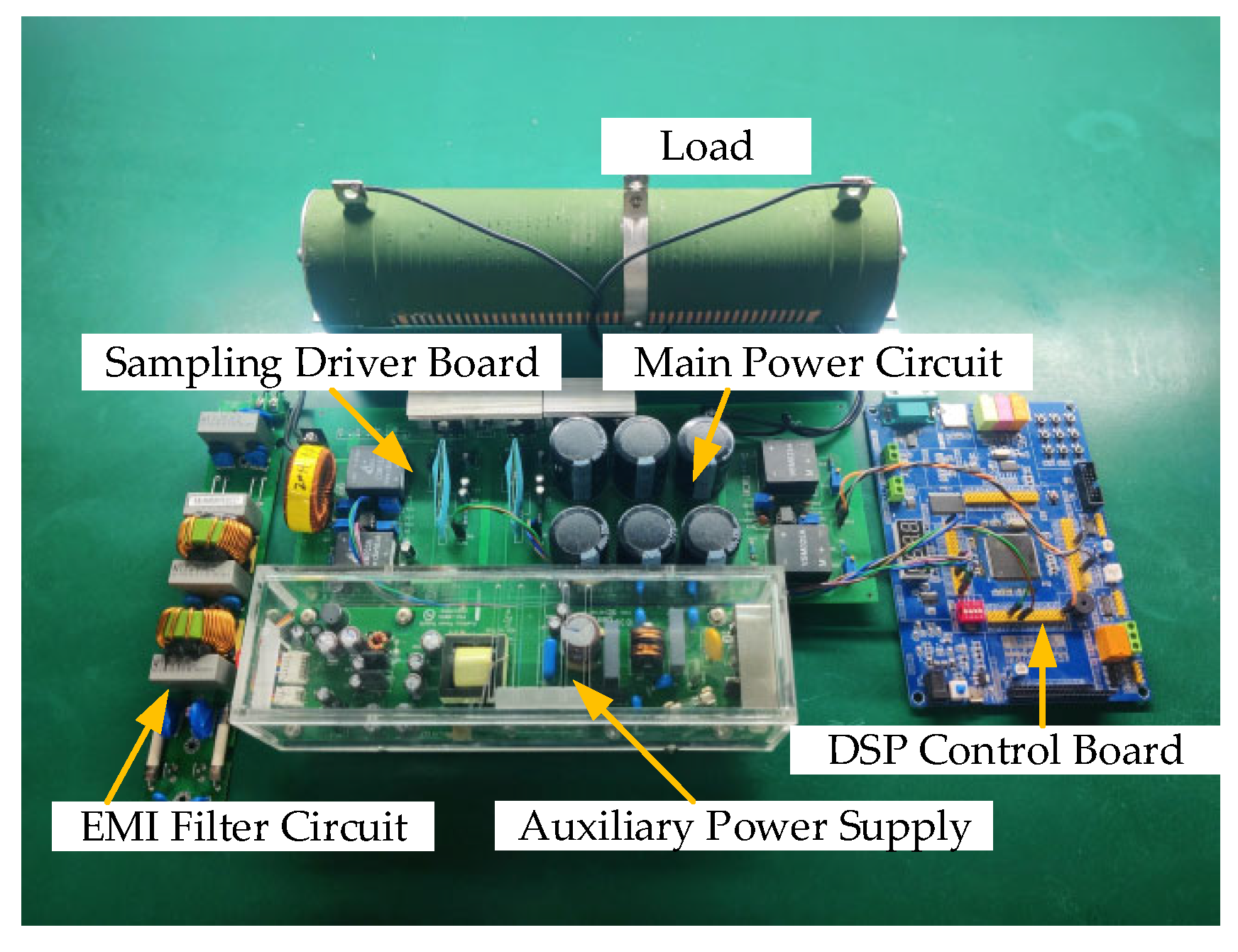

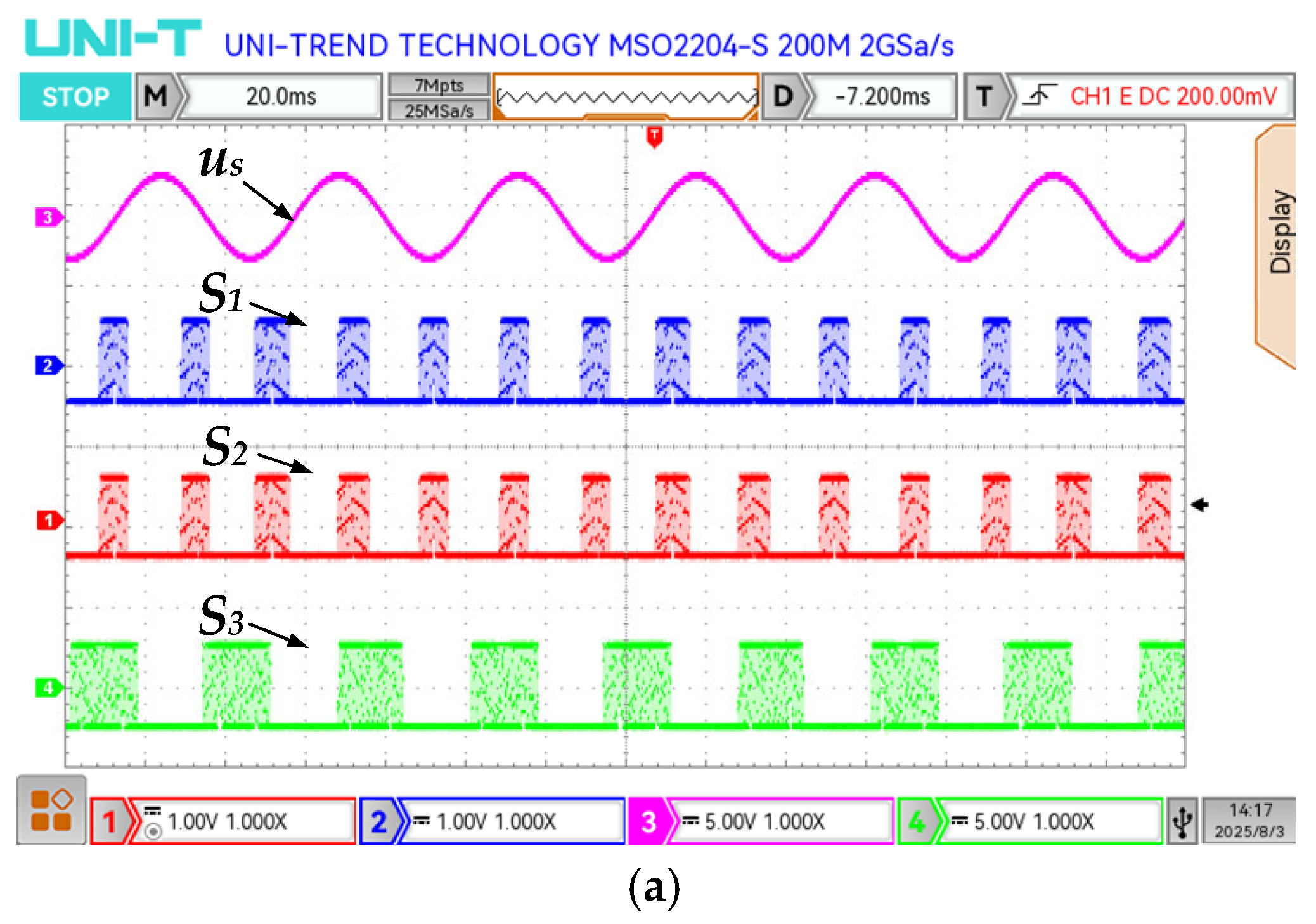

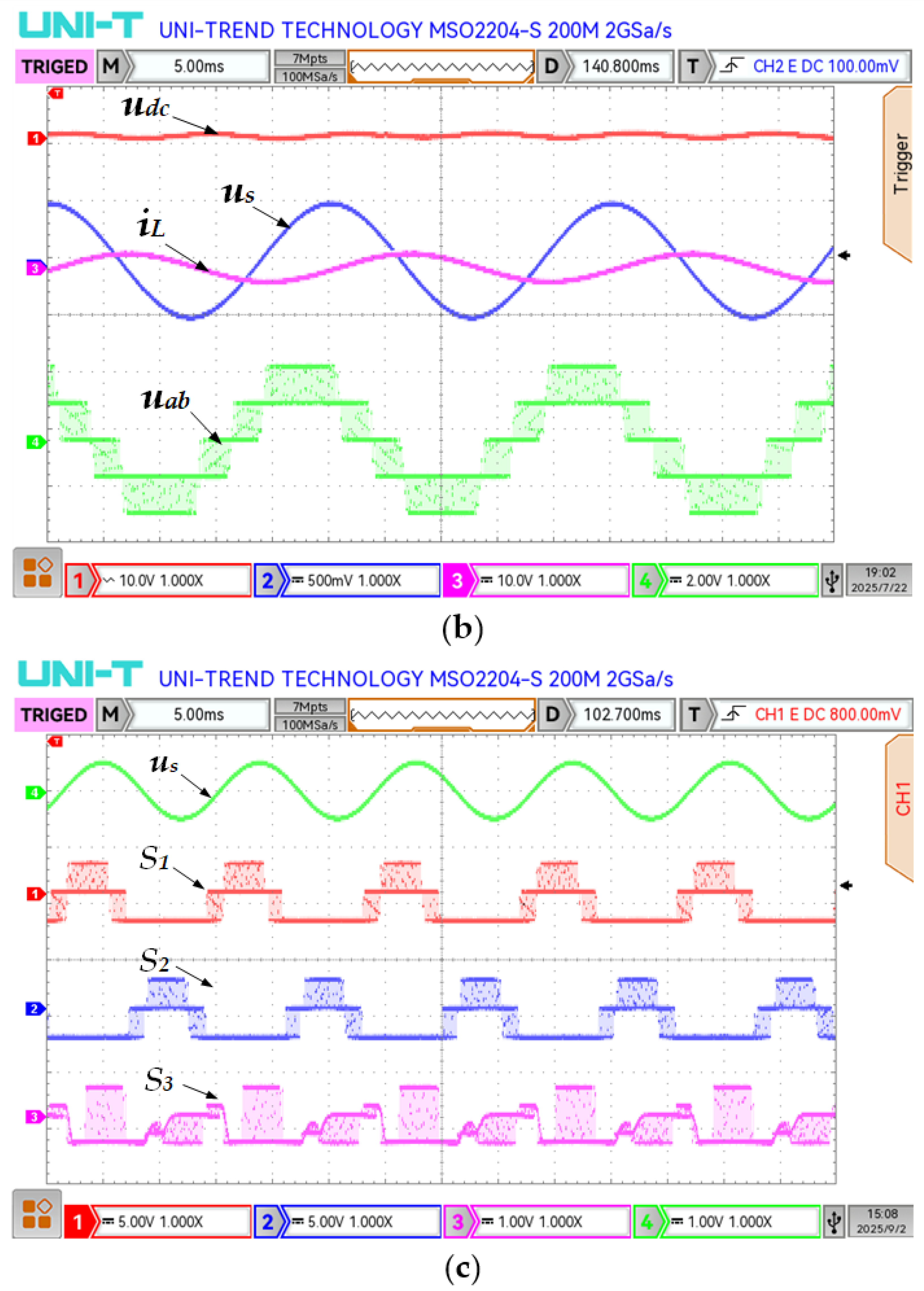

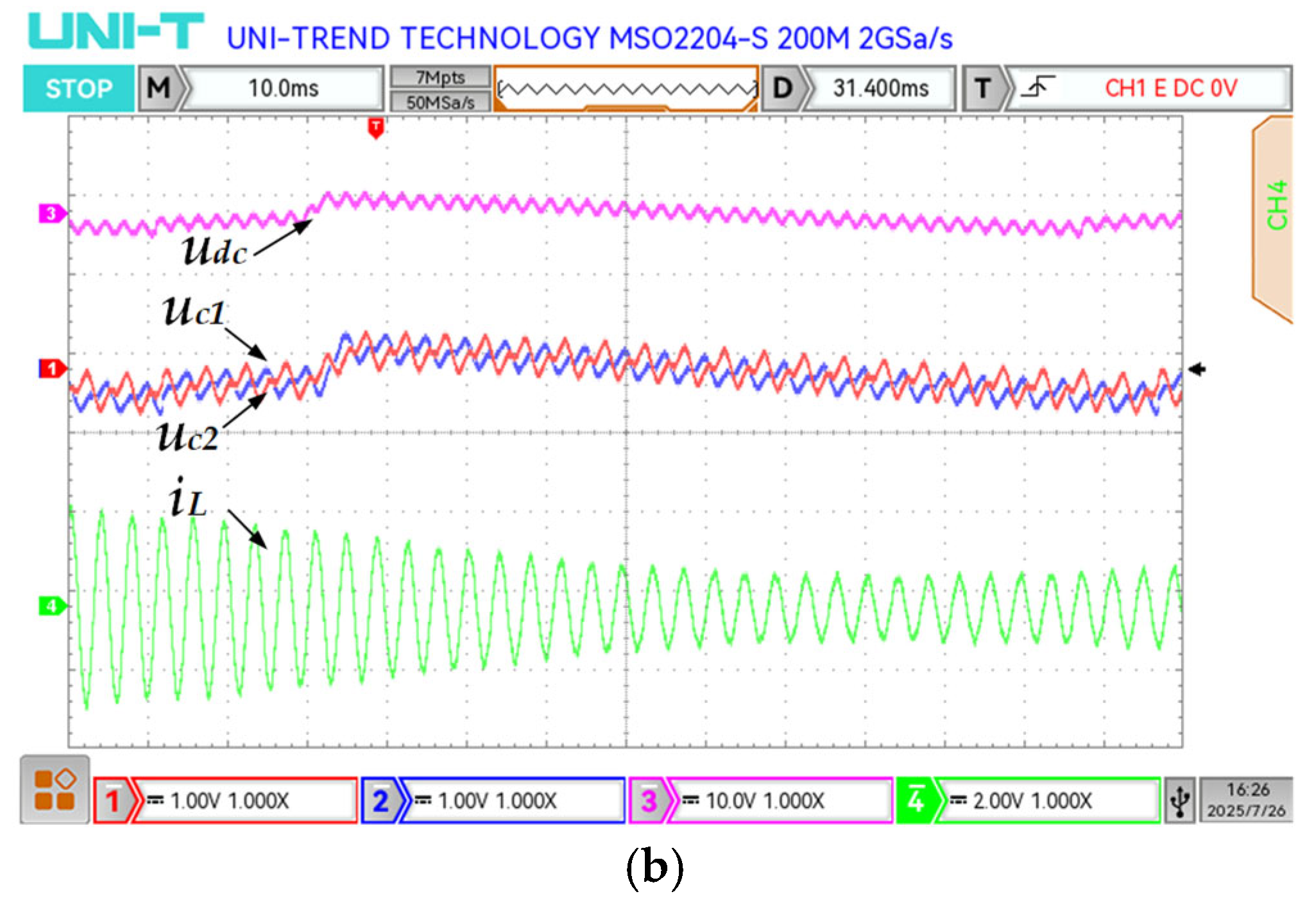

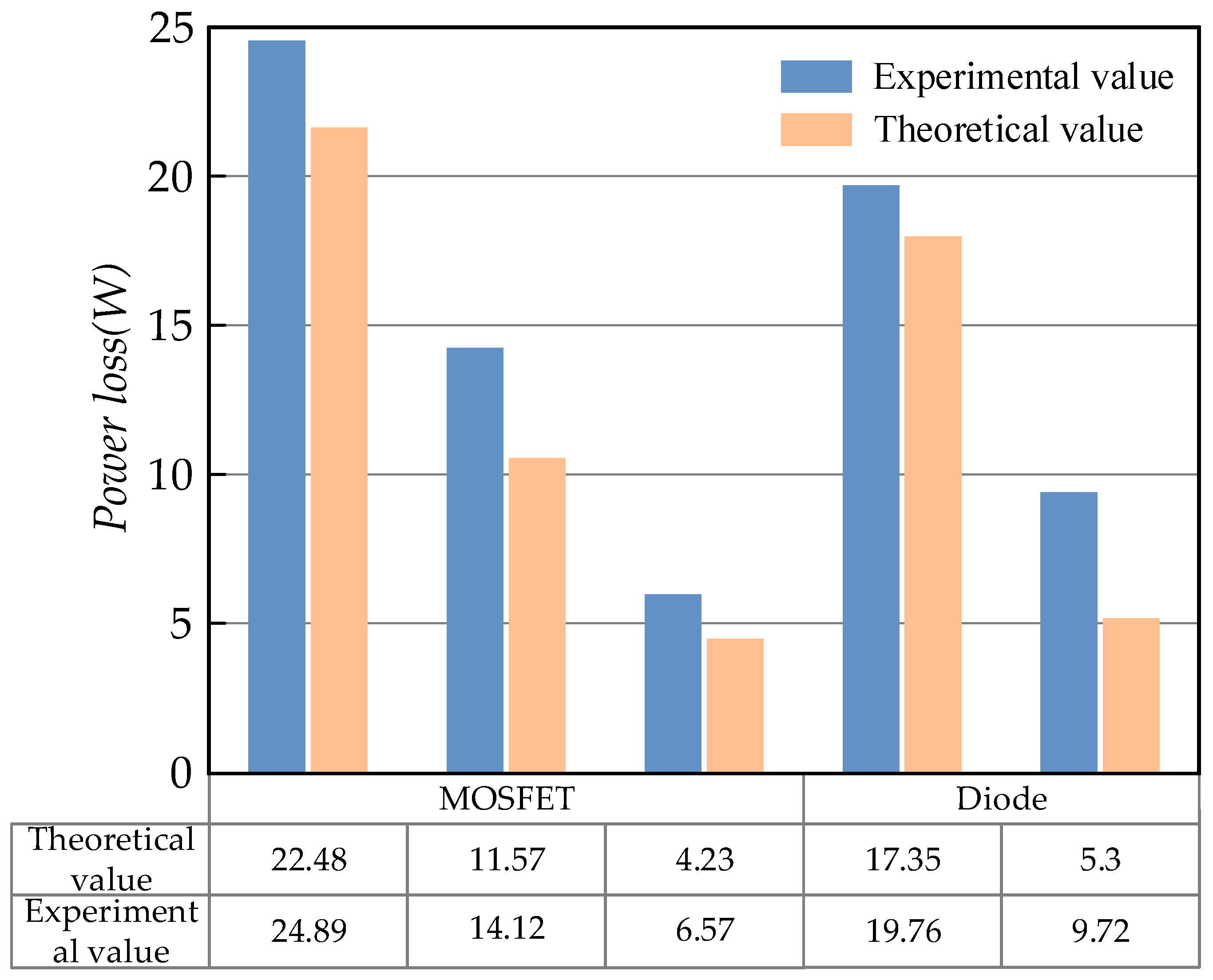

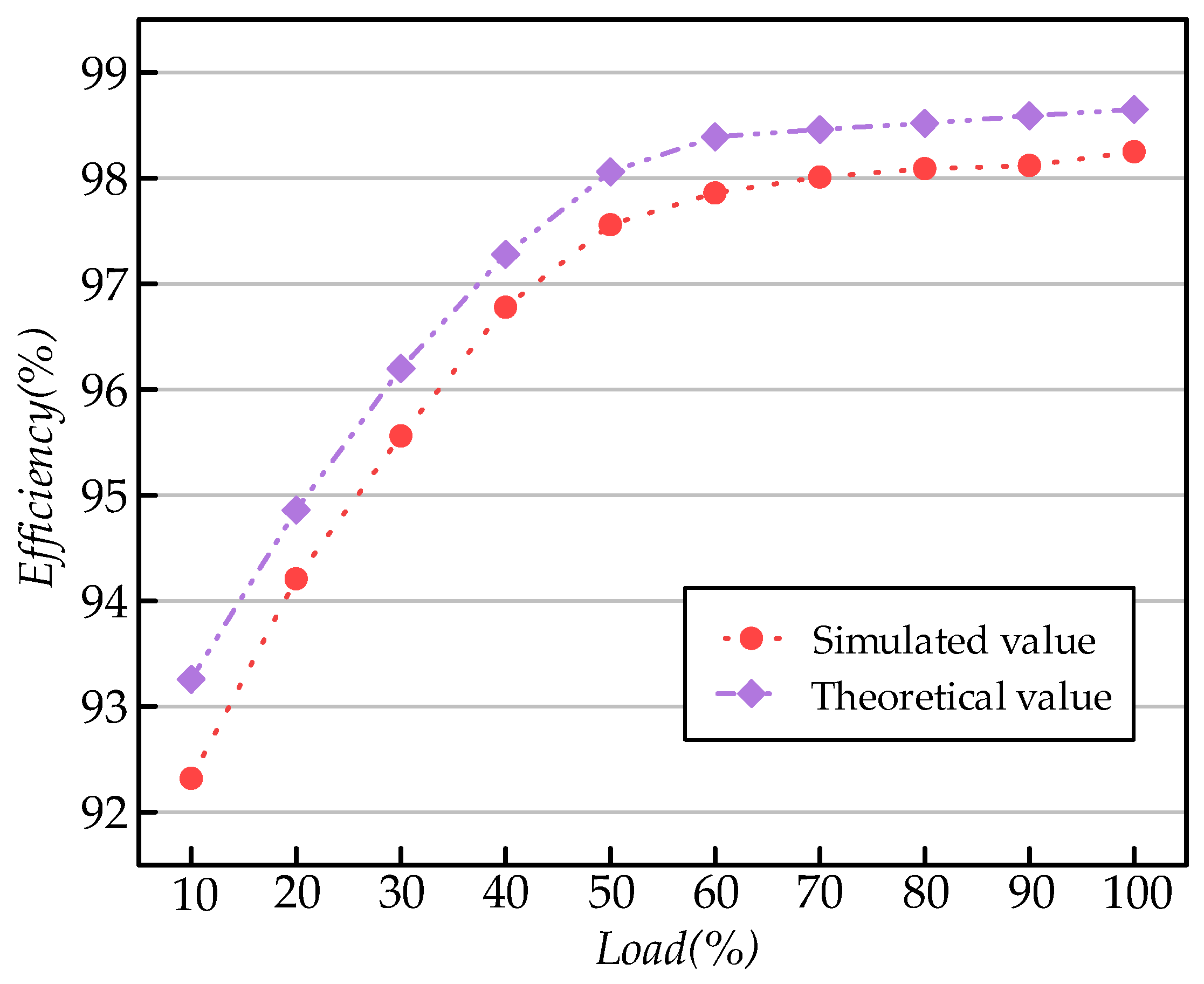

4. Experimental Simulation and Verification

5. Conclusions

- A modal segment integration method based on the device loss model is proposed to estimate the theoretical efficiency of bridgeless three-level PFC rectifier over a complete cycle. This method improves the theoretical basis of the efficiency analysis method and enhances its applicability during the design stage.

- Simulations and experiments demonstrate that the proposed efficiency estimation method is highly accurate. The error between the theoretical and experimental data is less than 0.4%, which verifies the method’s reliability.

- The experimental prototype was tested under both steady-state and dynamic operating conditions, and the results confirmed that the proposed topology exhibits excellent power factor correction capability and stable operational performance.

- In the future, this method can be expanded to the efficiency analysis of multilevel topologies and multiport power conversion systems. The analytical model can also be extended to include parasitic parameters, which would further improve the accuracy of theoretical prediction. In addition, it can be combined with dynamic modeling and intelligent algorithm optimization under complex operating conditions to achieve intelligent and generalized efficiency evaluation.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lee, J.-S.; Lee, K.-B. A Novel Carrier-Based PWM Method for Vienna Rectifier with a Variable Power Factor. IEEE Trans. Ind. Electron. 2016, 63, 3–12. [Google Scholar] [CrossRef]

- Soeiro, T.B.; Kolar, J.W. Analysis of High-Efficiency Three-Phase Two- and Three-Level Unidirectional Hybrid Rectifiers. IEEE Trans. Ind. Electron. 2013, 60, 3589–3601. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel Inverters: A Survey of Topologies, Controls, and Applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Kolar, J.W.; Friedli, T. The Essence of Three-Phase PFC Rectifier Systems—Part I. IEEE Trans. Power Electron. 2013, 28, 176–198. [Google Scholar] [CrossRef]

- Ortmann, M.S.; Mussa, S.A.; Heldwein, M.L. Three-Phase Multilevel PFC Rectifier Based on Multistate Switching Cells. IEEE Trans. Power Electron. 2015, 30, 1843–1854. [Google Scholar] [CrossRef]

- Wang, C.; Cheng, B.; He, X.; Xi, L.; Yang, N.; Zhao, Z.; Lai, C.S.; Lai, L.L. Integrated Underfrequency Load Shedding Strategy for Islanded Microgrids Integrating Multiclass Load-Related Factors. IEEE Trans. Smart Grid 2025, 367, 123343. [Google Scholar] [CrossRef]

- IEEE Std 519-2022; Standard for Harmonic Control in Electric Power Systems. IEEE: Piscataway, NJ, USA, 2022.

- IEC 61000-3-2:2018; Electromagnetic Compatibility (EMC)—Part 3-2: Limits—Limits for Harmonic Current Emissions (Equipment Input Current ≤ 16 A per Phase). International Electrotechnical Commission: Geneva, Switzerland, 2018.

- Hartmann, M.; Miniboeck, J.; Ertl, H.; Kolar, J.W. A Three-Phase Delta Switch Rectifier for Use in Modern Aircraft. IEEE Trans. Ind. Electron. 2012, 59, 3635–3647. [Google Scholar] [CrossRef]

- Gong, G.; Heldwein, M.L.; Drofenik, U.; Mino, K.; Kolar, J.W. Comparative Evaluation of Three-Phase High Power Factor AC-DC Converter Concepts for Application in Future More Electric Aircrafts. In Proceedings of the Nineteenth Annual IEEE Applied Power Electronics Conference and Exposition, 2004. APEC ’04., Anaheim, CA, USA, 22–26 February 2004; Volume 2, pp. 1152–1159. [Google Scholar]

- Siu, K.K.M.; Ho, C.N.M. Manitoba Rectifier—Bridgeless Buck–Boost PFC. IEEE Trans. Power Electron. 2020, 35, 403–414. [Google Scholar] [CrossRef]

- Perez-Tarragona, M.; Sarnago, H.; Lucia, O.; Burdio, J.M. Multiphase PFC Rectifier and Modulation Strategies for Domestic Induction Heating Applications. IEEE Trans. Ind. Electron. 2021, 68, 6424–6433. [Google Scholar] [CrossRef]

- Al-Saffar, M.A.; Ismail, E.H.; Sabzali, A.J. Integrated Buck–Boost–Quadratic Buck PFC Rectifier for Universal Input Applications. IEEE Trans. Power Electron. 2009, 24, 2886–2896. [Google Scholar] [CrossRef]

- Kim, J.-S.; Lee, S.-H.; Cha, W.-J.; Kwon, B.-H. High-Efficiency Bridgeless Three-Level Power Factor Correction Rectifier. IEEE Trans. Ind. Electron. 2017, 64, 1130–1136. [Google Scholar] [CrossRef]

- Lange, A.D.B.; Soeiro, T.B.; Ortmann, M.S.; Heldwein, M.L. Three-Level Single-Phase Bridgeless PFC Rectifiers. IEEE Trans. Power Electron. 2015, 30, 2935–2949. [Google Scholar] [CrossRef]

- Ma, H.; Zheng, K.; Jiang, H.; Yin, H. A Family of Dual-Boost Bridgeless Five-Level Rectifiers with Common-Core Inductors. IEEE Trans. Power Electron. 2021, 36, 12565–12578. [Google Scholar] [CrossRef]

- Lee, Y.-D.; Kim, D.; Choi, S.-H.; Moon, G.-W.; Kim, C.-E. New Bridgeless Power Factor Correction Converter with Simple Gate Driving Circuit and High Efficiency for Server Power Applications. IEEE Trans. Power Electron. 2020, 35, 13148–13156. [Google Scholar] [CrossRef]

- Meng, T.; Ben, H.; Li, C.; Wei, G. Investigation and Implementation of a Passive Snubber with a Coupled-Inductor in a Single-Stage Full-Bridge Boost PFC Converter. J. Power Electron. 2013, 13, 206–213. [Google Scholar] [CrossRef]

- Chen, J.-F.; Chen, R.-Y.; Liang, T.-J. Study and Implementation of a Single-Stage Current-Fed Boost PFC Converter with ZCS for High Voltage Applications. IEEE Trans. Power Electron. 2008, 23, 379–386. [Google Scholar] [CrossRef]

- Hu, Y.; Huber, L.; Jovanović, M.M. Single-Stage, Universal-Input AC/DC LED Driver With Current-Controlled Variable PFC Boost Inductor. IEEE Trans. Power Electron. 2012, 27, 1579–1588. [Google Scholar] [CrossRef]

- Cao, J.; Pei, Y.; Wang, Z. Analysis of Power Dissipation of Switching Components in Boost PFC Circuit. Adv. Technol. Electr. Eng. Energy 2002, 21, 41–44. [Google Scholar]

| Switching Device | Voltage Stress |

|---|---|

| S1 | Udc |

| S2 | Udc |

| S3 | Udc/2 |

| D1–D4 | Udc |

| D5, D6 | Udc/2 |

| D7, D8 | Udc/2 |

| Parameters | Value |

|---|---|

| Input AC voltage | 220 V |

| Output DC voltage | 400 V |

| Rated output power | 1 kW |

| Switching frequency | 20 kHz |

| Input inductor | 2.5 mH |

| Split DC-link capacitor | 2000 μF |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, Y.; Yu, Z.; Lu, Y.; Chen, Z. Efficiency Analysis of Bridgeless Three-Level PFC Circuits Based on Modal Segment Integration Method. Electronics 2025, 14, 3592. https://doi.org/10.3390/electronics14183592

Huang Y, Yu Z, Lu Y, Chen Z. Efficiency Analysis of Bridgeless Three-Level PFC Circuits Based on Modal Segment Integration Method. Electronics. 2025; 14(18):3592. https://doi.org/10.3390/electronics14183592

Chicago/Turabian StyleHuang, Yuehua, Ziyang Yu, Yun Lu, and Zhuo Chen. 2025. "Efficiency Analysis of Bridgeless Three-Level PFC Circuits Based on Modal Segment Integration Method" Electronics 14, no. 18: 3592. https://doi.org/10.3390/electronics14183592

APA StyleHuang, Y., Yu, Z., Lu, Y., & Chen, Z. (2025). Efficiency Analysis of Bridgeless Three-Level PFC Circuits Based on Modal Segment Integration Method. Electronics, 14(18), 3592. https://doi.org/10.3390/electronics14183592