This chapter presents an overview of various techniques for generating signals that belong to the PDM group.

2.1. Generation of Variable Pulse-Width Signals

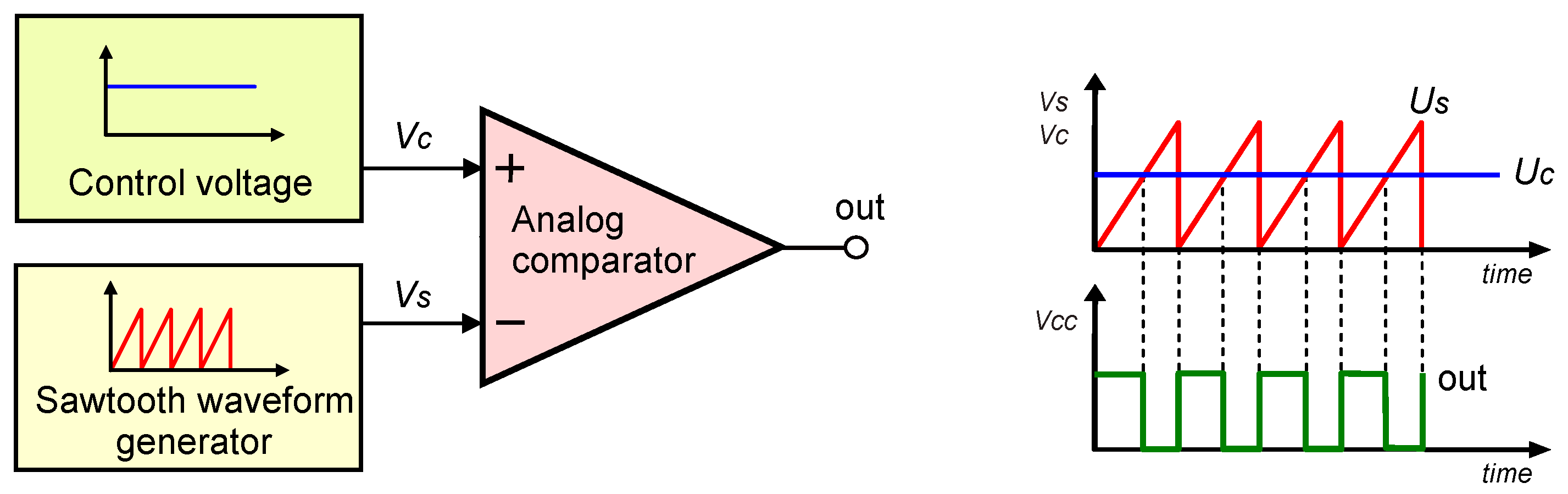

The most straightforward analog implementation of a PWM generator is presented in

Figure 1, as a simplified block form. The voltage

at the output of the sawtooth waveform generator increases linearly until it reaches its maximum value. When the sawtooth voltage equals the control voltage

, the analog comparator changes the state of its output voltage. As a result, the generated PWM signal (whose pulse duty cycle depends on the relationship between the control voltage

and the sawtooth waveform voltage

) has a frequency equal to the frequency of the generated sawtooth signal

.

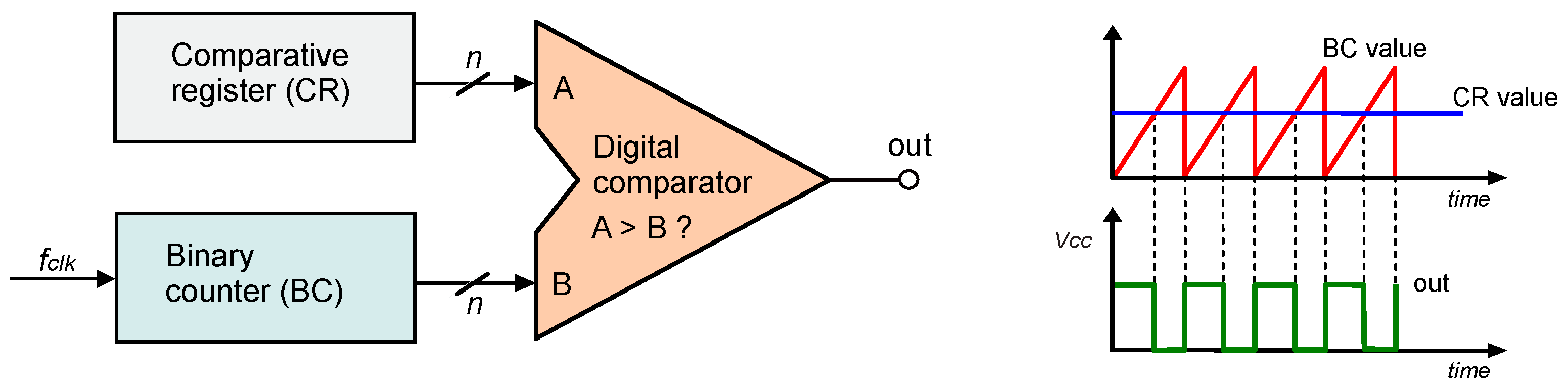

The same concept can be applied almost directly to digital circuits. An example counter-based solution of a digital PWM generator in the form of a simplified block diagram is shown in

Figure 2.

The simplest form of the digital PWM generator consists of an

n-bit binary counter BC that counts down or up and an

n-bit comparative register CR, which stores information about the desired pulse width. If a down counter is used, it is loaded during overflow with a value corresponding to the period of the generated modulated signal. The CR register stores the digital value, representing the duty cycle of the generated pulses (

Figure 2). The frequency of the clock signal

(

Figure 2) is

times higher than the output frequency of the PWM signal (Equation (

1)). In the case of high-resolution (large n value) and high-PWM signal frequency, the required clock signal frequency may be difficult to obtain. When the counter value is lower than the value of the CR register, the digital comparator output is set to the high logic level “1” but can easily be inverted.

where

n is the bit resolution of the PWM counter, defining the number of discrete steps (

) per PWM period.

The PWM signal can be described as follows [

27]:

where

A is the amplitude of the PWM signal (in the following expressions it is assumed that

),

T is the signal period expressed in seconds [s],

is the dimensionless duty cycle, and

is the time. The notation (

) expresses the cyclic nature of the signal that repeats every

T seconds:

The symbol

denotes the floor function, which returns the highest integer less than or equal to its argument. The PWM signal can also be represented as an infinite sum of rectangular functions shifted by the period

T:

where

denotes the rectangular function, defined as

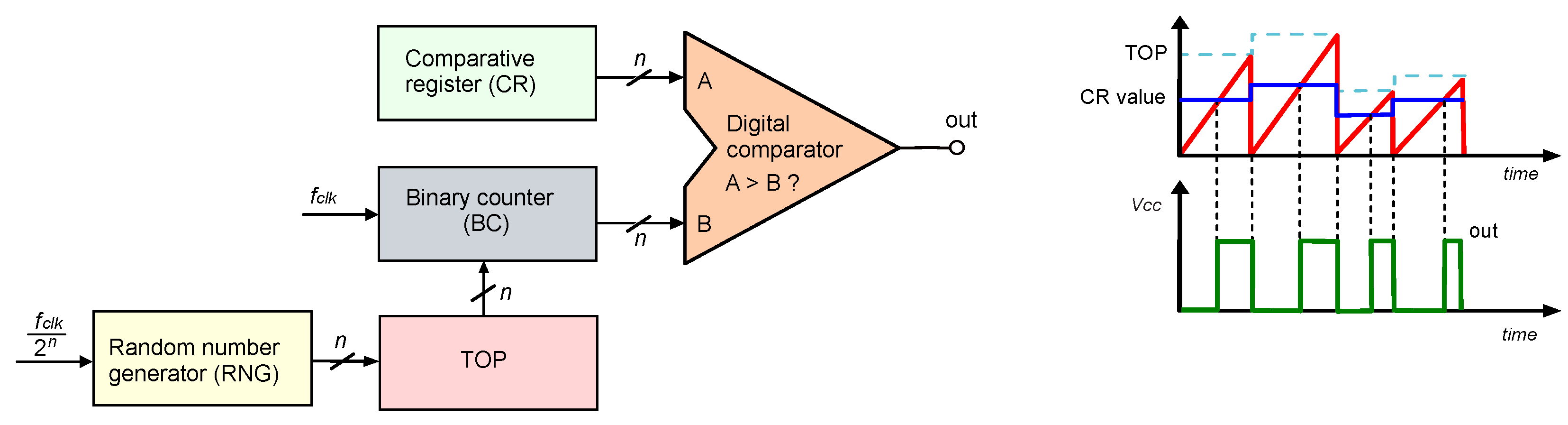

Digital control and PWM signals are a source of electromagnetic interference generation. The harmonics generated are particularly severe at low frequencies, which implies problems with output filter design. There is always a compromise between the price and size of the output filter (which influences the output signal quality) and, on the other hand, the dynamics of the output signals. SPDM (stochastic pulse-density modulation) or SSDM (stochastic signal density modulation) concepts can be considered an alternative. The idea is to spread the energy of the generated harmonics over a wider frequency band to make it easier to filter out these particularly undesirable harmonics due to their lower amplitudes. SPDM uses random (or pseudorandom) signal density modulation during the control period to generate a signal with a given average density.

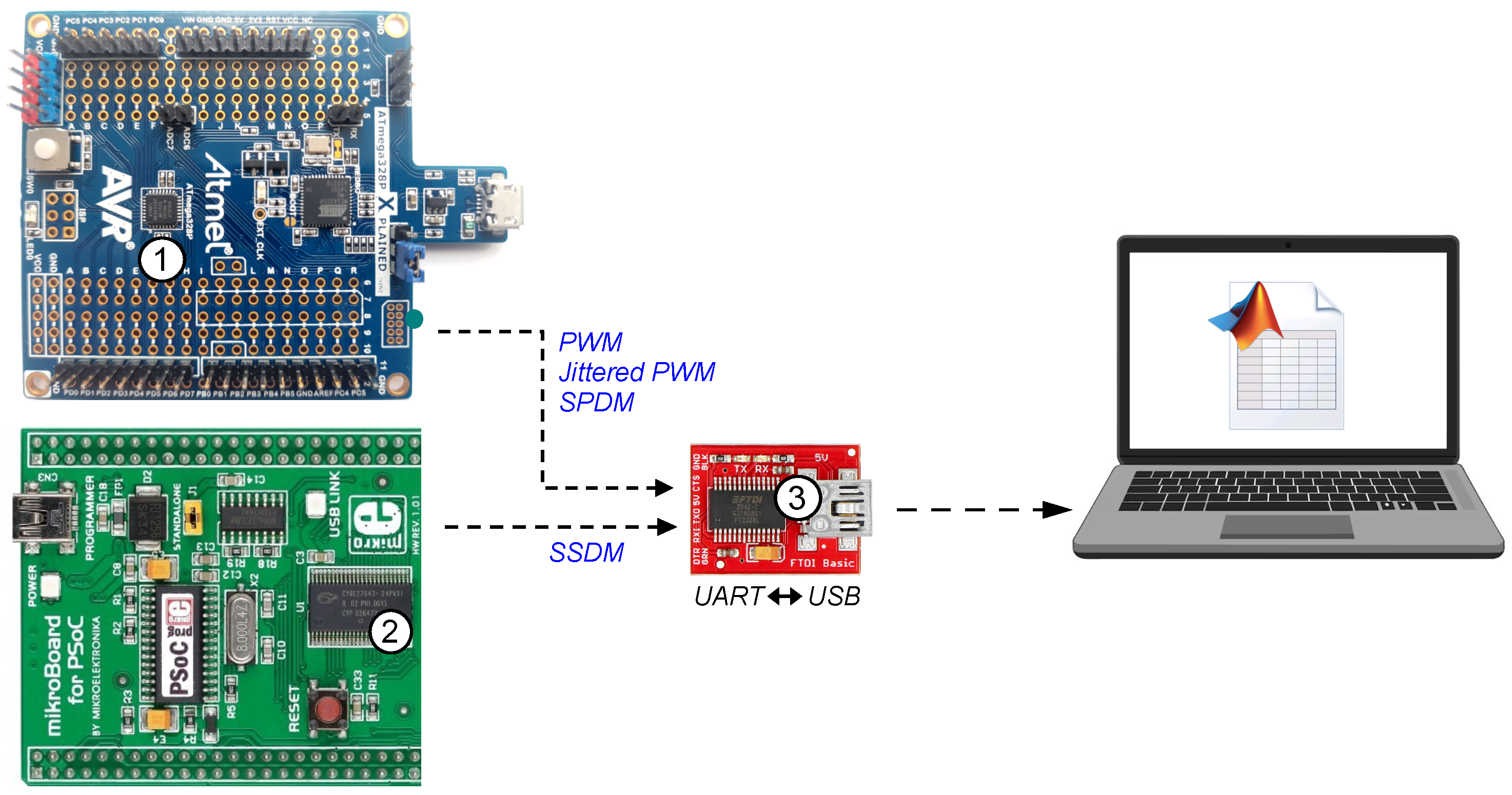

Figure 3 shows the basic components of a typical SPDM modulator. In this configuration, the maximum frequency of the generated SPDM waveform is equal to

, which is the (random number generator) RNG clock frequency (

Figure 3). For a practical use of this technique, PSoC systems (programmable system-on-chip) equipped with the necessary hardware blocks (e.g., random number generator) can be used [

28]. Another viable option is to employ microcontrollers integrated with the appropriate hardware solutions.

The SPDM is a binary stochastic modulation technique. Each signal sample is independently determined according to a predefined probability [

29,

30,

31]. This probability corresponds to the desired signal density. The SPDM signal

is modeled as a Bernoulli random process according to the following formula:

where

is the signal value in sample

n, and

is the modulation probability, representing the target average duty cycle (expected signal density). Physically,

p defines the expected proportion of time the signal remains at a high logic level (“1”), which directly determines the mean output voltage and affects the spectral properties of the SPDM waveform. This implies

, and

. For example, if

, then on average one out of every four samples will be equal to 1. Over time, the mean signal value will converge to 0.25, but high signal levels are randomly distributed. That feature distinguishes SPDM from SSDM, in which randomness is generated deterministically using an LFSR (linear feedback shift register) and compared with a reference value. SPDM is therefore a probabilistic modulation scheme. In the SPDM signal, the duty cycle for the

n-th period depends on the number of pulses

in that period, where

is a random variable (for example, following a Bernoulli distribution). The formula for the duty cycle

in the

n-th period is given by the following:

where

is the number of pulses in the

n-th period, and

is the maximum possible number of pulses that can fit into one period, based on the system clock. For a Bernoulli process, the expected duty cycle is as follows:

and the variance of the duty cycle is

The presented SSDM generator does not use a binary counter in its structure. The generated waveform has a variable frequency and is not a PWM signal. Variable frequency control signals cannot be used in every power converter topology. In many power electronic converter topologies, especially in utilizing resonant circuits and soft switching of semiconductor power devices, changing the control frequency may cause unfavorable operating conditions for the power switches. That may severely degrade the conversion efficiency. However, random sequences can be used in systems controlled at a constant frequency with PWM signals, using solutions based on binary counters. In this type of configuration, no resonant circuits are used; therefore, the resonance period does not need to be maintained. The only limitation is the maximum frequency that can be used with acceptable switching losses. An example of a PWM generator that works with a randomly set duty cycle is shown in

Figure 4. A constant frequency signal is obtained, and a random sequence controls the duty cycle. The RNG (random number generator) is clocked at

. This causes the PWM signal duty cycle to change every time the binary counter (BC) overflows. The current random value is compared to the BC binary counter. The stochastic modulated PWM signal is obtained from the output of the digital comparator (

Figure 4).

The next presented idea of a modified PWM may be called a jittered PWM. In this case, the signal is a PWM waveform with duty factor intentionally subjected to controlled jitter [

32,

33,

34]. Jitter in pulse-width modulation normally refers to unwanted variations in the timing of the PWM signal, essentially a deviation from the intended frequency and duty cycle. This can affect the accuracy of the PWM signal, leading to problems in applications such as motor control, audio generation, or data transmission. But in this case, if the jitter is properly controlled, the controlled output power may be properly set, the generated frequency spectrum is widespread, and the lower harmonics are attenuated.

Let the nominal period be

T and the nominal high-time duration be

. The jitter is modeled as a random variable

added to the falling edge timing in each PWM signal period

n:

where

T is the nominal period,

is the nominal duration of the high state (pulse width), and

is the jitter applied to the falling edge timing in the

n-th period and is a random variable with a bounded distribution typically satisfying

. Due to falling edge jitter, the instantaneous duty cycle

in each period

n is slightly varied. The instantaneous duty cycle is defined as follows:

Assuming that

is a random variable of zero mean (

), the expected value and variance of the duty cycle are

This shows that jitter around the falling edge can be used to spread the spectrum of the PWM signal without changing its average energy.

The effect of jitter on the falling edge of the PWM signal can be modeled using different statistical distributions for the jitter value . Two common distributions are the uniform and the Gaussian (bounded) distribution.

- 1.

Uniform distribution: The jitter

is uniformly distributed in the interval [

,

]:

This means that the jitter has an equal probability of being any value within this range. The instantaneous duty cycle of the PWM signal is then affected by this jitter at each period n, with the falling edge of the signal shifted by a random amount within this interval.

- 2.

Gaussian distribution (bounded): The jitter

follows a Gaussian (normal) distribution with a mean of 0 and a standard deviation

:

However, to avoid excessive jitter, it is bounded within the interval [, ]. This ensures that the jitter does not exceed a certain threshold. The Gaussian jitter typically causes smaller and more concentrated variations in the timing of the falling edge compared to the uniform distribution.

The uniform jitter distribution introduces an equal probability that the jitter is at any point within the defined range, causing noticeable random shifts in the falling edge timing of the PWM signal. The Gaussian jitter results in smaller and more concentrated variations around the mean, leading to subtler shifts in the duty factor.

Figure 5 shows another topology of a PDM family, with a variable frequency output signal. This configuration uses a digital comparator to compare the set value of the CR comparative register with the state of the BC binary counter. The BC is clocked at the frequency

and its capacity can be set by changing the TOP value (

Figure 5). The TOP value is the maximum value of the binary counter. The counter counts from zero to the TOP value and then overflows and counts from zero again. Changing the top value affects the counter capacity and, as a result, the period of the generated PDM (pulse-density modulation) signal. In this configuration, the RNG random number generator, which is necessary to obtain the SPDM signal, is clocked at

. The binary counter is clocked at

. The maximum output signal frequency that can appear in the SPDM output signal is also

.

A similar effect can be achieved using the topology shown in

Figure 6. In this case, the counter does not count from zero, but from the set BOTTOM value. Changing this value changes the period of the generated PDM signal. If the change in the BOTTOM value is controlled by a random sequence from the RNG generator, an SPDM signal is obtained at the digital comparator output. The RNG generator must be clocked at frequency

, while the BC counter is clocked at

. As in the previous configurations, the counter capacity affects the resolution of the output signal control. The set value, stored in the OCR register, can be fixed or variable, depending on the application’s needs.

2.2. Stochastic Signal Density Modulation

Stochastic signal density modulation SSDM is a power modulation technique that can be viewed as a special case of pulse-density modulation (PDM) or random pulse-width modulation (RPWM). An example block diagram, which illustrates the principle of SSDM signal generation, is shown in

Figure 7. Pseudorandom-width pulses adjust the output power level. Pulses are generated such that the average signal value reflects the predefined ratio of high to low states.

The RNG generates random numbers that modify the output frequency of the clock generator CG. The clock signal clocks with modulated frequency the binary counter BC. The comparative CR register stores the value to compare with the binary counter. The SSDM signal is achieved at the comparator output.

SSDM is a binary signal

generated based on the comparison of a random sequence with a reference value [

35,

36]. This process modulates the signal density in a stochastic manner. The general form of

is given by the following:

where

is the signal value in sample

n,

is the modulation density with

, and

is the random sequence.

In SSDM, the pulse density

refers to the average number of pulses per unit of time. The pulse density directly influences the duty cycle. For the period

n-th, the duty cycle

is defined as follows:

where

is the number of pulses in the

n-th period, and

T is the total time of a single period. The pulse density

is defined as the average number of pulses per time unit and can be written as follows:

where

is the average number of pulses per period

T. Therefore,

will be related to the specified pulse density

, and these parameters will be on average the same:

. The average duty cycle in SSDM with

will be equal to the given pulse density:

The variance of the duty cycle

depends on the statistical distribution of pulses over time. Assuming that the pulses follow a Poisson distribution (a common model for stochastic processes with a specified rate), the variance of the duty cycle is equal to the pulse density

. This can be expressed as follows:

Thus, the variance equals the specified signal density when the pulses are randomly distributed according to a Poisson distribution.

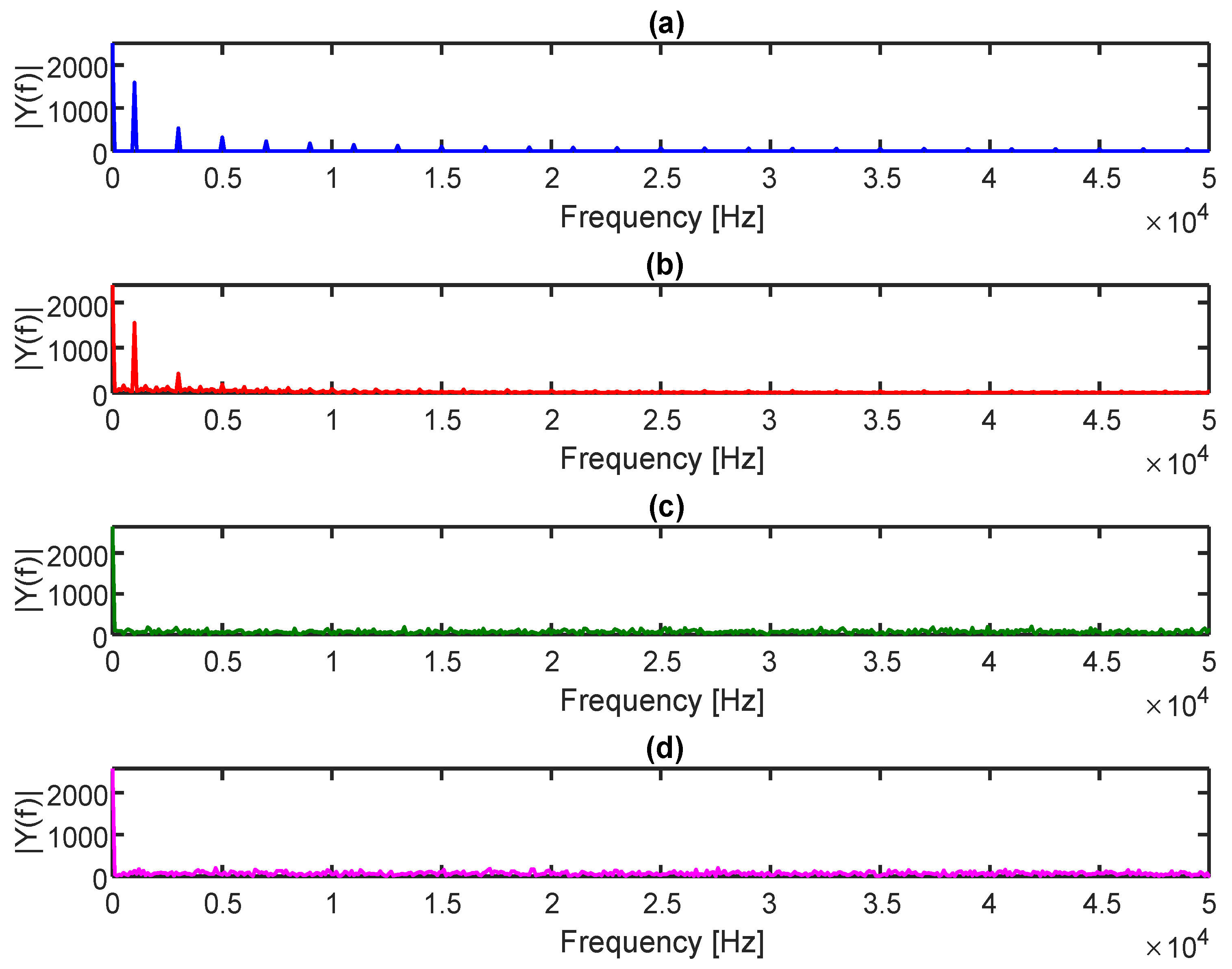

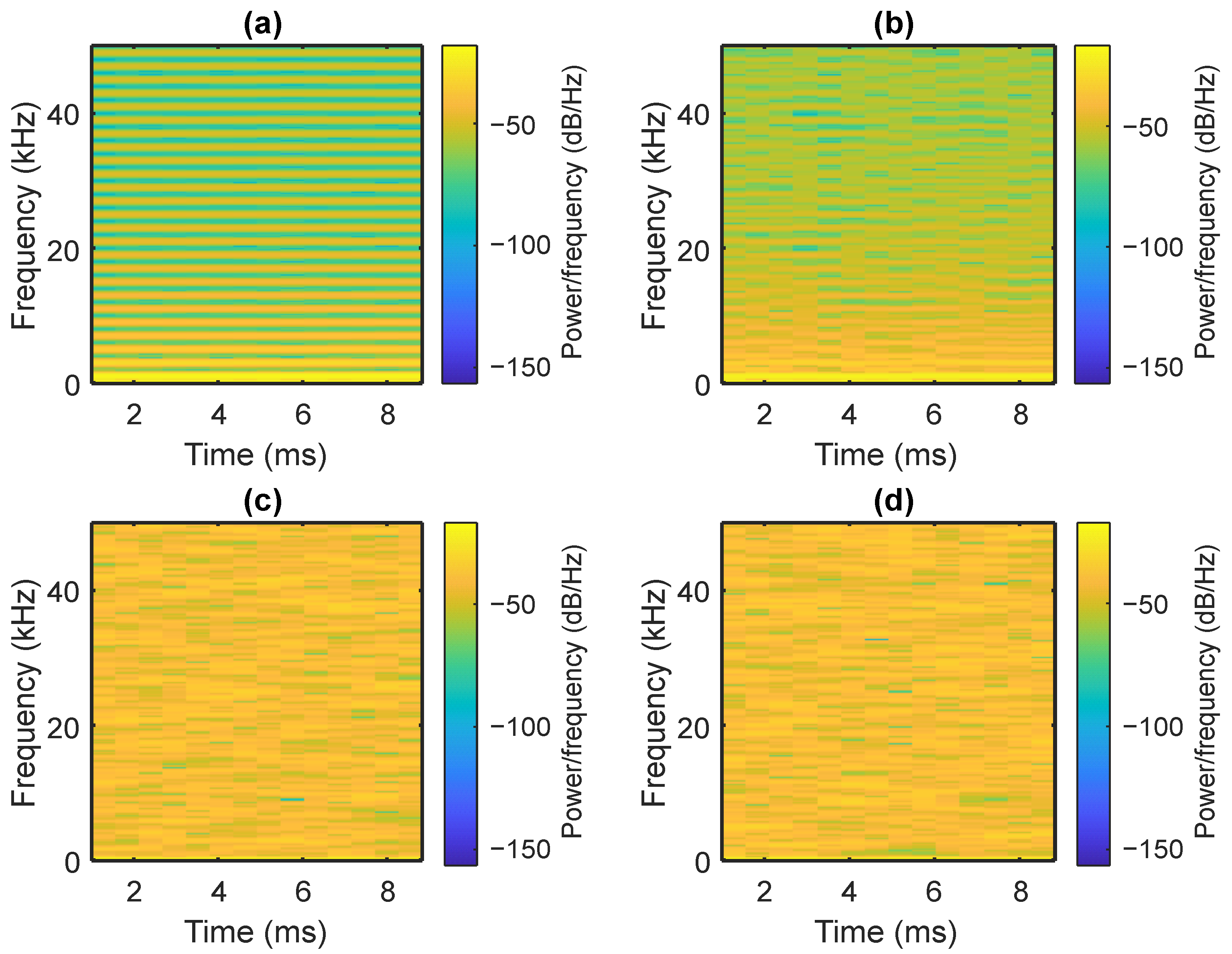

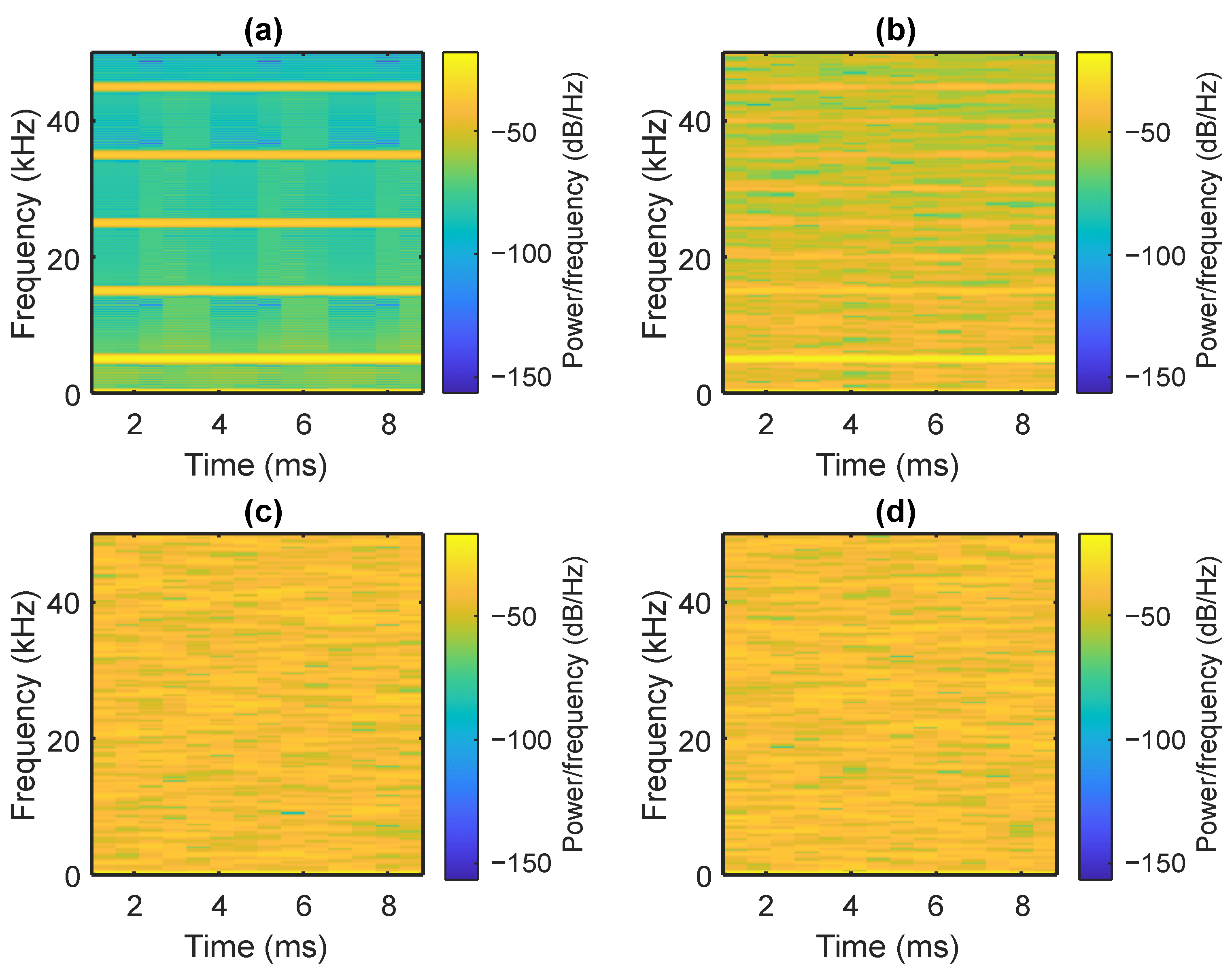

2.3. Spectral and Statistical Analysis of Variable Pulse-Width Modulated Signals

In digital modulation techniques, the spectral characteristics of the output signal are crucially important, especially in power electronics and audio applications. The following forms are the most common for signal representation and analysis [

37,

38,

39,

40,

41].

The discrete Fourier transform DFT is a fundamental tool for analyzing the frequency components present in a discrete-time signal. It allows identification of periodic content and harmonic structure in digital modulation schemes. The spectrum

of a digital signal

can be calculated using the following formula:

where

is the input signal in discrete time,

is the Fourier transform coefficient in the frequency bin

k,

N is the number of samples, and

j is the imaginary unit.

The power spectral density PSD describes how the power of a signal is distributed across different frequencies. It is useful for evaluating spectral spreading and harmonic suppression in modulated signals. The following expression provides an estimate of the discrete-time PSD:

where

is the discrete-time signal,

is the sampling frequency, and

N is the number of samples used for the estimation.

The spectrogram provides a time-varying view of the spectral content of a signal. It reveals how energy distribution across frequencies evolves, which is particularly useful for analyzing nonstationary or jittery signals. It is calculated as follows:

where

is the discrete-time signal,

is a window function (e.g., Hamming or Hann) centered at time

t,

f is the frequency, and

j is the imaginary unit.

Autocorrelation quantifies the similarity between a signal and a delayed version of itself. It helps identify periodicities, signal predictability, and the degree of randomness in switching patterns. The discrete-time autocorrelation function is calculated as follows:

where

is the delay in the samples and

N is the number of samples.