Active Gate Drive Based on Negative Feedback for SiC MOSFETs to Suppress Crosstalk Parasitic Oscillation and Avoid Decreased Efficiency

Abstract

1. Introduction

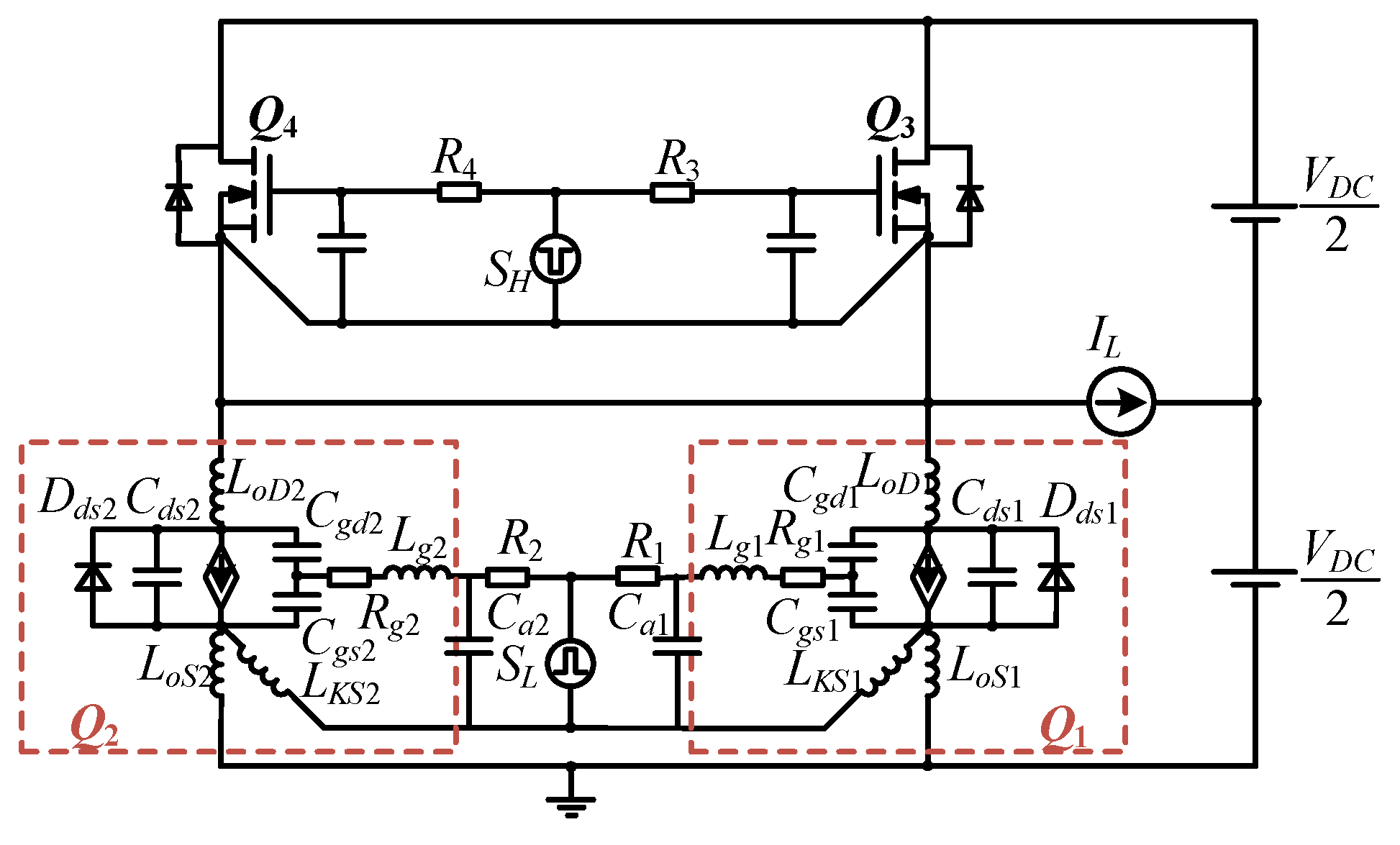

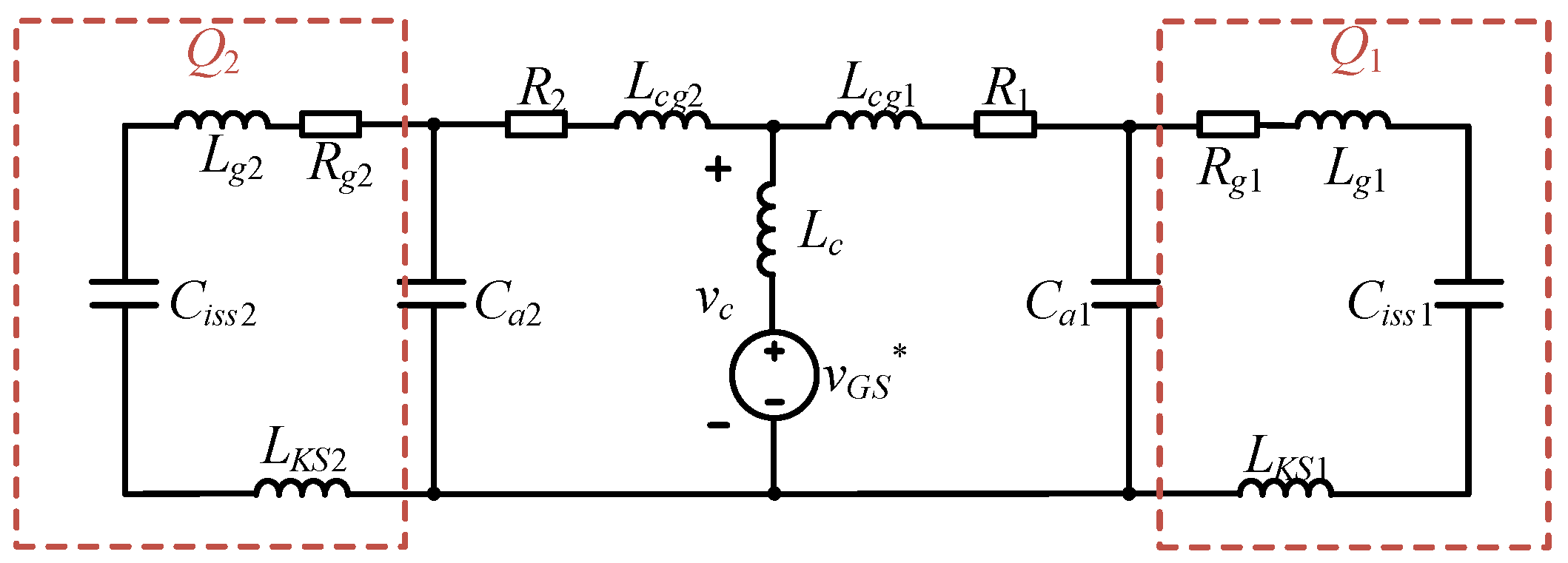

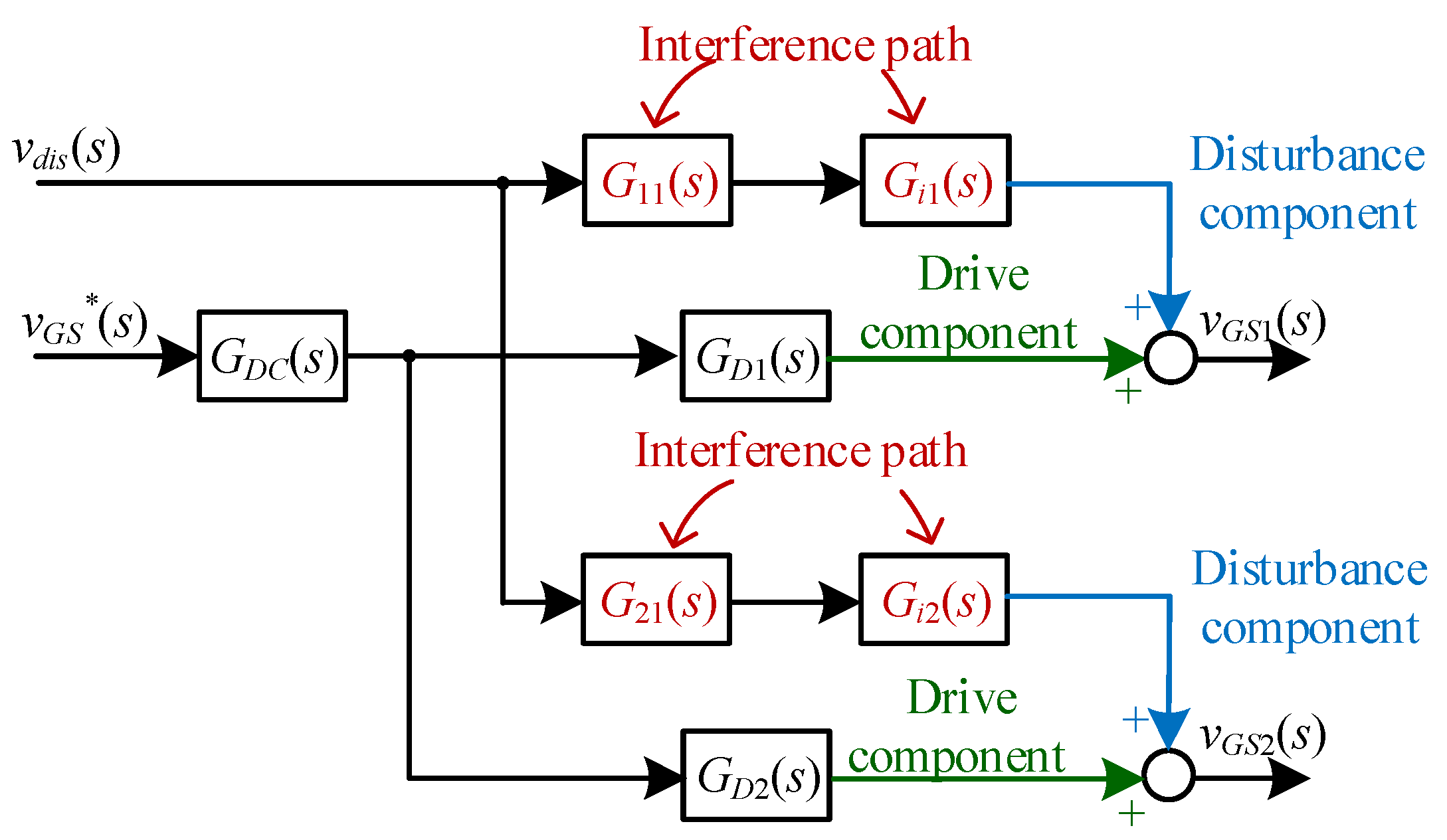

2. Dynamic Model of the Interference Path

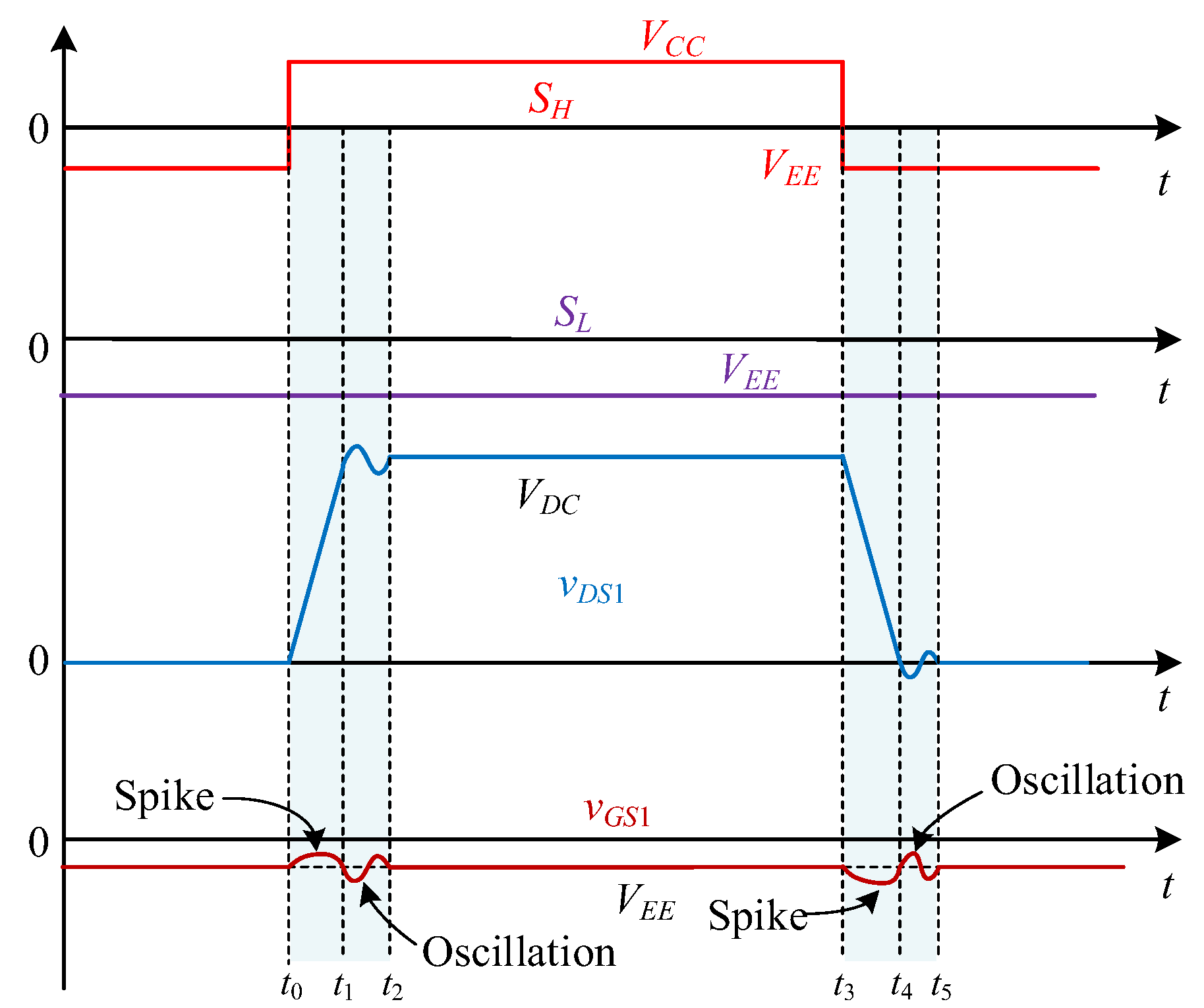

2.1. Typical Voltage Oscillation Phenomenon

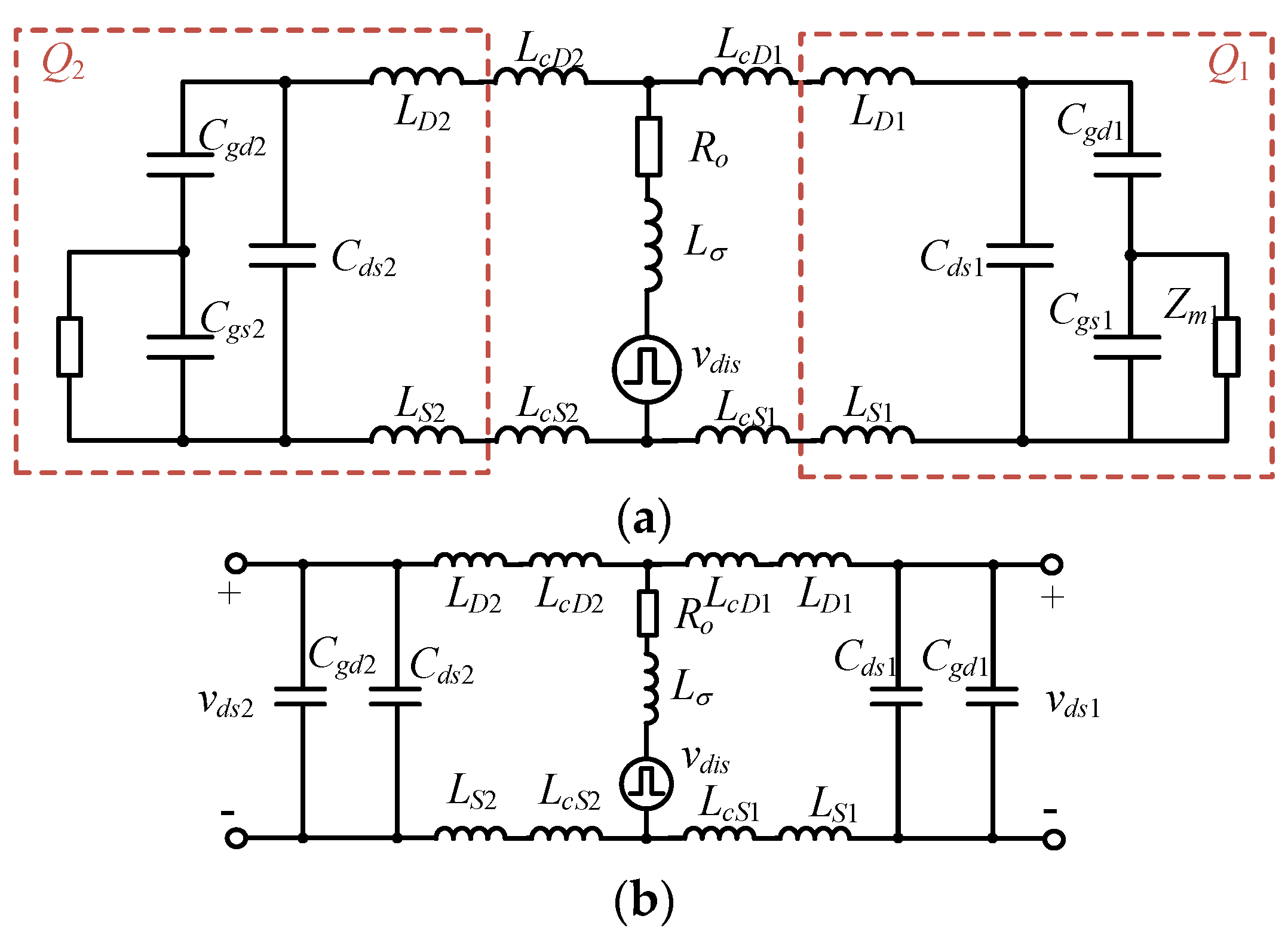

2.2. Dynamic Model: Disturbance Component

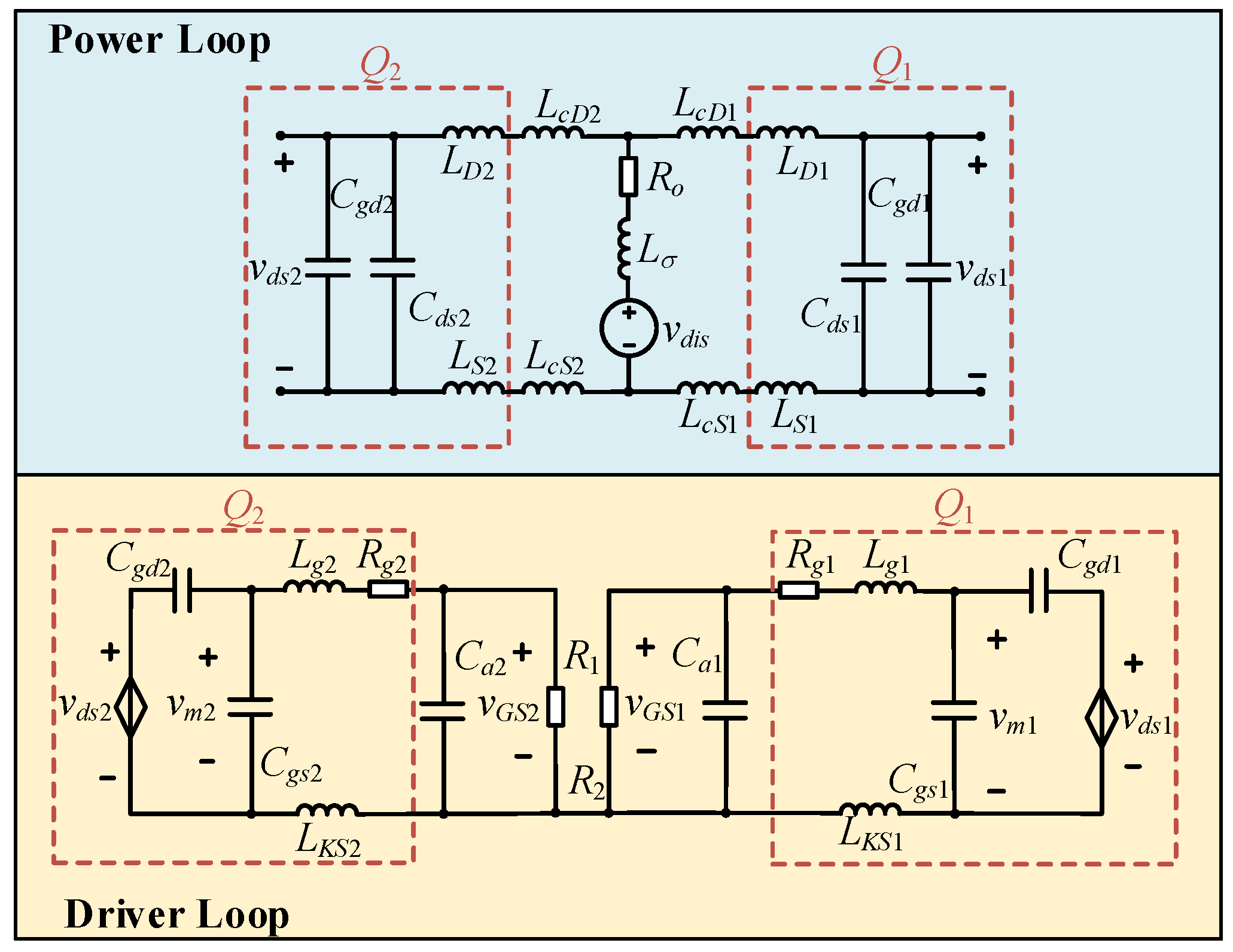

2.3. Dynamic Model: Drive Component

3. Crosstalk Parasitic Oscillation Suppression Strategy

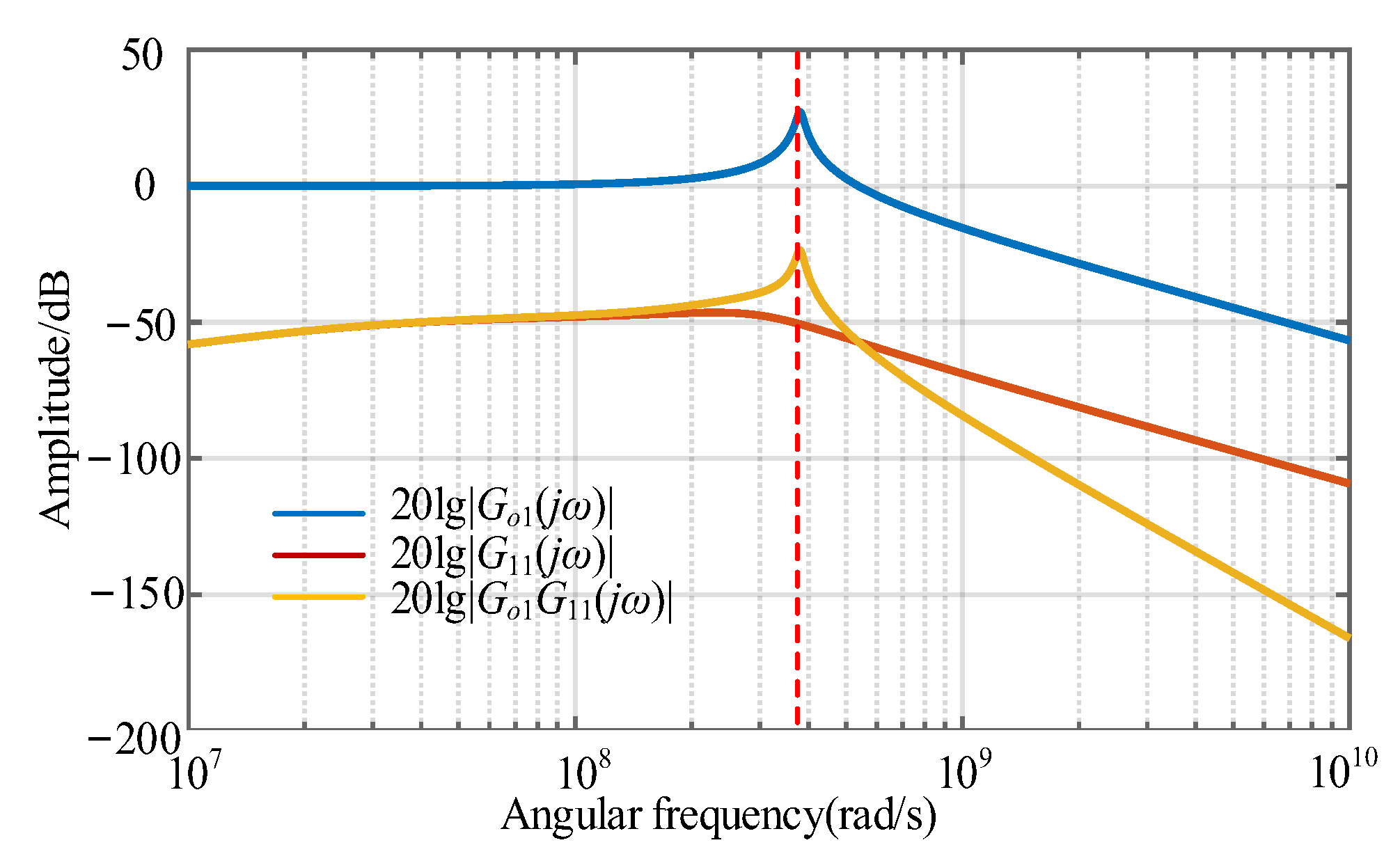

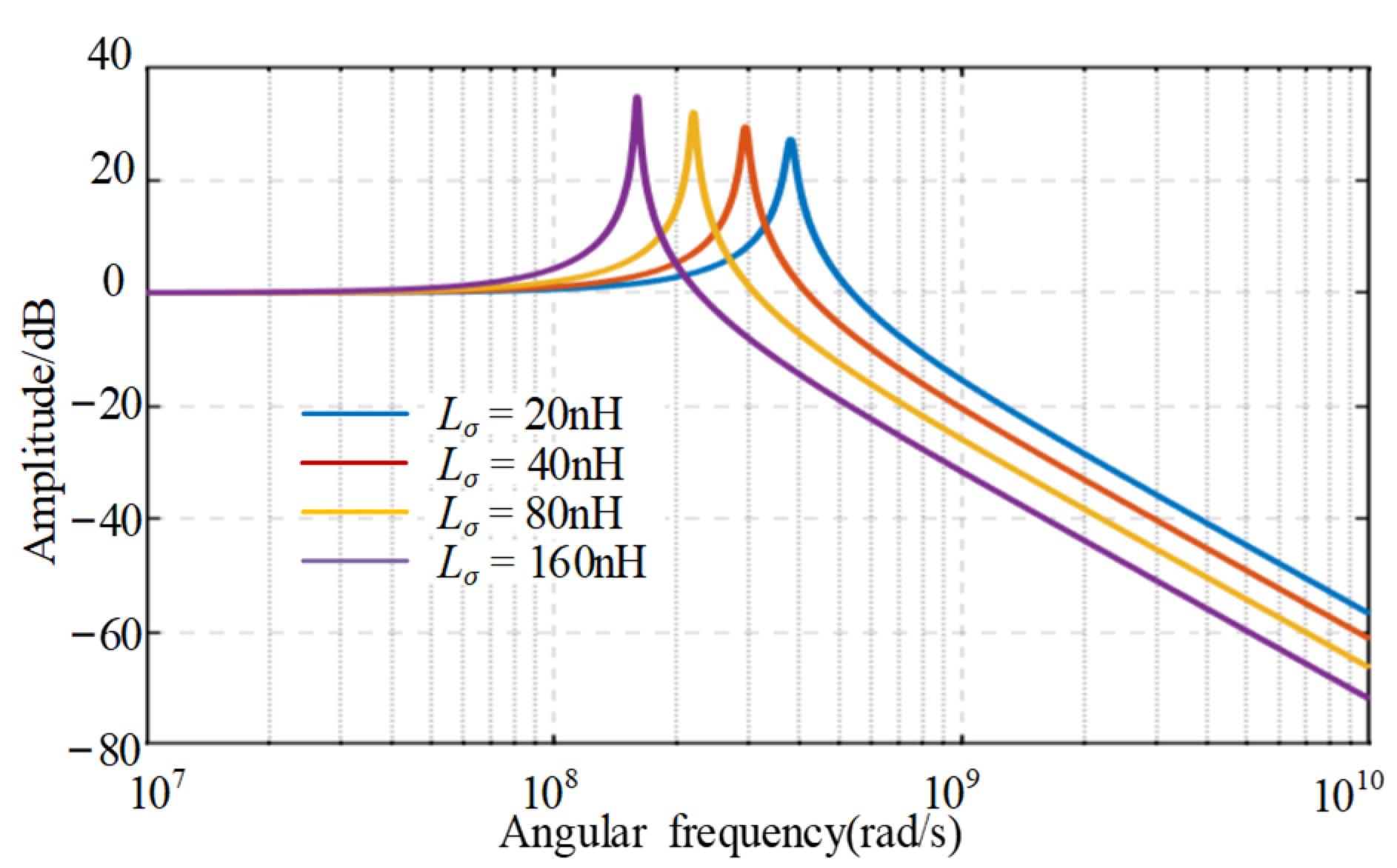

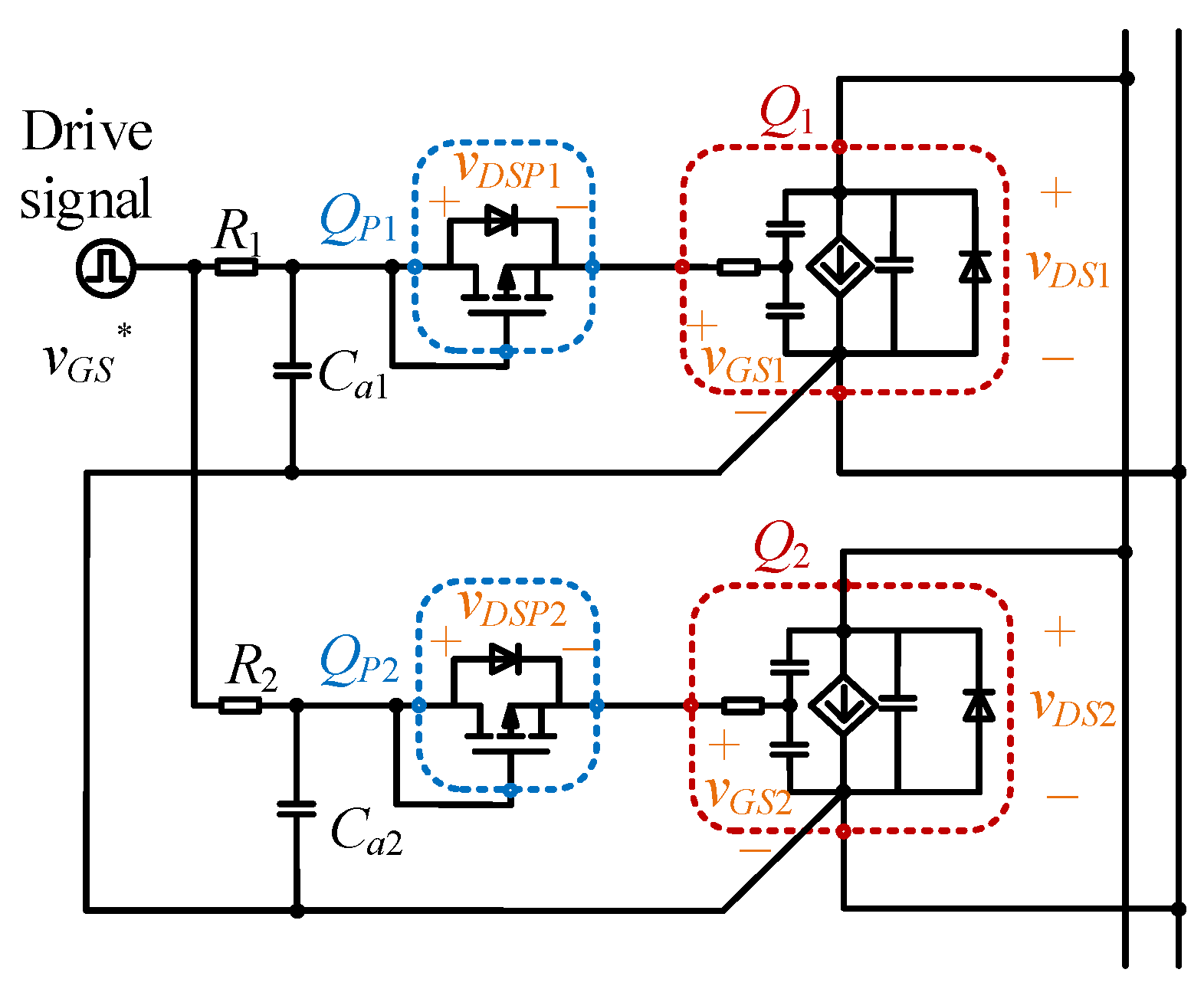

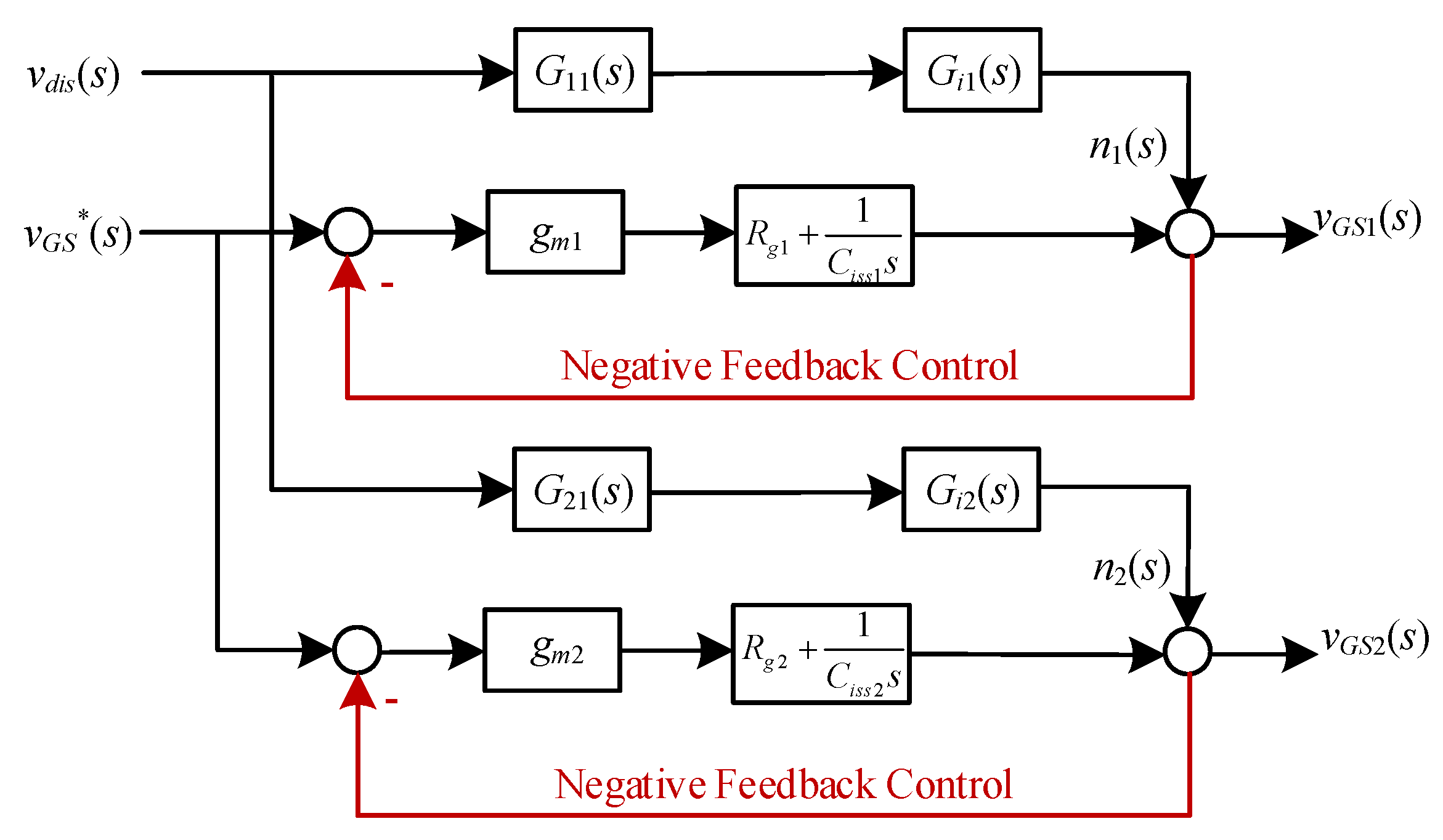

3.1. Crosstalk Parasitic Oscillation in Parallel Devices

3.1.1. Impact of Power Loop Stray Inductance

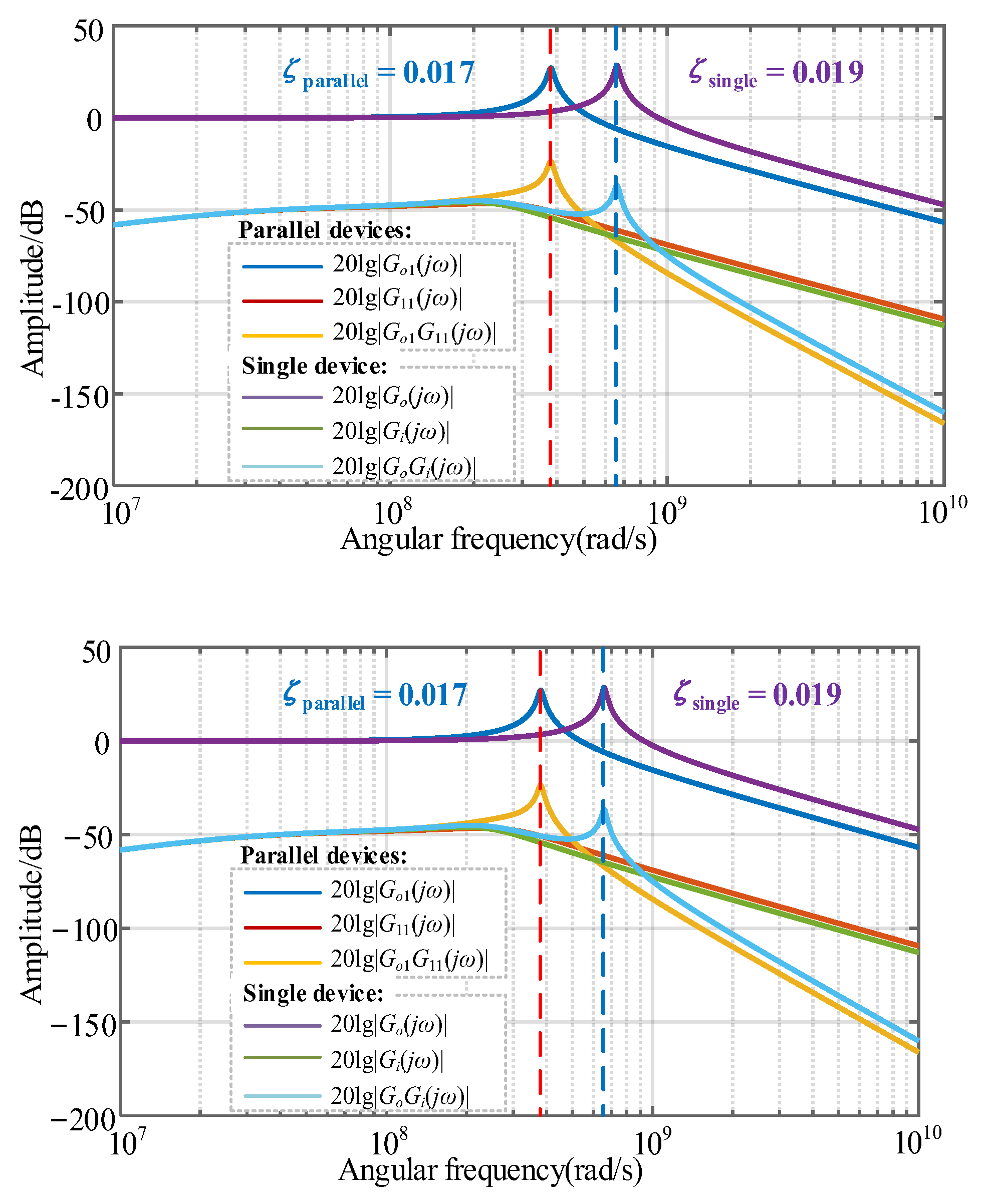

3.1.2. Comparison Between Parallel Devices and Single Device

3.2. Operation Principle of NFAGD in Parallel Devices

3.3. Parameter Design Recommendation

4. Experiment Verification

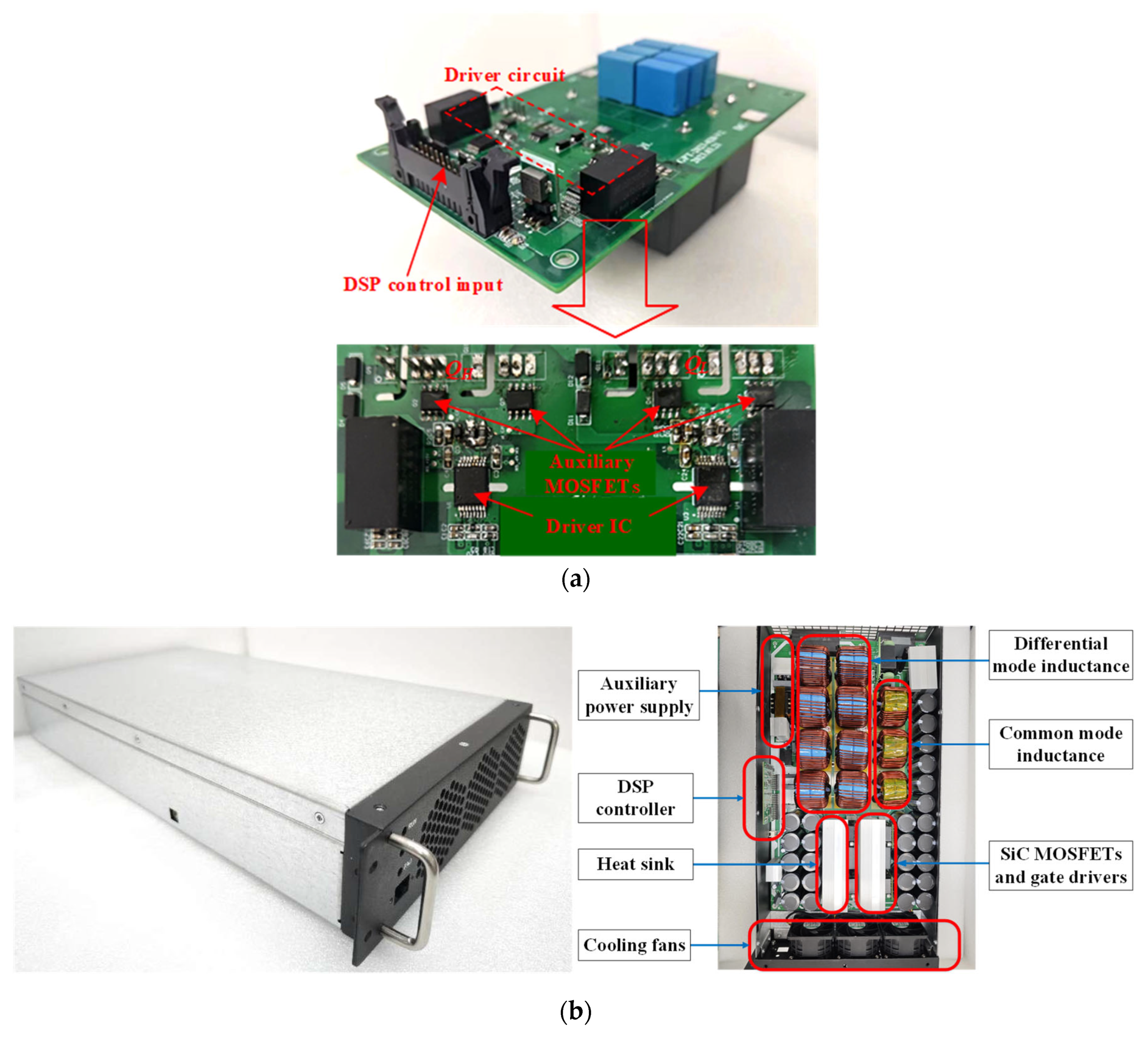

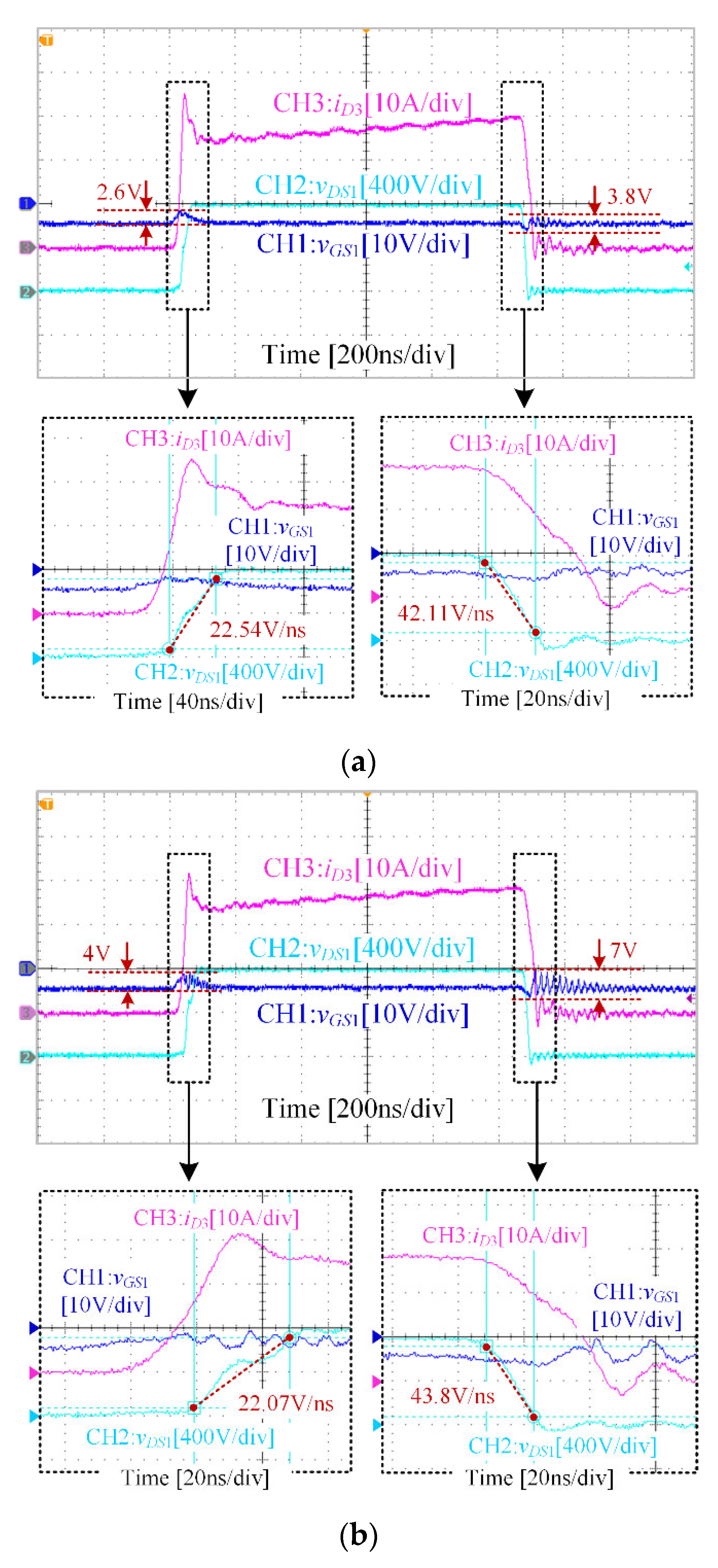

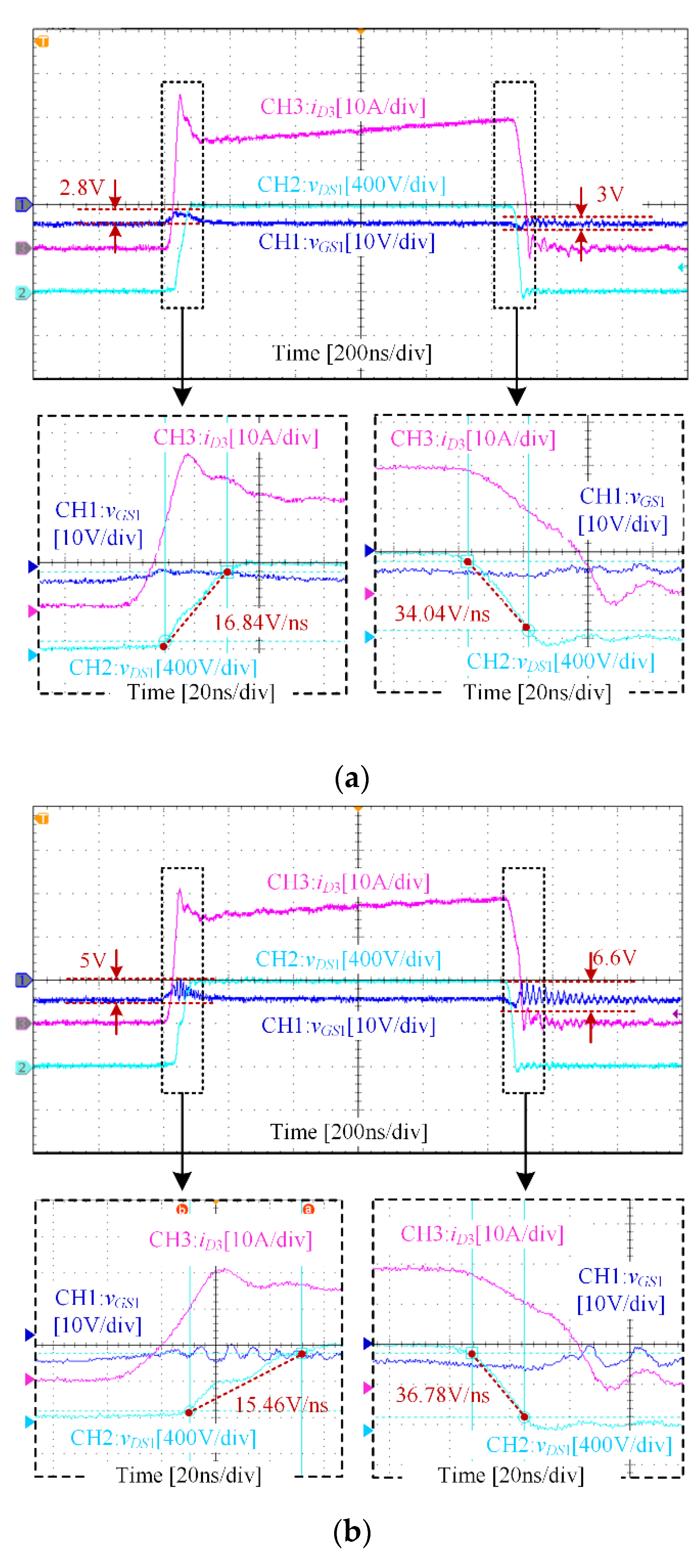

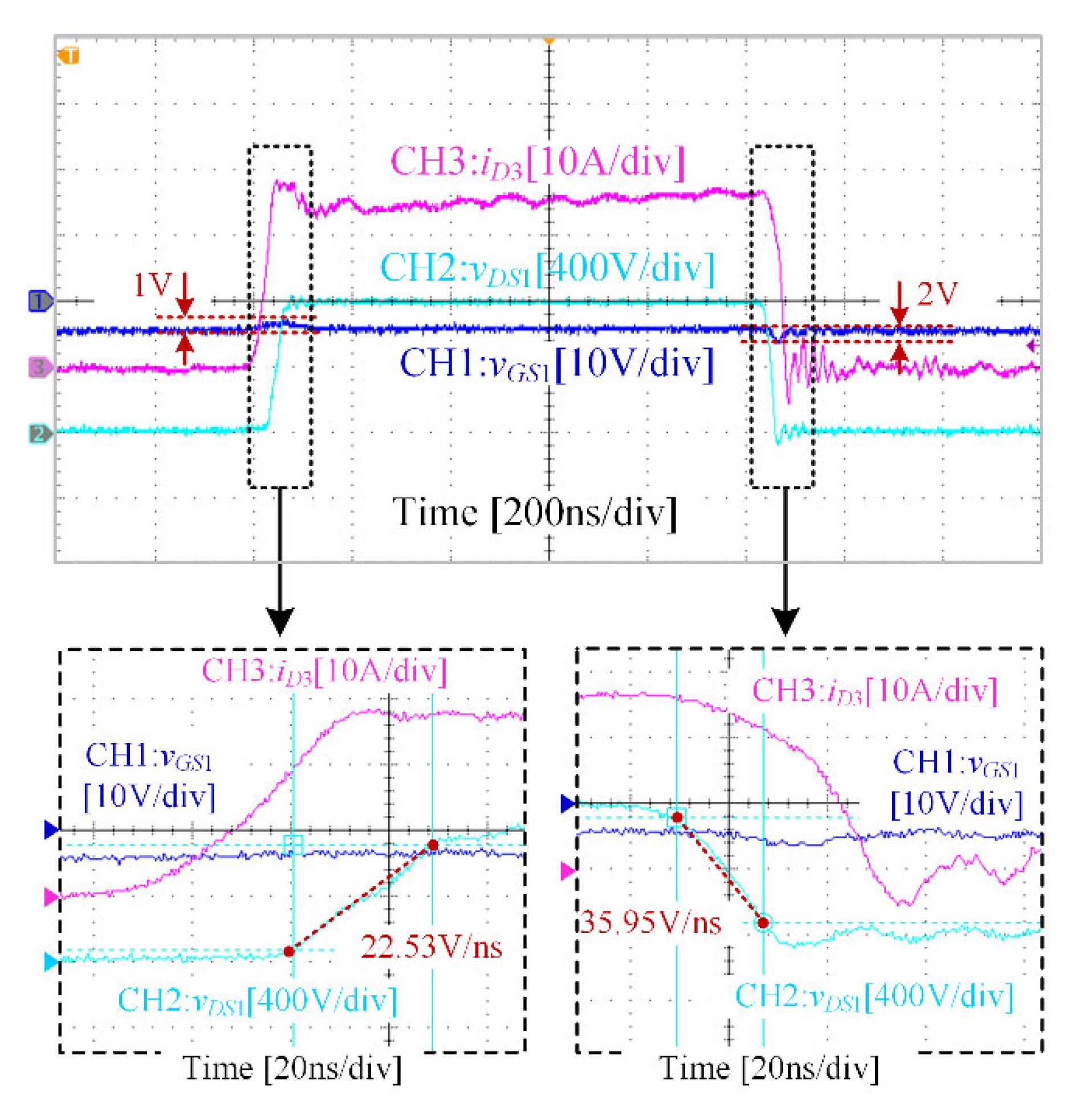

4.1. Double-Pulse Test

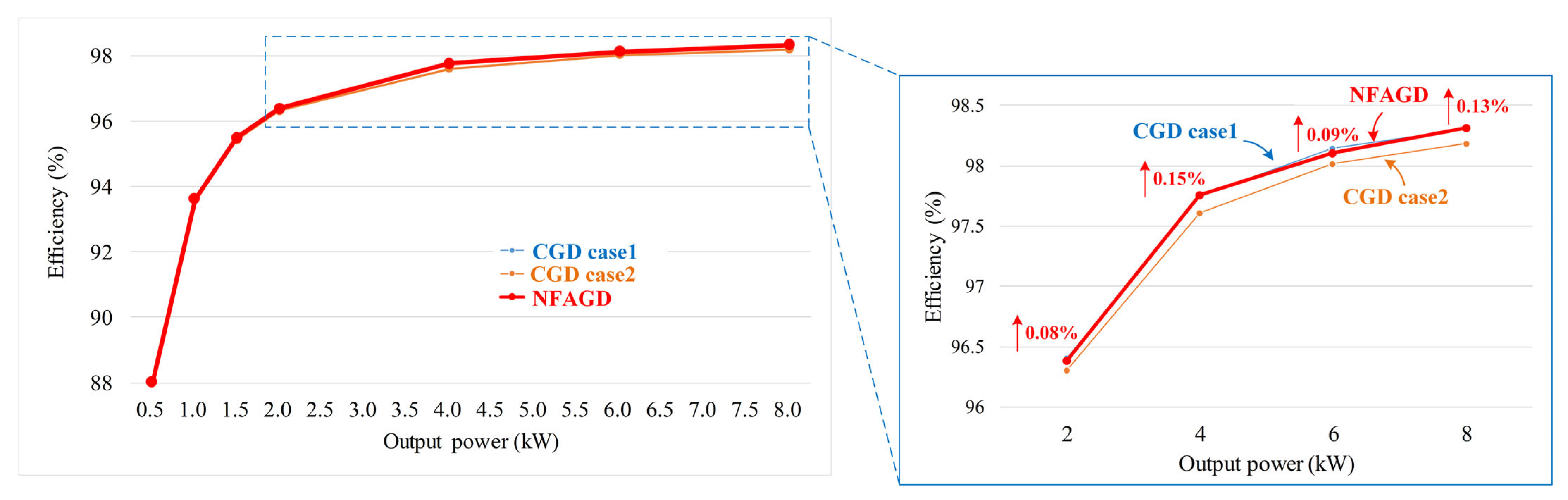

4.2. Synchronous Buck Converter Prototype Verification

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Nomenclature

| NFAGD | Negative feedback active gate drive. |

| Q1, Q2 | Passive devices |

| Q3, Q4 | Active devices |

| QP1, QP2 | P-channel auxiliary MOSFETs |

| vdis | Disturbance voltage source |

| vGS* | Gate drive signal |

| R1, R2, R3, R4 | External gate drive resistances |

| Lσ | Power loop inductance |

| Rg1, Rg2 | Internal gate resistances |

| Ciss1, Ciss2 | Input capacitance |

| Lg1, Lg2 | Drive stray inductance |

| LKS1, LKS2 | Kelvin stray inductance |

| LoD1, LoD2 | Drain stray inductance |

| LoS1, LoS2 | Source stray inductance |

| gm1, gm2 | Transconductance of QP1 and QP2 |

| KSC | Speed/crosstalk ratio |

References

- Zeng, Z.; Shao, W.; Hu, B.; Chen, H.; Liao, X.; Chen, W.; Li, H.; Ran, L. Chances and challenges of photovoltaic inverters with silicon carbide devices. Renew. Sustain. Energy Rev. 2017, 78, 624–639. [Google Scholar] [CrossRef]

- Qian, Z.; Zhang, J.; Sheng, K. Status and Development of Power Semiconductor Devices and Its Applications. Proc. CSEE 2014, 34, 5149–5161. [Google Scholar]

- Sheng, K.; Ren, N.; Xu, H. A Recent Review on Silicon Carbide Power Devices Technologies. Proc. CSEE 2020, 40, 1735–1741. [Google Scholar]

- Wang, F.; Zhang, Z. Overview of Silicon Carbide Technology: Device, Converter, System, and Application. CPSS Trans. Power Electron. Appl. 2016, 1, 13–32. [Google Scholar] [CrossRef]

- Shi, B.; Zhao, Z.; Jiang, Y.; Zhu, Y. Multi-Time Scale Transient Models for Power Semiconductor Devices (Part I: Switching Characteristics and Transient Modeling). Trans. China Electrotech. Soc. 2017, 32, 16–24. [Google Scholar]

- Jiang, Y.; Zhao, Z.; Shi, B.; Yuan, L. Multi-Time Scale Transient Models for Power Semiconductor Devices (Part II: Applications Analysis and Model Connection). Trans. China Electrotech. Soc. 2017, 32, 25–32. [Google Scholar]

- He, J.; Liu, Y.; Bi, D.; Li, X. Impacts of Voltage Probes for Accurate Measurement of High-Frequency Transient Voltage of Wide-Bandgap Devices. Trans. China Electrotech. Soc. 2021, 36, 362–372. [Google Scholar]

- Schrittwieser, L.; Leibl, M.; Haider, M.; Thöny, F.; Kolar, J.W.; Soeiro, T.B. 99.3% efficient three-phase buck-type all-SiC SWISS rectifier for DC distribution systems. IEEE Trans. Power Electron. 2019, 34, 126–140. [Google Scholar] [CrossRef]

- Li, Y.; Liang, M.; Chen, J.; Zheng, T.Q.; Guo, H. A Low Gate Turn–OFF Impedance Driver for Suppressing Crosstalk of SiC MOSFET Based on Different Discrete Packages. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 353–365. [Google Scholar] [CrossRef]

- Li, H.; Qiu, Z.; Shao, T.; Zeng, Y.; Du, H.; Yin, C. A Low Level–Clamped Active Gate Driver for Crosstalk Suppression of SiC MOSFET Based on dv/dt Detection. In Proceedings of the 2021 IEEE Energy Conversion Congress and Exposition (ECCE), Vancouver, BC, Canda, 10–14 October 2021; pp. 5348–5353. [Google Scholar]

- Li, H.; Jiang, Y.; Qiu, Z.; Shao, T.; Wang, Y. A Multi-step Active Gate Driver for Suppressing Crosstalk of SiC MOSFET. In Proceedings of the 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 29 November–2 December 2020. [Google Scholar]

- Qiu, Z.; Li, H.; Jiang, Y.; Shao, T.; Yang, Z.; Wang, J.; Zhang, Z. An Intelligent Three-level Active Gate Driver for Crosstalk Suppression of SiC MOSFET. In Proceedings of the Twelfth Annual IEEE Energy Conversion Congress and Exposition (ECCE 2020), Detroit, MI, USA, 10–15 October 2020. [Google Scholar]

- Zhang, Z.; Dix, J.; Wang, F.; Blalock, B.J.; Costinett, D.; Tolbert, L.M. Intelligent Gate Drive for Fast Switching and Crosstalk Suppression of SiC Devices. IEEE Trans. Power Electron. 2017, 32, 9319–9332. [Google Scholar] [CrossRef]

- Aichinger, T.; Rescher, G.; Pobegen, G. Threshold Voltage Peculiarities and Bias Temperature Instabilities of SiC MOSFETs. Microelectron. Reliab. 2018, 80, 68–78. [Google Scholar] [CrossRef]

- Yu, H.; Liang, S.; Liu, H.; Wang, J.; Shen, Z.J. Numerical Study of SiC MOSFET With Integrated n-/n-Type Poly-Si/SiC Heterojunction Freewheeling Diode. IEEE Trans. Electron Devices 2021, 68, 4571–4576. [Google Scholar] [CrossRef]

- Peters, D.; Aichinger, T.; Basler, T.; Rescher, G.; Puschkarsky, K.; Reisinger, H. Investigation of Threshold Voltage Stability of SiC MOSFETs. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 40–43. [Google Scholar]

- Burkart, R.M.; Kolar, J.W. Comparative Life Cycle Costs Analysis of Si and SiC PV Converter Systems Based on Advanced η-ρ-σ Multi–Objective Optimization Techniques. IEEE Trans. Power Electron. 2017, 32, 4344–4358. [Google Scholar] [CrossRef]

- Burkart, R.M.; Kolar, J.W. Comparative η–ρ–σ Pareto Optimization of Si and SiC Multilevel Dual-Active-Bridge Topologies With Wide Input Voltage Range. IEEE Trans. Power Electron. 2017, 32, 5258–5270. [Google Scholar] [CrossRef]

- Ba, T.; Li, Y.; Liang, M. The Effect of Parasitic Parameters on Gate–Source Voltage of SiC MOSFET. Trans. China Electrotech. Soc. 2016, 31, 64–73. [Google Scholar]

- Duan, Z.; Zhang, D.; Fan, T. Modeling and Prediction of Electromagnetic Interference in SiC Motor Drive Systems. Trans. China Electrotech. Soc. 2020, 35, 4726–4738. [Google Scholar]

- Zhang, Z.; Guo, B.; Wang, F.F.; Jones, E.A.; Tolbert, L.M.; Blalock, B.J. Methodology for Wide Band-Gap Device Dynamic Characterization. IEEE Trans. Power Electron. 2017, 32, 9307–9318. [Google Scholar] [CrossRef]

- Chen, J.; Du, X.; Luo, Q.; Zhang, X.; Sun, P.; Zhou, L. A Review of Switching Oscillations of Wide Bandgap Semiconductor Devices. IEEE Trans. Power Electron. 2020, 35, 13182–13199. [Google Scholar] [CrossRef]

- Wang, X.; Zhu, Y.; Zhao, Z.; Chen, K. Impact of Gate-Loop Parameters on the Switching Behavior of SiC MOSFETs. Trans. China Electrotech. Soc. 2017, 32, 23–30. [Google Scholar]

- Zhang, W.; Huang, X.; Lee, F.C.; Li, Q. Gate Drive Design Considerations for High Voltage Cascode GaN HEMT. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition–APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 1484–1489. [Google Scholar]

- Liu, P.; Guo, S.; Yu, R.; Huang, A.Q.; Zhang, L. Analysis of Trade-Off Between Noise and Wide Band-Gap (WBG) Device Switching Speed. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 3483–3489. [Google Scholar]

- Yang, X.; Li, J.; Ding, Y.; Xu, M.; Zhu, X.; Zhu, J. Observation of Transient Parity-Time Symmetry in Electronic Systems. Phys. Rev. Lett. 2022, 128, 065701. [Google Scholar] [CrossRef]

- Yang, X.; Yuan, Y.; Long, Z.; Goncalves, J.; Palmer, P.R. Robust Stability Analysis of Active Voltage Control for High-power IGBT Switching by Kharitonov’s Theorem. IEEE Trans. Power Electron. 2016, 31, 2584–2595. [Google Scholar] [CrossRef]

- Wang, K.; Yang, X.; Wang, L.; Jain, P. Instability Analysis and Oscillation Suppression of Enhancement-Mode GaN Devices in Half-Bridge Circuits. IEEE Trans. Power Electron. 2018, 33, 1585–1596. [Google Scholar] [CrossRef]

- Zeng, Z.; Li, X. Comparative Study on Multiple Degrees of Freedom of Gate Drivers for Transient Behavior Regulation of SiC MOSFET. IEEE Trans. Power Electron. 2018, 33, 8754–8763. [Google Scholar] [CrossRef]

- Zhu, T.; Zhuo, F.; Zhao, F.; Wang, F.; Zhao, T. Quantitative Model-Based False Turn-on Evaluation and Suppression for Cascode GaN Devices in Half-Bridge Applications. IEEE Trans. Power Electron. 2019, 34, 10166–10179. [Google Scholar] [CrossRef]

- Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Active Gate Driver for Crosstalk Suppression of SiC Devices in a Phase-Leg Configuration. IEEE Trans. Power Electron. 2014, 29, 1986–1997. [Google Scholar] [CrossRef]

- Zhao, S.; Dearien, A.; Wu, Y.; Farnell, C.; Rashid, A.U.; Luo, F.; Mantooth, H.A. Adaptive Multi-Level Active Gate Drivers for SiC Power Devices. IEEE Trans. Power Electron. 2020, 35, 1882–1898. [Google Scholar] [CrossRef]

- STMicroelectronics AN-5355, Mitigation Technique of the SiC MOSFET Gate Voltage Glitches with Miller Clamp. 2019. Available online: https://www.st.com/resource/en/application_note/dm00628522-mitigation-technique-of-the-sic-mosfet-gate-voltage-glitches-with-miller-clamp-stmicroelectronics.pdf (accessed on 15 February 2025).

- Avago Technologies AN-5314, Active Miller Clamp. 2010. Available online: https://docs.broadcom.com/doc/AV02-0072EN (accessed on 15 February 2025).

- Shao, T.; Zheng, T.Q.; Li, H.; Liu, J.; Li, Z.; Huang, B.; Qiu, Z. The Active Gate Drive Based on Negative Feedback Mechanism for Fast Switching and Crosstalk Suppression of SiC Devices. IEEE Trans. Power Electron. 2022, 37, 6739–6754. [Google Scholar] [CrossRef]

- Shao, T.; Zheng, T.Q.; Li, Z.; Li, H.; Liu, J. SiC MOSFET Gate Driver Design Based on Interference Dynamic Response Mechanism. Trans. China Electrotech. Soc. 2021, 36, 4204–4214. [Google Scholar]

- JESD24; Power MOSFETs. JEDEC: Arlington, VA, USA, 1985.

- Gao, Y.; Chen, Q. Silicon Carbide Power Semiconductor Devices: Characteristics, Testing and Applications; China Machine Press: Beijing, China, 2021. [Google Scholar]

| Drive Method | Typical Max. dv/dt | Influence of Switching Speed 1 | Typical Gate Parasitic Oscillation 2 | Speed/Crosstalk Ratio KSC | Constitutive Complexity 3 |

|---|---|---|---|---|---|

| Conventional Gate Drive (CGD) [29] | 35 V/ns | 100% | 6.6 V @36.78 V/ns | 5.57 | 2 devices: 1R, 1 IC |

| Gate Impedance Regulation (GIR) [31] | 25 V/ns | 71% | 1.5 V @24.4 V/ns [31] | 16.27 [31] | 5 devices: 1R, 2 IC, 1 SW, 1 C |

| Gate Voltage Control (GVC) [31] | 25 V/ns | 71% | 3.2 V @24.9 V/ns [31] | 7.78 [31] | 7 devices: 1R, 3 IC, 2 SW, 1 D |

| Intelligent Gate Drive (IGD) [13] | 20 V/ns | 57% | 4.16 V @22 V/ns [13] | 5.29 [13] | 8 devices: 1R, 3 IC, 2 SW, 2 D |

| Multi-level Active Gate Driver [32] | 10 V/ns | 29% | 10 V @10.7 V/ns [32] | 1.07 [32] | 7 devices: 1R, 2 IC, 4 SW |

| Active Miller Clamp (AMC) [15,33] | 20 V/ns | 57% | 10 V @30 V/ns [33] | 3 [33] | 7 devices: 1R, 2 IC, 4 SW |

| Negative Feedback Active Gate Drive (NFAGD) | 40 V/ns | 114% | 2 V @35.95 V/ns | 17.98 | 4 devices: 1R, 1 IC, 1 SW, 1C |

| Parameters | Symbols | Type Values |

|---|---|---|

| Input Capacitance | Ciss | 1900 pF |

| Output Capacitance | Coss | 115 pF |

| Reverse Transmission Capacitance | Crss | 13 pF |

| Gate Internal Resistor | Rg | 4 Ω |

| Parameters | Values/Type |

|---|---|

| Turn-on bias voltage (VCC) | 15 V |

| Turn-off bias voltage (VEE) | −4 V |

| CGD Case 1: drive resistance | 10 Ω |

| CGD Case 2: drive resistance | 15 Ω |

| NFAGD: drive resistance | 1.65 Ω |

| NFAGD: auxiliary MOSFET (QP) | BSO201SP |

| NFAGD: auxiliary capacitor (Ca) | 10 nF |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shao, T.; Sun, Y.; Bai, Z.; Zheng, T.Q.; Zhang, Y.; Jia, P. Active Gate Drive Based on Negative Feedback for SiC MOSFETs to Suppress Crosstalk Parasitic Oscillation and Avoid Decreased Efficiency. Electronics 2025, 14, 2100. https://doi.org/10.3390/electronics14112100

Shao T, Sun Y, Bai Z, Zheng TQ, Zhang Y, Jia P. Active Gate Drive Based on Negative Feedback for SiC MOSFETs to Suppress Crosstalk Parasitic Oscillation and Avoid Decreased Efficiency. Electronics. 2025; 14(11):2100. https://doi.org/10.3390/electronics14112100

Chicago/Turabian StyleShao, Tiancong, Yuhan Sun, Zhitong Bai, Trillion Q. Zheng, Yajing Zhang, and Pengyu Jia. 2025. "Active Gate Drive Based on Negative Feedback for SiC MOSFETs to Suppress Crosstalk Parasitic Oscillation and Avoid Decreased Efficiency" Electronics 14, no. 11: 2100. https://doi.org/10.3390/electronics14112100

APA StyleShao, T., Sun, Y., Bai, Z., Zheng, T. Q., Zhang, Y., & Jia, P. (2025). Active Gate Drive Based on Negative Feedback for SiC MOSFETs to Suppress Crosstalk Parasitic Oscillation and Avoid Decreased Efficiency. Electronics, 14(11), 2100. https://doi.org/10.3390/electronics14112100