A P-Q Coordination Control Strategy of VSC-HVDC and BESS for LVRT Recovery Performance Enhancement

Abstract

1. Introduction

- (1)

- An active power absorption control rule is proposed for a BESS to absorb active power according to the voltage drop during the LVRT process. Such a design can improve the system frequency regulation dynamics and enhance the system transient stability.

- (2)

- An adaptive current limitation method is proposed for a BESS in which the active and reactive current references will be limited according to the frequency and voltage deviation during the recovery process. In this way, the active and reactive powers can be dynamically adjusted while considering the frequency and voltage fluctuation degree and the constraint of the converter-rated capacity to provide both frequency and voltage support.

- (3)

- The coordination sequence of the sending-end systems and DC chopper is improved to reduce the surplus power that needs to be dissipated and to lower the requirement for electronic devices. Additionally, such coordination can also allow the sending- end systems to provide frequency regulation, with the DC voltage transmitting frequency information during the recovery process.

2. System Configuration and Problem Description

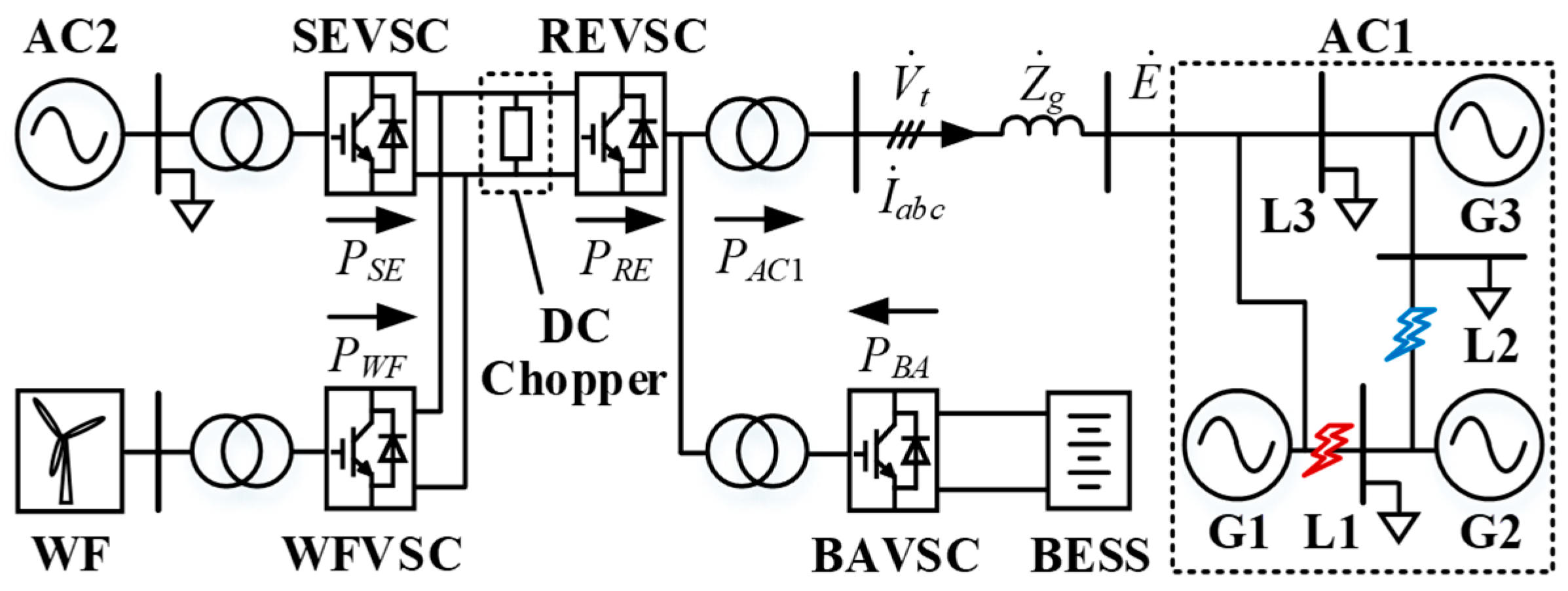

2.1. System Configuration

2.2. Conventional Control Strategy

- (1)

- BAVSC P-f and Q-V control [24], which enables BAVSC to generate/absorb active and reactive power with the ramp rate control when the grid frequency and voltage deviate from the nominal values.

- (2)

- REVSC reactive current control [12], which injects the reactive current as a priority for voltage support as per the grid code during LVRT and adjusts the active current reference according to the change in the reactive current reference.

- (3)

- WFVSC AC voltage reduction control and WF active power reduction control [19], which change the AC voltage to 0.2 p.u. after detecting that the DC voltage exceeds the limit, intentionally leading to the LVRT process of the WF and reducing the WF power output.

- (4)

- SEVSC active power reduction control [26], which controls the sending-end AC system to reduce the power output when the DC voltage exceeds the limit.

- (5)

- DC chopper control [19], which triggers the DC chopper to dissipate the surplus power in the DC link when the DC voltage increases to the limit value.

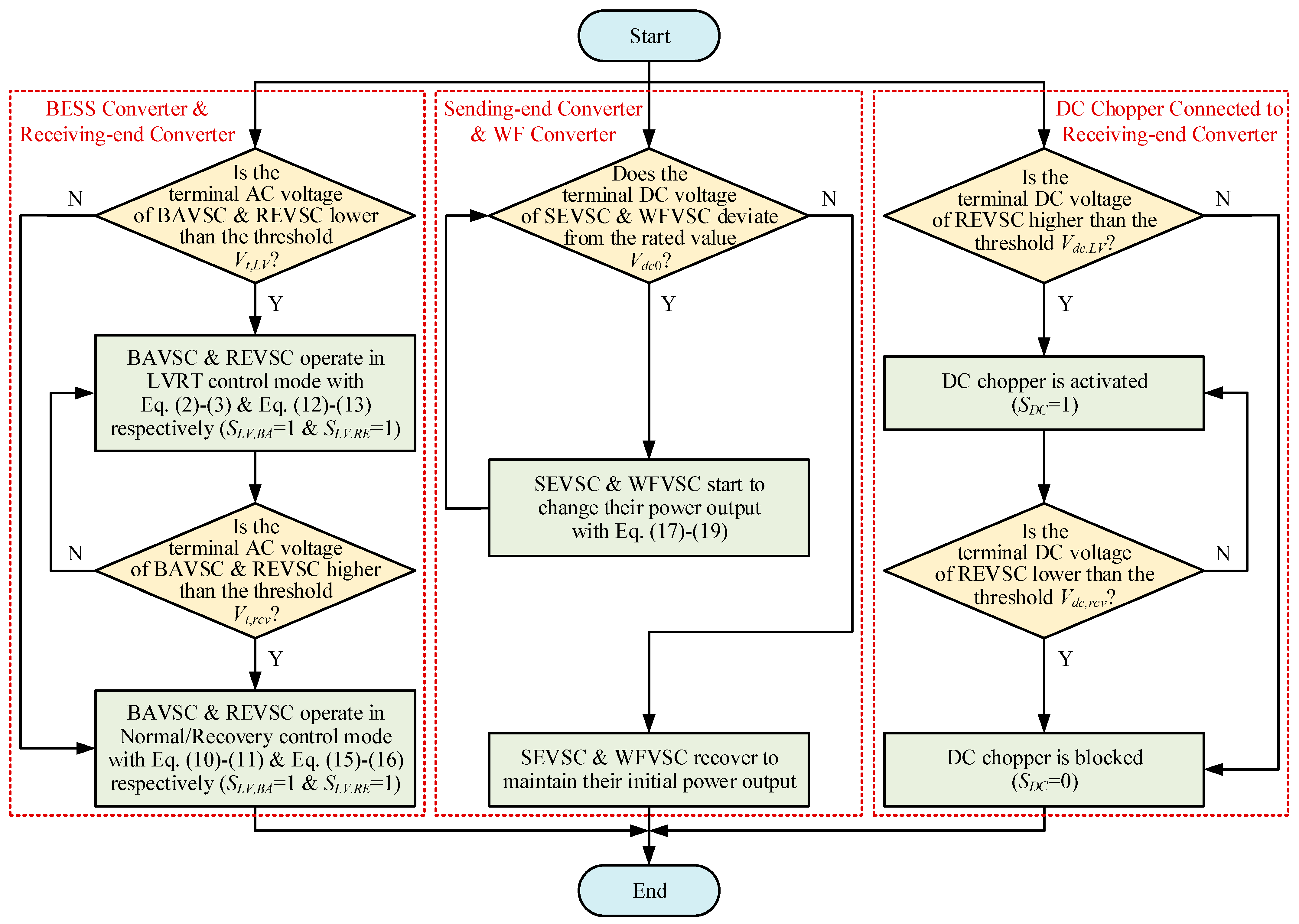

3. The Proposed P-Q Coordination Control Strategy

3.1. Overall Description

3.2. BESS Converter Control

3.3. Receiving-End Converter Control

3.4. Sending-End Systems Control

3.5. DC Chopper Control

3.6. Discussion

4. Key Parameters Affecting Analysis and Design

4.1. Transient Voltage Stability Analysis during LVRT

4.1.1. Relationship between Terminal Voltage and Active Current

4.1.2. Key Factors Influencing Transient Voltage Stability

- (1)

- Grid voltage E

- (2)

- Grid impedance amplitude Zg

- (3)

- Grid impedance angle θg

- (4)

- Proportional coefficient kq

- (5)

- Proportional coefficient kd

4.2. Key Parameter Design

4.2.1. Droop Coefficients

4.2.2. Threshold Values of Hysteresis Comparators

4.2.3. Resistor in DC Chopper

5. Case Study

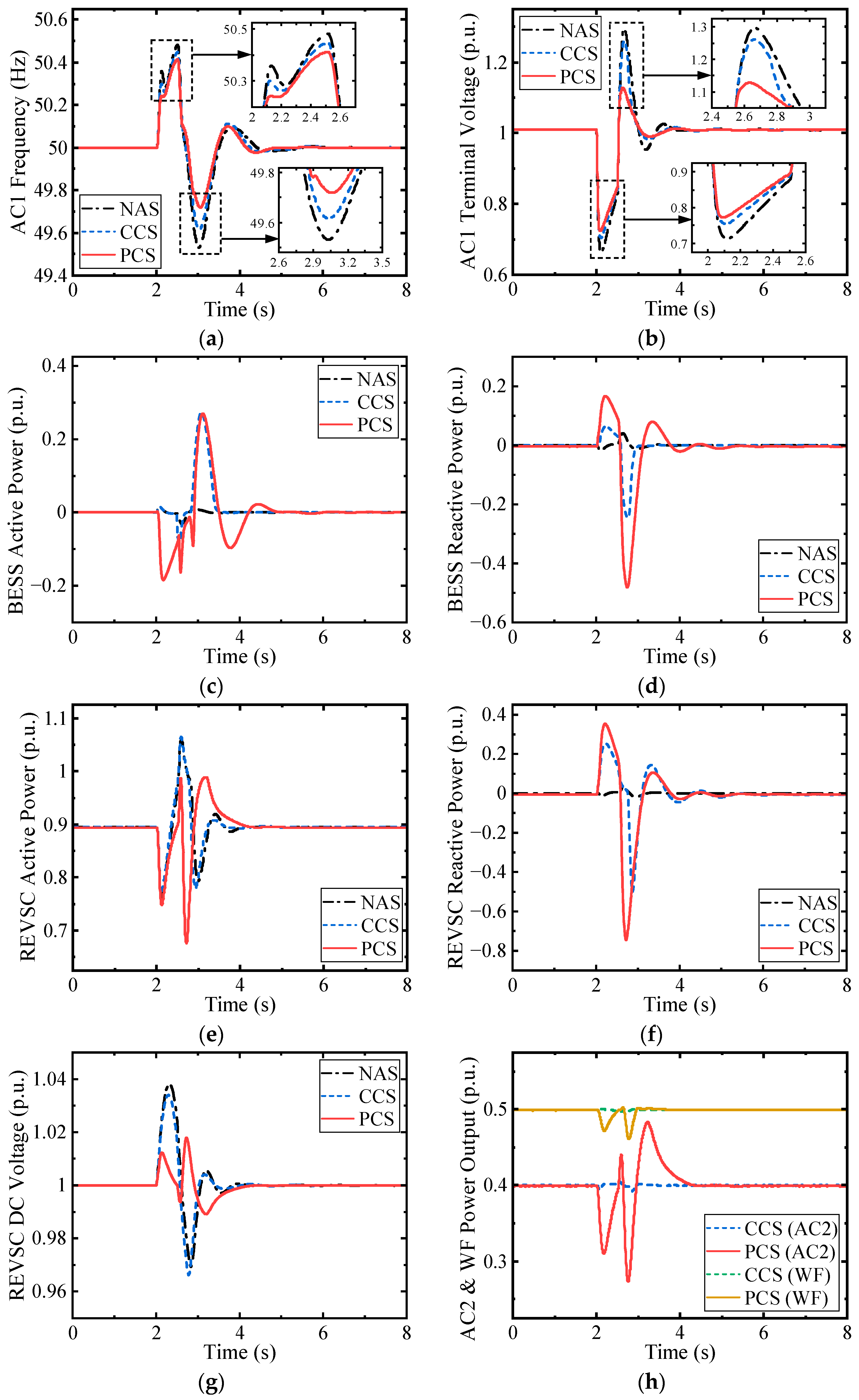

5.1. Case 1: Deep Voltage Drop in AC1

5.2. Case 2: Light Voltage Drop in AC1

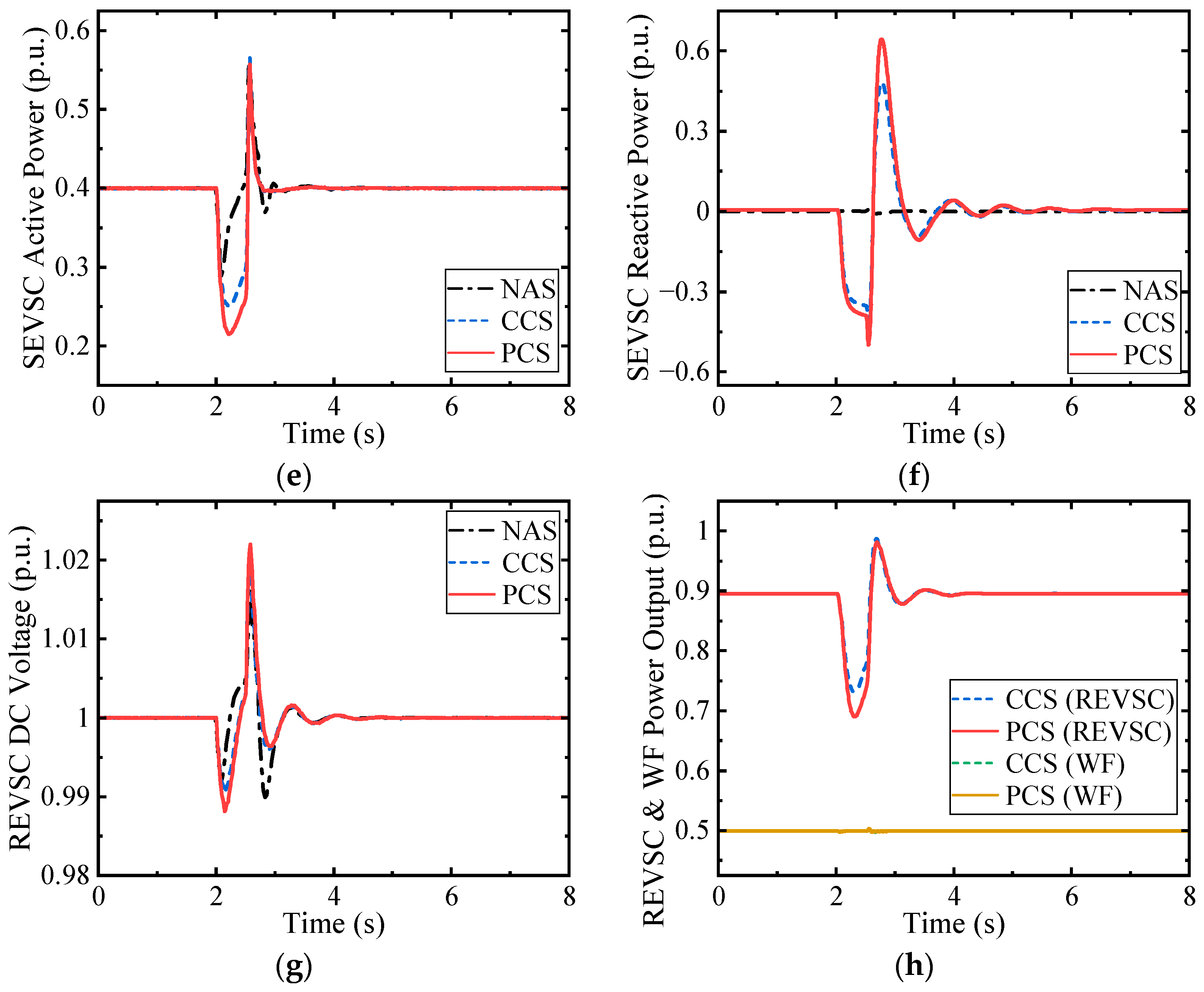

5.3. Case 3: Deep Voltage Drop in AC2

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A

| Symbol | Item | Value | Symbol | Item | Value |

|---|---|---|---|---|---|

| SVSC/p.u. | Rated VSC capacity (except BAVSC) | 1 | f0/Hz | Rated system frequency | 50 |

| SBA/p.u. | Rated BAVSC capacity | 0.5 | fWF0/Hz | Rated WF frequency | 50 |

| VVSC/p.u. | Rated VSC AC RMS voltage | 0.909 | LT, RT/p.u. | Transformer inductance and resistance | 0.1, 0.005 |

| Sdc/p.u. | Rated DC power | 1 | Zg, θg/p.u. | Line impedance and angle | 0.5, 80° |

| Vdc0/p.u. | Rated DC voltage | 1 | RDC/p.u. | Resistor in DC chopper | 3.03 |

| Symbol | Item | Value | Symbol | Item | Value |

|---|---|---|---|---|---|

| SG1/G2/G3/p.u. | Rated power | 2.5, 2.5, 2.5 | TCH1/CH2/CH3/s | Turbine time constant | 0.2, 0.2, 0.2, |

| VG1/G2/G3/p.u. | Rated terminal voltage | 1, 1, 1. | PG1/G2/G3ref/p.u. | Initial power output | 0.85, 0.78, 0.69 |

| HG1/G2/G3/s | Inertia time constant | 6, 6, 6 | PL1/L2/L3/p.u. | Load | 1+j0, 3.8+j0, 4.4-j1.2 |

| KG1/G2/G3 | Droop coefficient | 40, 40, 40 | PBAmax/p.u. | BESS maximum power | 0.5 |

| TG1/G2/G3/s | Governor time constant | 0.08, 0.08, 0.08 |

| Symbol | Item | Value | Symbol | Item | Value |

|---|---|---|---|---|---|

| SG/p.u. | Rated generator power | 4.0 | TG, TCH/s | Governor and turbine time constants | 0.08, 0.2 |

| VG/p.u. | Rated terminal voltage | 1.0 | PG/p.u. | Initial generator power output | 3.6 |

| HG/s | Inertia time constant | 8 | PL/p.u. | Initial load | 3.2 |

| KG | Droop coefficient of generator | 40 | PSE0/p.u. | Initial power reference of SEVSC | 0.4 |

| Symbol | Item | Value | Symbol | Item | Value |

|---|---|---|---|---|---|

| Sn/p.u. | Rated DFIG power | 2.778 × 10−3 | vn/m·s−1 | Rated wind speed | 12 |

| Pn/p.u. | Rated active power | 2.5 × 10−3 | HWT/s | Inertia time constant | 4.32 |

| Nwt | Number of DFIGs | 200 | σm | Maximum power reduction ratio | 0.2 |

| Symbol | Item | Value | Symbol | Item | Value |

|---|---|---|---|---|---|

| KBf, KBV | BAVSC power droop coefficients | 20, 2 | kpi | Converter proportional gain of inner PI loop | 0.3 |

| KV | REVSC voltage droop coefficients | 5 | kii | Converter integral gain of inner PI loop | 10 |

| KP | SEVSC power droop coefficient | 8 | kpo | Converter proportional gain of outer PI loop | 2 |

| Kf | WFVSC frequency droop coefficient | 0.2 | kio | Converter integral gain of outer PI loop | 40 |

| Kσ | WF power droop coefficient | 10 | Vt,LV, Vt,rcv | Hysteresis comparator thresholds in BAVSC and REVSC | 0.9, 0.95 |

| kq | BAVSC and REVSC reactive current droop coefficient | 2 | Vdc,LV, Vdc,rcv | Hysteresis comparator thresholds in DC chopper control | 1.05, 1.03 |

| kd | BAVSC active current droop coefficient | 3 | Δfdb, ΔVt,db | Frequency and voltage dead-band ranges of the BAVSC | 0.001, 0.01 |

References

- Koondhar, M.A.; Kaloi, G.S.; Saand, A.S.; Chandio, S.; Ko, W.; Park, S.; Choi, H.-J.; El-Sehiemy, R.A. Critical technical issues with a voltage-source-converter-based high voltage direct current transmission system for the onshore integration of offshore wind farms. Sustainability 2023, 15, 13526. [Google Scholar] [CrossRef]

- Yang, L.; Li, Y.; Li, Z.; Wang, P.; Xu, S.; Gou, R. A simplified analytical calculation model of average power loss for modular multilevel converter. IEEE Trans. Ind. Electron. 2019, 66, 2313–2322. [Google Scholar] [CrossRef]

- Apostolaki-Iosifidou, E.; McCormack, R.; Kempton, W.; McCoy, P.; Ozkan, D. Transmission design and analysis for large-scale offshore wind energy development. IEEE Power Energy Technol. Syst. J. 2019, 6, 22–31. [Google Scholar] [CrossRef]

- Liu, L.; Li, X.; Jiang, Q.; Teng, Y.; Chen, M.; Wang, Y.; Zeng, X.; Luo, Y.; Pan, P. A multi-terminal control method for AC grids based on a hybrid high-voltage direct current with cascaded MMC converters. Electronics 2023, 12, 4799. [Google Scholar] [CrossRef]

- Jiang, Q.; Li, B.; Liu, T. Tech-economic assessment of power transmission options for large-scale offshore wind farms in China. Processes 2022, 10, 979. [Google Scholar] [CrossRef]

- Wu, J.; Wang, Z.-X.; Xu, L.; Wang, G.-Q. Key technologies of VSC-HVDC and its application on offshore wind farm in China. Renew. Sustain. Energy Rev. 2014, 36, 247–255. [Google Scholar] [CrossRef]

- Ramtharan, G.; Arulampalam, A.; Ekanayake, J.B.; Hughes, F.M.; Jenkins, N. Fault ride through of fully rated converter wind turbines with AC and DC transmission systems. IET Renew. Power Gener. 2010, 3, 426–438. [Google Scholar] [CrossRef]

- Li, Z.; Liu, F. Frequency and voltage regulation control strategy of wind turbine based on supercapacitors under power grid fault. Energy Rep. 2023, 10, 2612–2622. [Google Scholar] [CrossRef]

- Liu, Y.; Wang, Y.; Liu, H.; Xiong, L.; Li, M.; Peng, Y.; Xu, Z.; Wang, M. An LVRT strategy with quantitative design of virtual impedance for VSG. Int. J. Electr. Power Energy Syst. 2022, 140, 107661–107670. [Google Scholar] [CrossRef]

- Döşoğlu, M.K. Enhancement of LVRT capability in DFIG-based wind turbines with STATCOM and supercapacitor. Sustainability 2023, 15, 2529. [Google Scholar] [CrossRef]

- Kim, M.-N.; Yi, J.-S.; Won, C.-Y.; Lee, J.-H. Methods to improve dynamic system response of power compensators using supercapacitors in low-voltage ride-through (LVRT) conditions. Electronics 2022, 11, 1144. [Google Scholar] [CrossRef]

- Liu, Y.; Chen, Z. A flexible power control method of VSC-HVDC link for the enhancement of effective short-circuit ratio in a hybrid multi-infeed HVDC system. IEEE Trans. Power Syst. 2013, 28, 1568–1581. [Google Scholar] [CrossRef]

- Rashid, G.; Ali, M.H. Fault ride through capability improvement of DFIG based wind farm by fuzzy logic controlled parallel resonance fault current limiter. Electr. Power Syst. Res. 2017, 146, 1–8. [Google Scholar] [CrossRef]

- Wu, Z.; Zhu, C.; Hu, M. Improved control strategy for DFIG wind turbines for low voltage ride through. Energies 2013, 6, 1181–1197. [Google Scholar] [CrossRef]

- Xu, B.; Gao, C.; Zhang, J.; Yang, J.; Xia, B.; He, Z. A novel DC chopper topology for VSC-based offshore wind farm connection. IEEE Trans. Power Electron. 2021, 36, 3017–3027. [Google Scholar] [CrossRef]

- Cao, S.; Xiang, W.; Lu, X.; Lin, W.; Zhang, K.; Wen, J.; Zhang, X. Energy dissipation of MMC-HVDC based onshore wind power integration system with FB-DBS and DCCB. IET Renew. Power Gener. 2019, 14, 222–230. [Google Scholar] [CrossRef]

- Erlich, I.; Feltes, C.; Shewarega, F. Enhanced voltage drop control by VSC–HVDC systems for improving wind farm fault ridethrough capability. IEEE Trans. Power Deliv. 2014, 29, 378–385. [Google Scholar] [CrossRef]

- Jing, Y.; Li, R.; Xu, L.; Wang, Y. Enhanced AC voltage and frequency control on offshore MMC station for wind farm. J. Eng. 2017, 2017, 1264–1268. [Google Scholar] [CrossRef]

- Wang, X.; Yang, R.; Shi, Z.; Cai, X.; Shi, X.; Chen, Y. Coordinated low voltage ride-through of MMC-HVDC transmission system and wind farm with distributed braking resistors. IEEE Access 2022, 10, 87860–87869. [Google Scholar] [CrossRef]

- Goksu, O.; Teodorescu, R.; Bak, C.L.; Iov, F.; Kjaer, P.C. Instability of wind turbine converters during current injection to low voltage grid faults and PLL frequency based stability solution. IEEE Trans. Power Syst. 2014, 29, 1683–1691. [Google Scholar] [CrossRef]

- Zhang, X.; Wu, Z.; Hu, M.; Li, X.; Lv, G. Coordinated control strategies of VSC-HVDC-based wind power systems for low voltage ride through. Energies 2015, 8, 7224–7242. [Google Scholar] [CrossRef]

- Zhou, H.; Yao, W.; Zhou, M.; Ai, X.; Wen, J.; Cheng, S. Active energy control for enhancing AC fault ride-through capability of MMC-HVDC connected with offshore wind farms. IEEE Trans. Power Syst. 2023, 38, 2705–2718. [Google Scholar] [CrossRef]

- Li, W.; Zhu, M.; Chao, P.; Liang, X.; Xu, D. Enhanced FRT and postfault recovery control for MMC-HVDC connected offshore wind farms. IEEE Trans. Power Syst. 2020, 35, 1606–1617. [Google Scholar] [CrossRef]

- Serban, E.; Ordonez, M.; Pondiche, C. Voltage and frequency grid support strategies beyond standards. IEEE Trans. Power Electron. 2017, 32, 298–309. [Google Scholar] [CrossRef]

- Charalambous, A.; Hadjidemetriou, L.; Kyriakides, E.; Polycarpou, M.M. A coordinated voltage–frequency support scheme for storage systems connected to distribution grids. IEEE Trans. Power Electron. 2021, 36, 8464–8475. [Google Scholar] [CrossRef]

- Wu, J.; Wang, Z.; Liu, R.; Shan, Y.; Wang, C. Decentralized primary frequency regulation for hybrid multi-terminal direct current power systems considering multi-source enhancement. J. Mod. Power Syst. Clean Energy, 2023; accepted. [Google Scholar]

- Lou, G.; Yang, Q.; Gu, W.; Zhang, J. An improved control strategy of virtual synchronous generator under symmetrical grid voltage sag. Int. J. Electr. Power Energy Syst. 2020, 121, 106093. [Google Scholar] [CrossRef]

- De Brabandere, K.; Bolsens, B.; Van den Keybus, J.; Woyte, A.; Driesen, J.; Belmans, R. A voltage and frequency droop control method for parallel inverters. IEEE Trans. Power Electron. 2007, 22, 1107–1115. [Google Scholar] [CrossRef]

- Li, Y.; Zhang, Z.; Yang, Y.; Li, Y.; Chen, H.; Xu, Z. Coordinated control of wind farm and VSC–HVDC system using capacitor energy and kinetic energy to improve inertia level of power systems. Int. J. Electr. Power Energy Syst. 2014, 59, 79–92. [Google Scholar] [CrossRef]

- Li, L.; Zhu, D.; Zou, X.; Hu, J.; Kang, Y.; Guerrero, J.M. Review of frequency regulation requirements for wind power plants in international grid codes. Renew. Sustain. Energy Rev. 2023, 187, 113731–113747. [Google Scholar] [CrossRef]

| Equipment | CCS | PCS | ||

|---|---|---|---|---|

| Control Rules | Activation | Control Rules | Activation | |

| BAVSC | Iq,BA injection as a priority | Vt,BA < Vt,LV | Iq,BA injection as a priority and Id,BA absorption | Vt,BA < Vt,LV |

| Id,BA injection as a priority | Vt,BA > Vt,rcv | adaptive current limitation control | Vt,BA > Vt,rcv | |

| REVSC | Iq,RE injection as a priority | Vt,RE < Vt,LV | Iq,RE injection as a priority | Vt,RE < Vt,LV |

| Id,RE injection as a priority | Vt,RE > Vt,rcv | Id,RE injection as a priority | Vt,RE > Vt,rcv | |

| SEVSC | Vdc-PSE droop control | Vdc,SE > Vdc,LV | Vdc-PSE droop control | Vdc,SE ≠ 0 |

| WFVSC | decrease WF voltage to 0.2 p.u. | Vdc,WF > Vdc,LV | Vdc-fWF droop control | Vdc,WF > 0 |

| WF | LVRT and reduce power output | Vt,WF < Vt,LV | fWF-PWF droop control | fWF > fWF0 |

| DC Chopper | activated | Vdc,RE > Vdc,LV | activated | Vdc,RE > Vdc,LV |

| block | Vdc,RE < Vdc,rcv | block | Vdc,RE < Vdc,rcv | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Z.; Wu, J.; Liu, R.; Shan, Y. A P-Q Coordination Control Strategy of VSC-HVDC and BESS for LVRT Recovery Performance Enhancement. Electronics 2024, 13, 741. https://doi.org/10.3390/electronics13040741

Wang Z, Wu J, Liu R, Shan Y. A P-Q Coordination Control Strategy of VSC-HVDC and BESS for LVRT Recovery Performance Enhancement. Electronics. 2024; 13(4):741. https://doi.org/10.3390/electronics13040741

Chicago/Turabian StyleWang, Zhen, Jialiang Wu, Ruixu Liu, and Yu Shan. 2024. "A P-Q Coordination Control Strategy of VSC-HVDC and BESS for LVRT Recovery Performance Enhancement" Electronics 13, no. 4: 741. https://doi.org/10.3390/electronics13040741

APA StyleWang, Z., Wu, J., Liu, R., & Shan, Y. (2024). A P-Q Coordination Control Strategy of VSC-HVDC and BESS for LVRT Recovery Performance Enhancement. Electronics, 13(4), 741. https://doi.org/10.3390/electronics13040741