Mitigating WL-to-WL Disturbance in Dynamic Random-Access Memory (DRAM) through Adopted Spherical Shallow Trench Isolation with Silicon Nitride Layer in the Buried Channel Array Transistor (BCAT)

Abstract

1. Introduction

2. Simulation Methodology

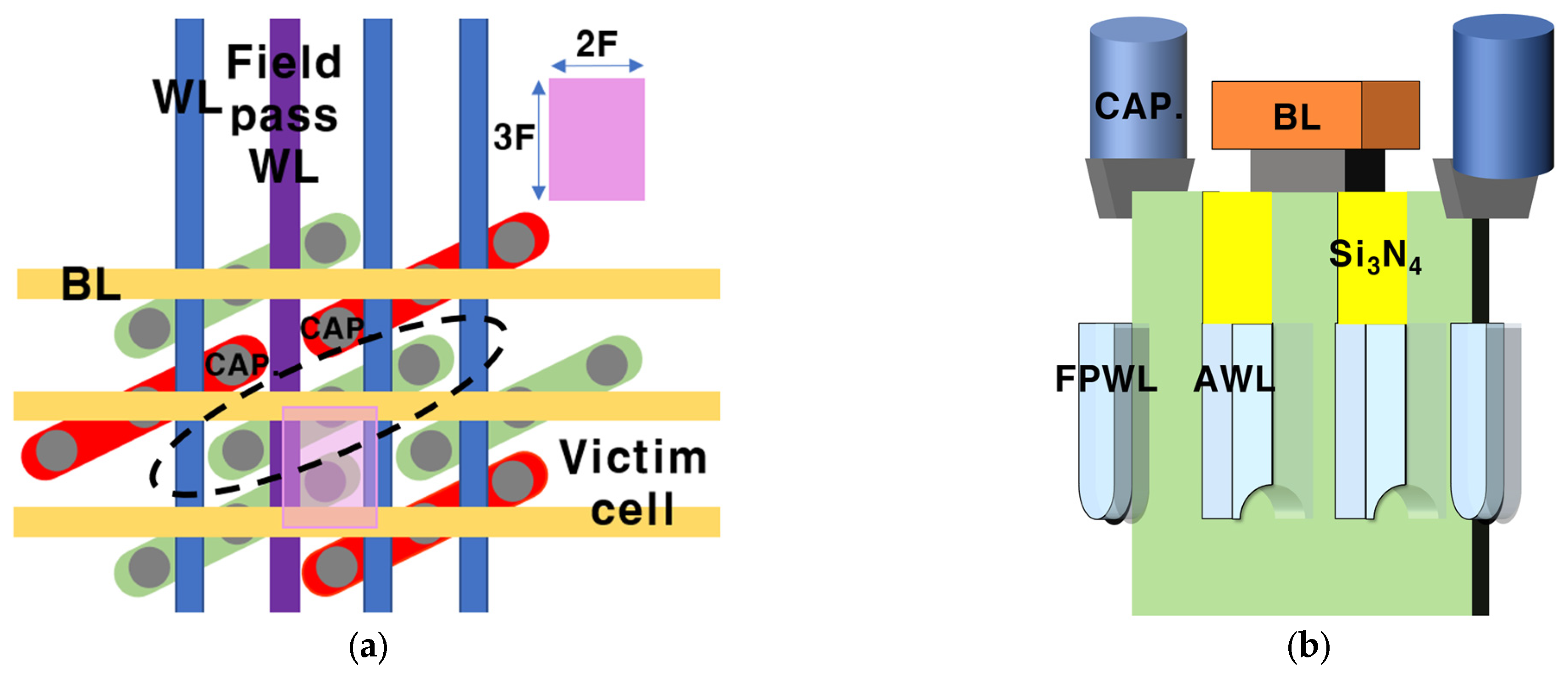

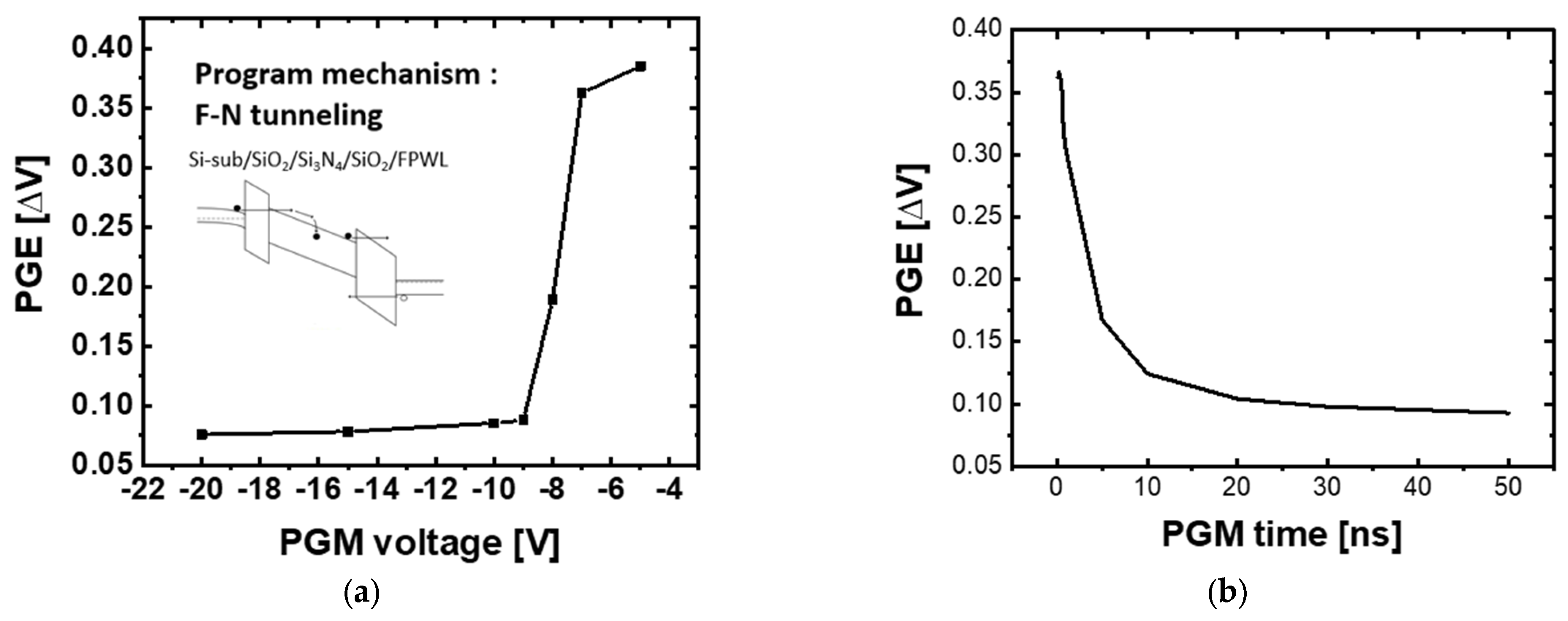

3. PGE Phenomenon and Investigation

4. Proposal Structure and Simulation Results

4.1. The Background to Suggesting a Structure

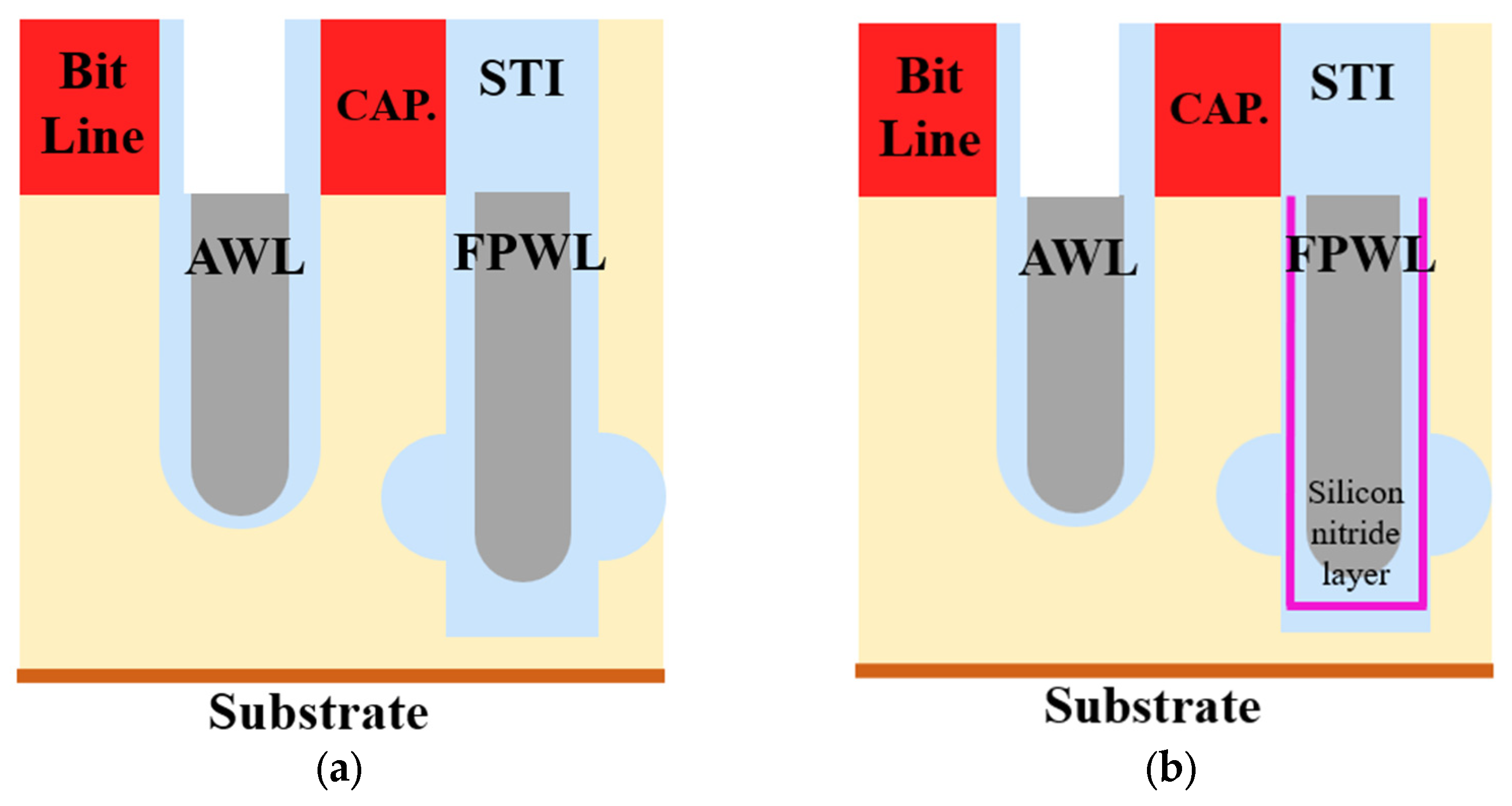

4.2. Proposed Structure

4.3. Simulation Experiment Results

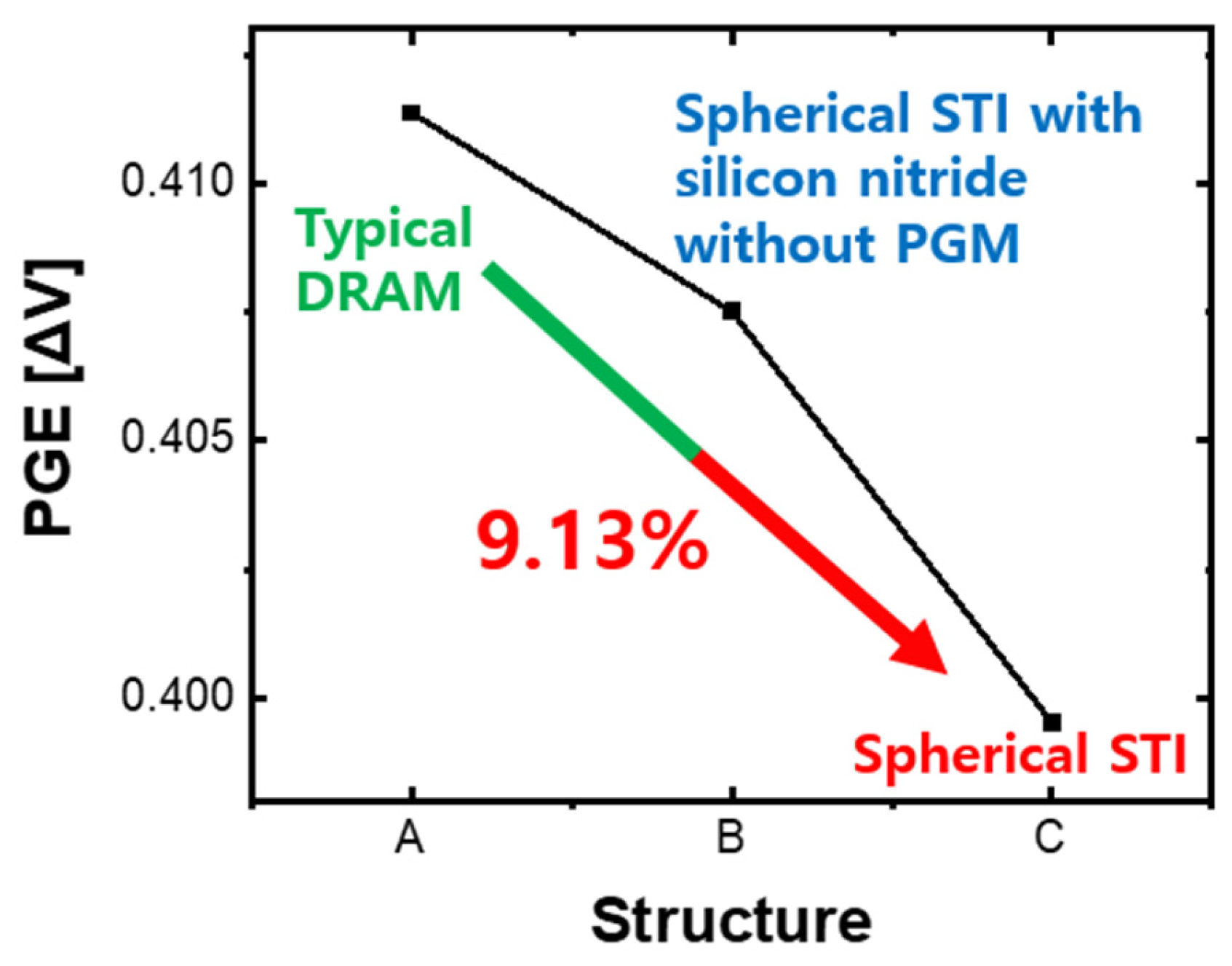

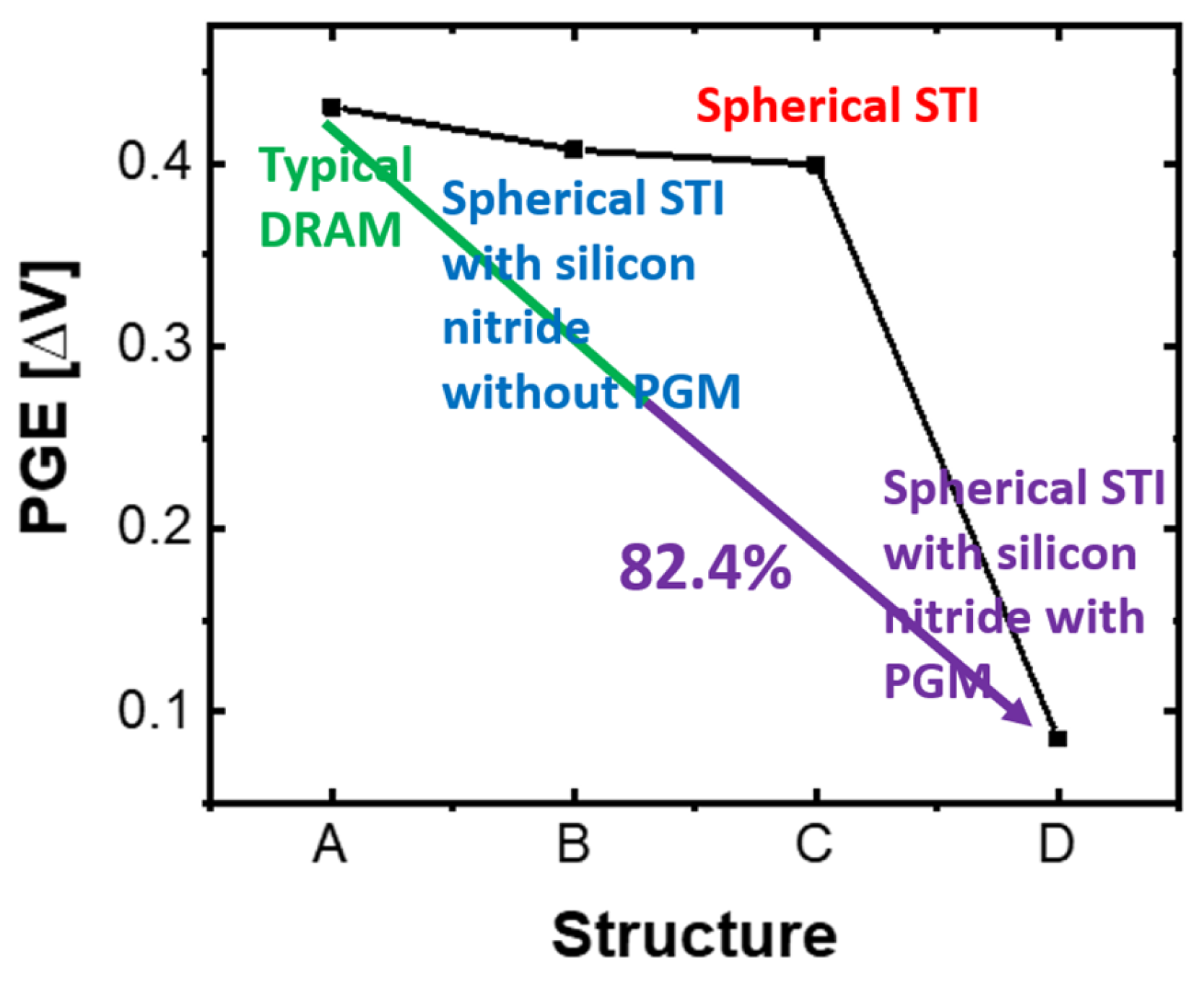

4.3.1. Structural PGE Comparison

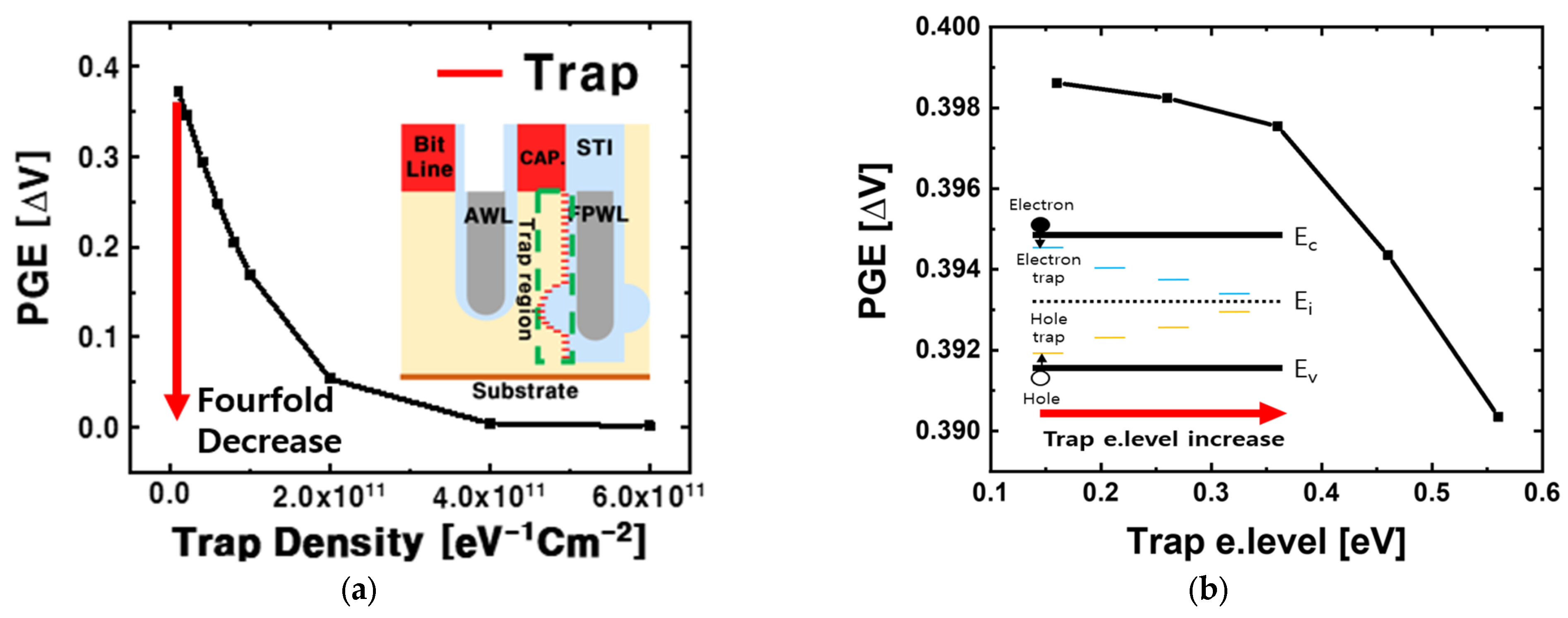

4.3.2. Optimization for Spherical STI

4.3.3. Optimization for Spherical STI with an Added Si3N4 Layer

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sun, Y.; Liu, X.; Wang, N.; Jeon, J.; Wu, B.; Cao, K. Trap-Assisted Passing Word Line Leakage and Variable Retention Time in DRAM. In Proceedings of the 2021 IEEE 4th International Conference on Electronics Technology (ICET), Chengdu, China, 7–10 May 2021. [Google Scholar]

- Gautam, S.K.; Manhas, S.K.; Kumar, A.; Pakala, M. Mitigating the passing word line induced soft errors in saddle fin DRAM. IEEE Trans. Electron Devices 2020, 67, 1902–1905. [Google Scholar] [CrossRef]

- Han, J.W.; Suh, M.; Lee, G.; Kim, J. Overhang Saddle Fin Sidewall Structure for Highly Reliable DRAM Operation. IEEE Access 2023, 11, 82738–82743. [Google Scholar] [CrossRef]

- Yang, T.; Lin, X.W. Trap-assisted DRAM row hammer effect. IEEE Electron. Device Lett. 2019, 40, 391–394. [Google Scholar] [CrossRef]

- Woo, J.; Chung, K.S. Mitigating Row-hammering by Adapting the Probability of Additional Row Refresh. In Proceedings of the 2019 IEEE 4th International Conference on Technology, Informatics, Management, Engineering & Environment (TIME-E), Bali, Indonesia, 13–15 November 2019. [Google Scholar]

- Kim, D.H.; Nair, P.J.; Qureshi, M.K. Architectural support for mitigating row hammering in DRAM memories. IEEE Computer Archit. Lett. 2014, 14, 9–12. [Google Scholar] [CrossRef]

- Son, M.; Park, H. Making DRAM strong against row hammering. In Proceedings of the 2017 54th ACM/EDAC/IEEE Design Automation Conference (DAC), New York, NY, USA, 18–22 June 2017. [Google Scholar] [CrossRef]

- Lim, K.Y.; Yu, X.; Yeo, D. A study on gate-induced junction breakdown. In Proceedings of the 2001 6th International Conference on Solid-State and Integrated Circuit Technology. Proceedings, Shanghai, China, 22–25 October 2001. [Google Scholar] [CrossRef]

- Lo, G.Q.; Joshi, A.B. Hot-carrier-stress effects on gate-induced drain leakage current in n-channel MOSFETs. IEEE Electron. Device Lett. 1991, 12, 5–7. [Google Scholar] [CrossRef]

- Chang, C.; Haddad, S.; Swaminathan, B.; Lien, J. Drain-avalanche and hole-trapping induced gate leakage in thin-oxide MOS device. IEEE Electron. Device Lett. 1988, 9, 588–590. [Google Scholar] [CrossRef]

- Yuan, X.; Park, J.E.; Wang, J.; Zhao, E.; Ahlgren, D.C.; Hook, T.; Yuan, J.; Chan, V.W.C.; Liang, C.-H. Gate-Induced-Drain-Leakage Current in 45-nm CMOS Technology. IEEE Trans. Device Mater. Reliab. 2008, 8, 501–508. [Google Scholar] [CrossRef]

- Lin, Y.; Wolf, J.K. Combined ECC/RLL code. IEEE Trans. Magn. 1998, 24, 2527–2529. [Google Scholar] [CrossRef]

- Kwon, S.; Son, Y.H.; Ahn, J.H. Understanding DDR4 in pursuit of In-DRAM ECC. In Proceedings of the 2014 International SoC Design Conference (ISOCC), Jeju, Republic of Korea, 3–6 November 2014. [Google Scholar] [CrossRef]

- Yamada, T.; Kotani, H.; Matsushima, J.; Inoue, M. A 4-Mbit DRAM with 16-bit concurrent ECC. IEEE J. Solid-State Circuits 1988, 23, 20–26. [Google Scholar] [CrossRef]

- Kim, Y.S.; Lim, C.Y.; Kwon, M.W. Reduction of the Pass Gate Effect with a Spherical Shallow Trench Isolation in the BCAT Structure. J. Semicond. Technol. Sci. 2023, 23, 236–242. [Google Scholar] [CrossRef]

| Structure Condition | [nm] | Simulation Condition | Voltage [V] |

|---|---|---|---|

| Gate oxide thickness side/bottom (Tox,side/Tox,bot) | 8/6 | BL voltage | 1 |

| Silicon active width (Wsi) | 23 | Silicon active WL voltage (Von/Voff) | 3/−0.2 |

| Shallow trench isolation width (WSTI) | 28 | Field Pass WL voltage (Von/Voff) | 3/−0.2 |

| Word line width (WAWL, WFPWL) | 12 | Substrate voltage | −0.6 |

| Fin depth (DFin) | 20 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, Y.-S.; Lim, C.-Y.; Kwon, M.-W. Mitigating WL-to-WL Disturbance in Dynamic Random-Access Memory (DRAM) through Adopted Spherical Shallow Trench Isolation with Silicon Nitride Layer in the Buried Channel Array Transistor (BCAT). Electronics 2024, 13, 681. https://doi.org/10.3390/electronics13040681

Kim Y-S, Lim C-Y, Kwon M-W. Mitigating WL-to-WL Disturbance in Dynamic Random-Access Memory (DRAM) through Adopted Spherical Shallow Trench Isolation with Silicon Nitride Layer in the Buried Channel Array Transistor (BCAT). Electronics. 2024; 13(4):681. https://doi.org/10.3390/electronics13040681

Chicago/Turabian StyleKim, Yeon-Seok, Chang-Young Lim, and Min-Woo Kwon. 2024. "Mitigating WL-to-WL Disturbance in Dynamic Random-Access Memory (DRAM) through Adopted Spherical Shallow Trench Isolation with Silicon Nitride Layer in the Buried Channel Array Transistor (BCAT)" Electronics 13, no. 4: 681. https://doi.org/10.3390/electronics13040681

APA StyleKim, Y.-S., Lim, C.-Y., & Kwon, M.-W. (2024). Mitigating WL-to-WL Disturbance in Dynamic Random-Access Memory (DRAM) through Adopted Spherical Shallow Trench Isolation with Silicon Nitride Layer in the Buried Channel Array Transistor (BCAT). Electronics, 13(4), 681. https://doi.org/10.3390/electronics13040681