CMOS Analogue Velocity-Selective Neural Processing System

Abstract

1. Introduction

2. VSR Topologies

2.1. Basic Principles

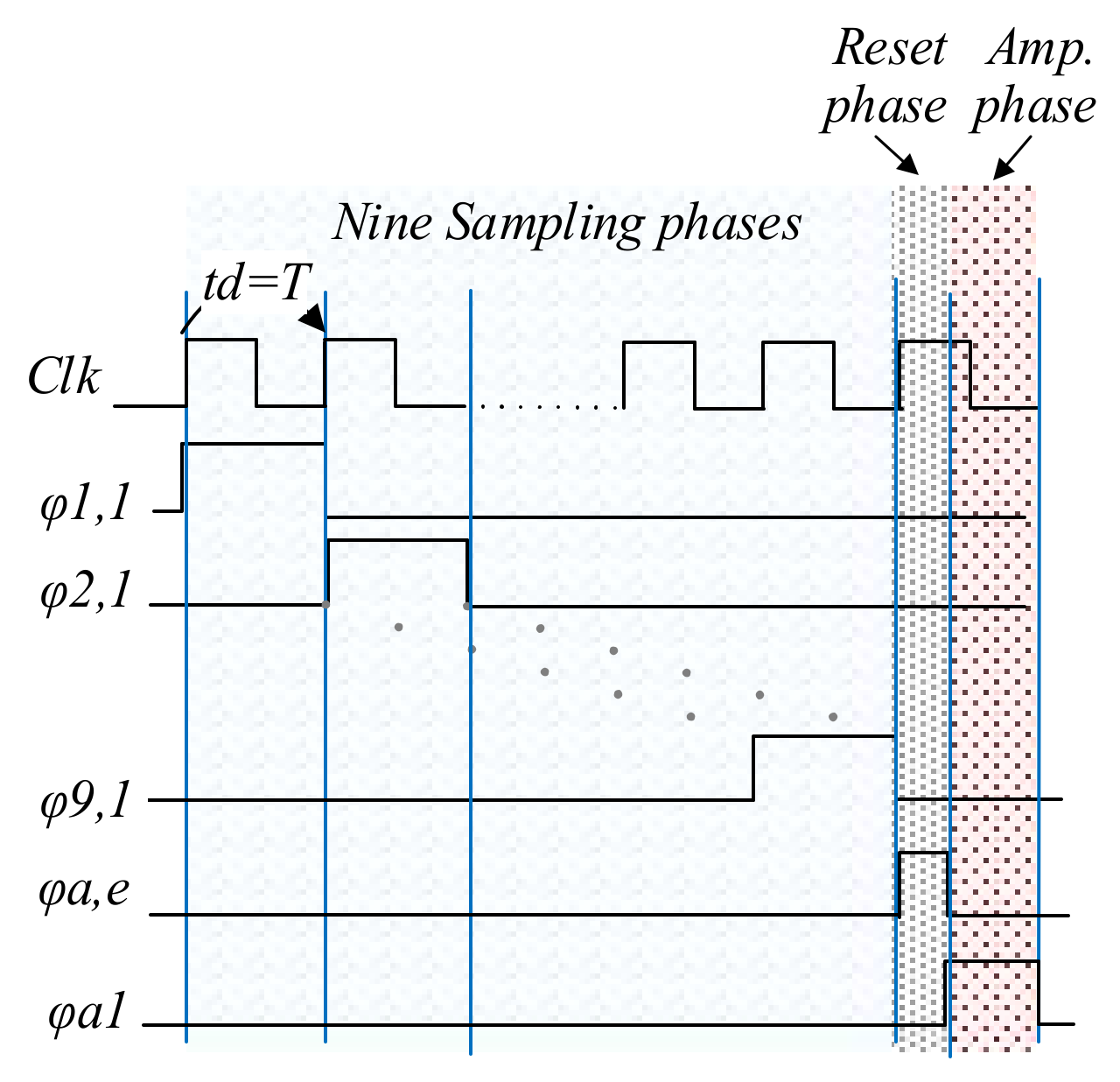

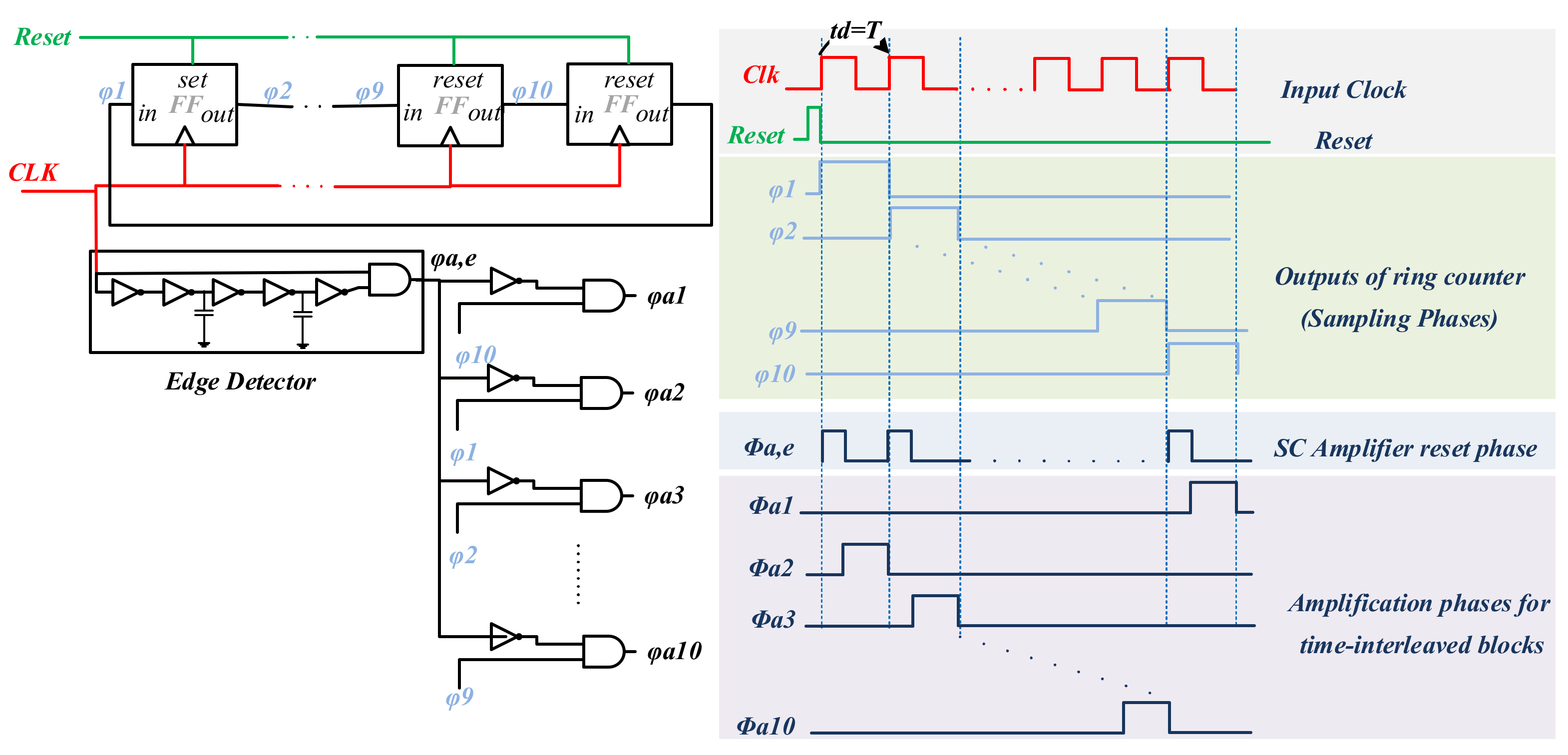

2.2. System Architecture and Specification

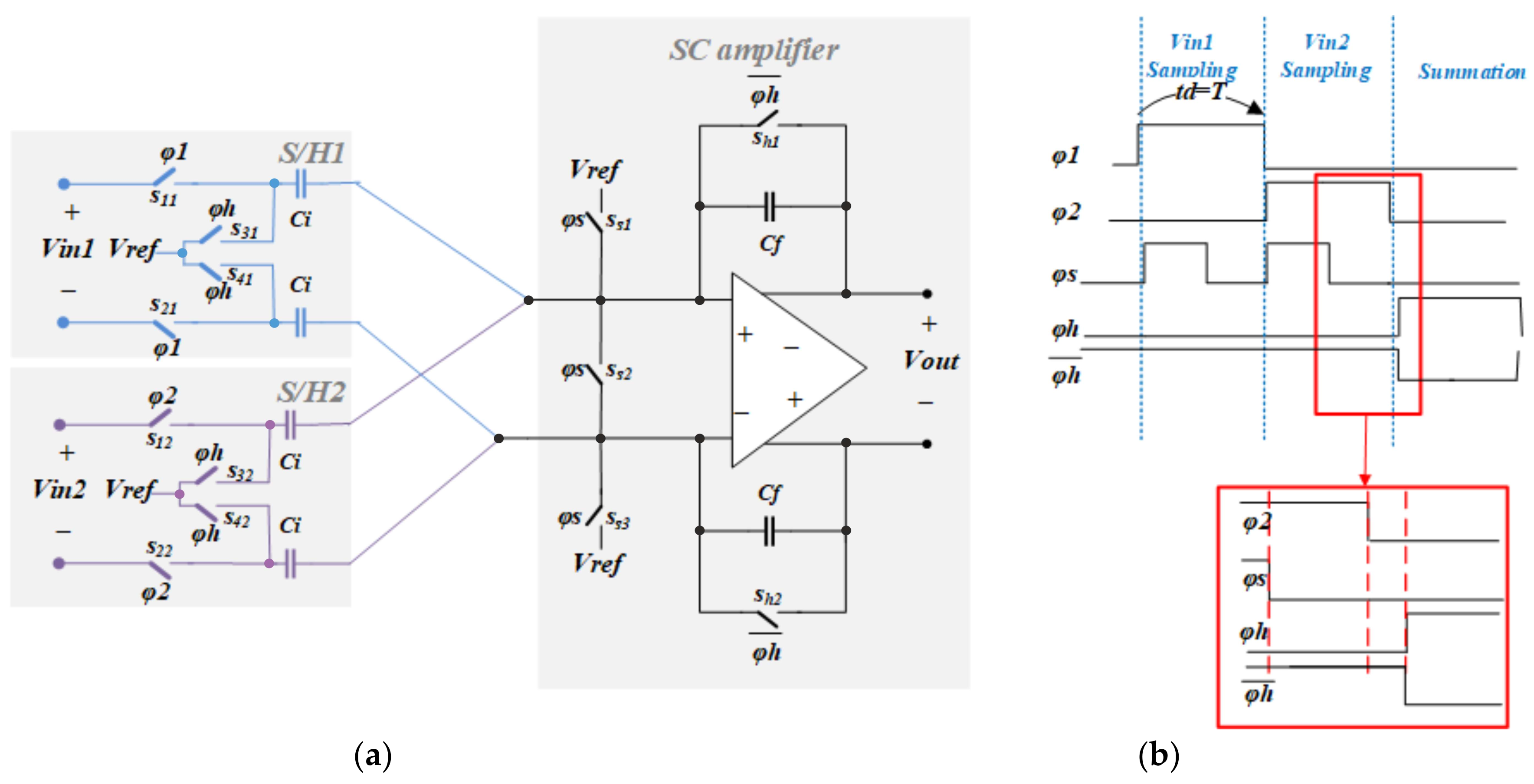

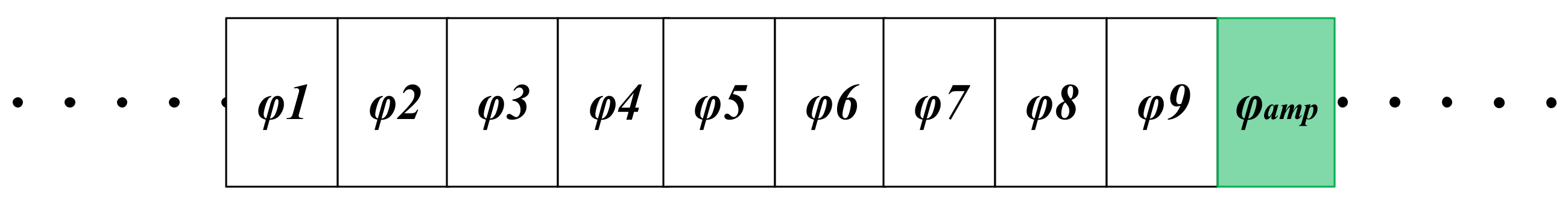

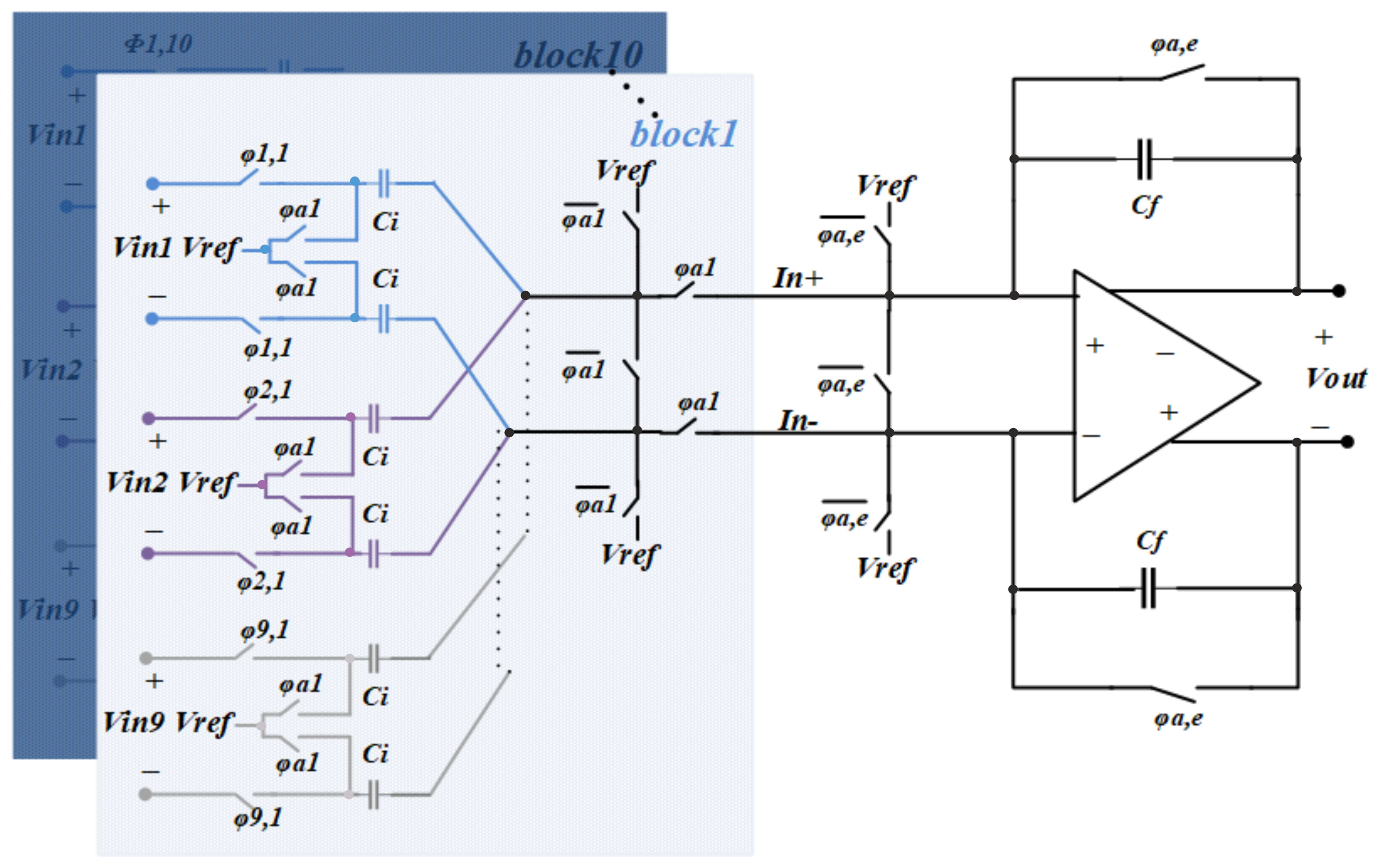

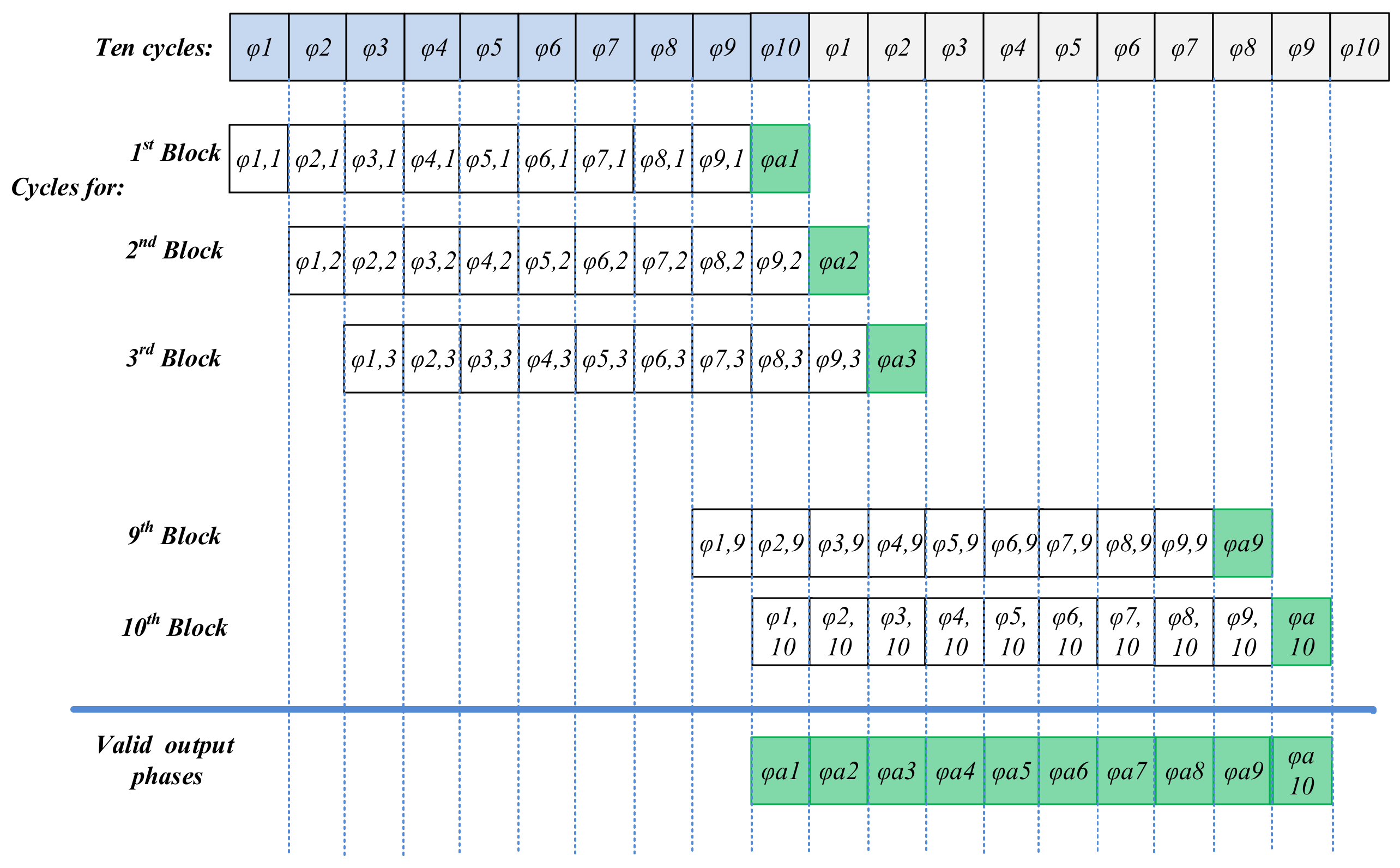

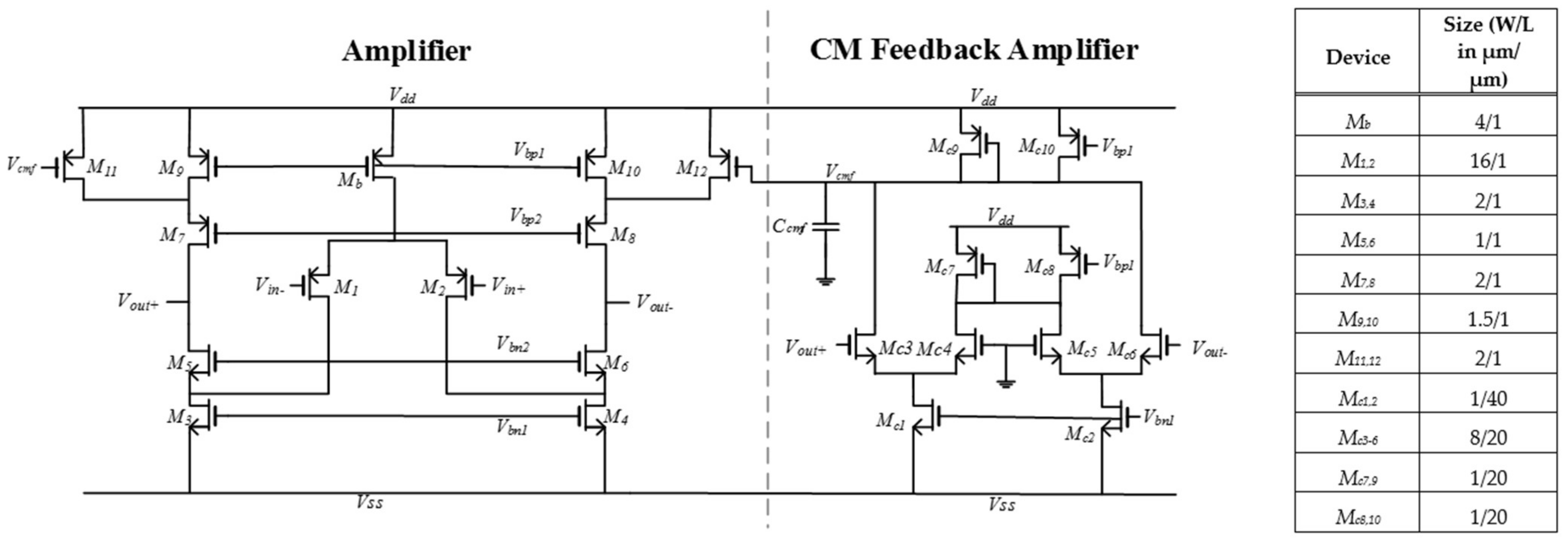

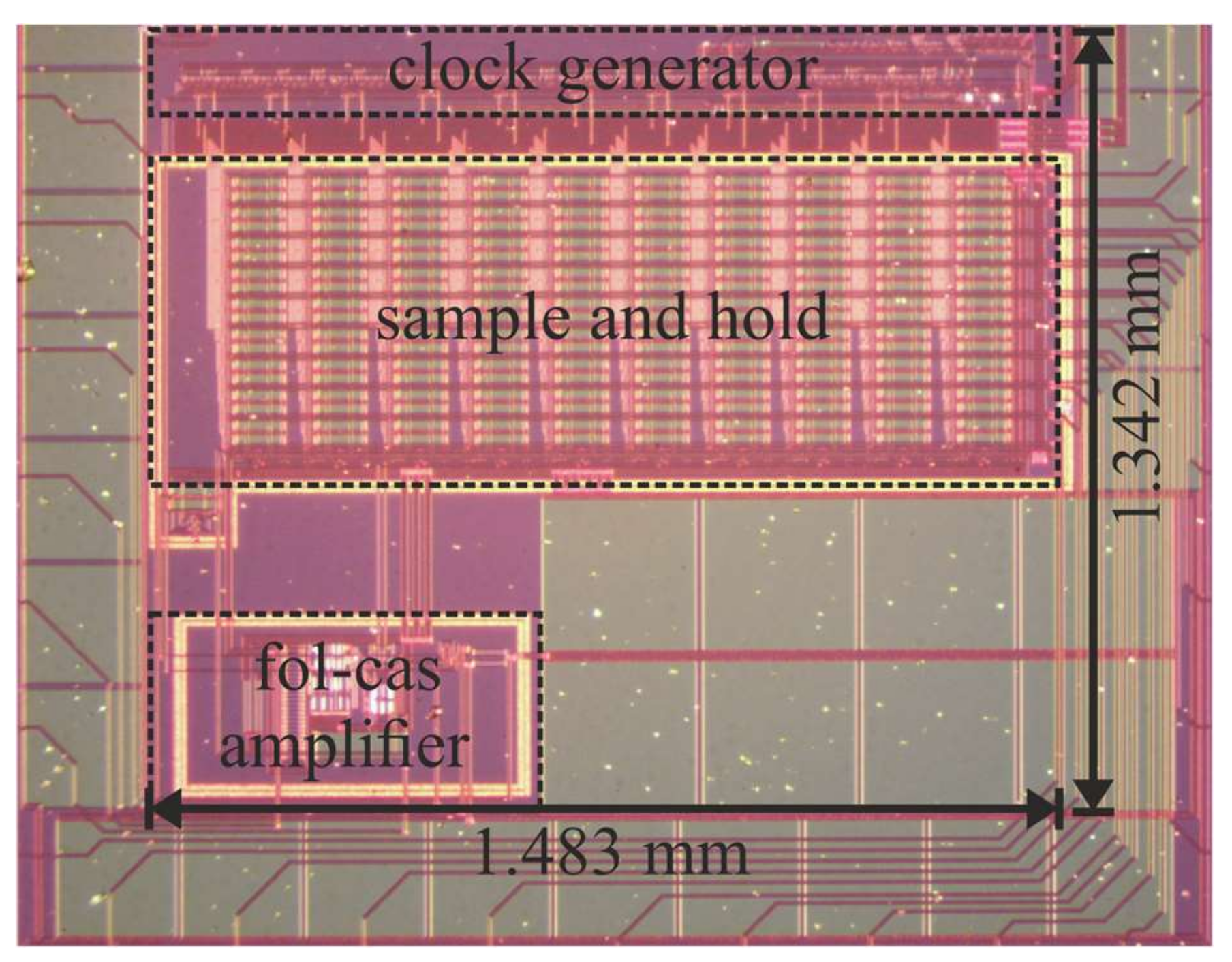

3. Circuit Design

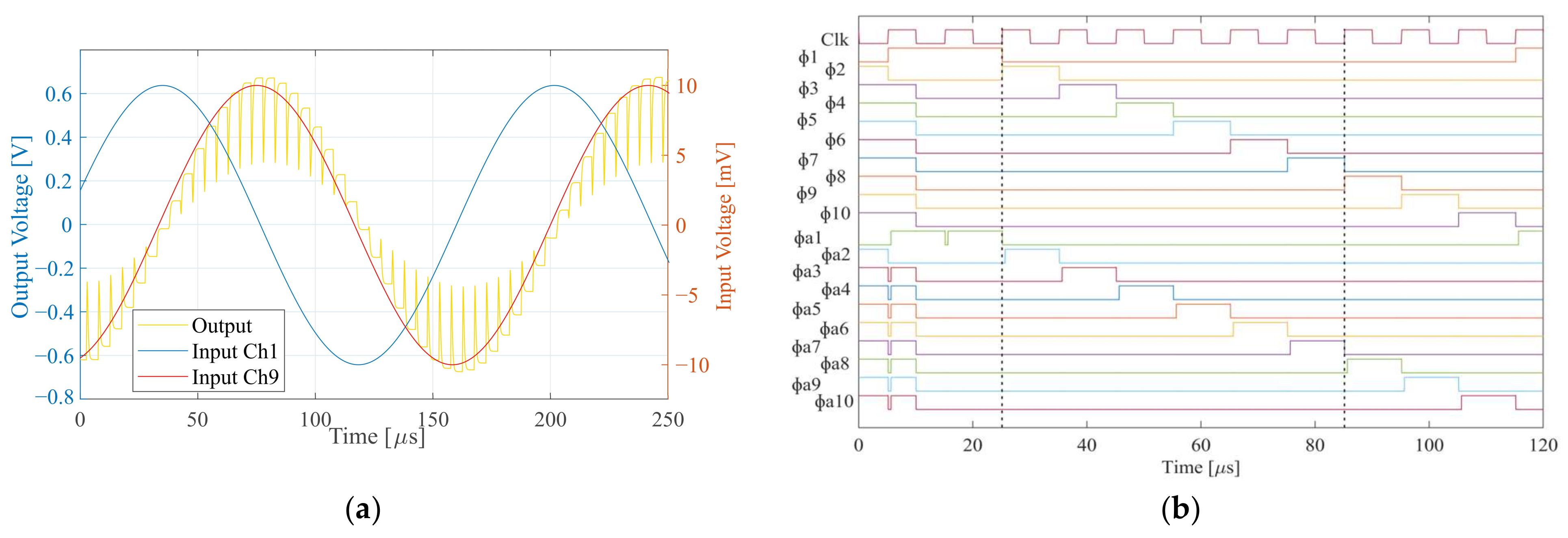

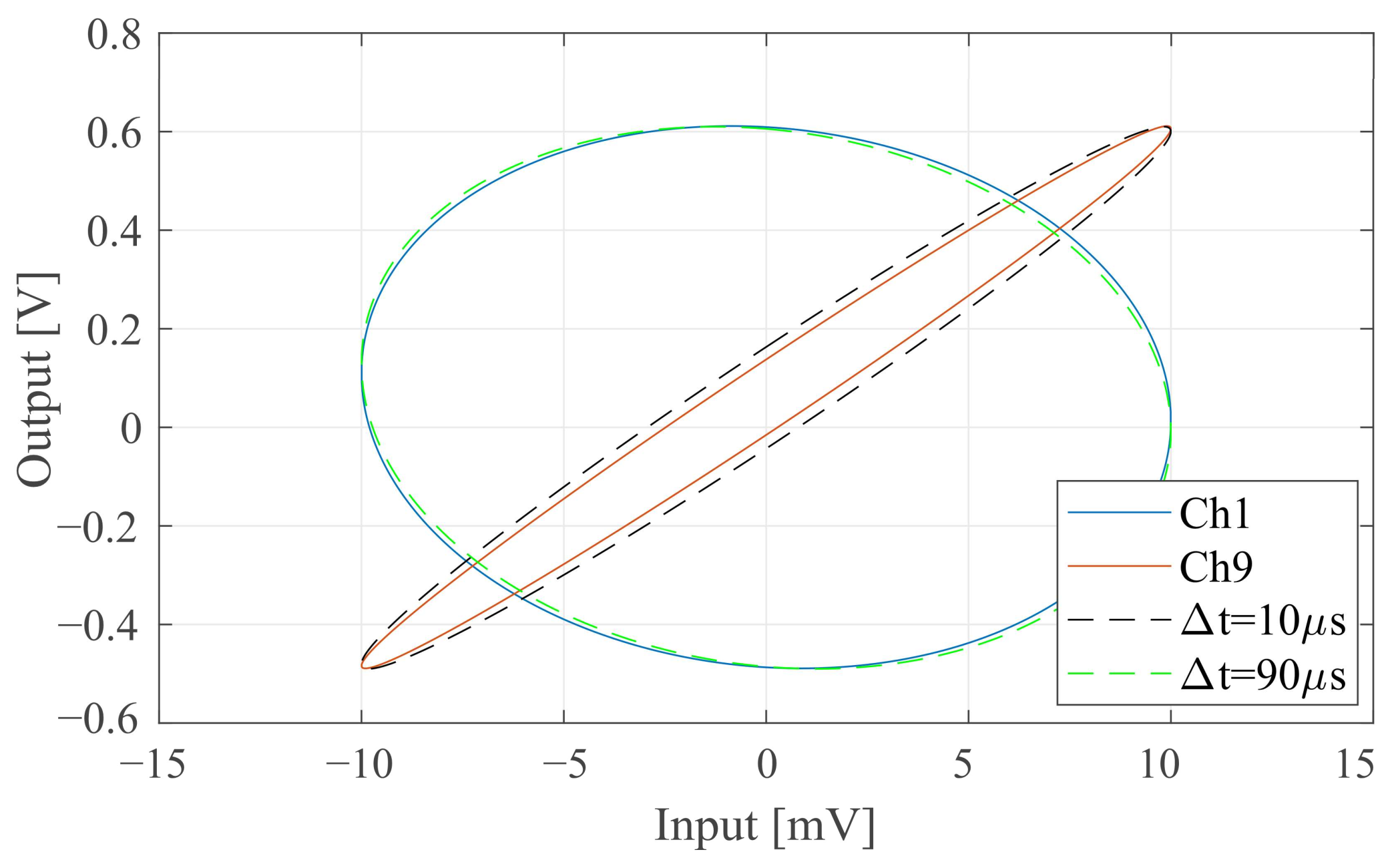

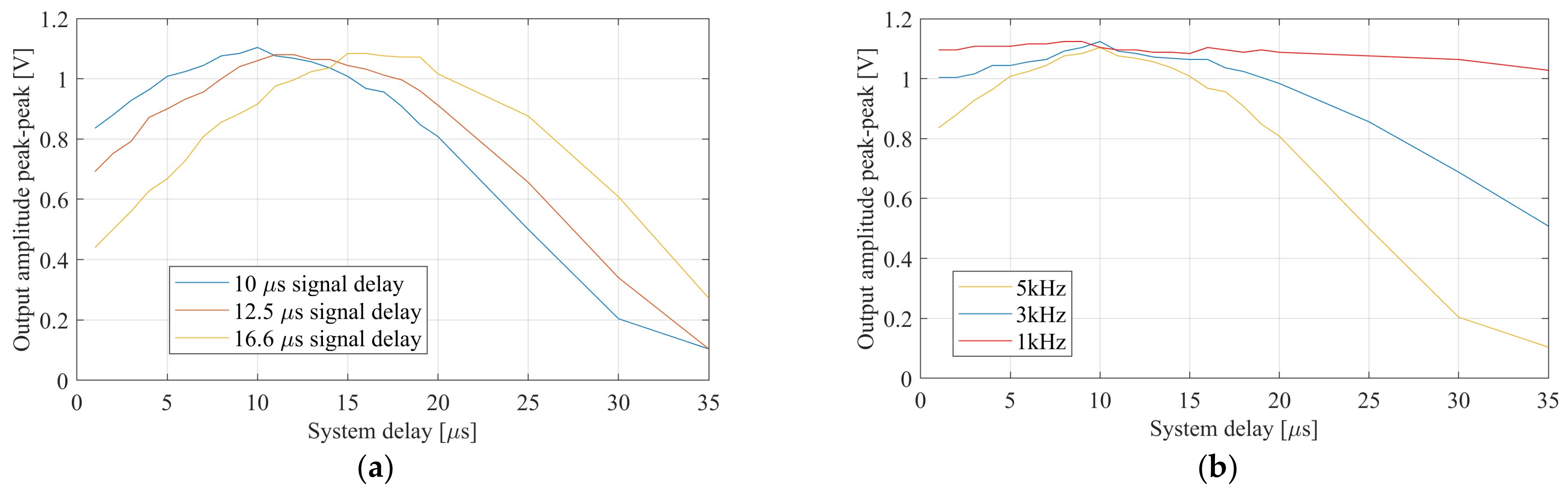

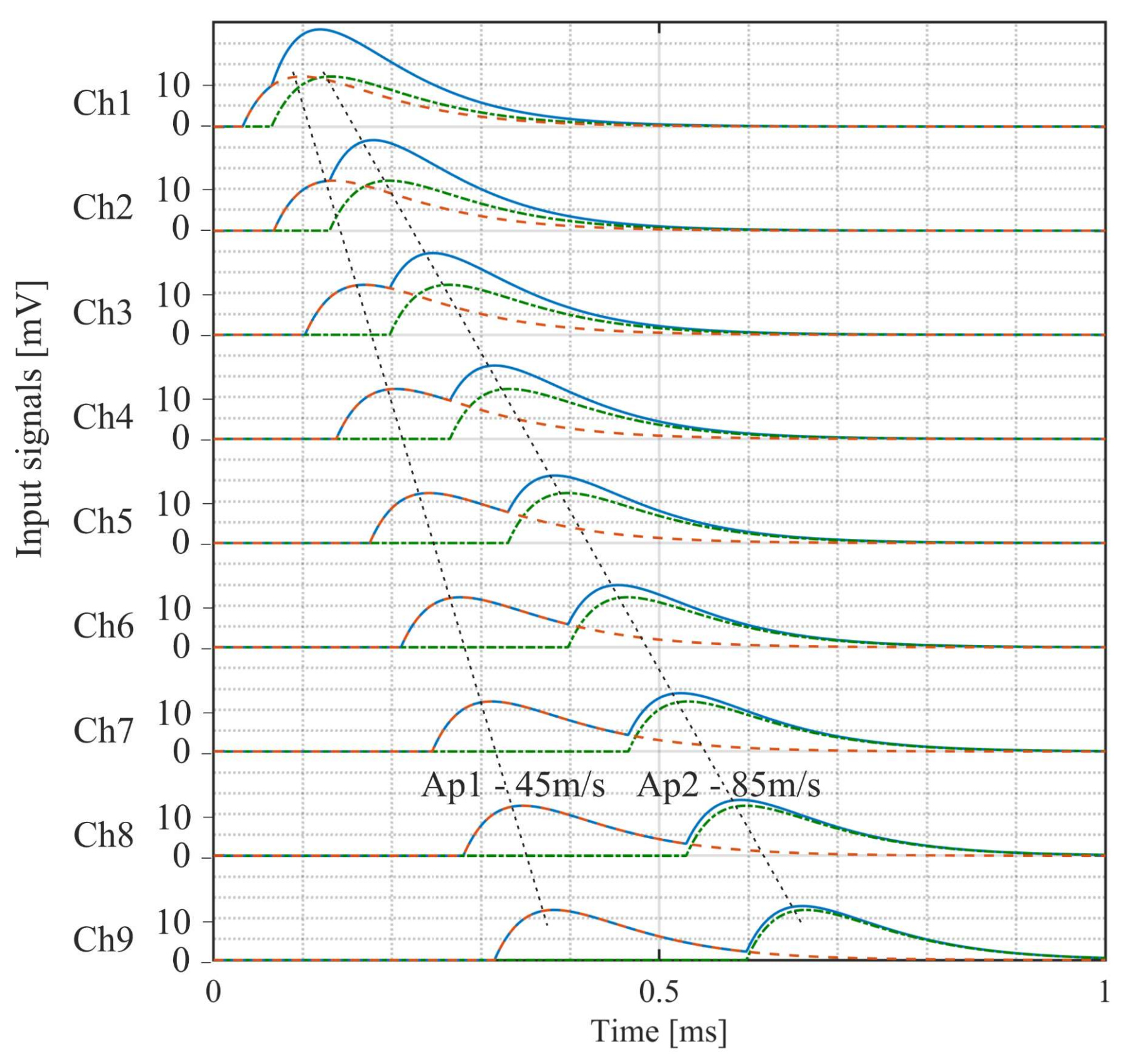

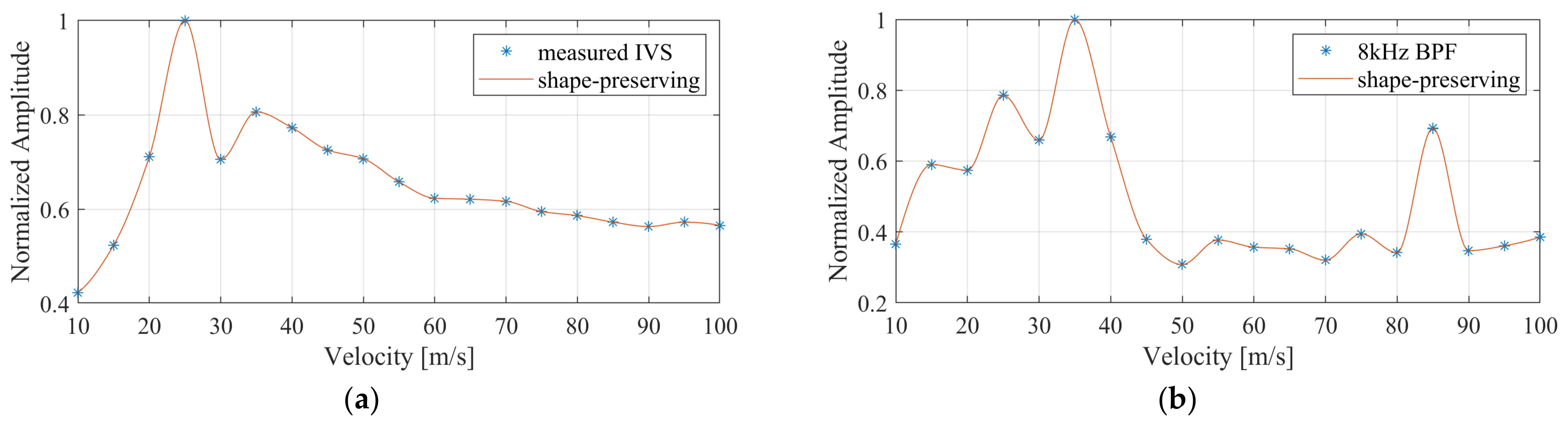

4. Simulated and Measured Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Brindley, G.; Rushton, D. Clinical Neurology: Neuroprostheses; Baillieres-Tindall: London, UK, 1995; Volume 14, Number 1. [Google Scholar]

- Chew, D.J.; Zhu, L.; Delivopoulos, E.; Minev, I.R.; Musick, K.M.; Mosse, C.A.; Craggs, M.; Donaldson, N.; Lacour, S.P.; McMahon, S.B. A microchannel neuroprosthesis for bladder control after spinal cord injury in rat. Sci. Transl. Med. 2013, 5, 210ra155. [Google Scholar] [CrossRef] [PubMed]

- Donaldson, N.; Rieger, R.; Schuettler, M.; Taylor, J. Noise and selectivity of velocity-selective multi-electrode nerve cuffs. Med. Biol. Eng. Comput. 2008, 46, 1005–1018. [Google Scholar] [CrossRef] [PubMed]

- Taylor, J.; Donaldson, N.; Winter, J. Multiple-electrode nerve cuffs for low-velocity and velocity-selective neural recording. Med. Biol. Eng. Comput. 2004, 42, 634–643. [Google Scholar] [CrossRef] [PubMed]

- Cho, Y.; Park, J.; Lee, C.; Lee, S. Recent progress on peripheral neural interface technology towards bioelectronic medicine. Bioelectron. Med. 2020, 6, 23. [Google Scholar] [CrossRef] [PubMed]

- Haugland, M.; Lickel, A.; Haase, J.; Sinkjær, T. Control of FES thumb force using slip information obtained from the cutaneous electroneurogram in quadriplegic man. IEEE Trans. Rehabil. Eng. 1999, 7, 215–227. [Google Scholar] [CrossRef]

- Haugland, M.K.; Hoffer, J.A. Artifact-free sensory nerve signals obtained from cuff electrodes during functional electrical stimulation of nearby muscles. IEEE Trans. Rehabil. Eng. 1994, 2, 37–40. [Google Scholar] [CrossRef]

- Haugland, M.; Lickel, A.; Riso, R.; Adamczyk, M.M.; Keith, M.; Jensen, I.L.; Haase, J.; Sinkjær, T. Restoration of lateral hand grasp using natural sensors. Artif. Organs 1997, 21, 250–253. [Google Scholar] [CrossRef]

- Haugland, M.; Hoffer, J. Slip information obtained from the cutaneous electroneurogram: Application in closed loop control of functional electrical stimulation. IEEE Trans. Rehab. Eng. 1994, 2, 29–36. [Google Scholar] [CrossRef]

- Haugland, M.K.; Hoffer, J.A.; Sinkjaer, T. Skin contact force information in sensory nerve signals recorded by implanted cuff electrodes. IEEE Trans. Rehabil. Eng. 1994, 2, 18–28. [Google Scholar] [CrossRef]

- Pflaum, C.; Riso, R.R.; Wiesspeiner, G. Performance of alternative amplifier configurations for tripolar nerve cuff recorded ENG. In Proceedings of the 18th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Amsterdam, The Netherlands, 31 October–3 November 1996; pp. 375–376. [Google Scholar]

- Koh, R.G.L.; Zariffa, J.; Jabban, L.; Yen, S.-C.; Donaldson, N.; Metcalfe, B.W. Tutorial: A guide to techniques for analysing recordings from the peripheral nervous system. J. Neural Eng. 2022, 19, 042001. [Google Scholar] [CrossRef]

- Taylor, J.; Schuettler, M.; Clarke, C.; Donaldson, N. A summary of the theory of velocity selective neural recording. In Proceedings of the Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Boston, MA, USA, 30 August–3 September 2011; pp. 4649–4652. [Google Scholar]

- Metcalfe, B.W.; Hunter, A.J.; Graham-Harper-Cater, J.E.; Taylor, J.T. Array processing of neural signals recorded from the peripheral nervous system for the classification of action potentials. J. Neurosci. Methods 2021, 347, 108967. [Google Scholar] [CrossRef] [PubMed]

- Metcalfe, B.; Granger, N.; Prager, J.; Sadrafshari, S.; Grego, T.; Taylor, J.; Donaldson, N. Selective Recording of Urinary Bladder Fullness from the Extradural Sacral Roots. In Proceedings of the 2020 42nd Annual International Conference of the IEEE Engineering in Medicine & Biology Society (EMBC), Montreal, QC, Canada, 20–24 July 2020; pp. 3873–3876. [Google Scholar]

- Schuettler, M.; Donaldson, N.; Seetohul, V.; Taylor, J. Fibre-selective recording from the peripheral nerves of frogs using a multi-electrode cuff. J. Neural Eng. 2013, 10, 036016. [Google Scholar] [CrossRef] [PubMed]

- Yoshida, K.; Kurstjens, G.A.M.; Hennings, K. Experimental validation of the nerve conduction velocity selective recording technique using a multi-contact cuff electrode. Med. Eng. Phys. 2009, 31, 1261–1270. [Google Scholar] [CrossRef] [PubMed]

- Schuettler, M.; Seetohul, V.; Rijkhoff, N.J.; Moeller, F.V.; Donaldson, N.; Taylor, J. Fibre-selective recording from peripheral nerves using a multiple-contact cuff: Report on pilot pig experiments. In Proceedings of the 2011 Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Boston, MA, USA, 30 August–3 September 2011; pp. 3103–3106. [Google Scholar]

- Jabban, L.; Ribeiro, M.; Andreis, F.R.; dos Santos Nielsen, T.G.N.; Metcalfe, B.W. Pig Ulnar Nerve Recording with Sinusoidal and Temporal Interference Stimulation. In Proceedings of the 2022 44th Annual International Conference of the IEEE Engineering in Medicine & Biology Society (EMBC), Glasgow, Scotland, 11–15 July 2022; pp. 5084–5088. [Google Scholar]

- Andreis, F.R.; Metcalfe, B.; Janjua, T.A.M.; Jensen, W.; Meijs, S.; Nielsen, T.G.N.d.S. The Use of the Velocity Selective Recording Technique to Reveal the Excitation Properties of the Ulnar Nerve in Pigs. Sensors 2021, 22, 58. [Google Scholar] [CrossRef] [PubMed]

- Karimi, F.; Seydnejad, S.R. Velocity Selective Neural Signal Recording Using a Space-Time Electrode Array. IEEE Trans. Neural Syst. Rehabil. Eng. 2015, 23, 837–848. [Google Scholar] [CrossRef] [PubMed]

- Rieger, R.; Schuettler, M.; Pal, D.; Clarke, C.; Langlois, P.; Taylor, J.; Donaldson, N. Very low-noise ENG amplifier system using CMOS technology. IEEE Trans. Neural Syst. Rehabil. Eng. 2006, 14, 427–437. [Google Scholar] [CrossRef]

- Clarke, C.T.; Xu, X.; Rieger, R.; Taylor, J.; Donaldson, N. An implanted system for multi-site nerve cuff-based ENG recording using velocity selectivity. Analog Integr. Circuits Signal Process. 2009, 58, 91–104. [Google Scholar] [CrossRef]

- Clarke, C.; Rieger, R.; Schuettler, M.; Donaldson, N.; Taylor, J. An implantable ENG detector with in-system velocity selective recording (vsr) capability. Med. Biol. Eng. Comput. 2017, 55, 885–895. [Google Scholar] [CrossRef]

- Rieger, R.; Taylor, J. Delay-line-based signal processing ASIC for velocity selective nerve recording. In Proceedings of the 2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Ishigaki, Japan, 17–20 November 2014; pp. 205–208. [Google Scholar]

- Pelgrom, M.J.M. Analog-to-Digital Conversion; Springer: Berlin/Heidelberg, Germany, 2013. [Google Scholar]

- Chuang, C. Analysis of the settling behavior of an operational amplifier. IEEE J. Solid-State Circuits 1982, 17, 74–80. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits; Mc Graw Hill: New York, NY, USA, 2017. [Google Scholar]

- Rieger, R.; Schuettler, M.; Chuang, S.-C. A device for emulating cuff recordings of action potentials propagating along peripheral nerves. IEEE Trans. Neural Syst. Rehabil. Eng. 2014, 22, 937–945. [Google Scholar] [CrossRef]

- Rieger, R.; Taylor, J. A Switched-Capacitor Front-End for Velocity-Selective ENG Recording. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 480–488. [Google Scholar] [CrossRef] [PubMed]

| This Work | [25] | [30] | [23] | |

|---|---|---|---|---|

| Channel | 9 | 8 | 2 | 10 |

| Technology (µm) | 0.35 | 0.35 | 0.8 | 0.8 |

| Gain (dB) | 36 | - | 36.5 | - |

| IRN/ch (nV/√Hz) | 67 | - | 14 * | - |

| Sample and Hold | Analogue | Analogue | Analogue | Digital |

| Detection Velocity (m/s) | 10–300 | 16–120 | 39–300 | 1–30 |

| Clock Generator | Integrated | Integrated | µC | µC |

| System Delay Td (µs) | 10–300 | 10–100 | 5–80 | 100–3000 |

| Δ Td (µs) | 1–300 | 10 | 5–80 | 100 |

| Rel. Velocity Resolution | 0.003–0.09 | 0.09–0.5 | 0.06–0.2 | 0.03–0.5 |

| Power/ch (µW) | 91 | 22.5 | 1400 | >13,000 |

| Area/ch (mm2) | 0.129 | 0.0975 | 0.05 | 1.6 |

| FOM (µm2) | 387 | 8775 | 3000 | 48,000 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sadrafshari, S.; Simmich, S.; Metcalfe, B.; Prager, J.; Granger, N.; Donaldson, N.; Rieger, R.; Taylor, J. CMOS Analogue Velocity-Selective Neural Processing System. Electronics 2024, 13, 569. https://doi.org/10.3390/electronics13030569

Sadrafshari S, Simmich S, Metcalfe B, Prager J, Granger N, Donaldson N, Rieger R, Taylor J. CMOS Analogue Velocity-Selective Neural Processing System. Electronics. 2024; 13(3):569. https://doi.org/10.3390/electronics13030569

Chicago/Turabian StyleSadrafshari, Shamin, Sebastian Simmich, Benjamin Metcalfe, Jon Prager, Nicolas Granger, Nick Donaldson, Robert Rieger, and John Taylor. 2024. "CMOS Analogue Velocity-Selective Neural Processing System" Electronics 13, no. 3: 569. https://doi.org/10.3390/electronics13030569

APA StyleSadrafshari, S., Simmich, S., Metcalfe, B., Prager, J., Granger, N., Donaldson, N., Rieger, R., & Taylor, J. (2024). CMOS Analogue Velocity-Selective Neural Processing System. Electronics, 13(3), 569. https://doi.org/10.3390/electronics13030569