An Enhanced Verilog-A Model for Graphene Field-Effect Transistors Using Variable Fermi Velocity

Abstract

1. Introduction

2. Evolution of GFET Models

2.1. Fermi Velocity

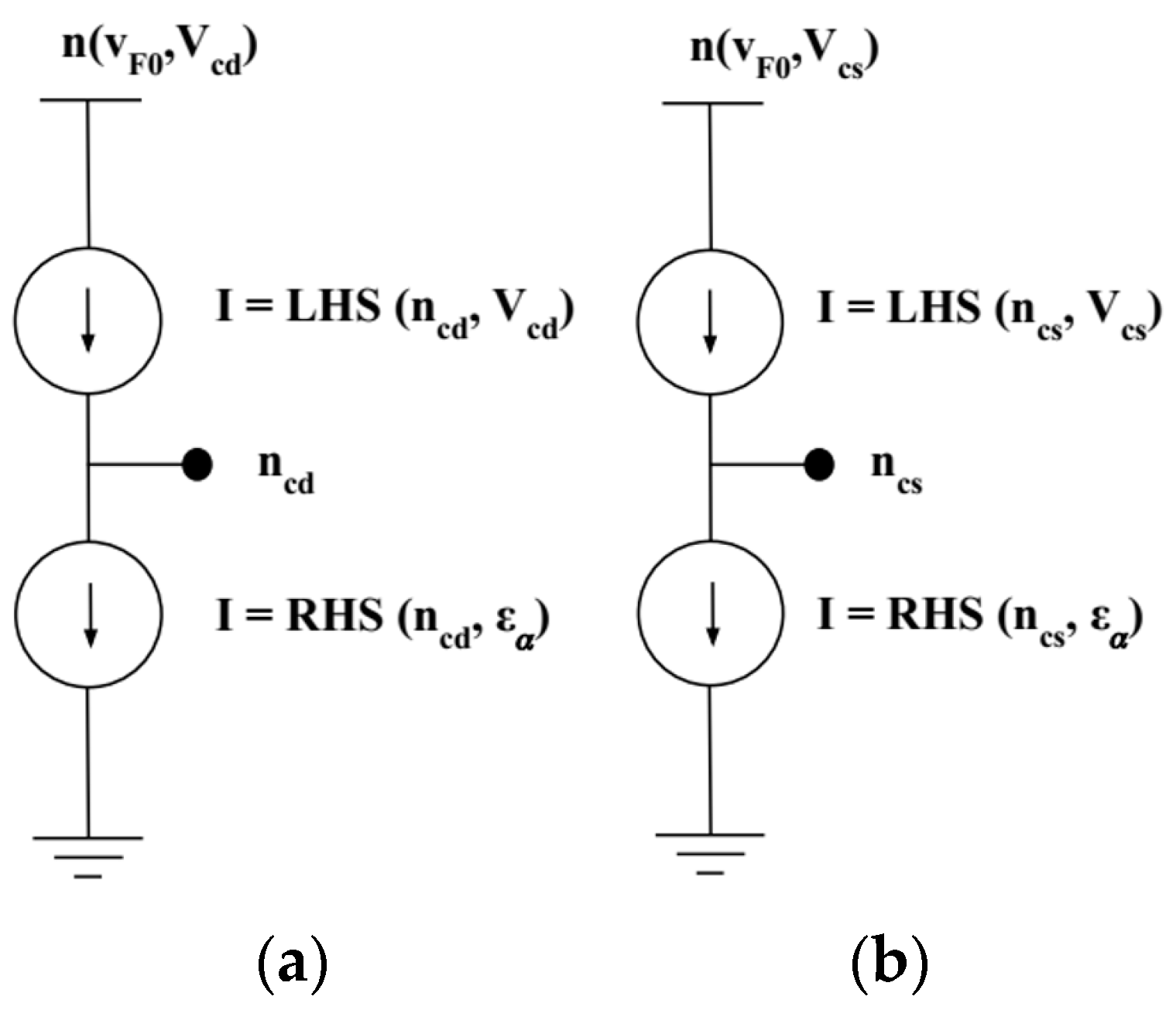

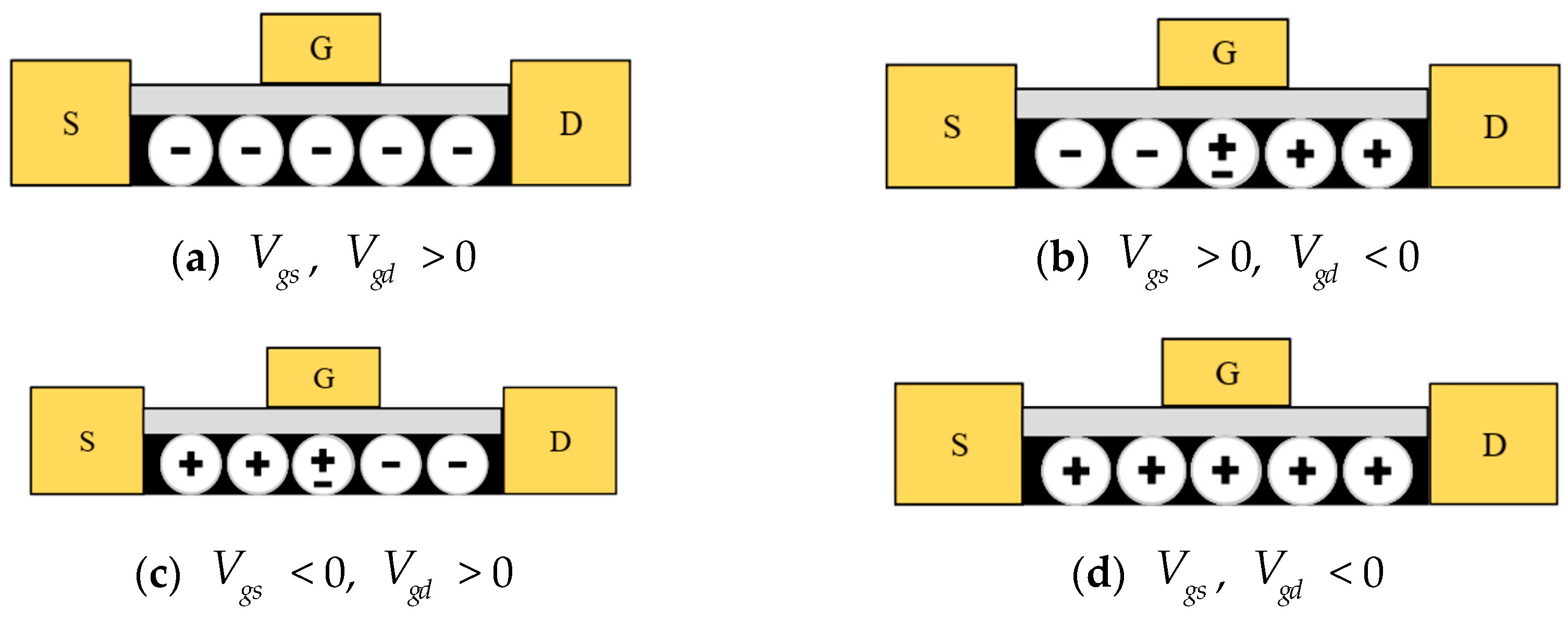

2.2. Revisiting the Dual-Gated GFET Model

3. Fermi Velocity Modeling and Improved Mobility

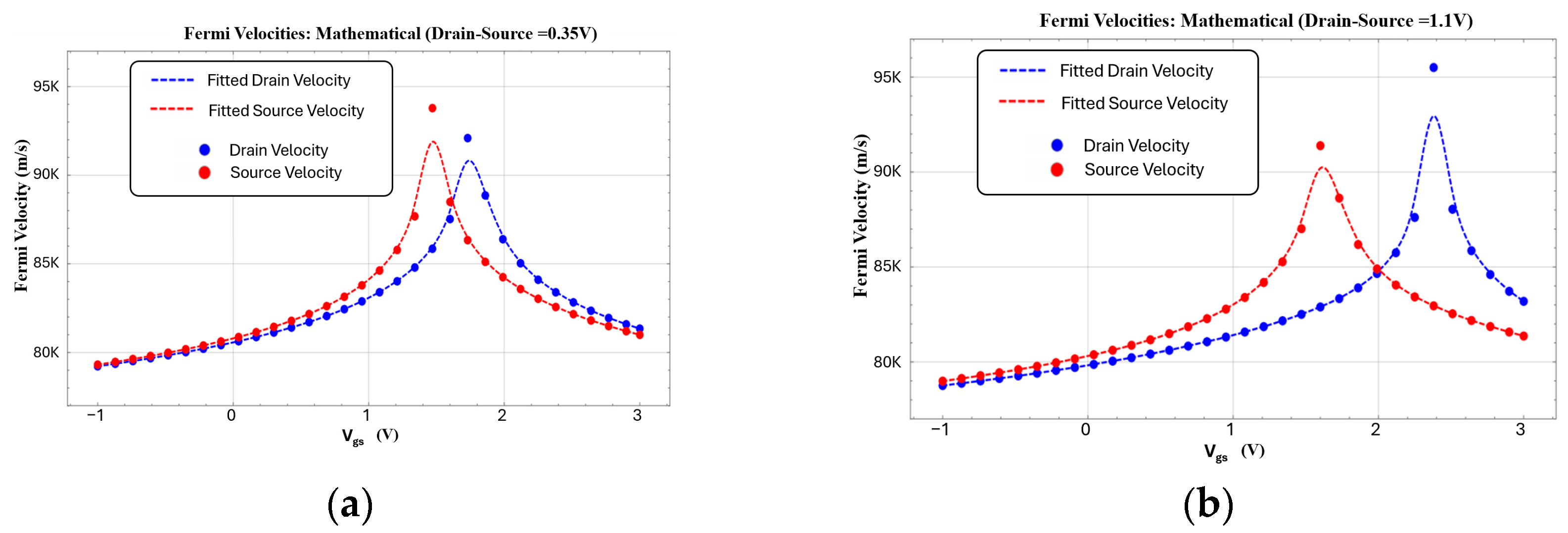

3.1. Fermi Velocity Modeling

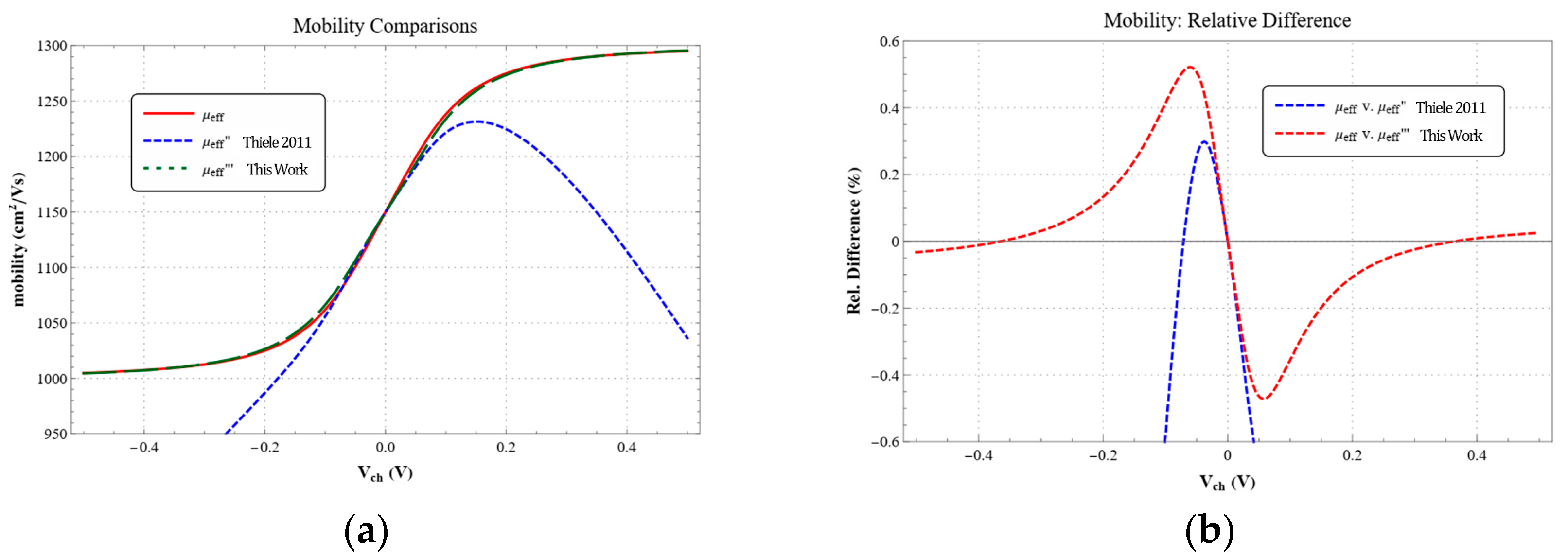

3.2. Employing the Novel Fermi Velocity Model

3.3. Simplifying the Effective Mobility for Simulation

3.4. The Closed-Form Solution for the Drain Current

4. The Implementation and Validation of the Model

4.1. Creating the Enhanced GFET Model

4.2. Fermi Velocity Model

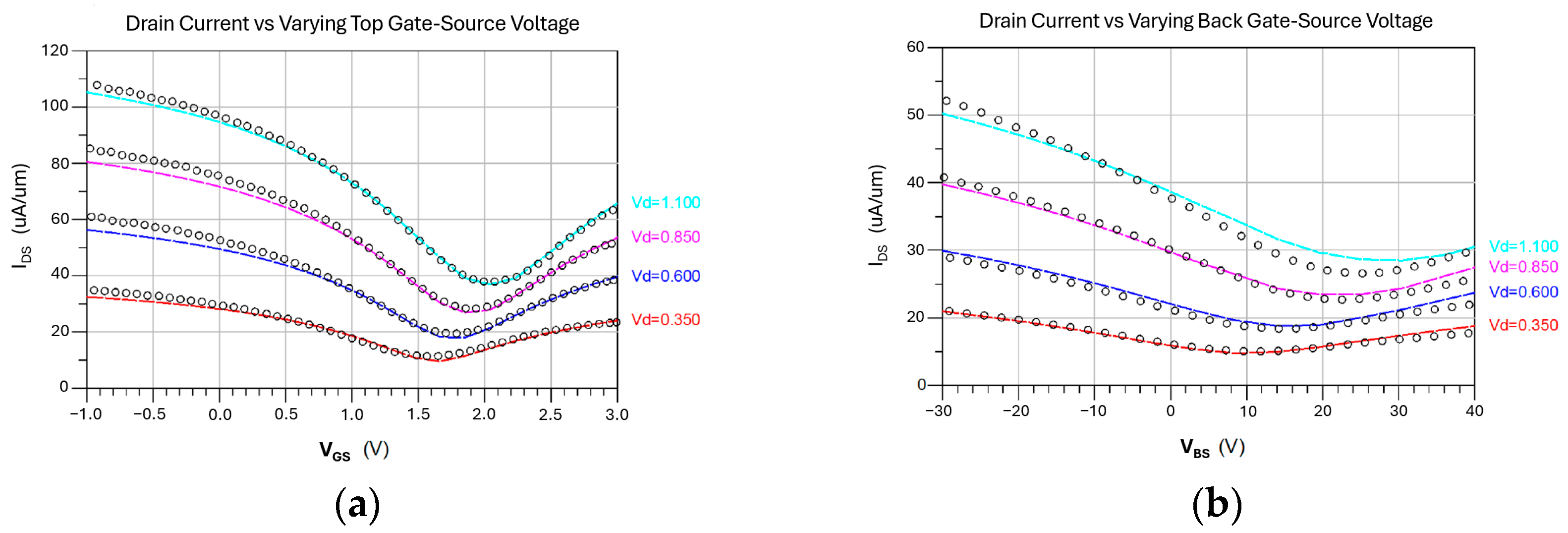

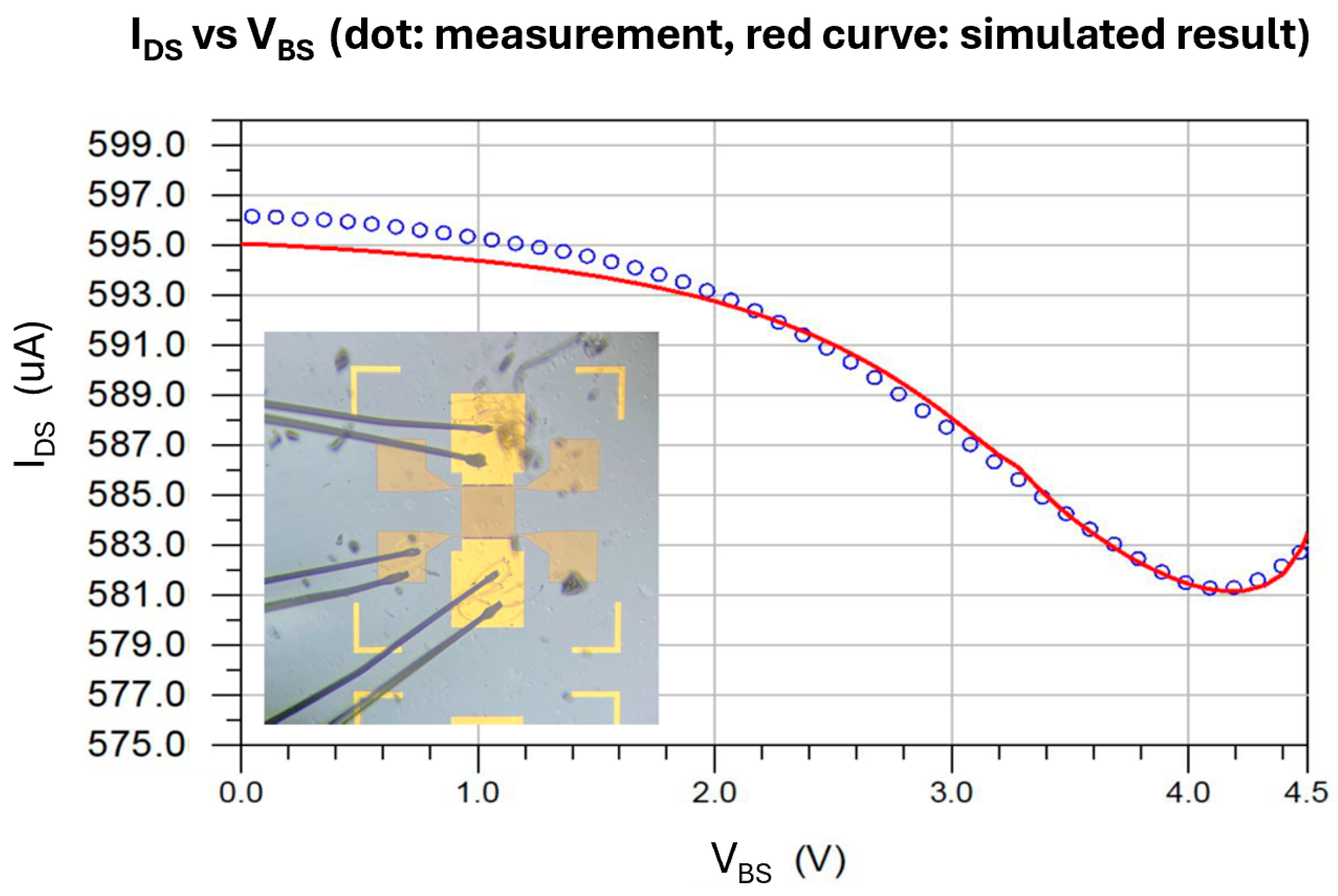

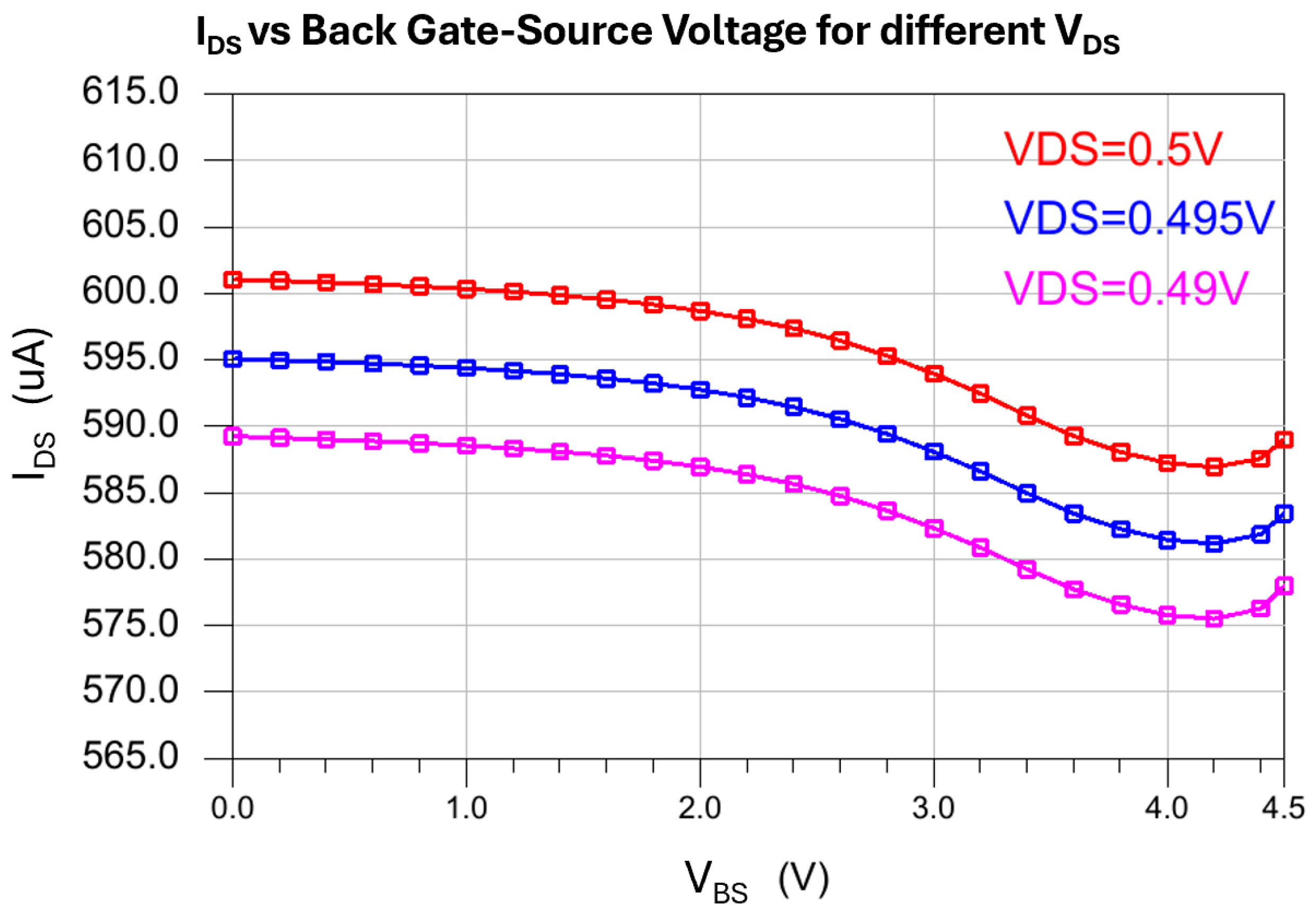

4.3. GFET Model Validation

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Novoselov, K.S.; Geim, A.K.; Morozov, S.V.; Jiang, D.; Zhang, Y.; Dubonos, S.V.; Grigorieva, I.V.; Firsov, A.A. Electric field effect in atomically thin carbon films. Science 2004, 306, 666–669. [Google Scholar] [CrossRef] [PubMed]

- Thiele, S.A.; Schaefer, J.A.; Schwierz, F. Modeling of graphene metal-oxide-semiconductor field-effect transistors with gapless large-area graphene channels. J. Appl. Phys. 2010, 107, 094505. [Google Scholar] [CrossRef]

- Tian, J. Theory, Modelling and Implementation of Graphene Field- Effect Transistor. Ph.D. Thesis, Queen Mary University of London, London, UK, 2017. [Google Scholar]

- Fang, T.; Konar, A.; Xing, H.; Jena, D. Carrier statistics and quantum capacitance of graphene sheets and ribbons. Appl. Phys. Lett. 2007, 91, 0921091-1–0921091-3. [Google Scholar] [CrossRef]

- Thiele, S.; Schwierz, F. Modeling of the steady state characteristics of large-area graphene field-effect transistors. J. Appl. Phys. 2011, 110. [Google Scholar] [CrossRef]

- Wang, Z.; Zhang, Z.; Peng, L. Graphene-based ambipolar electronics for radio frequency applications. Chin. Sci. Bull. 2012, 57, 2956–2970. [Google Scholar] [CrossRef]

- Parrish, K.; Ramón, M.E.; Banerjee, S.; Akinwande, D. A Compact Model for Graphene FETs for Linear and Non-linear Circuits. In Proceedings of the IEEE International Conference on Simulation of Semiconductor Processes and Devices, Denver, CO, USA, 5–7 September 2012. [Google Scholar]

- Rodriguez, S.; Vaziri, S.; Smith, A.; Fregonese, S.; Ostling, M.; Lemme, M.C.; Rusu, A. A Comprehensive Graphene FET Model for Circuit Design. IEEE Trans. Electron Devices 2014, 61, 1199–1206. [Google Scholar] [CrossRef]

- Landauer, G.M.; Jimenez, D.; Gonzalez, J.L. An Accurate and Verilog-A Compatible Compact Model for Graphene Field-Effect Transistors. IEEE Trans. Nanotechnol. 2014, 13, 895–904. [Google Scholar] [CrossRef]

- Tian, J.; Katsounaros, A.; Smith, D.; Hao, Y. Graphene Field-Effect Transistor Model with Improved Carrier Mobility Analysis. IEEE Trans. Electron Devices 2015, 62, 3433–3440. [Google Scholar] [CrossRef]

- Elias, D.C.; Gorbachev, R.V.; Mayorov, A.S.; Morozov, S.V.; Zhukov, A.A.; Blake, P.; Ponomarenko, L.A.; Grigorieva, I.V.; Novoselov, K.S.; Guinea, F.; et al. Dirac cones reshaped by interaction effects in suspended graphene. Nat. Phys. 2011, 7, 701–704, Erratum in: Nat. Phys. 2012, 7, 172. [Google Scholar] [CrossRef]

- Hwang, C.; Siegel, D.A.; Mo, S.-K.; Regan, W.; Ismach, A.; Zhang, Y.; Zettl, A.; Lanzara, A. Fermi velocity engineering in graphene by substrate modification. Sci. Rep. 2012, 2, 590. [Google Scholar] [CrossRef]

- Van Halen, P.; Pulfrey, D.L. Accurate, short series approximations to Fermi–Dirac integrals of order −1/2, 1/2, 1, 3/2, 2, 5/2, 3, and 7/2. J. Appl. Phys. 1985, 57, 5271–5274. [Google Scholar] [CrossRef]

- Zhu, W.; Perebeinos, V.; Freitag, M.; Avouris, P. Carrier scattering, mobilities, and electrostatic potential in monolayer, bilayer, and trilayer graphene. Phys. Rev. B 2009, 80, 235402. [Google Scholar] [CrossRef]

- Luryi, S. Quantum capacitance devices. Appl. Phys. Lett. 1988, 52, 501–503. [Google Scholar] [CrossRef]

- Parrish, K.N.; Akinwande, D. Impact of contact resistance on the transconductance and linearity of graphene transistors. Appl. Phys. Lett. 2011, 98, 183505. [Google Scholar] [CrossRef]

- Deng, J.; Wong, H.-S.P. A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application—Part I: Model of the Intrinsic Channel Region. IEEE Trans. Electron Devices 2007, 54, 3186–3194. [Google Scholar] [CrossRef]

- Whelan, P.R.; Shen, Q.; Zhou, B.; Serrano, I.G.; Kamalakar, M.V.; A Mackenzie, D.M.; Ji, J.; Huang, D.; Shi, H.; Luo, D.; et al. Fermi velocity renormalization in graphene probed by terahertz time-domain spectroscopy. 2D Mater. 2020, 7, 035009. [Google Scholar] [CrossRef]

- Stauber, T.; Parida, P.; Trushin, M.; Ulybyshev, M.V.; Boyda, D.L.; Schliemann, J. Interacting Electrons in Graphene: Fermi Velocity Renormalization and Optical Response. Phys. Rev. Lett. 2017, 118, 266801. [Google Scholar] [CrossRef] [PubMed]

- Aguirre-Morales, J.-D.; Fregonese, S.; Mukherjee, C.; Wei, W.; Happy, H.; Maneux, C.; Zimmer, T. A Large-Signal Monolayer Graphene Field-Effect Transistor Compact Model for RF-Circuit Applications. IEEE Trans. Electron Devices 2017, 64, 4302–4309. [Google Scholar] [CrossRef]

- Wang, H.; Hsu, A.; Kong, J.; Antoniadis, A.D.; Palacios, T. Compact Virtual-Source Current–Voltage Model for Top- and Back-Gated Graphene Field-Effect Transistors. IEEE Trans. Electron Devices 2011, 58, 1523–1533. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ji, S.; Mappes, J.; Koudelka, P.; Scardelletti, M.C.; Zorman, C.; Lavasani, H.M. An Enhanced Verilog-A Model for Graphene Field-Effect Transistors Using Variable Fermi Velocity. Electronics 2024, 13, 5051. https://doi.org/10.3390/electronics13245051

Ji S, Mappes J, Koudelka P, Scardelletti MC, Zorman C, Lavasani HM. An Enhanced Verilog-A Model for Graphene Field-Effect Transistors Using Variable Fermi Velocity. Electronics. 2024; 13(24):5051. https://doi.org/10.3390/electronics13245051

Chicago/Turabian StyleJi, Shuwei, John Mappes, Peter Koudelka, Maximilian C. Scardelletti, Christian Zorman, and Hossein Miri Lavasani. 2024. "An Enhanced Verilog-A Model for Graphene Field-Effect Transistors Using Variable Fermi Velocity" Electronics 13, no. 24: 5051. https://doi.org/10.3390/electronics13245051

APA StyleJi, S., Mappes, J., Koudelka, P., Scardelletti, M. C., Zorman, C., & Lavasani, H. M. (2024). An Enhanced Verilog-A Model for Graphene Field-Effect Transistors Using Variable Fermi Velocity. Electronics, 13(24), 5051. https://doi.org/10.3390/electronics13245051