High-Data-Rate Modulators Based on Graphene Transistors: Device Circuit Co-Design Proposals †

Abstract

1. Introduction

2. Exploiting Ambipolarity in GFETs

3. Device under Test: Modeling and Calibration

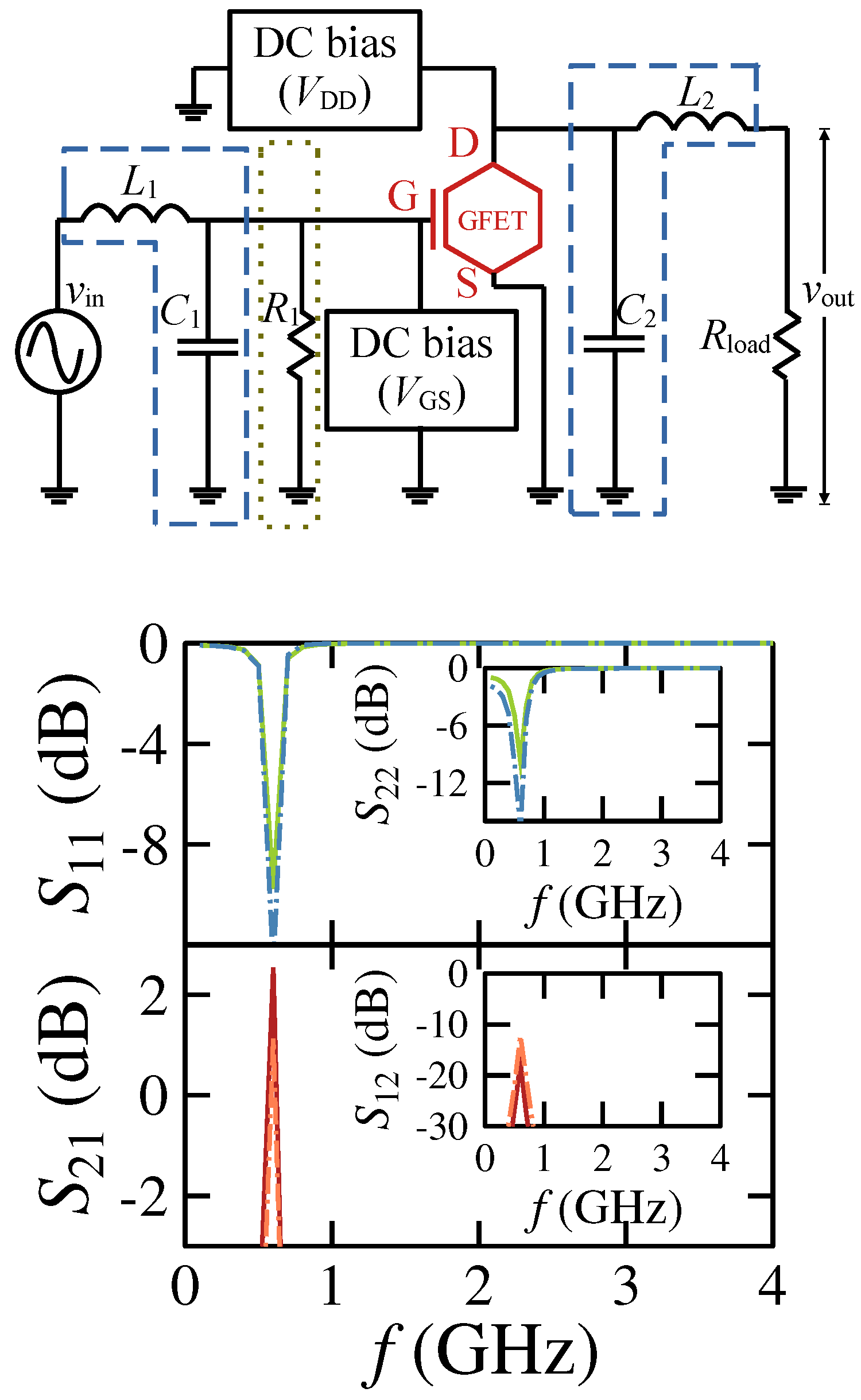

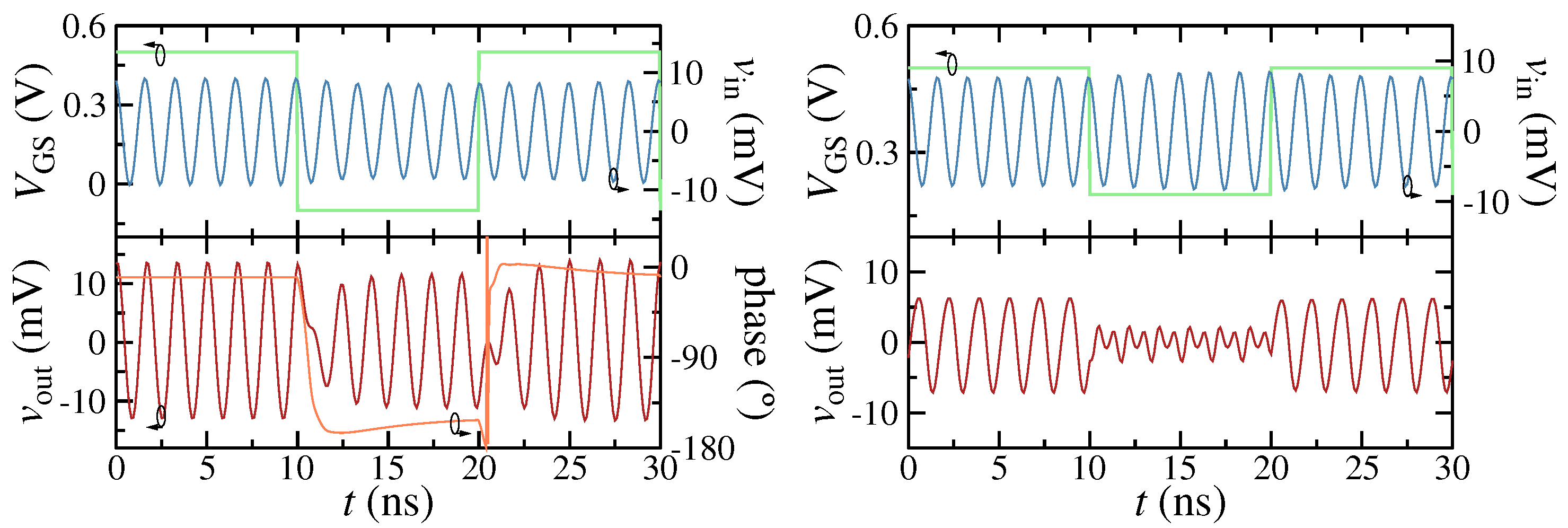

4. Multifunctional Circuit Design and Results

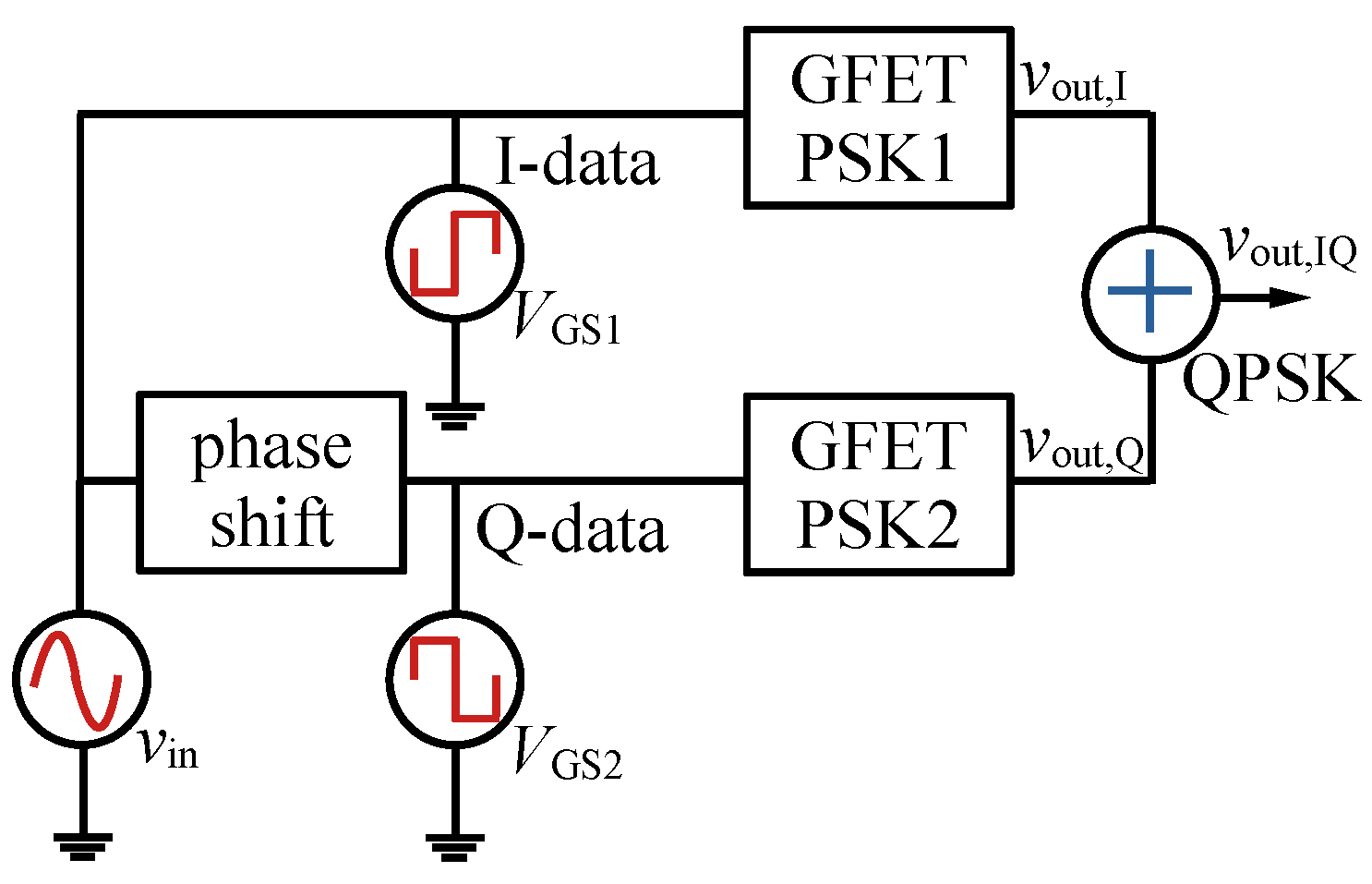

5. Modulator Designs and Results: PSK, FSK and QPSK

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Rudolph, D. Modulation Methods. In Fundamentals of RF and Microwave Techniques and Technologies; Hartnagel, H.L., Quay, R., Rohde, U.L., Rudolph, M., Eds.; Springer: Cham, Switzerland, 2023; pp. 1297–1528. [Google Scholar]

- Alimenti, F.; Palazzi, V.; Mariotti, C.; Mezzanotte, P.; Correia, R.; Carvalho, N.B.; Roselli, L. Smart Hardware for Smart Objects: Microwave Electronic Circuits to Make Objects Smart. IEEE Microw. Mag. 2018, 19, 48–68. [Google Scholar] [CrossRef]

- Champlain, J.G. On the use of the term “ambipolar”. Appl. Phys. Lett. 2011, 99, 123502. [Google Scholar] [CrossRef]

- Moura, R.; Claus, M.; Blawid, S. Multi-mode nanoFETs: From low power to high performance on demand. Semicond. Sci. Technol. 2020, 35, 055027. [Google Scholar] [CrossRef]

- Mikolajick, T.; Galderisi, G.; Simon, M.; Rai, S.; Kumar, A.; Heinzig, A.; Weber, W.M.; Trommer, J. 20 Years of reconfigurable field-effect transistors: From concepts to future applications. Solid-State Electron. 2021, 186, 108036. [Google Scholar] [CrossRef]

- Das, S.; Das, S. Digital Keying Enabled by Reconfigurable 2D Modulators. Adv. Mater. 2022, 34, 2203753. [Google Scholar] [CrossRef]

- Ghivela, G.C.; Sengupta, J. The Promise of Graphene: A Survey of Microwave Devices Based on Graphene. IEEE Microw. Mag. 2020, 21, 48–65. [Google Scholar] [CrossRef]

- Hartmann, M.; Hermann, S.; Marsh, P.F.; Rutherglen, C.; Wang, D.; Ding, L.; Peng, L.-M.; Claus, M.; Schröter, M. CNTFET technology for RF applications: Review and future perspective. IEEE J. Microw. 2021, 1, 275–287. [Google Scholar] [CrossRef]

- Ramos-Silva, J.N.; Pacheco-Sanchez, A.; Ramirez-Garcia, E.; Jiménez, D. Multifunctional high-frequency circuit capabilities of ambipolar carbon nanotube FETs. IEEE Trans. Nanotechnol. 2021, 20, 474–480. [Google Scholar] [CrossRef]

- Yang, X.; Liu, G.; Balandin, A.A.; Mohanram, K. Triple-Mode Single-Transistor Graphene Amplifier and Its Applications. ACS Nano 2010, 4, 5532–5538. [Google Scholar] [CrossRef]

- Lee, S.; Lee, K.; Liu, C.-H.; Kulkarni, G.S.; Zhong, Z. Flexible and transparent all-graphene circuits for quaternary digital modulations. Nat. Commun. 2012, 3, 1018. [Google Scholar] [CrossRef]

- Habibpour, O.; He, Z.S.; Strupinski, W.; Rorsman, N.; Ciuk, T.; Ciepielewski, P.; Zirath, H. Graphene FET Gigabit ON–OFF Keying Demodulator at 96 GHz. IEEE Electron. Device Lett. 2016, 37, 333–336. [Google Scholar] [CrossRef]

- Habibpour, O.; He, Z.S.; Strupinski, W.; Rorsman, N.; Zirath, H. Wafer scale millimeter-wave integrated circuits based on epitaxial graphene in high data rate communication. Sci. Rep. 2017, 7, 41828. [Google Scholar] [CrossRef]

- Saeed, M.; Palacios, P.; Wei, M.-D.; Baskent, E.; Fan, C.-Y.; Uzlu, B.; Wang, K.-T.; Hemmetter, A.; Wang, Z.; Neumaier, D.; et al. Graphene-Based Microwave Circuits: A Review. Adv. Mater. 2022, 34, 2108473. [Google Scholar] [CrossRef]

- Tateno, Y.; Mitsuhashi, F.; Adachi, M.; Yonemura, T.; Saito, Y.; Yamamoto, Y.; Nakabayashi, T. An investigation to determine the interface condition between graphene and aluminum oxide. Jpn. J. Appl. Phys. 2020, 59, 124001. [Google Scholar] [CrossRef]

- Pacheco-Sanchez, A.; Mavredakis, N.; Feijoo, P.C.; Wei, W.; Pallecchi, E.; Happy, H.; Jiménez, D. Experimental observation and modeling of the impact of traps on static and analog/HF performance of graphene transistors. IEEE Trans. Electron Devices 2020, 67, 5790–5796. [Google Scholar] [CrossRef]

- Knobloch, T.; Uzlu, B.; Illarionov, Y.; Wang, Z.; Otto, M.; Filipovic, L.; Waltl, M.; Neumaier, D.; Lemme, M.C.; Grasser, T. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning. Nat. Electron. 2022, 5, 356–366. [Google Scholar] [CrossRef]

- Ribes, G.; Mitard, J.; Denais, M.; Bruyere, S.; Monsieur, F.; Parthasarathy, C.; Vincent, E.; Ghibaudo, G. Review on high-k dielectrics reliability issues. IEEE Trans. Device Mater. Reliab. 2005, 5, 5–19. [Google Scholar] [CrossRef]

- Hong, S.K.; Kim, C.S.; Hwang, W.S.; Cho, B.J. Hybrid Integration of Graphene Analog and Silicon Complementary Metal-Oxide-Semiconductor Digital Circuits. ACS Nano 2016, 10, 7142–7146. [Google Scholar] [CrossRef]

- Akinwande, D.; Huyghebaert, C.; Wang, C.-H.; Serna, M.I.; Goossens, S.; Li, L.-J.; Philip Wong, H.-S.; Koppens, F.H.L. Graphene and twodimensional materials for silicon technology. Nature 2019, 573, 507–518. [Google Scholar] [CrossRef]

- Pacheco-Sanchez, A.; Ramos-Silva, J.N.; Mavredakis, N.; Ramírez-García, E.; Jiménez, D. Design of GFET-based active modulators leveraging device performance reproducibility conditions. In Proceedings of the IEEE Conference on Design of Circuits and Integrated Systems (DCIS), Malaga, Spain, 15–17 November 2023. [Google Scholar]

- Pasadas, F.; Medina-Rull, A.; Ruiz, F.G.; Ramos-Silva, J.N.; Pacheco-Sanchez, A.; Pardo, M.C.; Toral-Lopez, A.; Godoy, A.; Ramírez-García, E.; Jiménez, D.; et al. Exploiting ambipolarity in graphene field-effect transistors for novel designs on high-frequency analog electronics. Small 2023, 19, 2303595. [Google Scholar] [CrossRef]

- Heinzig, A.; Slesazeck, S.; Kreupl, F.; Mikolajick, T.; Weber, W.M. Reconfigurable Silicon Nanowire Transistors. Nano Lett. 2012, 12, 119–124. [Google Scholar] [CrossRef] [PubMed]

- Pasadas, F.; Feijoo, P.C.; Mavredakis, N.; Pacheco-Sanchez, A.; Chaves, F.A.; Jiménez, D. Compact modeling technology for the simulation of integrated circuits based on graphene field-effect transistors. Adv. Mater. 2022, 34, 2201691. [Google Scholar] [CrossRef]

- Mavredakis, N.; Pacheco-Sanchez, A.; Txoperena, O.; Torres, E.; Jiménez, D. A Scalable Compact Model for the Static Drain Current of Graphene FETs. IEEE Trans. Electron Devices 2024, 71, 853–859. [Google Scholar] [CrossRef]

- Wei, W.; Zhou, X.; Deokar, G.; Kim, H.; Belhaj, M.M.; Galopin, E.; Pallecchi, E.; Happy, H. Graphene FETs with aluminum bottom-gate electrodes and its natural oxide as dielectrics. IEEE Trans. ONE Devices 2015, 62, 2769–2773. [Google Scholar] [CrossRef]

- Toral-Lopez, A.; Marin, E.G.; Pasadas, F.; Gonzalez-Medina, J.M.; Ruiz, F.G.; Jiménez, D.; Godoy, A. GFET Asymmetric Transfer Response Analysis through Access Region Resistances. Nanomaterials 2019, 9, 1027. [Google Scholar] [CrossRef]

- Zhang, Z.; Xu, H.; Zhong, H.; Peng, L.-M. Direct extraction of carrier mobility in graphene field-effect transistor using current-voltage and capacitance-voltage measurements. Appl. Phys. Lett. 2012, 101, 213101. [Google Scholar] [CrossRef]

- Gahoi, A.; Kataria, S.; Driussi, F.; Venica, S.; Pandey, H.; Esseni, D.; Selmi, L.; Lemme, M.C. Dependable Contact Related Parameter Extraction in Graphene–Metal Junctions. Adv. Electron. Mater. 2020, 6, 2000386. [Google Scholar] [CrossRef]

- Carrion, E.A.; Serov, A.Y.; Islam, S.; Behnam, A.; Malik, A.; Xiong, F.; Bianchi, M.; Sordan, R.; Pop, E. Hysteresis-Free Nanosecond Pulsed Electrical Characterization of Top-Gated Graphene Transistors. IEEE Trans. Electron Devices 2014, 61, 1583–1589. [Google Scholar] [CrossRef]

- Nathawat, J.; Zhao, M.; Kwan, C.-P.; Yin, S.; Arabchigavkani, N.; Randle, M.; Ramamoorthy, H.; He, G.; Somphonsane, R.; Matsumoto, N.; et al. Transient Response of h-BN-Encapsulated Graphene Transistors: Signatures of Self-Heating and Hot-Carrier Trapping. ACS Omega 2019, 4, 4082–4090. [Google Scholar] [CrossRef]

- Zhu, Y.; Zuegel, J.D.; Marciante, J.R.; Wu, H. Distributed Waveform Generator: A New Circuit Technique for Ultra-Wideband Pulse Generation, Shaping and Modulation. IEEE J. Solid-State Circuits 2009, 44, 808–823. [Google Scholar] [CrossRef]

- Sneler, L.; Matic, T.; Herceg, M. A Tunable CMOS IR-UWB Pulse Generator Based on Feedback Controlled Oscillator Switching. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 1902–1906. [Google Scholar] [CrossRef]

- Karthaus, U.; Fischer, M. Fully integrated passive UHF RFID transponder IC with 16.7-uW minimum RF input power. IEEE J. Solid-State Circuits 2003, 38, 1602–1608. [Google Scholar] [CrossRef]

- Carlowitz, C.; Vossiek, M. PSK Modulator for Regenerative Sampling Gigabit UWB Communication. In Proceedings of the GeMiC 2014; German Microwave Conference, Aachen, Germany, 10–12 March 2014. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pacheco-Sanchez, A.; Ramos-Silva, J.N.; Mavredakis, N.; Ramírez-García, E.; Jiménez, D. High-Data-Rate Modulators Based on Graphene Transistors: Device Circuit Co-Design Proposals. Electronics 2024, 13, 4022. https://doi.org/10.3390/electronics13204022

Pacheco-Sanchez A, Ramos-Silva JN, Mavredakis N, Ramírez-García E, Jiménez D. High-Data-Rate Modulators Based on Graphene Transistors: Device Circuit Co-Design Proposals. Electronics. 2024; 13(20):4022. https://doi.org/10.3390/electronics13204022

Chicago/Turabian StylePacheco-Sanchez, Anibal, J. Noé Ramos-Silva, Nikolaos Mavredakis, Eloy Ramírez-García, and David Jiménez. 2024. "High-Data-Rate Modulators Based on Graphene Transistors: Device Circuit Co-Design Proposals" Electronics 13, no. 20: 4022. https://doi.org/10.3390/electronics13204022

APA StylePacheco-Sanchez, A., Ramos-Silva, J. N., Mavredakis, N., Ramírez-García, E., & Jiménez, D. (2024). High-Data-Rate Modulators Based on Graphene Transistors: Device Circuit Co-Design Proposals. Electronics, 13(20), 4022. https://doi.org/10.3390/electronics13204022