A 0.5 V Nanowatt Biquadratic Low-Pass Filter with Tunable Quality Factor for Electronic Cochlea Applications

Abstract

1. Introduction

2. Materials and Methods

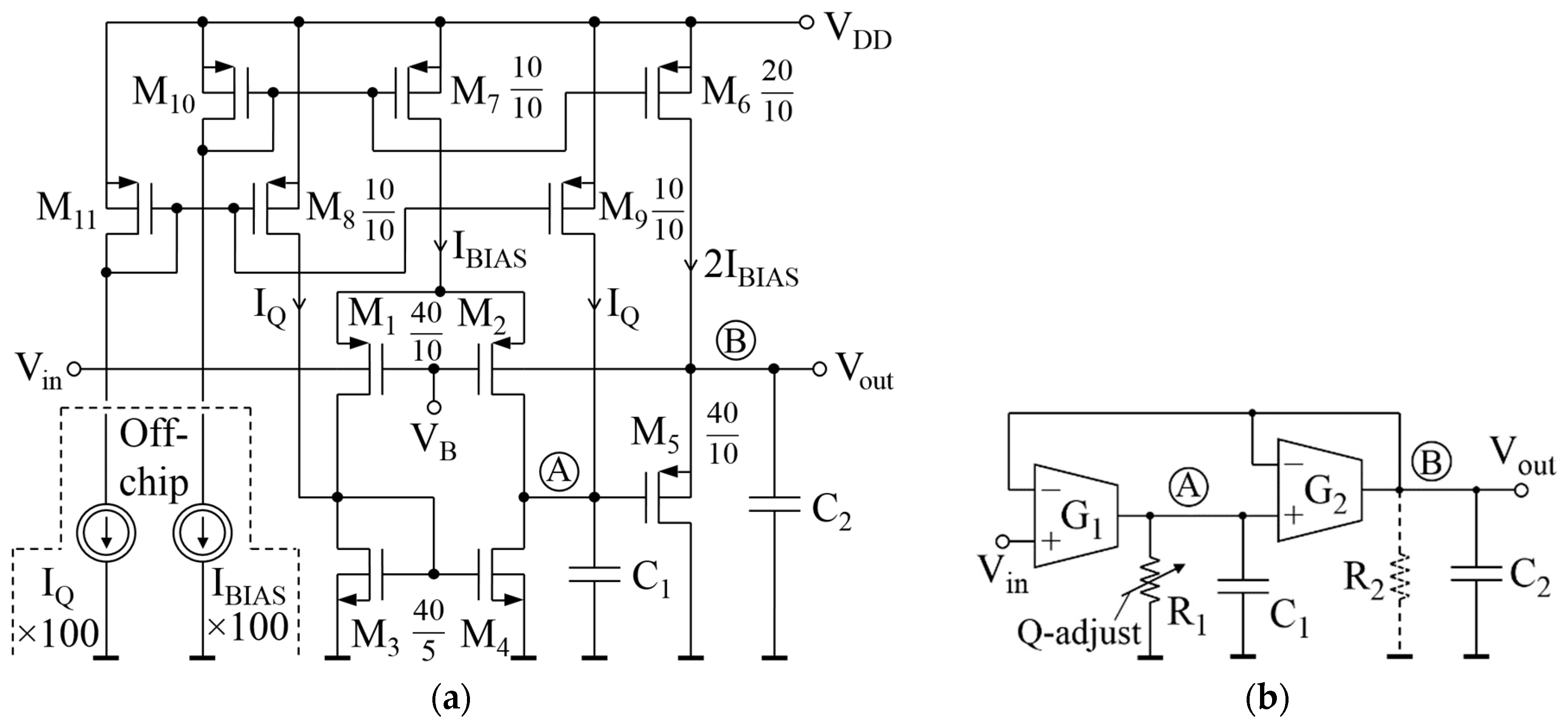

2.1. Principle of Operation

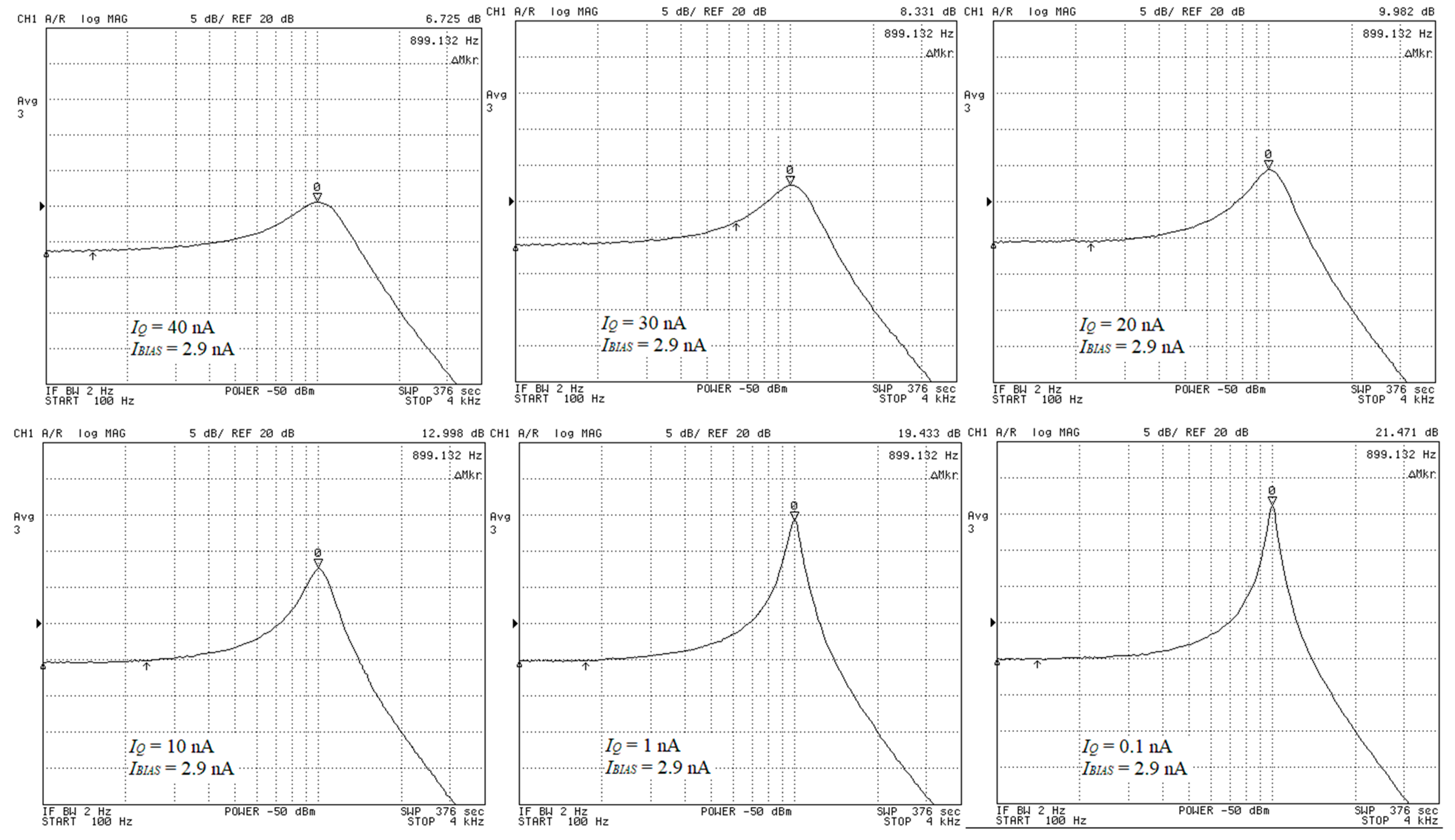

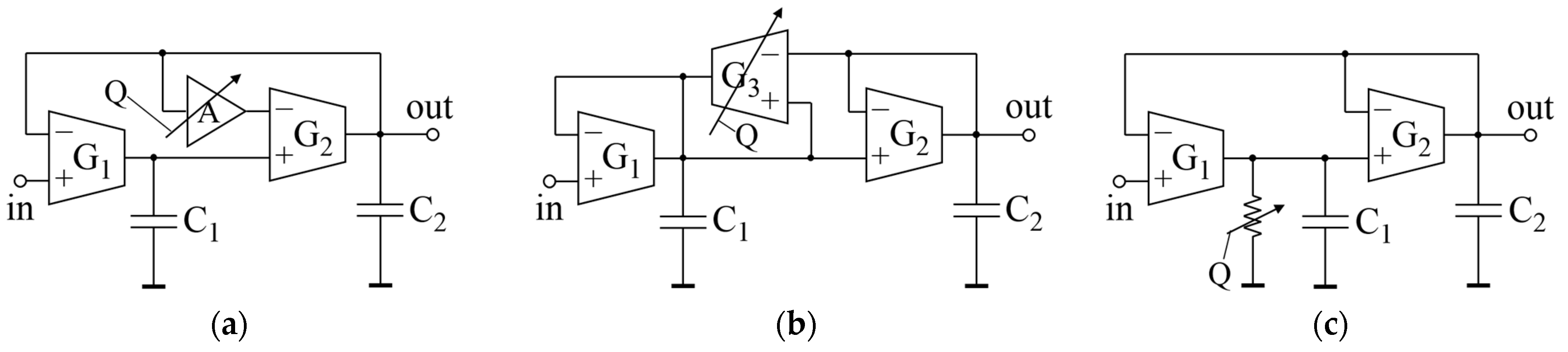

2.2. Q Tuning

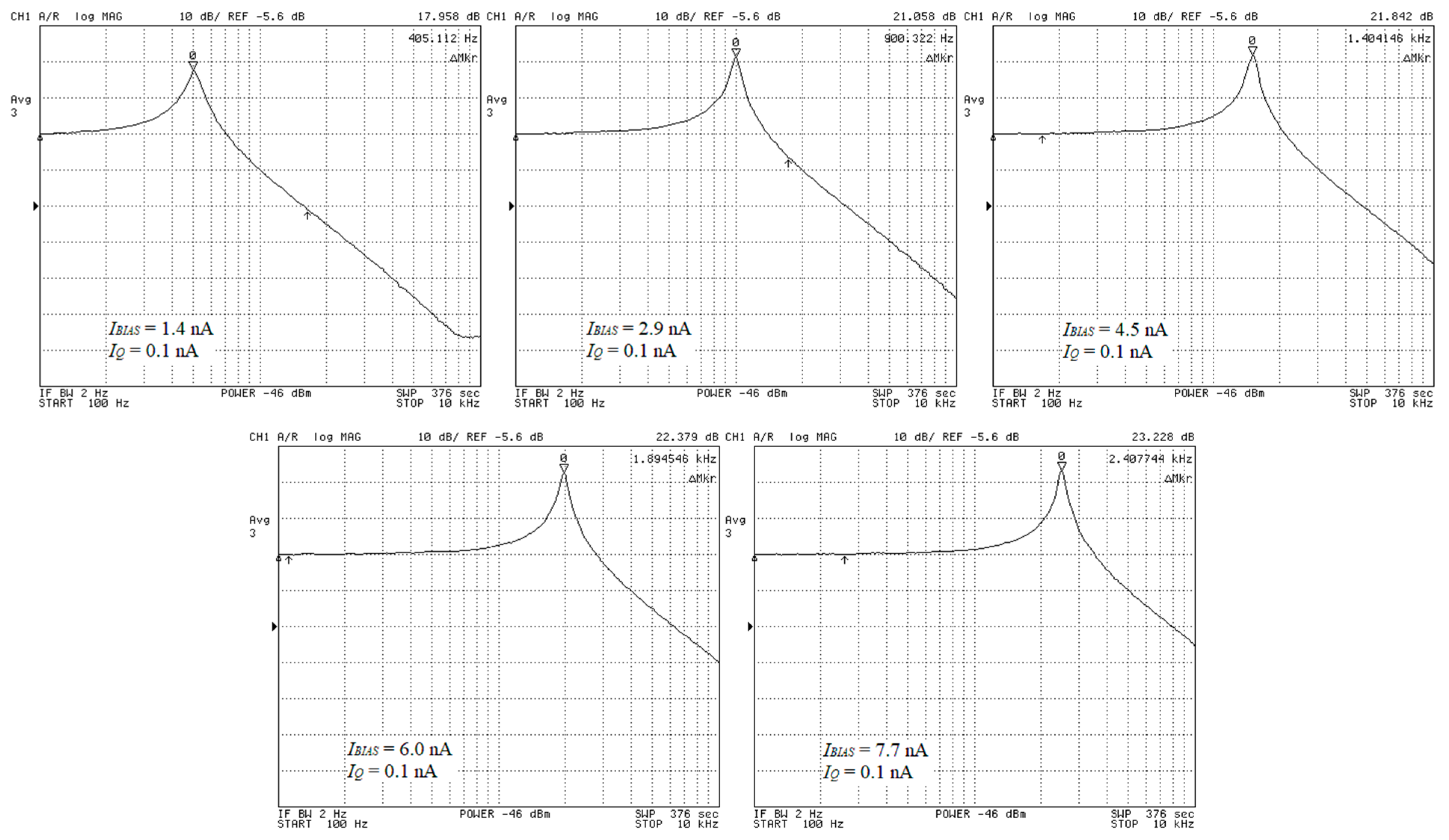

2.3. ω0 Tuning

2.4. Mismatch

2.5. Noise

3. Experiments

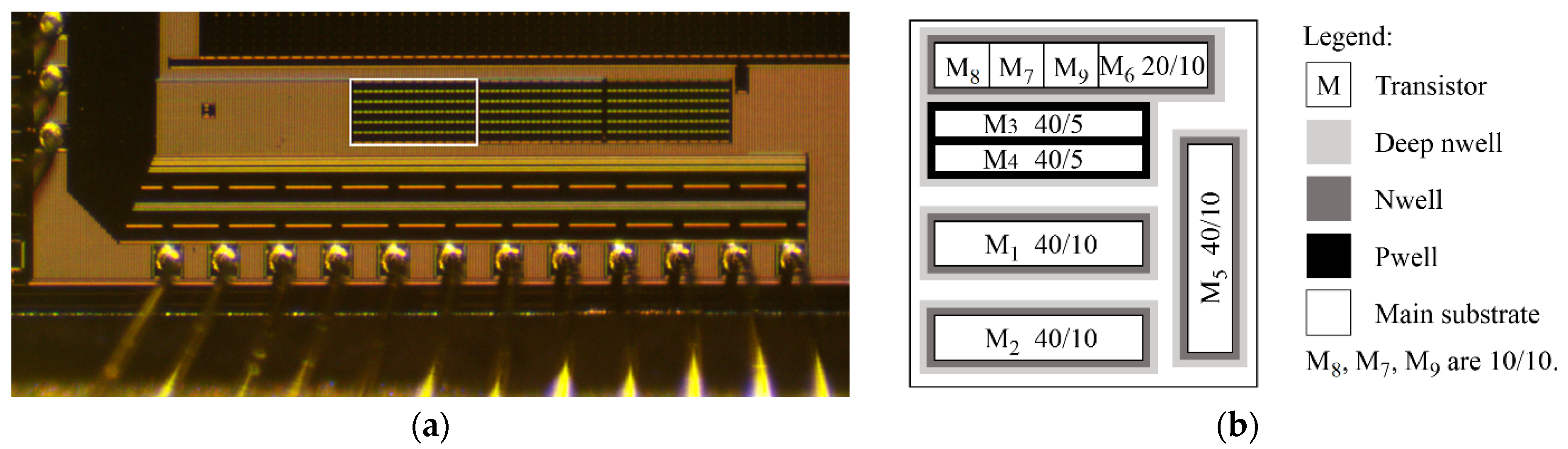

3.1. The Chip and Measurements

3.2. Filter Bank Design Example (Simulations)

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Karrenbauer, J.; Klein, S.; Schönewald, S.; Gerlach, L.; Blawat, M.; Benndorf, J.; Blume, H. SmartHeaP—A High-level Programmable, Low Power, and Mixed-Signal Hearing Aid SoC in 22 nm FD-SOI. In Proceedings of the 48th IEEE European Solid State Circuits Conference, ESSCIRC 2022, Milan, Italy, 19–22 September 2022; pp. 265–268. [Google Scholar] [CrossRef]

- Raychowdhury, A.; Tokunaga, C.; Beltman, W.; Deisher, M.; Tschanz, J.W.; De, V. A 2.3 nJ/frame voice activity detector-based audio front-end for context-aware system-on-chip applications in 32-nm CMOS. IEEE J. Solid-State Circuits 2013, 48, 1963–1969. [Google Scholar] [CrossRef]

- Price, M.; Glass, J.; Chandrakasan, A.P. A 6 mW, 5000-word real-time speech recognizer using WFST models. IEEE J. Solid-State Circuits 2015, 50, 102–112. [Google Scholar] [CrossRef]

- Yang, G.; Lyon, R.F.; Drakakis, E.M. A 6 μW per channel analog biomimetic cochlear implant processor filterbank architecture with across channels AGC. IEEE Trans. Biomed. Circuits Syst. 2015, 9, 72–86. [Google Scholar] [CrossRef] [PubMed]

- Harczos, T.; Chilian, A.; Husar, P. Making use of auditory models for better mimicking of normal hearing processes with cochlear implants: The SAM coding strategy. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 414–425. [Google Scholar] [CrossRef] [PubMed]

- Yip, M.; Jin, R.; Nakajima, H.H.; Stankovic, K.M.; Chandrakasan, A.P. A Fully-Implantable Cochlear Implant SoC With Piezoelectric Middle-Ear Sensor and Arbitrary Waveform Neural Stimulation. IEEE J. Solid-State Circuits 2015, 50, 214–229. [Google Scholar] [CrossRef] [PubMed]

- Russo, M.; Stella, M.; Sikora, M.; Pekić, V. Robust Cochlear-Model-Based Speech Recognition. Computers 2019, 8, 5. [Google Scholar] [CrossRef]

- Ma, T.; Shen, C.; Wei, Y. Adjustable Filter Bank Design for Hearing Aids System. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems, ISCAS 2019, Sapporo, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Wei, Y.; Ma, T.; Ho, B.K.; Lian, Y. The Design of Low-Power 16-Band Nonuniform Filter Bank for Hearing Aids. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 112–123. [Google Scholar] [CrossRef] [PubMed]

- Özbek, B.; Külah, H. A 1-V Nanopower Highly Tunable Biquadratic Gm − C Bandpass Filter for Fully Implantable Cochlear Implants. In Proceedings of the 2021 IEEE Biomedical Circuits and Systems Conference, BioCAS 2021, Berlin, Germany, 6–9 October 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Özbek, B.; Külah, H. A 9.03 µW Low Noise Highly Tunable Analog Front-End for Fully Implantable Cochlear Prosthesis. In Proceedings of the 2022 IEEE Biomedical Circuits and Systems Conference, BioCAS 2022, Taipei, Taiwan, 13–15 October 2022; pp. 349–353. [Google Scholar] [CrossRef]

- Wang, S.; Koickal, T.J.; Hamilton, A.; Cheung, R.; Smith, L.S. A bio-realistic analog CMOS cochlea filter with high tunability and ultra-steep roll-off. IEEE Trans. Biomed. Circuits Syst. 2015, 9, 297–311. [Google Scholar] [CrossRef] [PubMed]

- Sarpeshkar, R.; Salthouse, C.; Sit, J.J.; Baker, M.W.; Zhak, S.M.; Lu, T.T.; Turicchia, L.; Balster, S. An ultra-low-power programmable analog bionic ear processor. IEEE Trans. Biomed. Eng. 2005, 52, 711–727. [Google Scholar] [CrossRef] [PubMed]

- Yang, M.; Chien, C.-H.; Delbruck, T.; Liu, S.-C. A 0.5 V 55 μW 64 × 2 Channel Binaural Silicon Cochlea for Event-Driven Stereo-Audio Sensing. IEEE J. Solid-State Circuits 2016, 51, 2554–2569. [Google Scholar] [CrossRef]

- Lyon, R.F.; Mead, C. An analog electronic cochlea. IEEE Trans. Acoust. Speech Signal Process 1988, 36, 1119–1134. [Google Scholar] [CrossRef]

- Watts, L.; Kerns, D.A.; Lyon, R.F.; Mead, C.A. Improved implementation of the silicon cochlea. IEEE J. Solid-State Circuits 1992, 27, 692–700. [Google Scholar] [CrossRef]

- Sarpeshkar, R.; Lyon, R.F.; Mead, C.A. An analog VLSI cochlea with new transconductance amplifiers and nonlinear gain control. In Proceedings of the 1996 IEEE International Symposium on Circuits and Systems, Circuits and Systems Connecting the World, ISCAS 96, Atlanta, GA, USA, 15 May 1996; Volume 3, pp. 292–296. [Google Scholar] [CrossRef]

- Liu, S.-C.; van Schaik, A.; Minch, B.A.; Delbruck, T. Asynchronous binaural spatial audition sensor with 2 × 64 × 4 channel output. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 453–464. [Google Scholar] [CrossRef] [PubMed]

- Suzuki, Y.; Takeshima, H. Equal-loudness-level contours for pure tones. J. Acoust. Soc. Am. 2004, 116, 918–933. [Google Scholar] [PubMed]

- Ruggero, M.A.; Shyamla Narayan, S.; Temchin, A.N.; Recio, A. Mechanical bases of frequency tuning and neural excitation at the base of the cochlea: Comparison of basilar-membrane vibrations and auditory-nerve-fiber responses in chinchilla. Proc. Natl. Acad. Sci. USA 2000, 97, 11744–11750. [Google Scholar] [CrossRef] [PubMed]

- Alioto, M. Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial. IEEE Tran. Circuits Syst. II Reg. Pap. 2012, 59, 3–29. [Google Scholar] [CrossRef]

- Enz, C.; Krummenacher, F.; Vittoz, E.A. An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. J. Anal. Integr. Circuits Signal Process 1995, 8, 83–114. [Google Scholar] [CrossRef]

- Jendernalik, W.; Jakusz, J.; Blakiewicz, G. Low-Voltage Low-Power Filters with Independent ω0 and Q Tuning for Electronic Cochlea Applications. Electronics 2022, 11, 534. [Google Scholar] [CrossRef]

- Grech, I.; Micallef, J.; Azzopardi, G.; Debono, C.J. A 0.9 V wide-input-range bulk-input CMOS OTA for GM-C filters. In Proceedings of the 10th IEEE International Conference on Electronics, Circuits and Systems, ICECS 2003, Sharjah, United Arab Emirates, 14–17 December 2003; Volume 2, pp. 818–821. [Google Scholar] [CrossRef]

- Jendernalik, W.; Jakusz, J.; Blakiewicz, G. Ladder-Based Synthesis and Design of Low-Frequency Buffer-Based CMOS Filters. Electronics 2021, 10, 2931. [Google Scholar] [CrossRef]

| Parameter | This Work | [23] Simulated | [18] | [12] | [13] | [14] |

|---|---|---|---|---|---|---|

| Process | 0.18 µm | 0.18 µm | 0.35 µm | 0.35 µm | 1.5 µm | 0.18 µm |

| Supply | 0.5 V | 0.5 V | 3.3 V | 3.3 V | 2.8 V | 0.5 V |

| Power | 2.2–52 nW | 8.25–10.75 nW | NA | 13–20 µW 1 | 0.1–5.4 µW | 0.1–100 nW 2 |

| ω0 | 0.5–2.5 kHz | 1.28 kHz | 0.1–20 kHz bank | 0.31–8 kHz bank | 0.2–6 kHz bank | 0.08–20 kHz bank |

| Q | 2–11 | 2–40 | NA | 2–19 | 1–10 | 1.3–39 |

| S/N | 59 dB | 68 dB | 36–52 3 dB | 17–32 dB | 57 dB | 40–55 dB |

| ω0 (kHz) | C2 (pF) | IBIAS (nA) | M 2 | IQ (nA) | P (nW) | ||

|---|---|---|---|---|---|---|---|

| Q = 11.22 (21 dB) | Q = 5.01 (14 dB) | Q = 11.22 (21 dB) | Q = 5.01 (14 dB) | ||||

| 0.5 | 60 | 1.42 | 1 | 0.025 | 1.54 | 2.155 | 3.67 |

| 1 | 60 | 2.93 | 1 | 0.136 | 3.1 | 4.531 | 7.495 |

| 2 | 30 | 6.01 | 2 | 0.453 | 6.2 | 9.468 | 15.215 |

| 4 | 15 | 9.12 | 2 | 0.198 | 5.83 | 13.878 | 19.51 |

| 8 | 7.5 | 9.4 | 2 | 0.055 | 5.95 | 14.155 | 20.05 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jakusz, J.; Jendernalik, W. A 0.5 V Nanowatt Biquadratic Low-Pass Filter with Tunable Quality Factor for Electronic Cochlea Applications. Electronics 2024, 13, 399. https://doi.org/10.3390/electronics13020399

Jakusz J, Jendernalik W. A 0.5 V Nanowatt Biquadratic Low-Pass Filter with Tunable Quality Factor for Electronic Cochlea Applications. Electronics. 2024; 13(2):399. https://doi.org/10.3390/electronics13020399

Chicago/Turabian StyleJakusz, Jacek, and Waldemar Jendernalik. 2024. "A 0.5 V Nanowatt Biquadratic Low-Pass Filter with Tunable Quality Factor for Electronic Cochlea Applications" Electronics 13, no. 2: 399. https://doi.org/10.3390/electronics13020399

APA StyleJakusz, J., & Jendernalik, W. (2024). A 0.5 V Nanowatt Biquadratic Low-Pass Filter with Tunable Quality Factor for Electronic Cochlea Applications. Electronics, 13(2), 399. https://doi.org/10.3390/electronics13020399