Multi-View Graph Learning for Path-Level Aging-Aware Timing Prediction

Abstract

1. Introduction

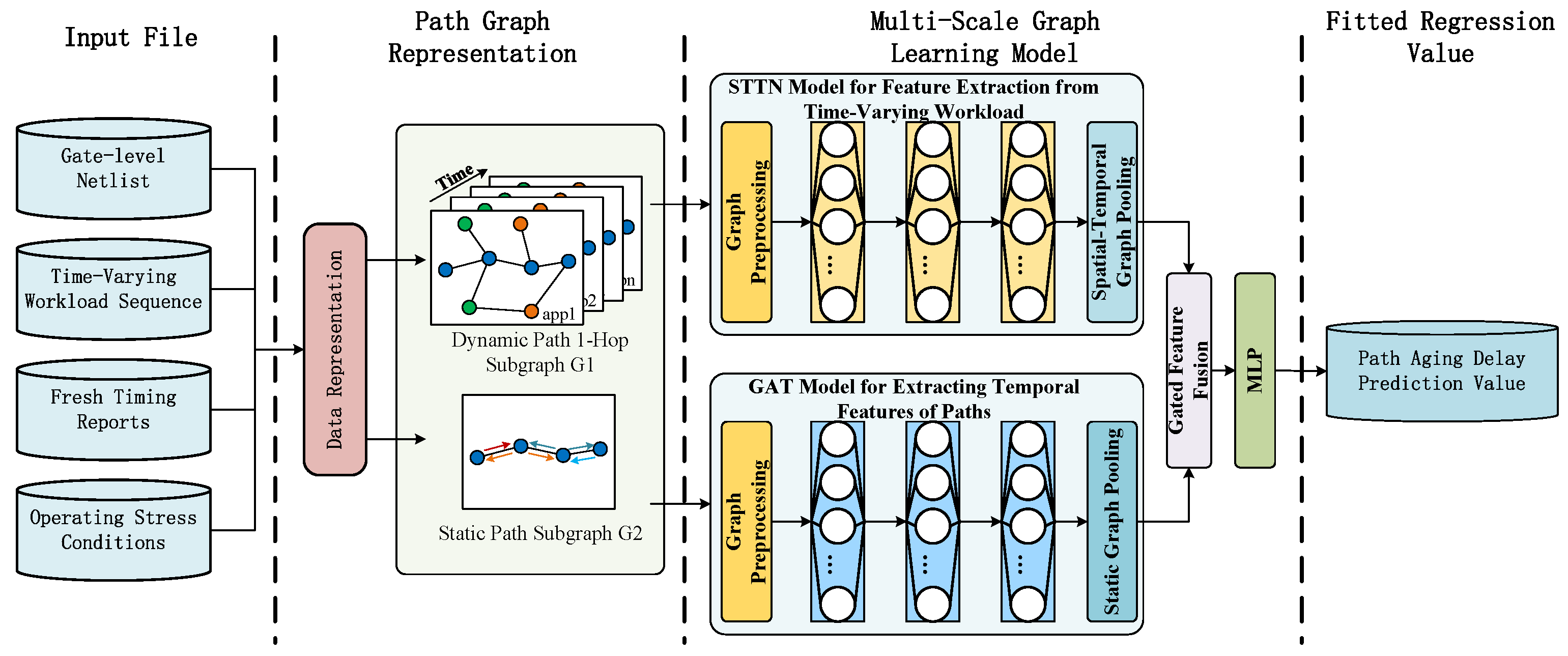

- We have implemented an end-to-end aging-aware path time prediction framework based on multi-view graph learning, achieving a tradeoff between efficiency and accuracy.

- We customize a STTN-GAT model to improve the model’s expressing ability and reduce the over-smoothing issues.

- The prediction accuracy and runtime of our model has been validated on multiple industrial designs.

2. Related Works

2.1. Existing Approaches for Aging-Aware Timing Modeling

2.1.1. Aging-Aware SPICE Simulation

2.1.2. Aging-Aware STA

2.2. Frontier Machine Learning Techniques for Timing Prediction

3. Preliminaries

3.1. NBTI Degradation

3.2. Graph Neural Networks

3.3. Transformer Network

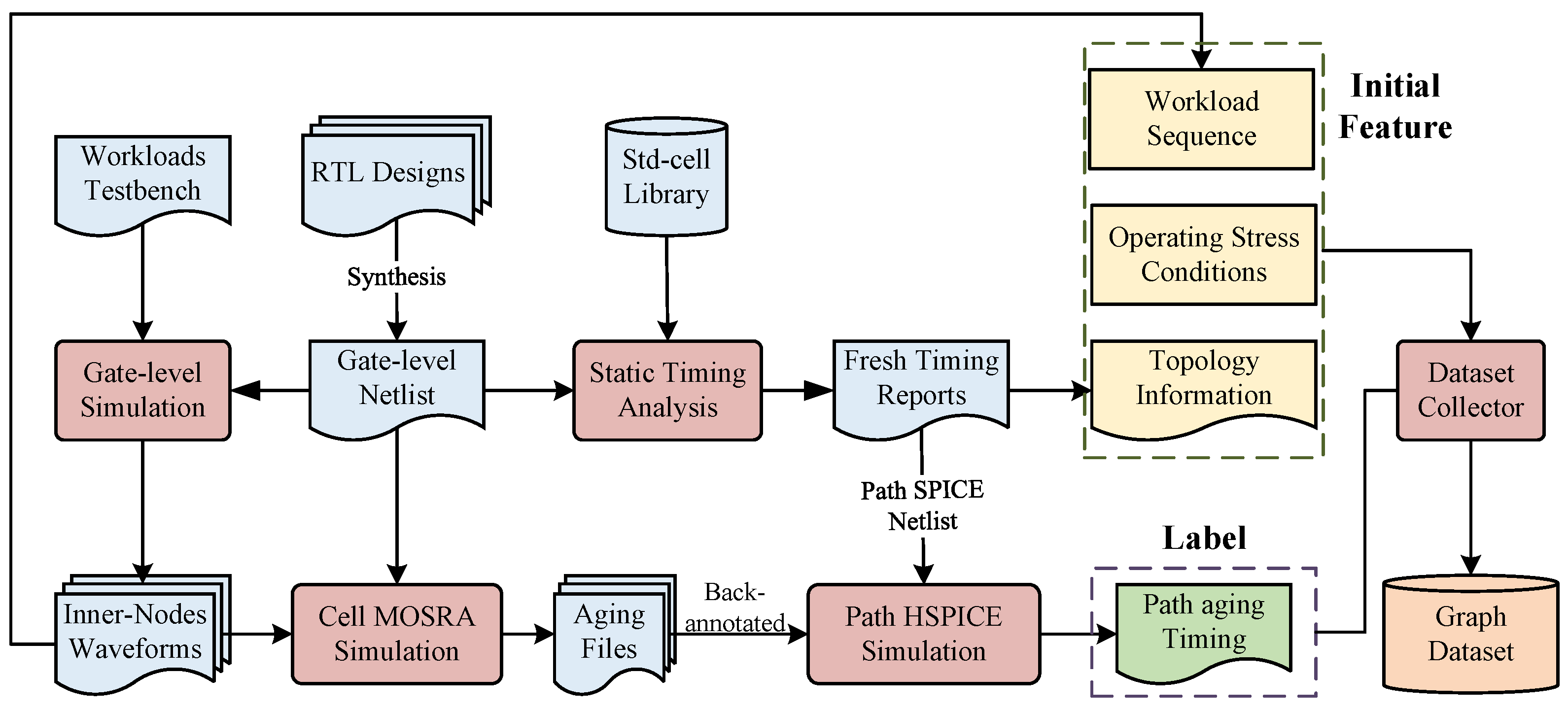

4. Aging-Aware Timing Prediction Model

4.1. Overview

4.2. Spatial–Temporal Transformer Network Design for Workload Features

4.2.1. Graph Representation and Workload Features

4.2.2. Spatial–Temporal Embedding

4.2.3. Spatial–Temporal Transformer Model

| Algorithm 1 Dynamic path 1-hop subgraph overall representation |

|

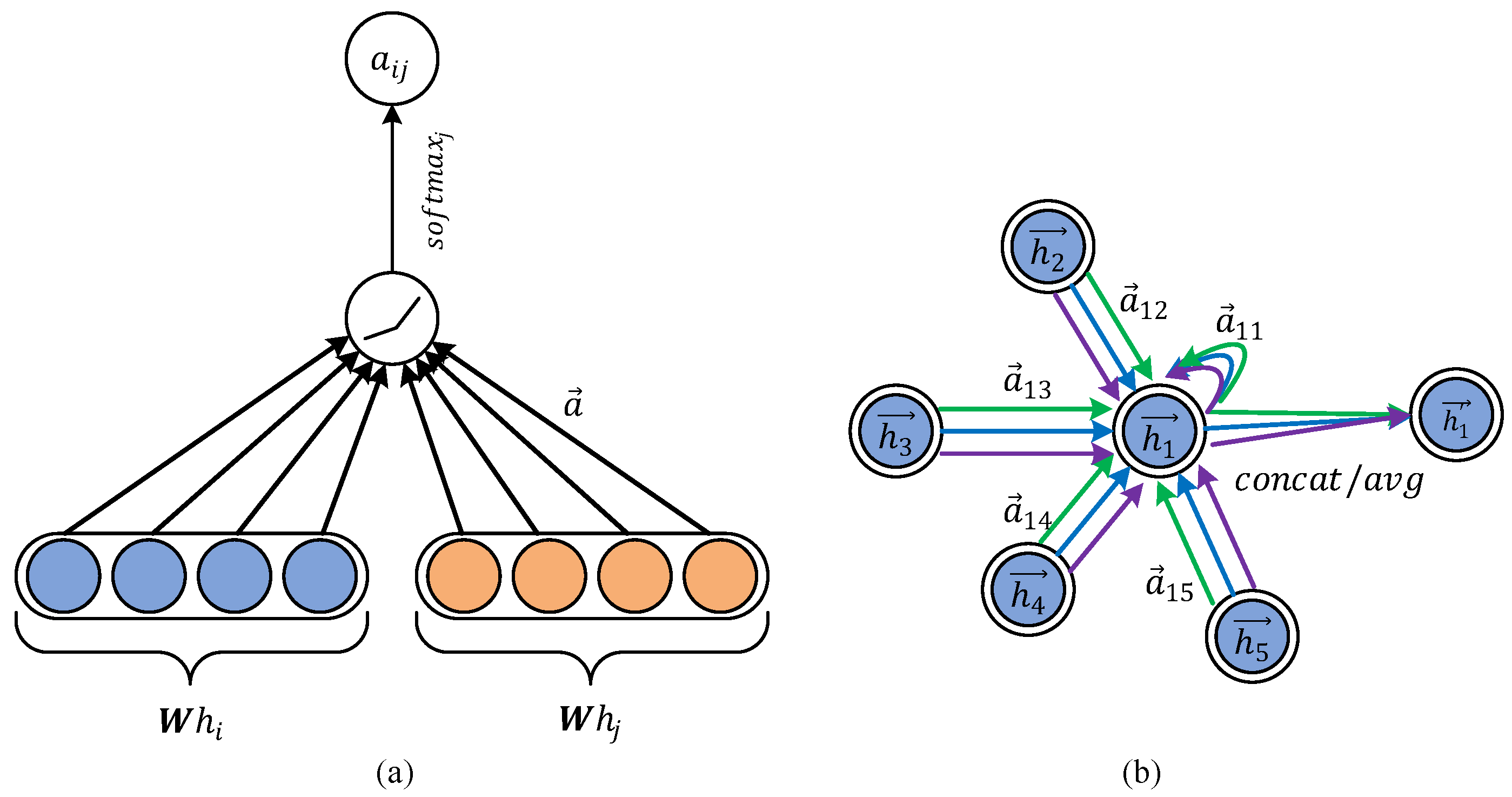

4.3. Graph Attention Networks Design for Path Timing Features

4.3.1. Graph Representation and Timing Features

4.3.2. Graph Attention Model

5. Experimental Result

5.1. Experiment Setup

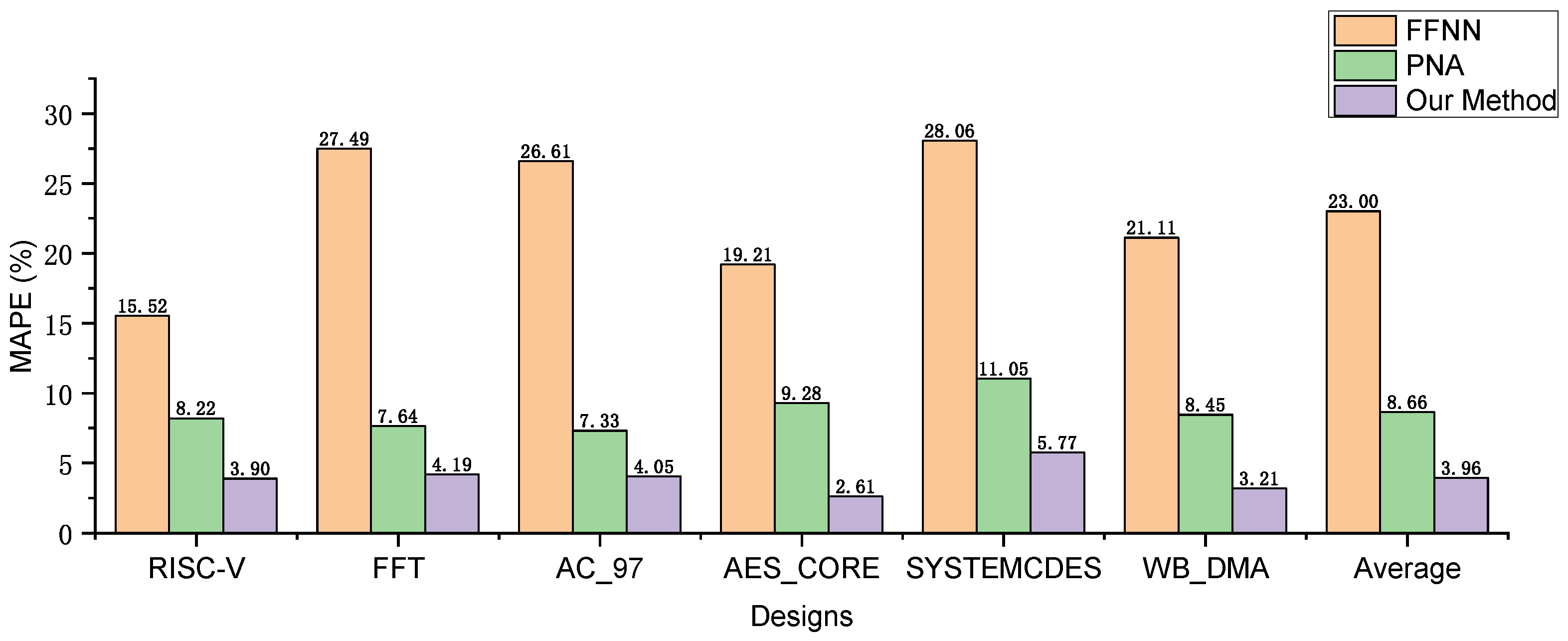

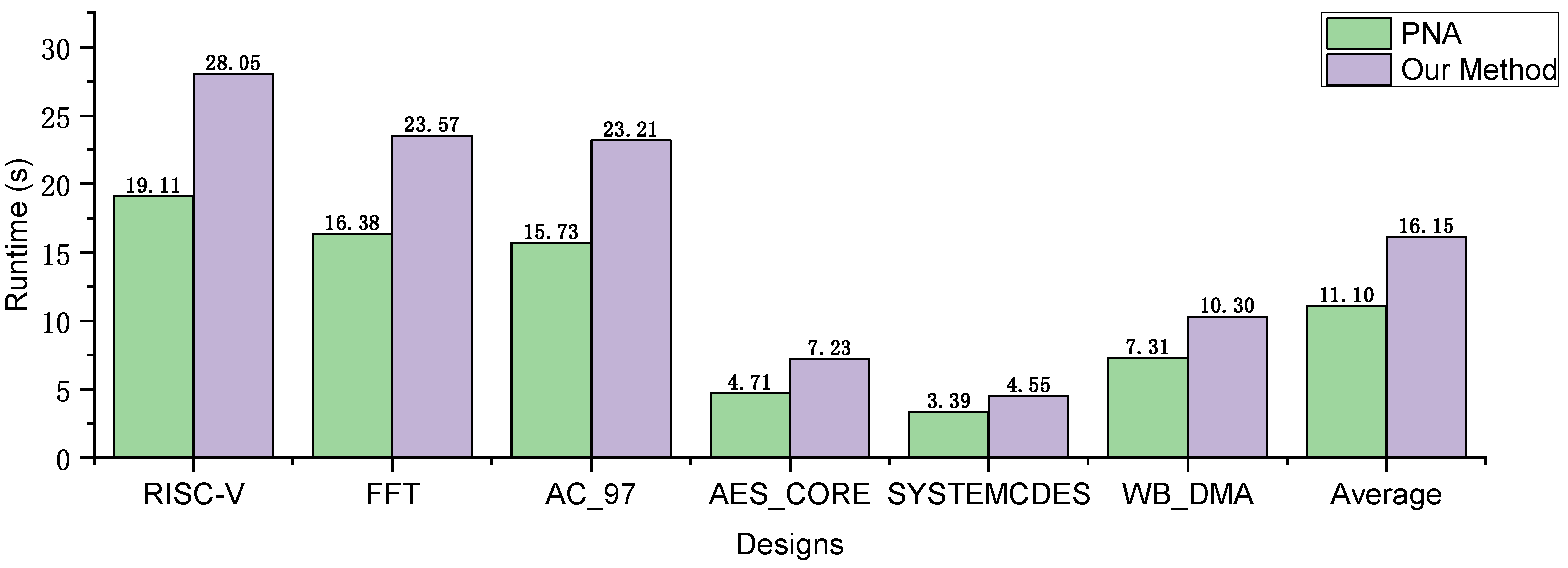

5.2. Results and Comparison

5.2.1. Ablation Experiment

5.2.2. Comparison with Existing Models

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Hill, I.; Chanawala, P.; Singh, R.; Sheikholeslam, S.A.; Ivanov, A. CMOS Reliability From Past to Future: A Survey of Requirements, Trends, and Prediction Methods. IEEE Trans. Device Mater. Relib. 2022, 22, 1–18. [Google Scholar] [CrossRef]

- Kim, S.; Park, H.; Choi, E.; Kim, Y.H.; Kim, D.; Shim, H.; Chung, S.; Jung, P. Reliability Assessment of 3nm GAA Logic Technology Featuring Multi-Bridge-Channel FETs. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–8. [Google Scholar]

- Yasuda-Masuoka, Y.; Jeong, J.; Son, K.; Lee, S.; Park, S.; Lee, Y.; Youn Kim, J.; Lee, J.; Cho, M.; Lee, S.; et al. High Performance 4nm FinFET Platform (4LPE) with Novel Advanced Transistor Level DTCO for Dual-CPP/HP-HD Standard Cells. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11 December 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 13.3.1–13.3.4. [Google Scholar]

- Mishra, S.; Weckx, P.; Zografos, O.; Lin, J.Y.; Spessot, A.; Catthoor, F. Overhead Reduction with Optimal Margining Using A Reliability Aware Design Paradigm. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 1–7. [Google Scholar]

- Tu, R.H.; Rosenbaum, E.; Chan, W.Y.; Li, C.C.; Minami, E.; Quader, K.; Ko, P.K.; Hu, C. Berkeley Reliability Tools-BERT. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1993, 12, 1524–1534. [Google Scholar] [CrossRef]

- Thirunavukkarasu, A.; Amrouch, H.; Joe, J.; Goel, N.; Parihar, N.; Mishra, S.; Dabhi, C.K.; Chauhan, Y.S.; Henkel, J.; Mahapatra, S. Device to Circuit Framework for Activity-Dependent NBTI Aging in Digital Circuits. IEEE Trans. Electron. Devices 2019, 66, 316–323. [Google Scholar] [CrossRef]

- Wang, L.; Dernoncourt, F.; Bui, T. Bayesian Optimization for Selecting Efficient Machine Learning Models. arXiv 2020, arXiv:2008.00386. [Google Scholar]

- Jamhiri, B.; Xu, Y.; Shadabfar, M.; Costa, S. Probabilistic Machine Learning for Predicting Desiccation Cracks in Clayey Soils. Bull. Eng. Geol. Environ. 2023, 82, 355. [Google Scholar] [CrossRef]

- Meng, C.; Xie, S.; Liu, L.; Wei, P.; Tang, Y.; Zhang, Y. Regional PM2.5 Concentration Prediction Analysis and Spatio-Temporal Mapping Incorporating ZWD Data. Atmos. Pollut. Res. 2024, 15, 102028. [Google Scholar] [CrossRef]

- Guo, Z.; Liu, M.; Gu, J.; Zhang, S.; Pan, D.Z.; Lin, Y. A Timing Engine Inspired Graph Neural Network Model for Pre-Routing Slack Prediction. In Proceedings of the 59th ACM/IEEE Design Automation Conference, San Francisco, CA, USA, 10 July 2022; ACM: New York, NY, USA, 2022; pp. 1207–1212. [Google Scholar]

- Xie, Z.; Liang, R.; Xu, X.; Hu, J.; Chang, C.-C.; Pan, J.; Chen, Y. Preplacement Net Length and Timing Estimation by Customized Graph Neural Network. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2022, 41, 4667–4680. [Google Scholar] [CrossRef]

- Shrestha, P.; Phatharodom, S.; Savidis, I. Graph Representation Learning for Gate Arrival Time Prediction. In Proceedings of the 2022 ACM/IEEE 4th Workshop on Machine Learning for CAD (MLCAD), Snowbird, UT, USA, 12 September 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 127–133. [Google Scholar]

- Bian, S.; Shintani, M.; Morita, S.; Hiromoto, M.; Sato, T. Nonlinear Delay-Table Approach for Full-Chip NBTI Degradation Prediction. In Proceedings of the 2016 17th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 15–16 March 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 307–312. [Google Scholar]

- Amrouch, H.; Khaleghi, B.; Gerstlauer, A.; Henkel, J. Reliability-Aware Design to Suppress Aging. In Proceedings of the 53rd Annual Design Automation Conference, Austin, TX, USA, 5 June 2016; ACM: New York, NY, USA, 2016; pp. 1–6. [Google Scholar]

- Zhang, X.; Zhang, Z.; Lin, Y.; Ji, Z.; Wang, R.; Huang, R. Efficient Aging-Aware Standard Cell Library Characterization Based on Sensitivity Analysis. IEEE Trans. Circuits Syst. II 2023, 70, 721–725. [Google Scholar] [CrossRef]

- Ebrahimipour, S.M.; Ghavami, B.; Mousavi, H.; Raji, M.; Fang, Z.; Shannon, L. Aadam: A Fast, Accurate, and Versatile Aging-Aware Cell Library Delay Model Using Feed-Forward Neural Network. In Proceedings of the 2020 IEEE/ACM International Conference On Computer Aided Design (ICCAD), San Diego, CA, USA, 2–5 November 2020; ACM: New York, NY, USA, 2020; pp. 1–9. [Google Scholar]

- Ye, Y.; Chen, T.; Wang, Z.; Yan, H.; Yu, B.; Shi, L. Fast and Accurate Aging-Aware Cell Timing Model via Graph Learning. IEEE Trans. Circuits Syst. II 2024, 71, 156–160. [Google Scholar] [CrossRef]

- Synopsys, Inc. PrimeLib: Unified Library Characterization and Validation. [Online]. 2024. Available online: https://www.synopsys.com/implementation-and-signoff/signoff/primelib.html (accessed on 13 June 2024).

- Yang, T.; He, G.; Cao, P. Pre-Routing Path Delay Estimation Based on Transformer and Residual Framework. In Proceedings of the 2022 27th Asia and South Pacific Design Automation Conference (ASP-DAC), Taipei, Taiwan, 17 January 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 184–189. [Google Scholar]

- Ye, Y.; Chen, T.; Gao, Y.; Yan, H.; Yu, B.; Shi, L. Fast and Accurate Wire Timing Estimation Based on Graph Learning. In Proceedings of the 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium, 17–19 April 2023; IEEE: Piscataway, NJ, USA, 2023; pp. 1–6. [Google Scholar]

- Ye, Y.; Chen, T.; Gao, Y.; Yan, H.; Yu, B.; Shi, L. Graph-Learning-Driven Path-Based Timing Analysis Results Predictor from Graph-Based Timing Analysis. In Proceedings of the 28th Asia and South Pacific Design Automation Conference, Tokyo, Japan, 16 January 2023; ACM: New York, NY, USA, 2023; pp. 547–552. [Google Scholar]

- Alrahis, L.; Knechtel, J.; Klemme, F.; Amrouch, H.; Sinanoglu, O. GNN4REL: Graph Neural Networks for Predicting Circuit Reliability Degradation. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2022, 41, 3826–3837. [Google Scholar] [CrossRef]

- Ye, Y.; Chen, T.; Gao, Y.; Yan, H.; Yu, B.; Shi, L. Aging-Aware Critical Path Selection via Graph Attention Networks. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2023, 42, 5006–5019. [Google Scholar] [CrossRef]

- Liu, J.C.; Mukhopadhyay, S.; Kundu, A.; Chen, S.H.; Wang, H.C.; Huang, D.S.; Lee, J.H.; Wang, M.I.; Lu, R.; Lin, S.S.; et al. A Reliability Enhanced 5nm CMOS Technology Featuring 5 th Generation FinFET with Fully-Developed EUV and High Mobility Channel for Mobile SoC and High Performance Computing Application. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12 December 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 9.2.1–9.2.4. [Google Scholar]

- Fan, A.; Wang, J.; Aptekar, V. Advanced Circuit Reliability Verification for Robust Design. In Proceedings of the 2019 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–8. [Google Scholar]

- Lee, W.-K.; Huang, K.; Hsu, L.C.; Huang, C.; Liang, J.; Chen, J.; Hsiao, C.; Su, K.-W.; Lin, C.-K.; Jeng, M.-C. A Unified Aging Model with Recovery Effect and Its Impact on Circuit Design. In Proceedings of the 2017 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Kamakura, Japan, 7–9 September 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 93–96. [Google Scholar]

- Rezazadeh, N.; De Luca, A.; Perfetto, D. Unbalanced, Cracked, and Misaligned Rotating Machines: A Comparison between Classification Procedures throughout the Steady-State Operation. J. Braz. Soc. Mech. Sci. Eng. 2022, 44, 450. [Google Scholar] [CrossRef]

- Dwivedi, V.P.; Joshi, C.K.; Luu, A.T.; Laurent, T.; Bengio, Y.; Bresson, X. Benchmarking Graph Neural Networks. J. Mach. Learn. Res. 2024, 24. [Google Scholar] [CrossRef]

- Kreuzer, D.; Beaini, D.; Hamilton, W.L.; Létourneau, V.; Tossou, P. Rethinking Graph Transformers with Spectral Attention. In Proceedings of the 35th International Conference on Neural Information Processing Systems, Online, 6–14 December 2024; Curran Associates Inc.: Red Hook, NY, USA, 2024. [Google Scholar]

- Wu, Z.; Pan, S.; Long, G.; Jiang, J.; Zhang, C. Graph Wavenet for Deep Spatial-Temporal Graph Modeling. In Proceedings of the 28th International Joint Conference on Artificial Intelligence, Macao, China, 10–16 August 2019; AAAI Press: Washington, DC, USA, 2019; pp. 1907–1913. [Google Scholar]

| Type | Name | Description | Dimension |

|---|---|---|---|

| Node | cell_func | one-hot encoded cell type | 8 |

| drive_strength | drive strength of cell | 1 | |

| wst_output_slack | worst slack of output pins | 1 | |

| wst_input_slack | worst slack of input pins | 1 | |

| max_input_slew | maximum slew of input pins | 1 | |

| max_output_slew | maximum slew of output pins | 1 | |

| tot_input_cap | total capacitance of input pins | 1 | |

| input_wst_sp | worst signal probability of input pins | 1 | |

| output_sp | signal probability of output pins | 1 | |

| Global | op_temp | operation temperature | 1 |

| op_voltage | operation voltage | 1 | |

| op_time | operation time range | 1 |

| Type | Name | Description | Dimension |

|---|---|---|---|

| Node | cell_func | one-hot encoded cell type | 8 |

| drive_strength | drive strength of cell | 1 | |

| in_trans | transition time of input pins | 1 | |

| in_type | transition type of input pins | 1 | |

| out_trans | transition time of output pins | 1 | |

| cell_delay | cell delay | 1 | |

| cell_cap | cell load capacitance | 1 | |

| fanout | cell fanout number | 1 | |

| Global | path_delay | fresh path delay | 1 |

| path_depth | path depth | 1 |

| Design | #Cells | #FFs | #Train Paths | #Test Paths | |

|---|---|---|---|---|---|

| Known | RISC-V | 154,912 | 9829 | 10,385 | 2596 |

| FFT | 102,226 | 9922 | 11,191 | 2238 | |

| Unknow | AC_97 | 12,787 | 2229 | 0 | 2129 |

| AES_CORE | 16,424 | 530 | 0 | 659 | |

| SYSTEMCDES | 2258 | 190 | 0 | 445 | |

| WB_DMA | 4573 | 611 | 0 | 921 | |

| Design | R2Score/MAPE (%) | |||||

|---|---|---|---|---|---|---|

| Ma | Mb | Mc | Md | M | ||

| Known | RISC-V | 0.846/7.84 | 0.909/5.12 | 0.922/5.04 | 0.942/4.93 | 0.974/3.90 |

| FFT | 0.850/5.87 | 0.914/4.43 | 0.938/5.14 | 0.973/4.67 | 0.981/4.19 | |

| Unknow | AC_97 | 0.910/6.09 | 0.916/4.97 | 0.952/4.92 | 0.962/4.72 | 0.992/4.05 |

| AES_CORE | 0.811/10.27 | 0.908/4.83 | 0.948/3.30 | 0.968/4.06 | 0.991/2.61 | |

| SYSTEMCDES | 0.865/11.48 | 0.919/5.71 | 0.909/6.15 | 0.949/6.06 | 0.962/5.77 | |

| WB_DMA | 0.830/9.26 | 0.916/5.29 | 0.927/3.84 | 0.964/3.766 | 0.986/3.21 | |

| Average | 0.852/8.468 | 0.914/5.083 | 0.933/4.732 | 0.959/4.701 | 0.981/3.955 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bu, A.; Li, X.; Li, Z.; Chen, Y. Multi-View Graph Learning for Path-Level Aging-Aware Timing Prediction. Electronics 2024, 13, 3479. https://doi.org/10.3390/electronics13173479

Bu A, Li X, Li Z, Chen Y. Multi-View Graph Learning for Path-Level Aging-Aware Timing Prediction. Electronics. 2024; 13(17):3479. https://doi.org/10.3390/electronics13173479

Chicago/Turabian StyleBu, Aiguo, Xiang Li, Zeyu Li, and Yizhen Chen. 2024. "Multi-View Graph Learning for Path-Level Aging-Aware Timing Prediction" Electronics 13, no. 17: 3479. https://doi.org/10.3390/electronics13173479

APA StyleBu, A., Li, X., Li, Z., & Chen, Y. (2024). Multi-View Graph Learning for Path-Level Aging-Aware Timing Prediction. Electronics, 13(17), 3479. https://doi.org/10.3390/electronics13173479