An Analog Delay-Locked Loop with Digital Coarse Lock Incorporating Error Compensation for Fast and Robust Locking

Abstract

1. Introduction

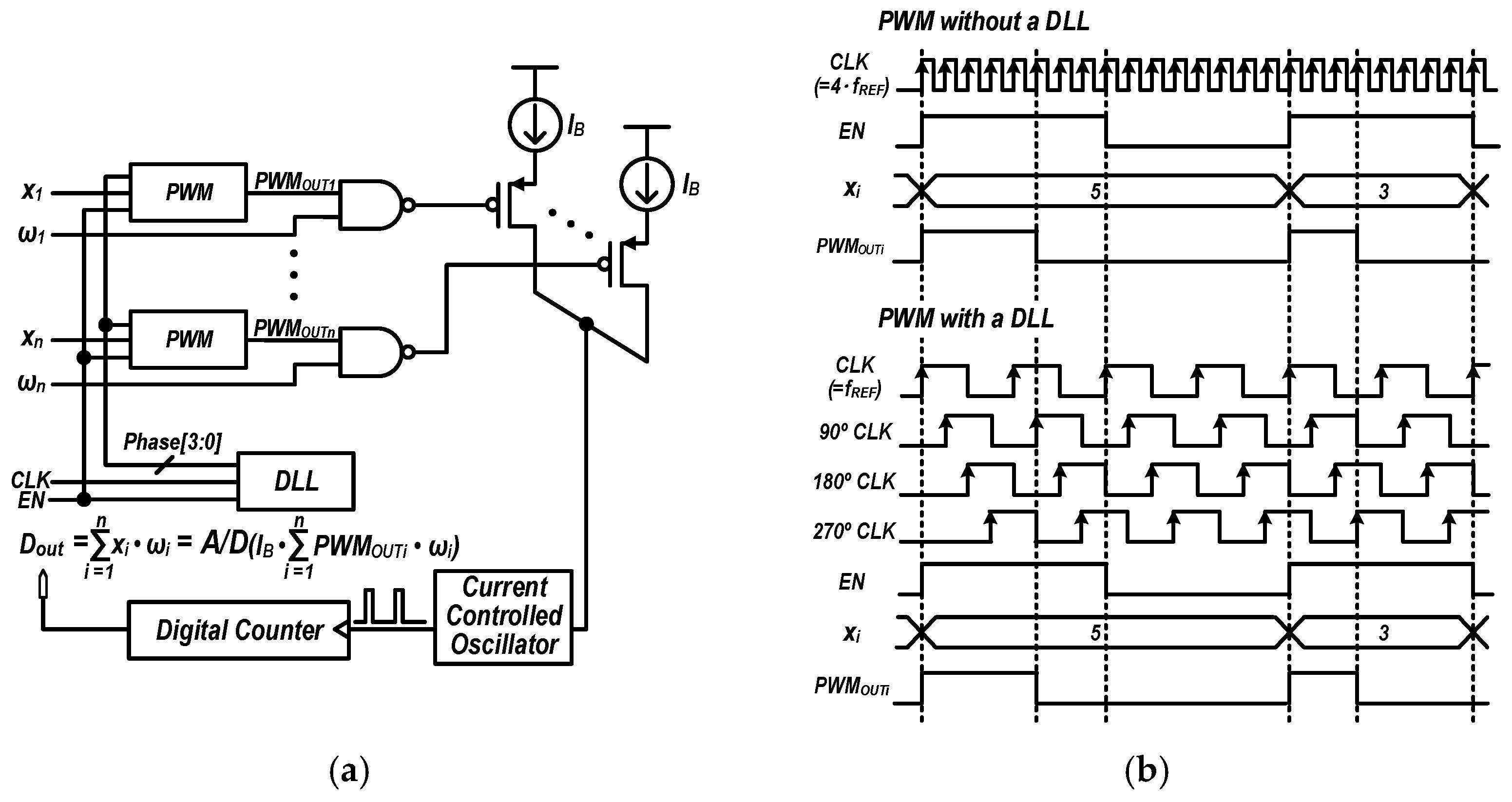

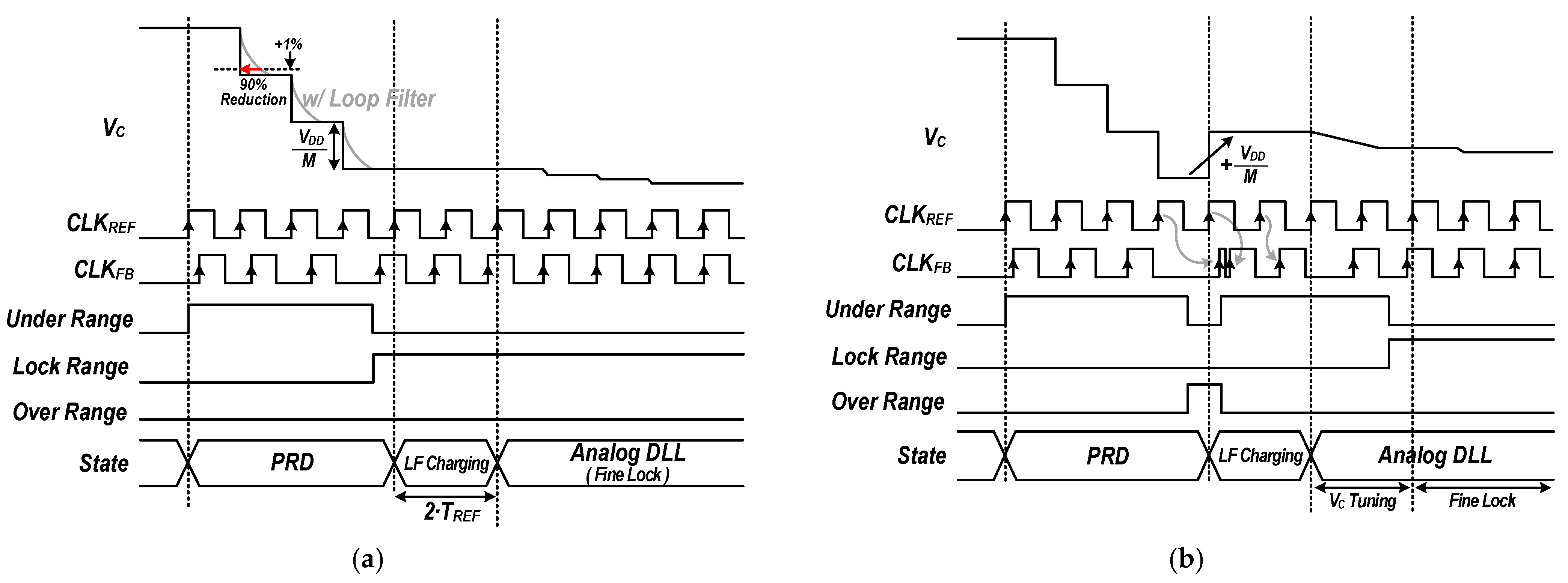

2. Architecture

3. Circuit Implementation

3.1. Phase Range Detector

3.2. DAC, Auto-Zero Buffer, and Voltage-Boosting Circuits (VBCs)

3.3. Self-Resetting Phase Detector

3.4. Digital Building Blocks

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Cho, H.; Son, H.; Seong, K.; Kim, B.; Park, H.-J.; Sim, J.-Y. An On-Chip Learning Neuromorphic Autoencoder with Current-Mode Transposable Memory Read and Virtual Lookup Table. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 161–170. [Google Scholar] [CrossRef] [PubMed]

- Son, H.; Cho, H.; Lee, J.; Bae, S.; Kim, B.; Park, H.-J.; Sim, J.-Y. A Multilayer-Learning Current-Mode Neuromorphic System with Analog-Error Compensation. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 986–998. [Google Scholar] [CrossRef] [PubMed]

- Kim, Y.; Jin, H.; Kim, D.; Ha, P.; Park, M.-K.; Hwang, J.; Lee, J.; Woo, J.-M.; Choi, J.; Lee, C.; et al. Design of Synaptic Driving Circuit for TFT eFlash-Based Processing-In-Memory Hardware Using Hybrid Bonding. Electronics 2023, 12, 678. [Google Scholar] [CrossRef]

- Kim, S.; Jeong, D.-K.; Choi, Y.; Lim, H.K. A 960-Mb/s/pin Interface for Skew-Tolerant Bus Using Low Jitter PLL. IEEE J. Solid-State Circuits 1997, 32, 691–700. [Google Scholar]

- Sun, L.; Kwasniewski, T.A. A 1.25-GHz 0.35-μm monolithic CMOS PLL based on a multiphase ring oscillator. IEEE J. Solid-State Circuits 2001, 36, 910–916. [Google Scholar]

- Moon, Y.; Choi, J.; Lee, K.; Jeong, D.-K.; Kim, M.-K. An All-Analog Multiphase Delay-Locked Loop Using a Replica Delay Line for Wide-Range Operation and Low-Jitter Performance. IEEE J. Solid-State Circuits 2000, 35, 377–384. [Google Scholar] [CrossRef]

- Chang, H.-H.; Lin, J.-W.; Yang, C.-Y.; Liu, S.-I. A Wide-Range Delay-Locked Loop with a Fixed Latency of One Clock Cycle. IEEE J. Solid-State Circuits 2002, 37, 1021–1027. [Google Scholar] [CrossRef]

- Chang, H.-H.; Lin, J.-W.; Liu, S.-I. A fast locking and low jitter delay-locked loop using DHDL. IEEE J. Solid-State Circuits 2003, 38, 343–346. [Google Scholar] [CrossRef]

- Bae, S.-J.; Chi, H.-J.; Sohn, Y.-S.; Park, H.-J. A VCDL-Based 60–760-MHz Dual-Loop DLL with Infinite Phase-Shift Capability and Adaptive-Bandwidth Scheme. IEEE J. Solid-State Circuits 2005, 40, 1119–1129. [Google Scholar]

- Cheng, K.-H.; Lo, Y.-L. A Fast-Lock Wide-Range Delay-Locked Loop Using Frequency-Range Selector for Multiphase Clock Generator. IEEE Trans. Circuits Syst. II 2007, 54, 561–565. [Google Scholar] [CrossRef]

- Moon, Y.-H.; Kong, I.-S.; Ryu, Y.-S.; Kang, J.-K. A 2.2-mW 20–135-MHz False-Lock-Free DLL for Display Interface in 0.15-μm CMOS. IEEE Trans. Circuits Syst. II 2014, 61, 554–558. [Google Scholar]

- Dehng, G.-K.; Lin, J.-W.; Liu, S.-I. A Fast-Lock Mixed-Mode DLL Using a 2-b SAR Algorithm. IEEE J. Solid-State Circuits 2001, 36, 1464–1471. [Google Scholar] [CrossRef]

- Ryu, K.; Jung, D.-H.; Jung, S.-O. A DLL with Dual Edge Triggered Phase Detector for Fast Lock and Low Jitter Clock Generator. IEEE Trans. Circuits Syst. I 2012, 59, 1860–1870. [Google Scholar] [CrossRef]

- Chuang, C.-N.; Liu, S.-I. A 0.5–5-GHz Wide-Range Multiphase DLL with a Calibrated Charge Pump. IEEE Trans. Circuits Syst. II 2007, 54, 939–943. [Google Scholar] [CrossRef]

- Lee, K.-W.; Cho, J.-H.; Choi, B.-J.; Lee, G.-I.; Jung, H.-D.; Lee, W.-Y.; Park, K.-C.; Joo, Y.-S.; Cha, J.-H.; Choi, Y.-J.; et al. A 1.5-V 3.2 Gb/s/pin Graphic DDR4 SDRAM with Dual-Clock System, Four-Phase Input Strobing, and Low-Jitter Fully Analog DLL. IEEE J. Solid-State Circuits 2007, 42, 2369–2377. [Google Scholar] [CrossRef]

- Kuo, C.-H.; Lai, H.-J.; Lin, M.-F. A Multi-Band Fast-Locking Delay-Locked Loop with Jitter-Bounded Feature. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2011, 58, 51–59. [Google Scholar]

- Park, S.; Kim, J.; Hwang, C.; Park, H.; Yoo, S.; Seong, T.; Choi, J. A 0.1–1.5-GHz Wide Harmonic-Locking-Free Delay-Locked Loop Using an Exponential DAC. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 548–550. [Google Scholar] [CrossRef]

- Tong, X.; Wu, J.; Chen, D. Low-Phase-Error Small-Area 4-Phase DLL with a Single-Ended-Differential-Single-Ended Voltage-Controlled Delay Line. IEEE Trans. Circuits Syst. II 2022, 69, 25–29. [Google Scholar] [CrossRef]

- Yang, J.; Pan, Q.; Yin, J.; Mak, P.-I. A 2.0-to-7.4-GHz 16-Phase Delay-Locked Loop with a Sub-0.6-ps Phase-Delay Error in 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2023, 71, 3596–3604. [Google Scholar] [CrossRef]

- Hoyos, S.; Tsang, C.W.; Vanderhaegen, J.; Chiu, Y.; Aibara, Y.; Khorramabadi, H.; Nikolic, B. A 15 MHz to 600 MHz, 20 mW, 0.38 mm2 Split-Control, Fast Coarse Locking Digital DLL in 0.13 μm CMOS. IEEE Trans. VLSI Syst. 2012, 20, 564–568. [Google Scholar] [CrossRef]

- Zhang, D.; Yang, H.-G.; Zhu, W.; Li, W.; Huang, Z.; Li, L.; Li, T. A Multiphase DLL with a Novel Fast-Locking Fine-Code Time-to-Digital Converter. IEEE Trans. VLSI Syst. 2015, 23, 2680–2684. [Google Scholar] [CrossRef]

- Rehman, M.R.U.; Hejazi, A.; Ali, I.; Lee, J.J.; Oh, S.J.; Pu, Y.; Lee, K.-Y. A Design of 6.8 mW All Digital Delay Locked Loop with Digitally Controlled Dither Cancellation for TDC in Ranging Sensor. IEEE Access 2020, 8, 57722–57732. [Google Scholar] [CrossRef]

- Byun, S.; Park, C.-H.; Song, Y.; Wang, S.; Conroy, C.S.G.; Kim, B. A Low-Power CMOS Bluetooth RF Transceiver with a Digital Offset Canceling DLL-Based GFSK Demodulator. IEEE J. Solid-State Circuits 2003, 38, 1609–1618. [Google Scholar] [CrossRef]

- Son, H.; Cho, H.; Koo, J.; Ji, Y.; Kim, B.; Park, H.-J.; Sim, J.-Y. A Low-Power Wide Dynamic-Range Current Readout Circuit for Ion-Sensitive FET Sensors. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 523–533. [Google Scholar] [CrossRef] [PubMed]

- Daly, D.C.; Chandrakasan, A.P. A 6-bit, 0.2 V to 0.9 V Highly Digital Flash ADC with Comparator Redundancy. IEEE J. Solid-State Circuits 2009, 44, 3030–3038. [Google Scholar] [CrossRef]

- Ryu, K.; Jung, D.-H.; Jung, S.-O. Process-Variation-Calibrated Multiphase Delay Locked Loop with a Loop-Embedded Duty Cycle Corrector. IEEE Trans. Circuits Syst. II 2014, 61, 1–5. [Google Scholar] [CrossRef]

- Yoon, Y.; Park, H.; Kim, C. A DLL-Based Quadrature Clock Generator with a 3-Stage Quad Delay Unit Using the Sub-Range Phase Interpolator for Low-Jitter and High-Phase Accuracy DRAM Applications. IEEE Trans. Circuits Syst. II 2020, 67, 2342–2346. [Google Scholar] [CrossRef]

| VDD (V) | Average Lock Time (Cycles) | Lock Time Reduction (%) | ||||

|---|---|---|---|---|---|---|

| * Conv. | Proposed (Initial Lock) | Proposed (Relock) | Initial Lock vs. Conv. | Relock vs. Conv. | Initial Lock vs. Relock | |

| 0.5 | 29.6 | 15 | 10.1 | 49.3 | 65.9 | 32.7 |

| 1 | 34.9 | 20.1 | 10.4 | 42.4 | 70.2 | 48.3 |

| TCAS-I’ 2012 [13] | TCAS-II’ 2022 [18] | TVLSI’ 2015 [21] | Access’ 2020 [22] | TCAS-II’ 2014 [26] | TCAS-II’ 2020 [27] | This Work | |

|---|---|---|---|---|---|---|---|

| Process (nm) | 180 | 180 | 130 | 180 | 130 | 28 | 28 |

| Loop Filter | Analog | Analog | Digital | Digital | Digital | Digital | Analog |

| VDD (V) | 1.8 | 1.8 | 1.5 | 1.8 | 1.2 | 1 | 0.5–1 |

| Area (mm2) | 0.035 | 0.0092 | 0.08 | 0.06 | 0.025 | 0.0072 | 0.013 |

| Locking Freq. (MHz) | 400–800 | 250 | 80–450 | 350–900 | 400–800 | 1800–2500 | 0.5–2.5 @0.5 V 1–40 @1 V |

| RMS Jitter (ps) | 2.81 @800 MHz | 1 14.72 @250 MHz | 2.3 @180 MHz | 1.2 @625 MHz | 2.3 @800 MHz | 1.7 @2.5 GHz | 24.57 @40 MHz, 1 V |

| Power (mW) | 19 @800 MHz | 2.28 @250 MHz | 26 @180 MHz | 6.8 @625 MHz | 7.2 @800 MHz | 3.7 @2.5 GHz | 0.107 @40 MHz, 1 V |

| 2 FOMPOWER | 7.33 | 2.81 | 64.2 | 3.35 | 6.25 | 1.48 | 3.50 @0.5 V 2.68 @1 V |

| Lock Time (Cycle) | <52 | - | 8–16 | - | 75–374 | <72 | 9–25 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kang, H.; Koo, J.; Woo, J.-M.; Ji, Y.; Son, H. An Analog Delay-Locked Loop with Digital Coarse Lock Incorporating Error Compensation for Fast and Robust Locking. Electronics 2024, 13, 2514. https://doi.org/10.3390/electronics13132514

Kang H, Koo J, Woo J-M, Ji Y, Son H. An Analog Delay-Locked Loop with Digital Coarse Lock Incorporating Error Compensation for Fast and Robust Locking. Electronics. 2024; 13(13):2514. https://doi.org/10.3390/electronics13132514

Chicago/Turabian StyleKang, Hyungmin, Jahyun Koo, Jeong-Min Woo, Youngwoo Ji, and Hyunwoo Son. 2024. "An Analog Delay-Locked Loop with Digital Coarse Lock Incorporating Error Compensation for Fast and Robust Locking" Electronics 13, no. 13: 2514. https://doi.org/10.3390/electronics13132514

APA StyleKang, H., Koo, J., Woo, J.-M., Ji, Y., & Son, H. (2024). An Analog Delay-Locked Loop with Digital Coarse Lock Incorporating Error Compensation for Fast and Robust Locking. Electronics, 13(13), 2514. https://doi.org/10.3390/electronics13132514