3.1. Approximations: Two Examples

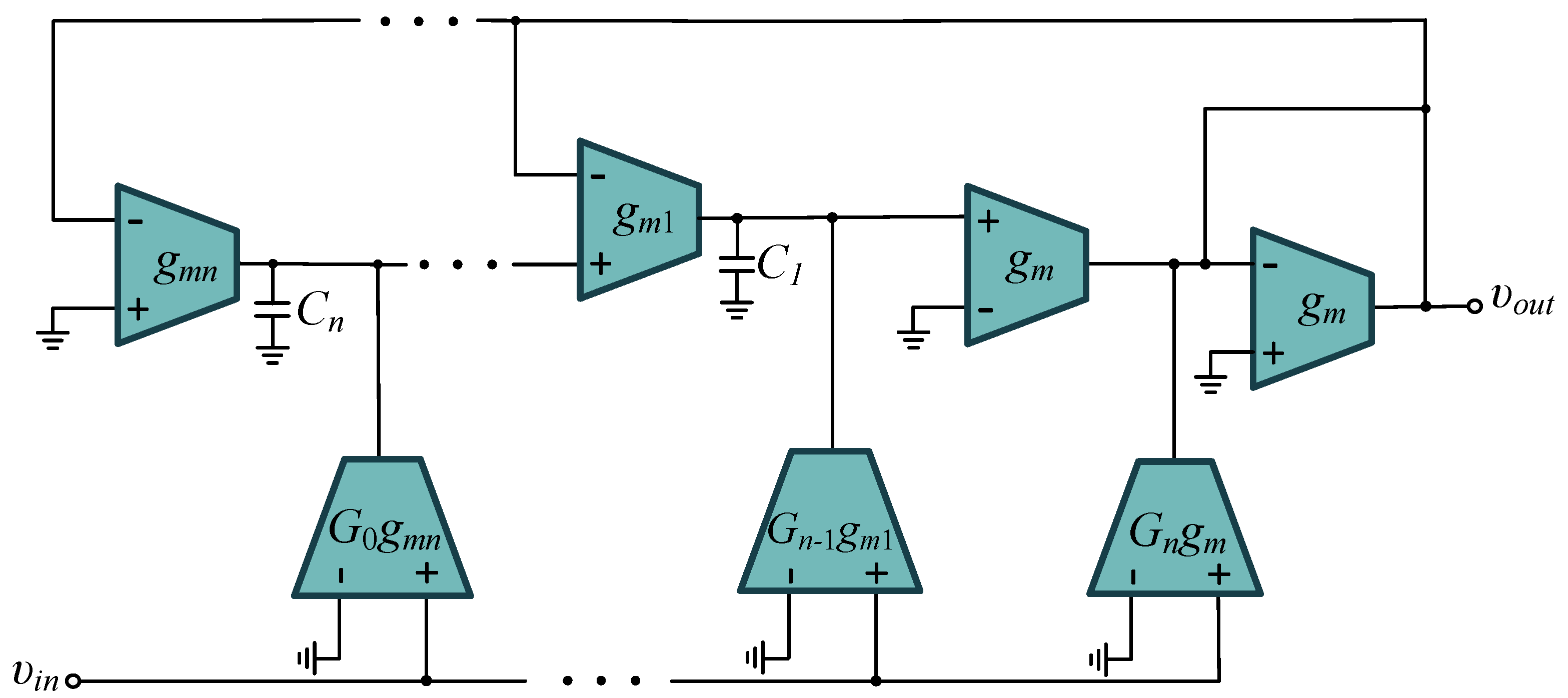

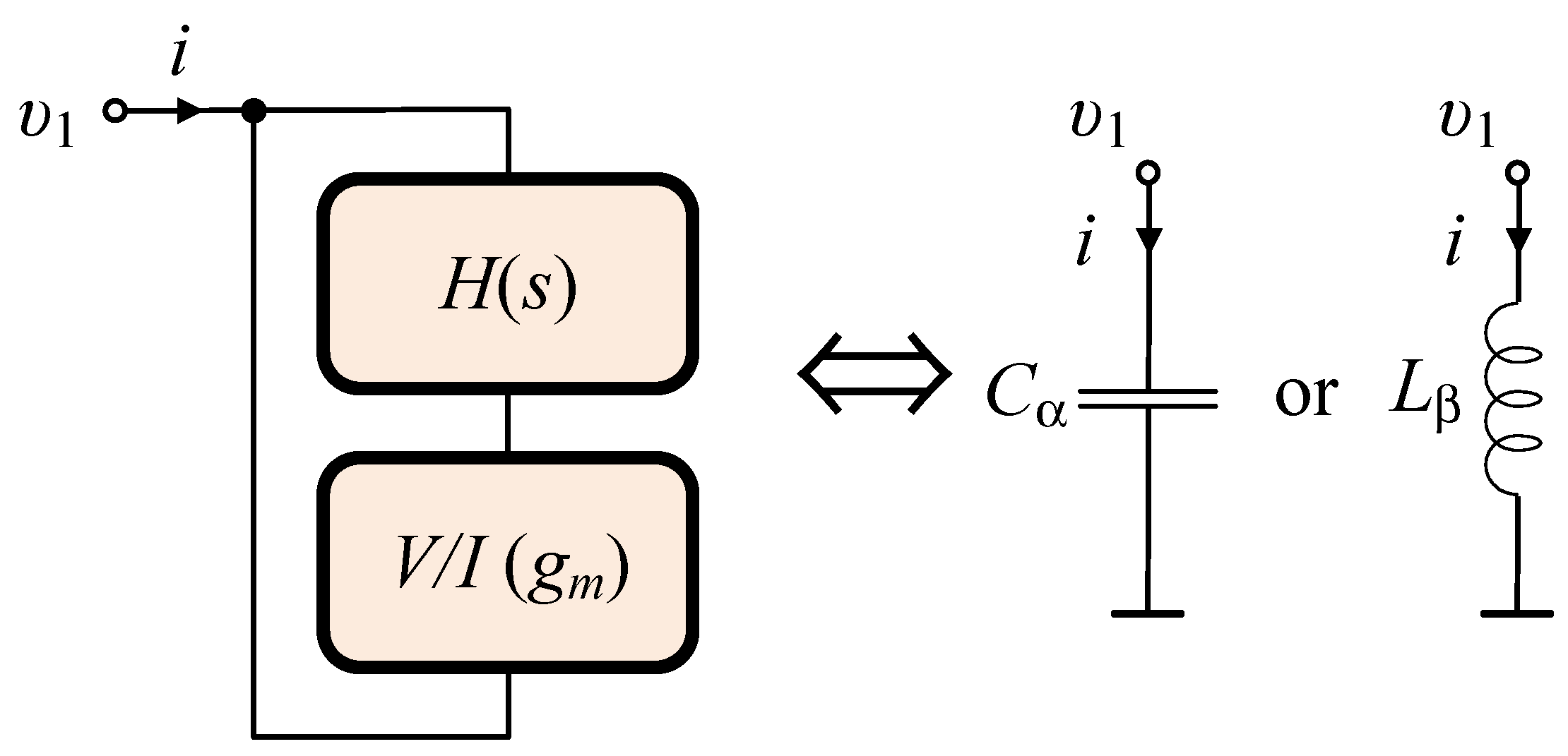

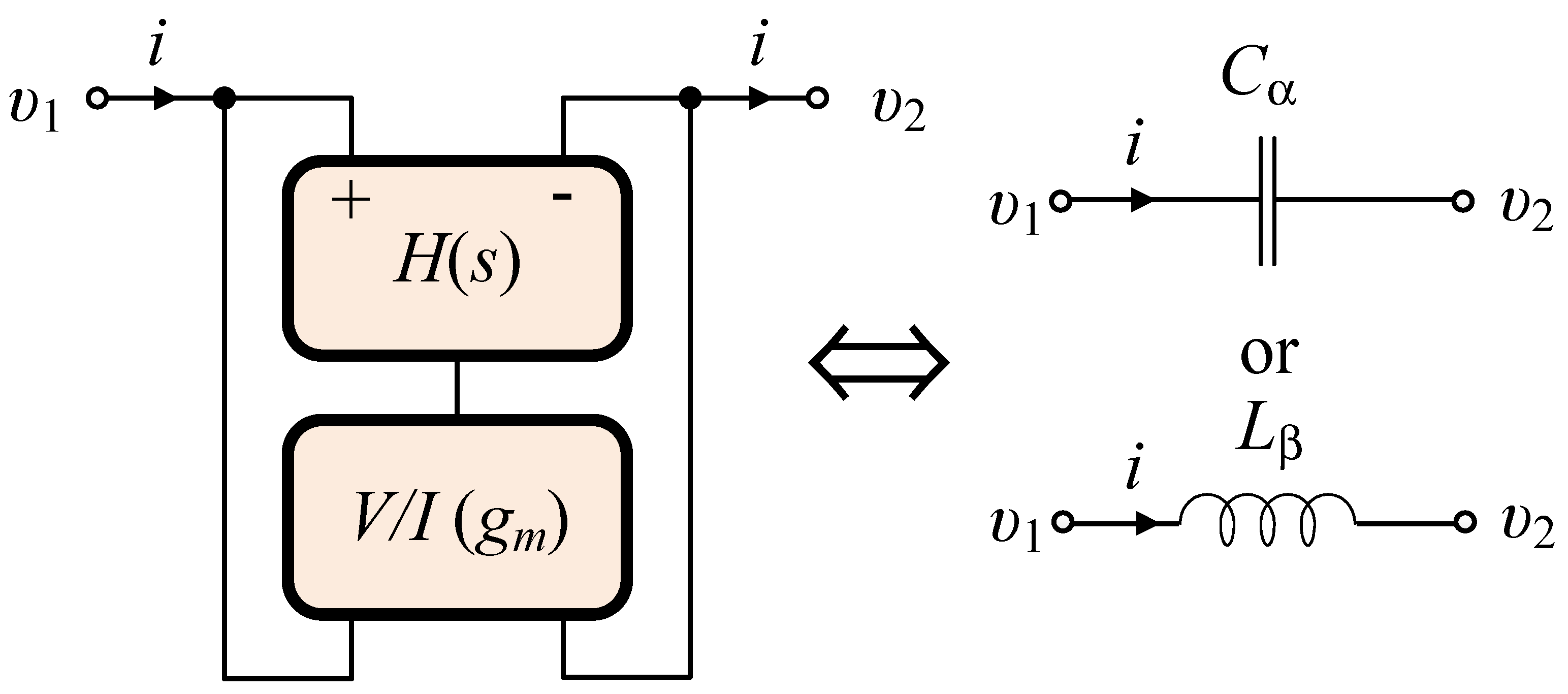

The circuit in

Figure 8 is designed for

α = −1/2, with the centre frequency

f0 = 50 [kHz] and the CPE capacitance

C = 500 [pF] at

f0. Note that

ω0 = 2

πf0 = 100

π [krad/s].

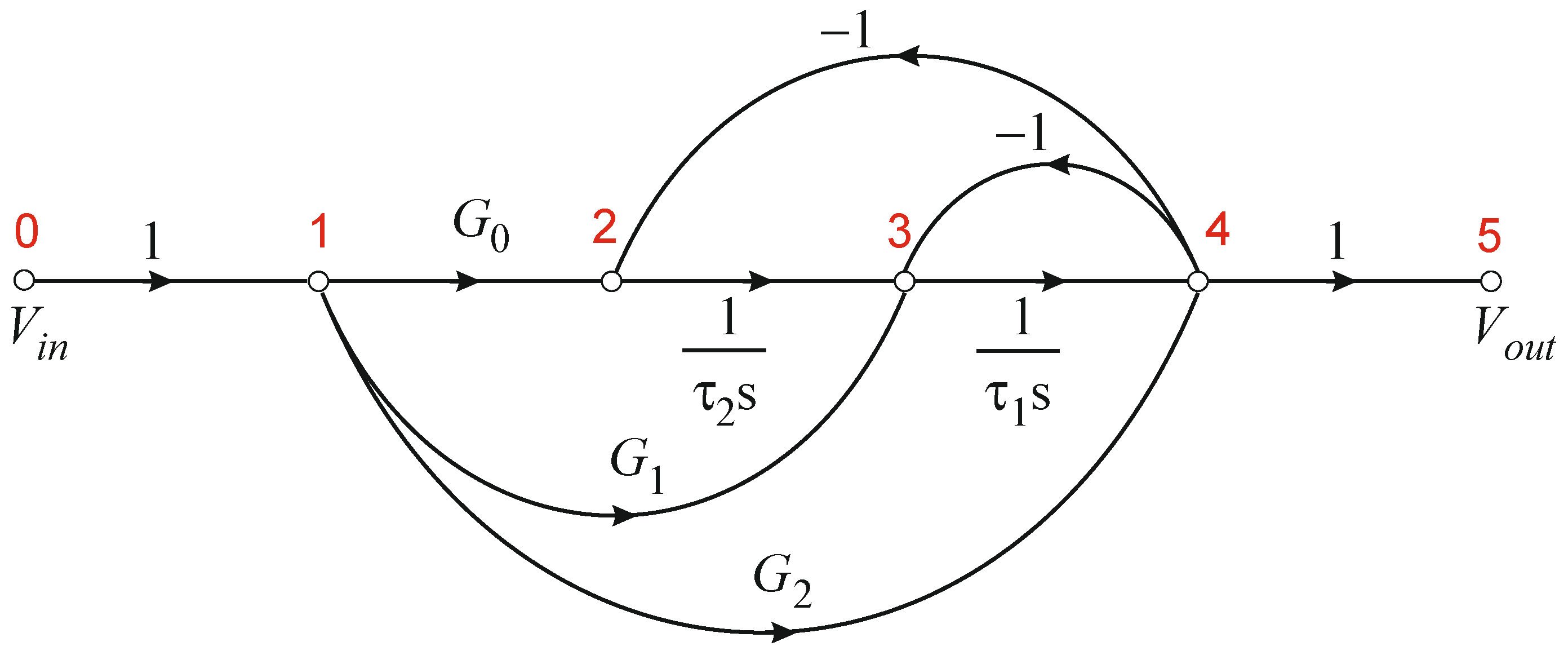

For Example 1, the second-order approximation with the continued-fractional expansion (CFE) as in [

29] is used. The values obtained are the same as in [

26] and are repeated in

Table 1 in this paper. For Example 2 in this paper, the recently introduced minimax approximation from [

27] is used. The Matlab R2021b (academic use) programme Ver. 1.0.1 in [

28] can be used to calculate the minimax coefficients. Then the minimax approximation is compared with the CPE approximation used in [

26].

The frequency analysis is performed from 5 kHz to 500 kHz because the centre frequency is at 50 kHz, and the second-order CFE approximation is efficient within almost two decades. A minimax approximation was developed that covers the same bandwidth as CFE. Therefore, BW =

ωH/

ωL = 50 is used in the design along with the programme in [

28]. The values

ωH = 7.071 [rad/s] and

ωL = 0.14142 [rad/s] represent the normalised upper and lower limits of the useful frequency range for approximating a constant phase. Note that when designing the minimax approximation, it is possible to define the bandwidth BW, while this is not possible when designing CFE. The coefficients of

H(

s) for the second-order CFE and minimax approximations for the three values of

α = 1/3, 1/2, and 2/3 are given in

Table 1.

Note that the coefficients of the transfer functions in

Table 1 are symmetrical. Therefore, from Equation (13) and

τ = 1, the normalised coefficients of the transfer function

H(

s) are obtained for

α = 1/2 from the second row in

Table 1, given by:

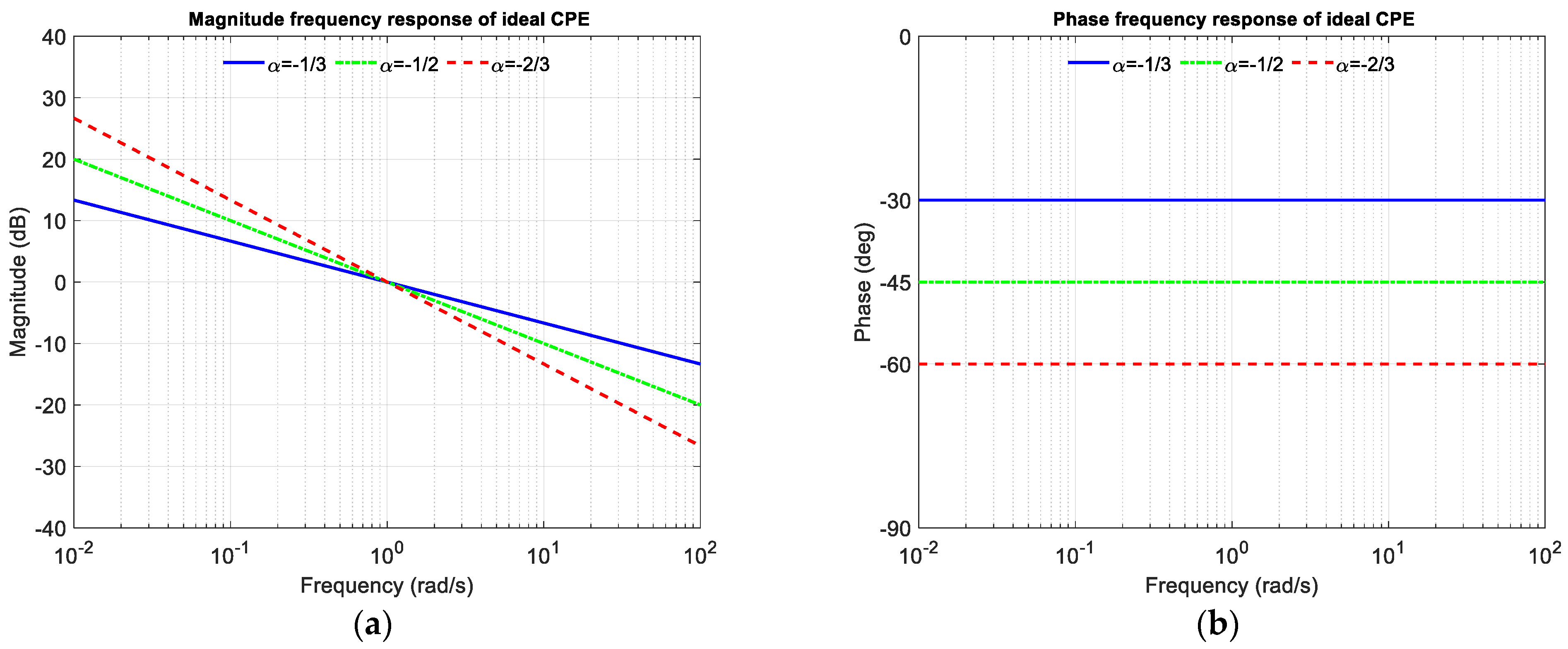

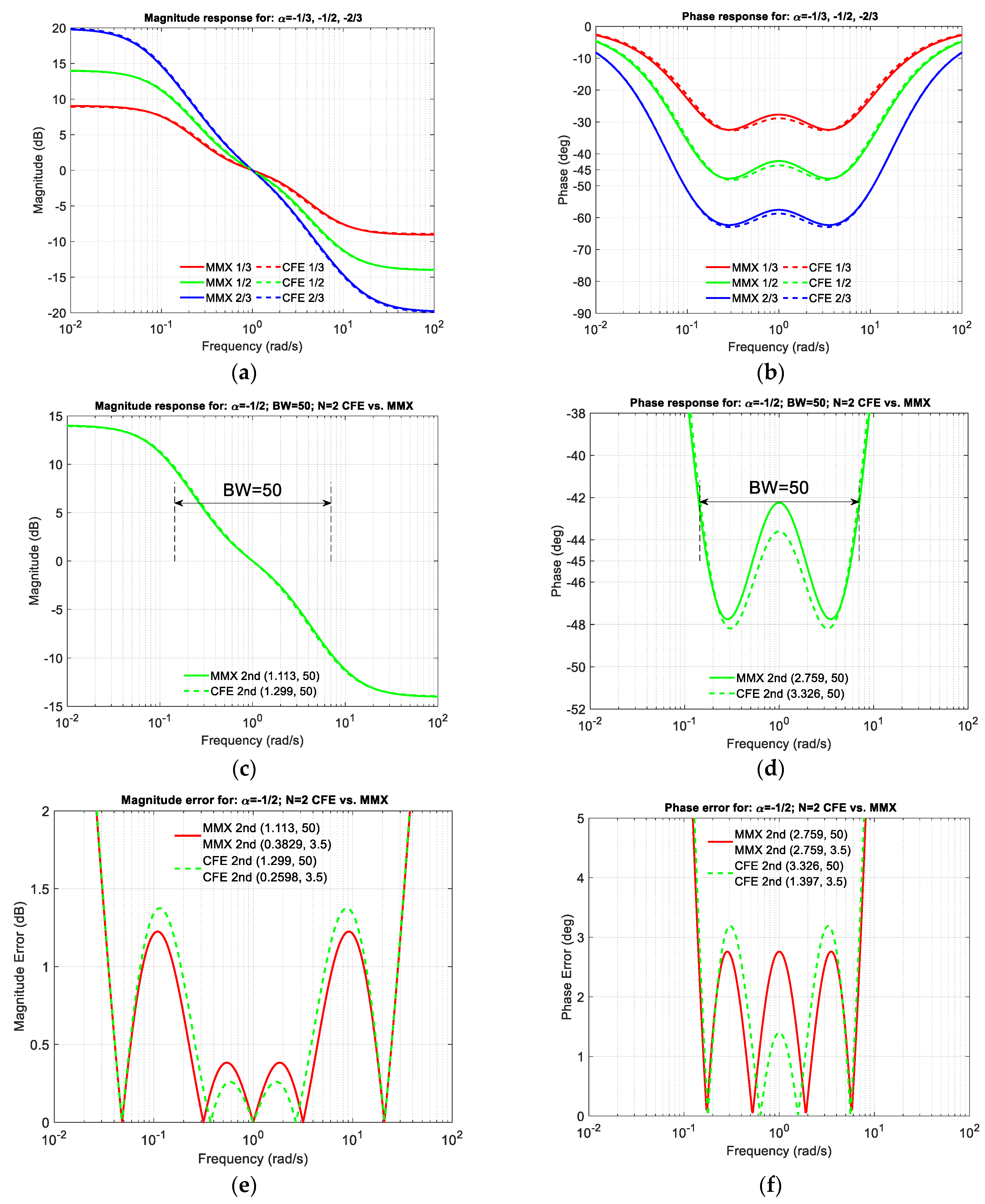

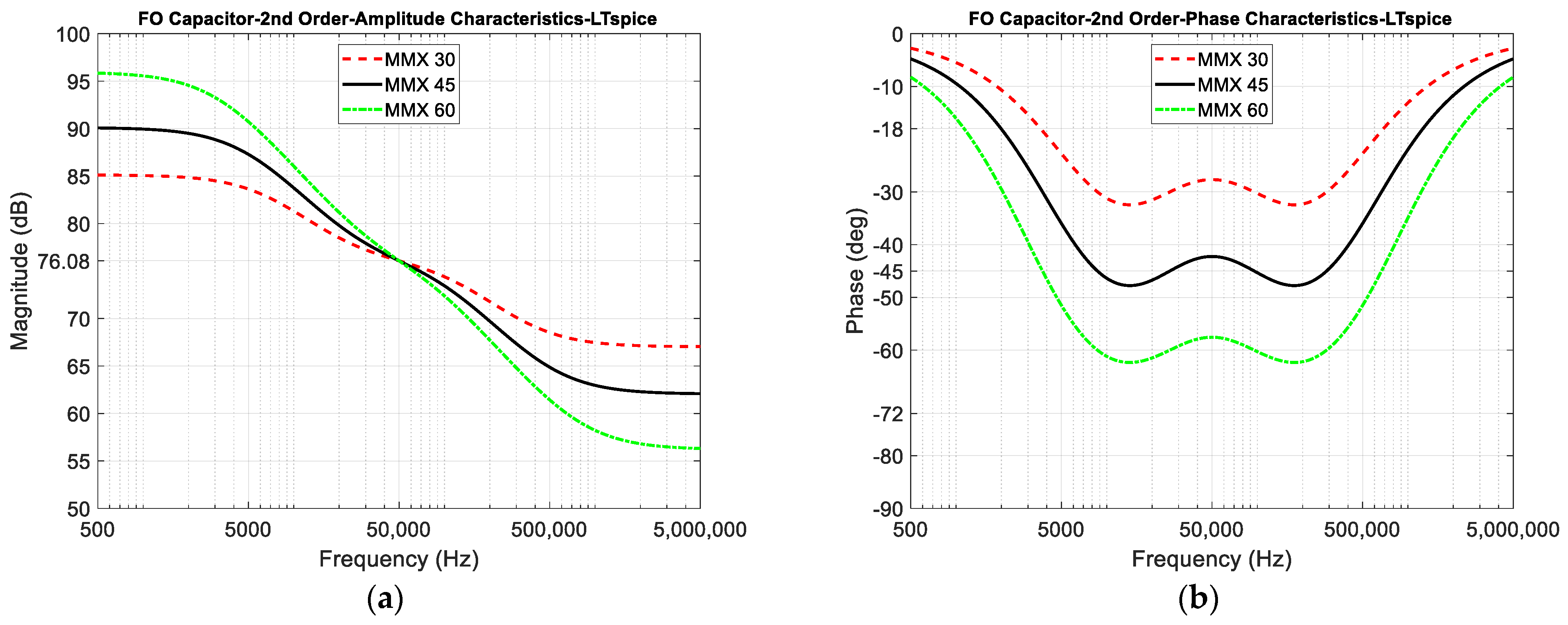

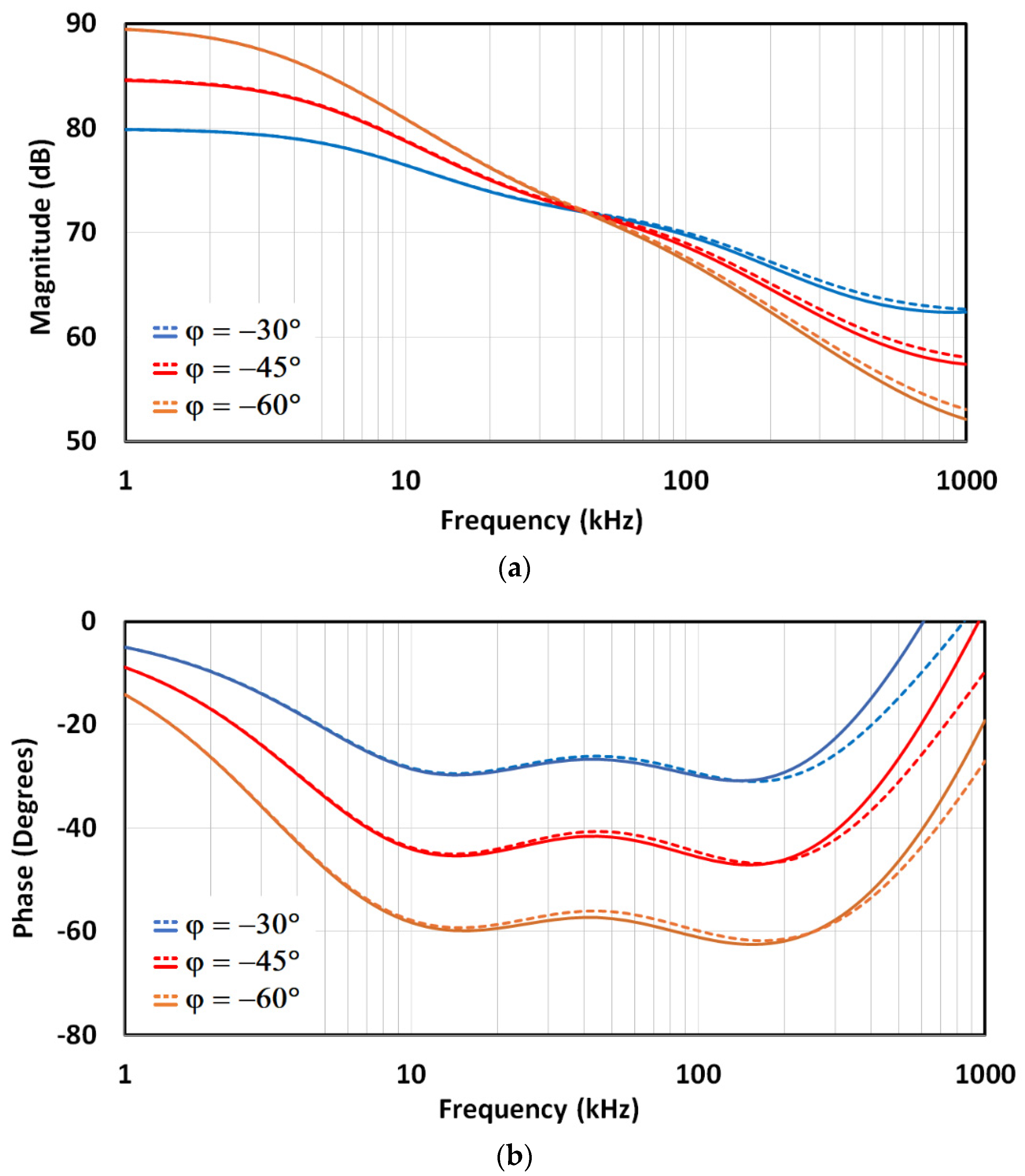

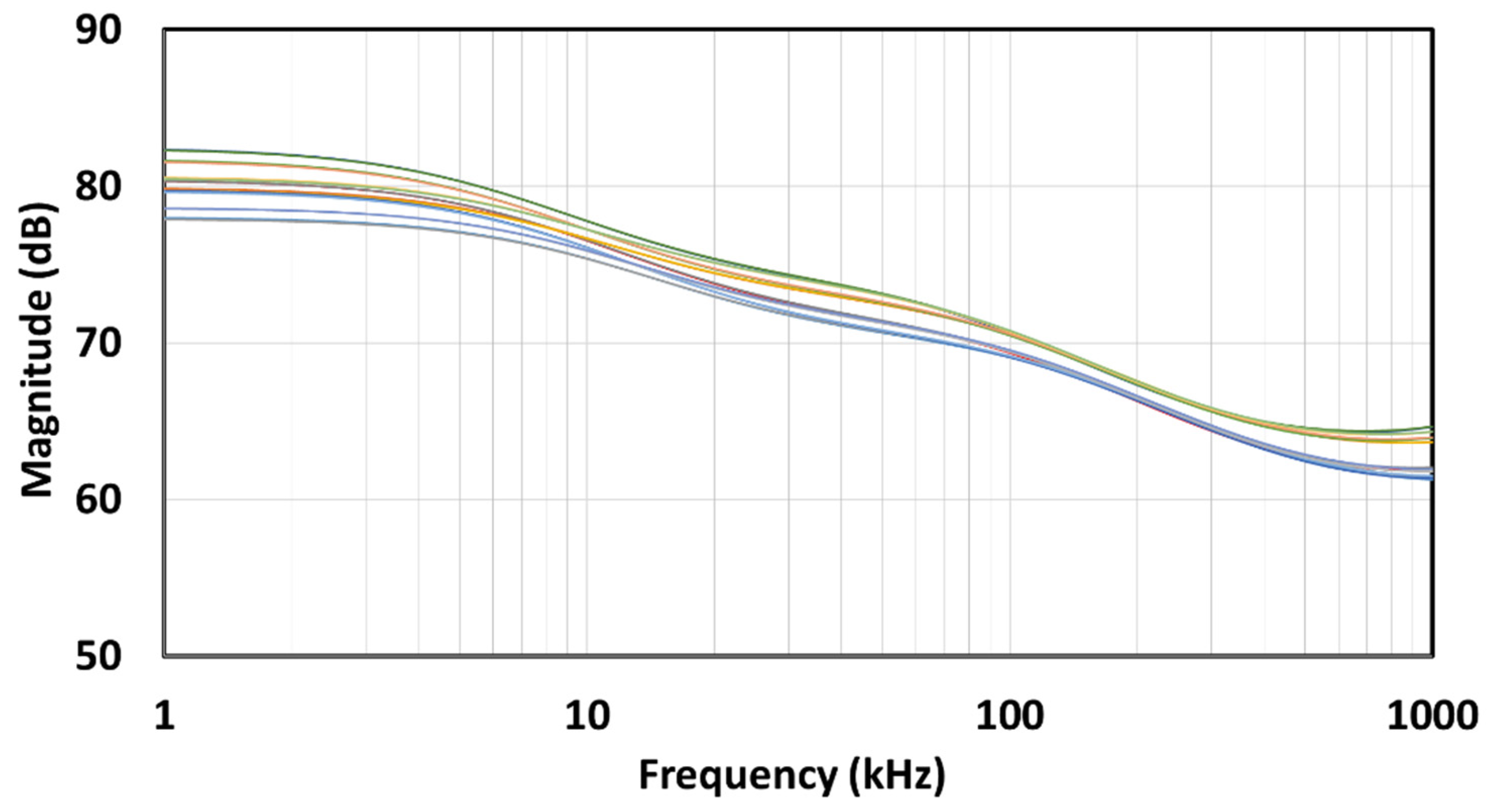

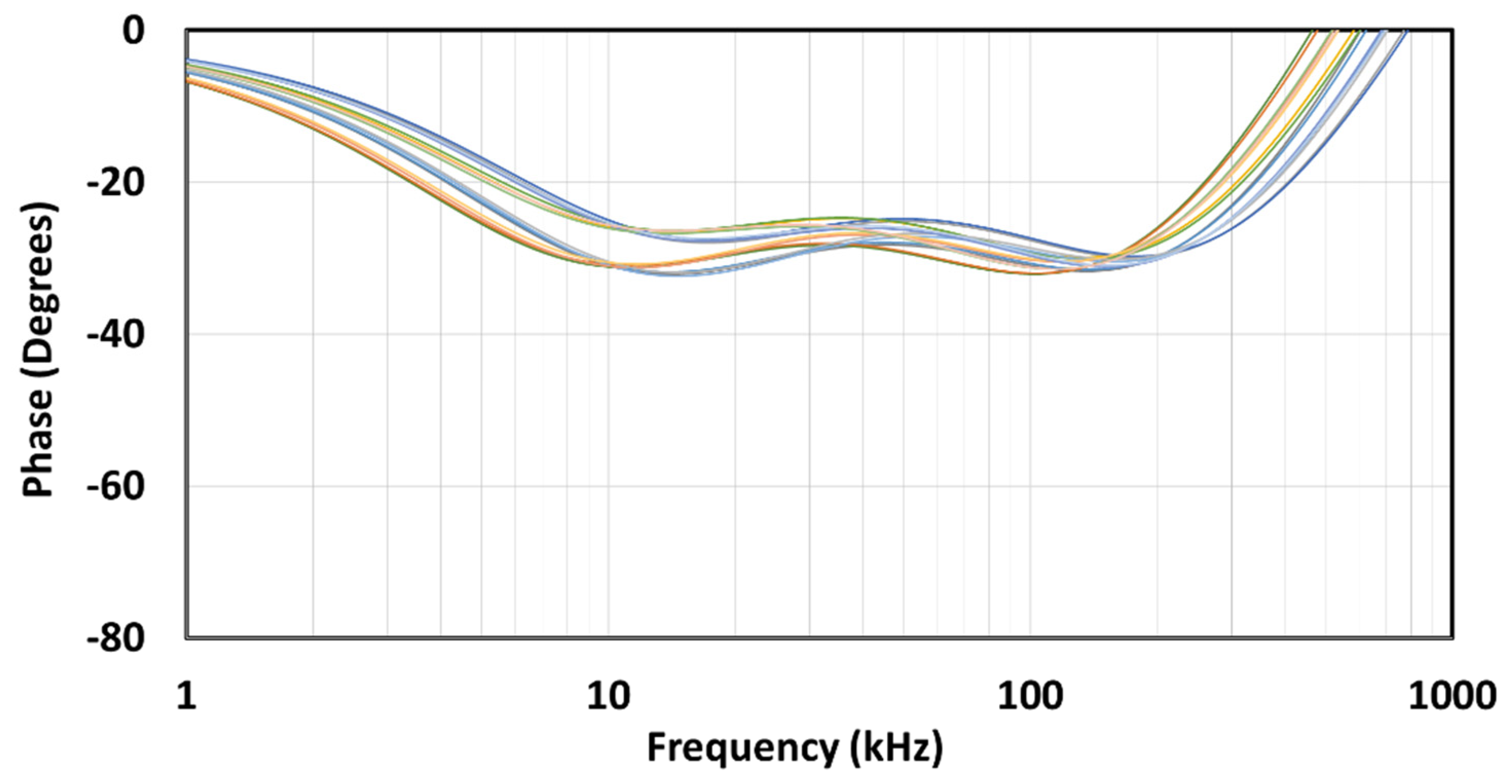

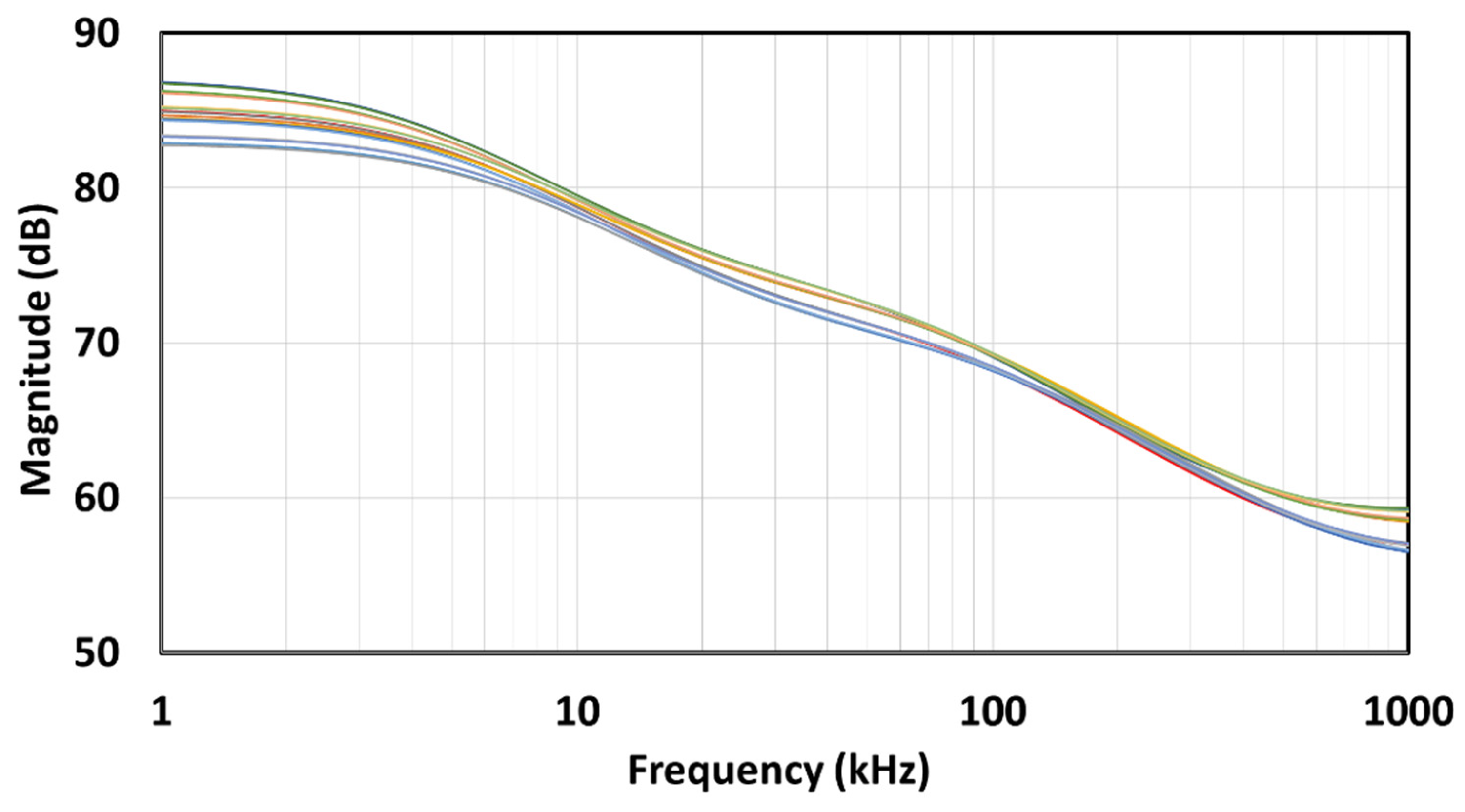

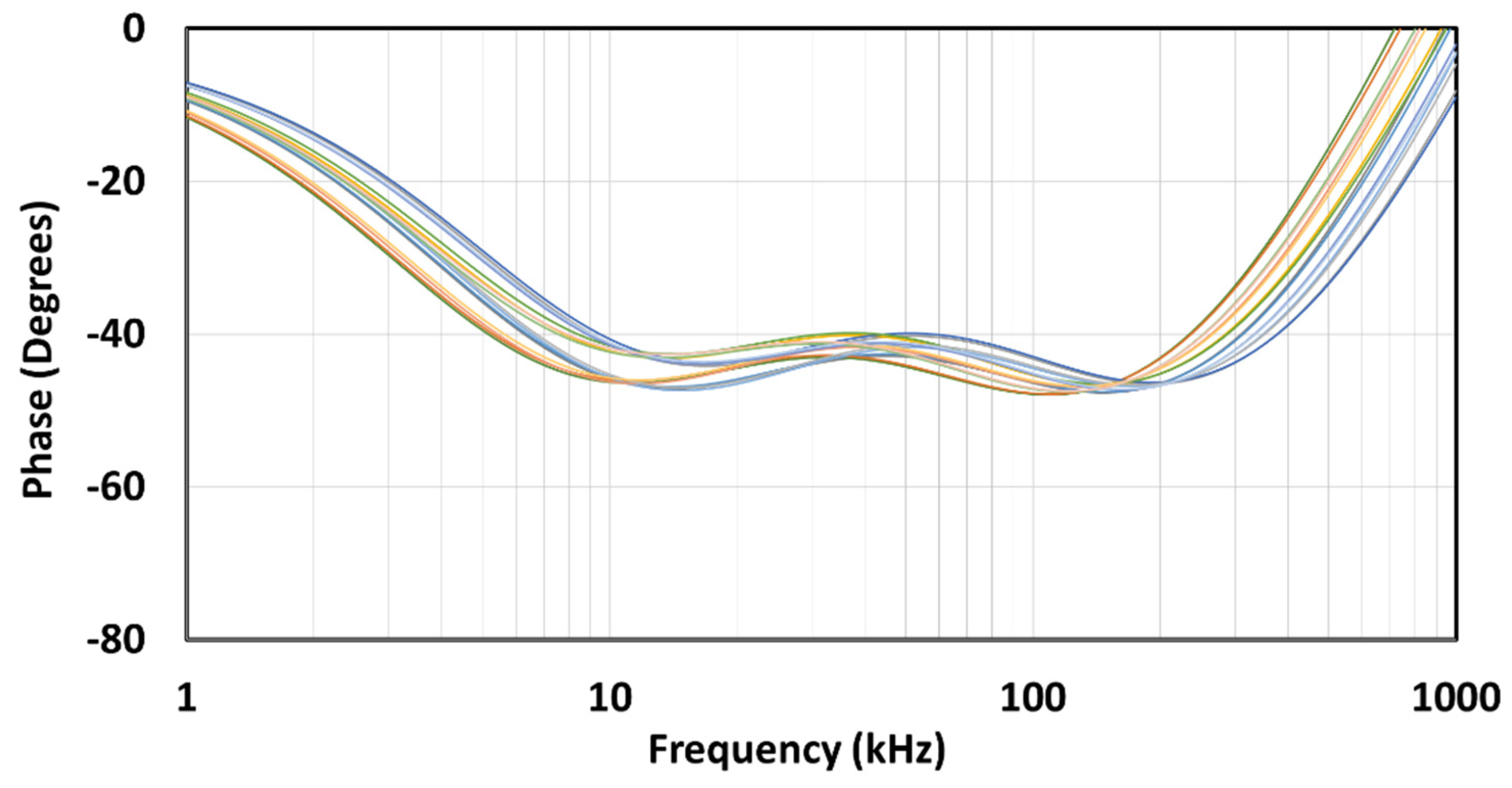

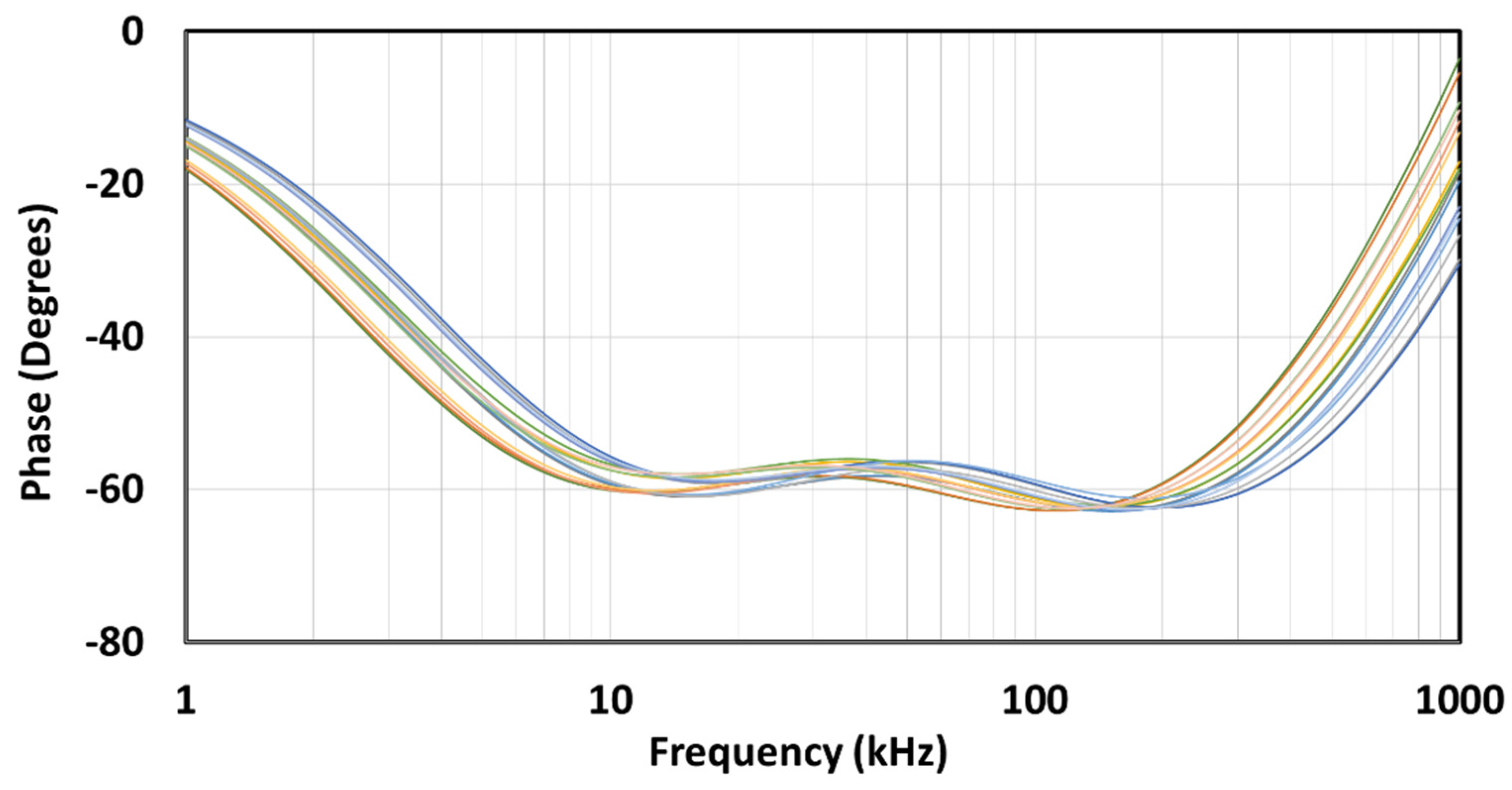

Normalised magnitude and phase of 1/

H(

s), where

H(

s) is defined for

α = −1/3, −1/2, and −2/3, are shown in

Figure 9. A detailed analysis for the case of

α = −1/2 is also given. Recall that we must use 1/

H(

s) since in Equation (12),

Z(

s) is inversely proportional to

H(

s). Remember that the inverse of

H(

s) changes the sign of the angle from positive to negative.

If we look at

Figure 9a,b, we can see that there is a slight difference between the CFE and MMX approximations in both the amplitude and phase characteristics. In the zoomed amplitude response in

Figure 9c, we can see this slight difference, while in the zoomed phase response in

Figure 9d, we can see that the MMX is slightly more centred around the ideal phase of −45°. The values in brackets were determined numerically in Matlab R2021b (academic use) and represent the maximum deviation from the ideal value within the usable passband (BW =

ωH/

ωL = 50). In the case of MMX, it is 1.113 dB and 2.759°, while in the case of CFE, it is 1.299 dB and 3.326°. These values confirm that both the magnitude and phase curves of MMX are closer to the ideal than those of CFE when the entire usable frequency band is considered.

Figure 9e,f shows absolute amplitude and phase errors. The CFE is a better approximation near the centre frequency, while the MMX is a better approximation near the edges. Looking at the phase errors for the CFE, the absolute local peak-to-peak difference in phase is 3.326° + 1.397° = 4.723°, with the middle value −((3.326° − 1.397°)/2 + 45°) = −45.9645°, which represents the small phase offset from the desired −45°. In the case of MMX, the absolute local peak-to-peak difference in phase is 5.518°, which is worse than the CFE, but there is no phase offset. If a small phase can be added (or a small phase offset can be removed) in advance of the design process, the performance of the CFE can be better than that of the MMX.

In the following part of the paper, we will continue with the design of the MMX approximation in the CPE design.

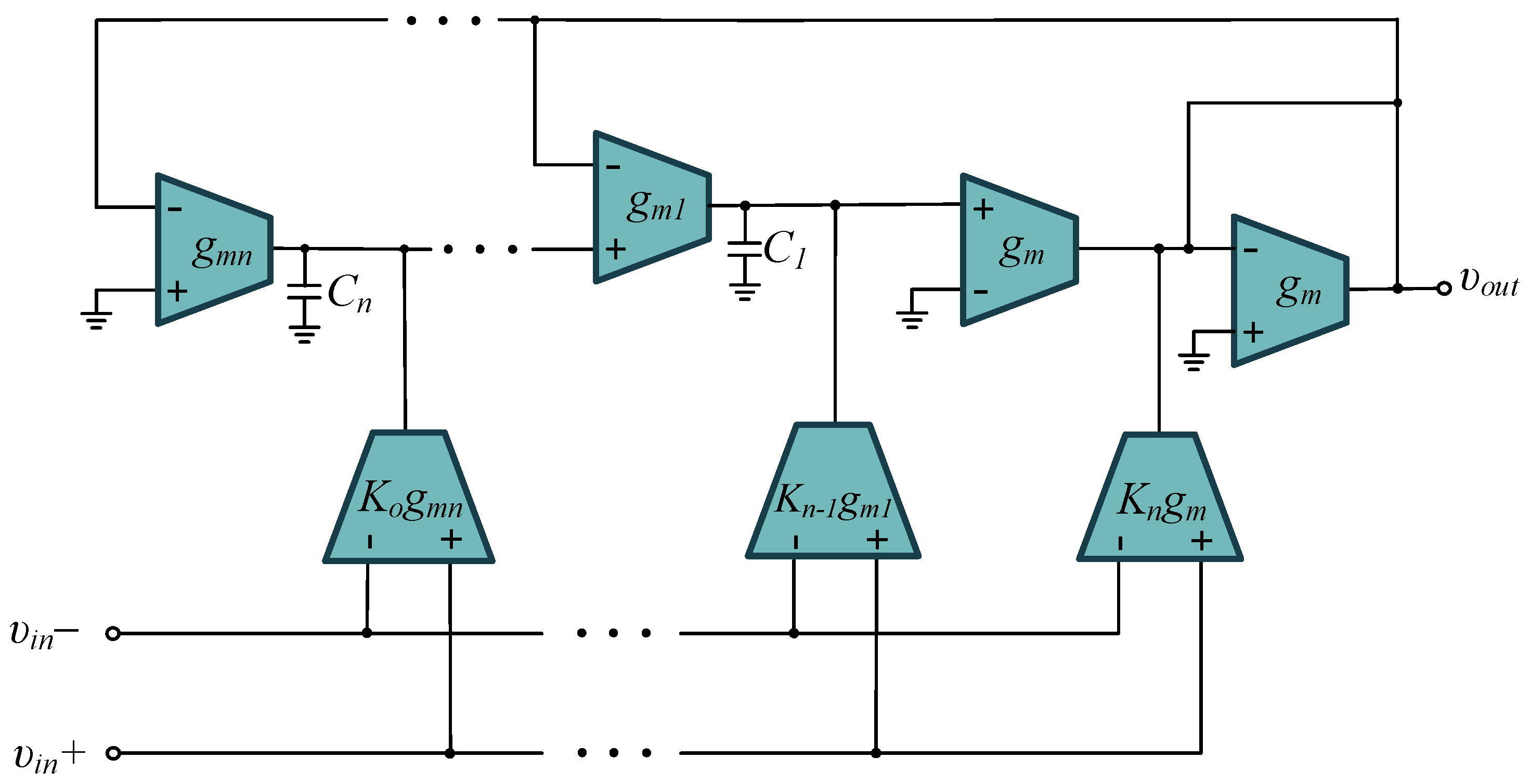

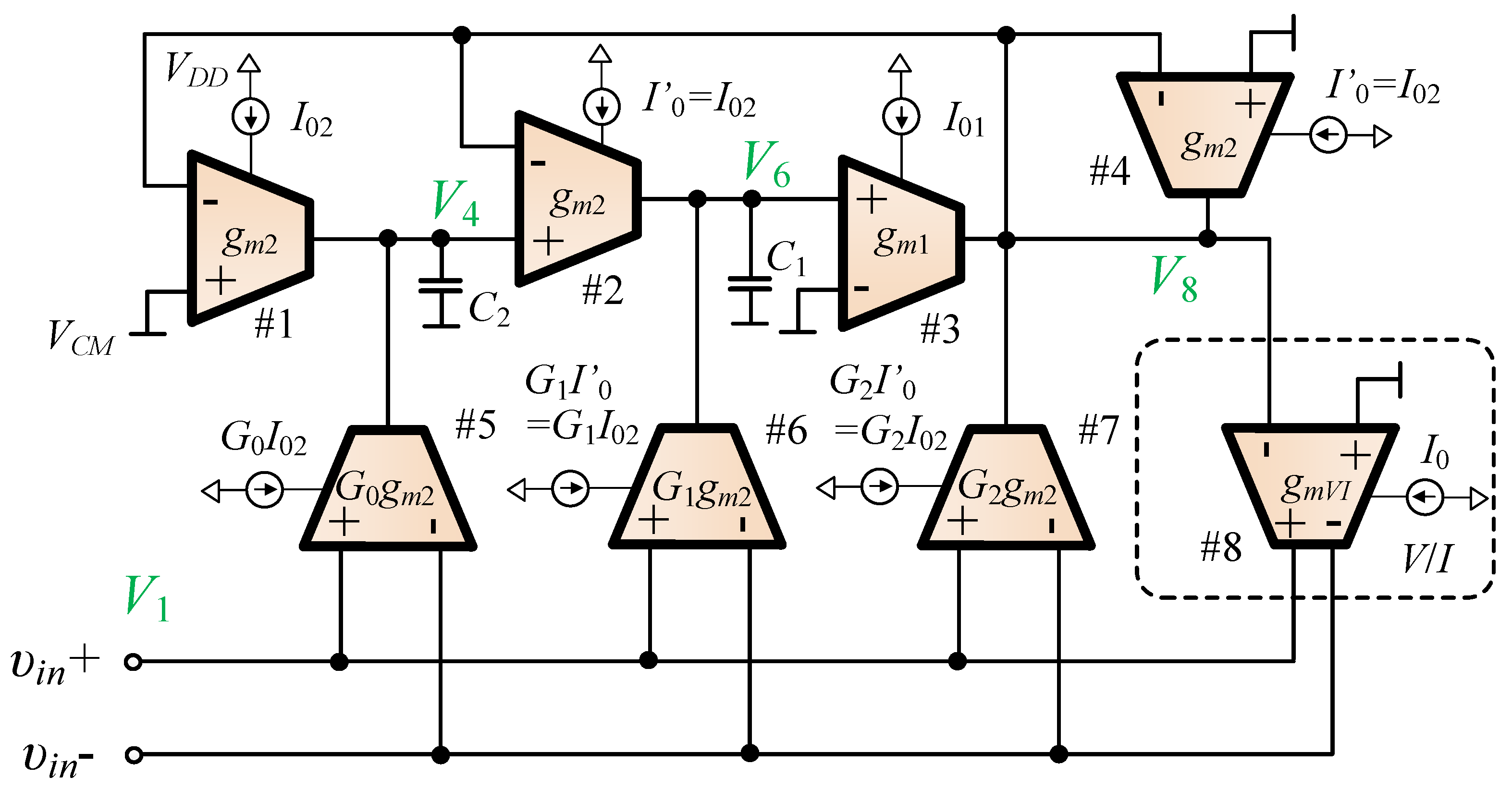

3.3. Designing of OTAs

In our paper, we will use OTAs with MOS transistors in the strong inversion region to operate at high frequency. The proposed OTAs are also referred to as gm cells with different gm values. OTAs (gm cells) are single-stage amplifiers for stability reasons, have a high output impedance because they have built-in cascodes, use source degeneration of the input diff pair by two MOSFETs operating in the triode region (see [

24,

25] and Section 14.1 in [

32]), and use wide-swing current mirrors to have less headroom (see Section 6.3.1 in [

33]).

The voltage supply is typical for the AMS 0.35 technology:

VDD = −

VSS = 2 V. First, we define a reference current

Ibias in the acceptable value range for each OTA to be able to realise the required transconductances in

Table 3. We consider that the source degeneration also reduces the resulting transconductance of the entire OTA compared to the transconductance of the input transistors. The optimum ratio between the dimensions of the input transistors and the dimensions of the degeneration transistors (the latter operate in the triode region) is

N = (

W/

L)

input/(

W/

L)

deg = 6.7.

In the first step, we calculate the transconductances

gm1,2 of the OTA input pair M

N1,2 based on the required OTA transconductance

gm with

. For example, to realise

gm7=165.057 [μS] of OTA #7 in

Figure 8, we need an input pair with

gm1,2 = 2.675·165.057 [μS] = 441.53 [μS] in the electronic realisation of the OTA. This is a fairly high value.

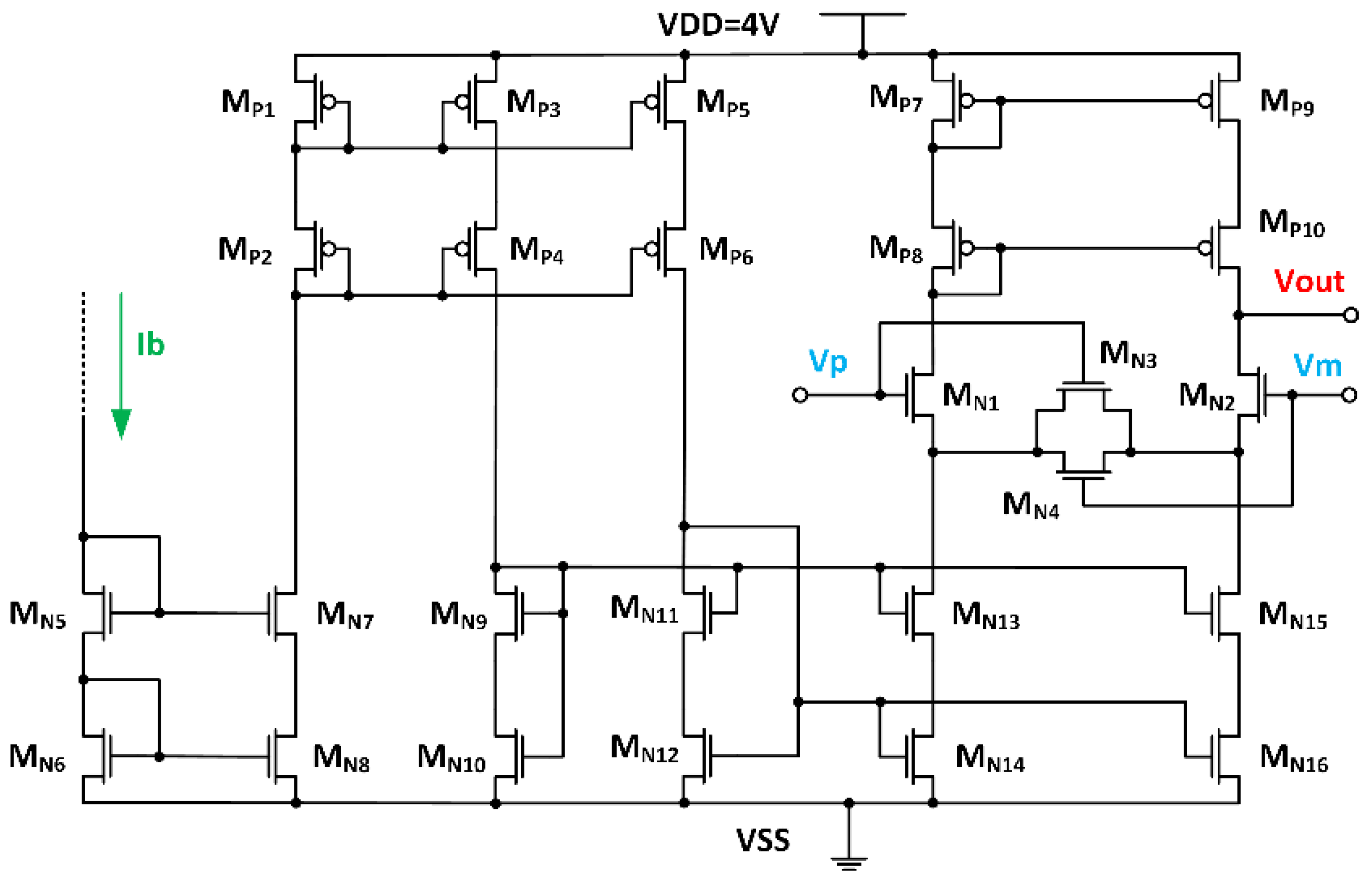

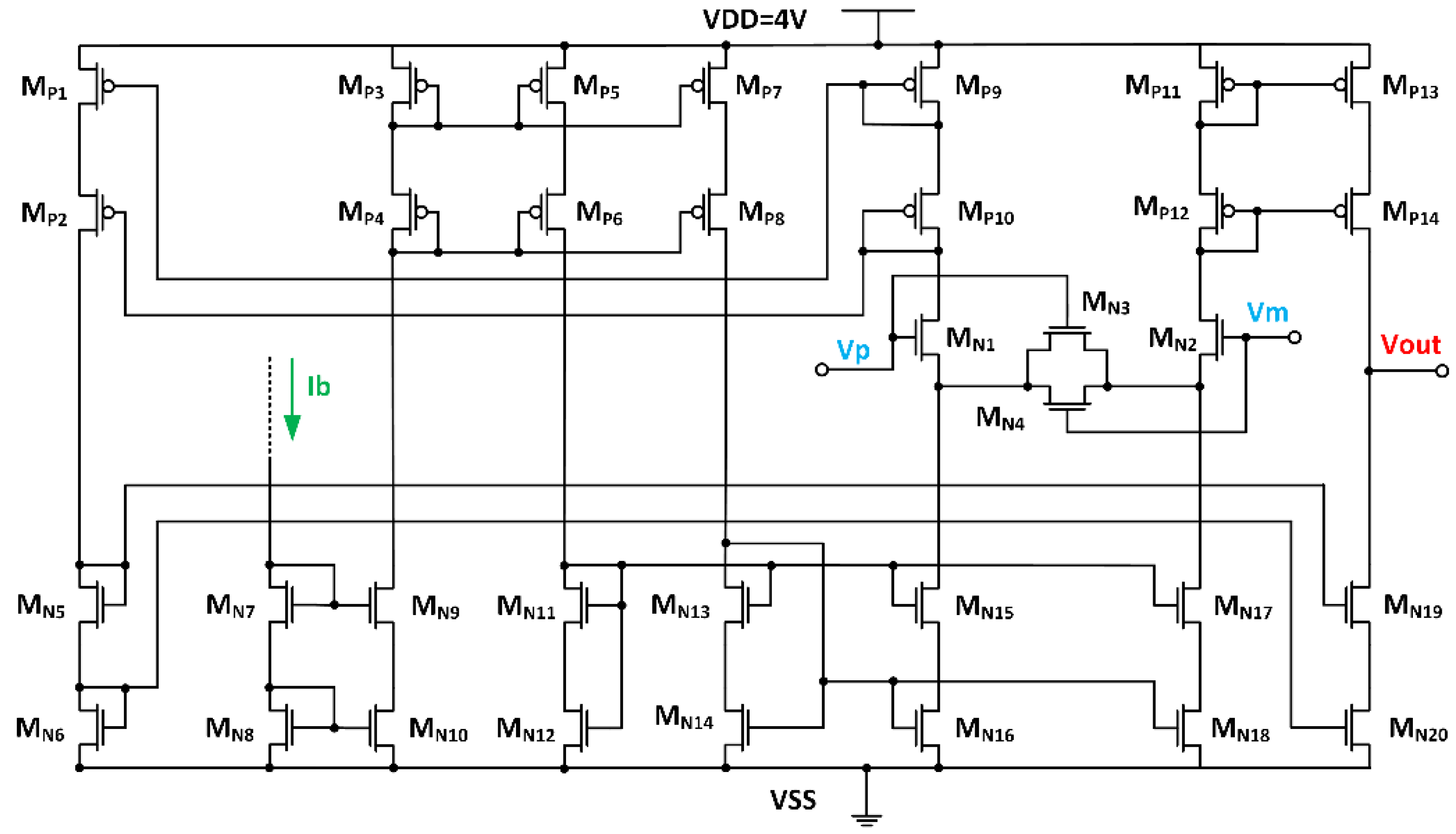

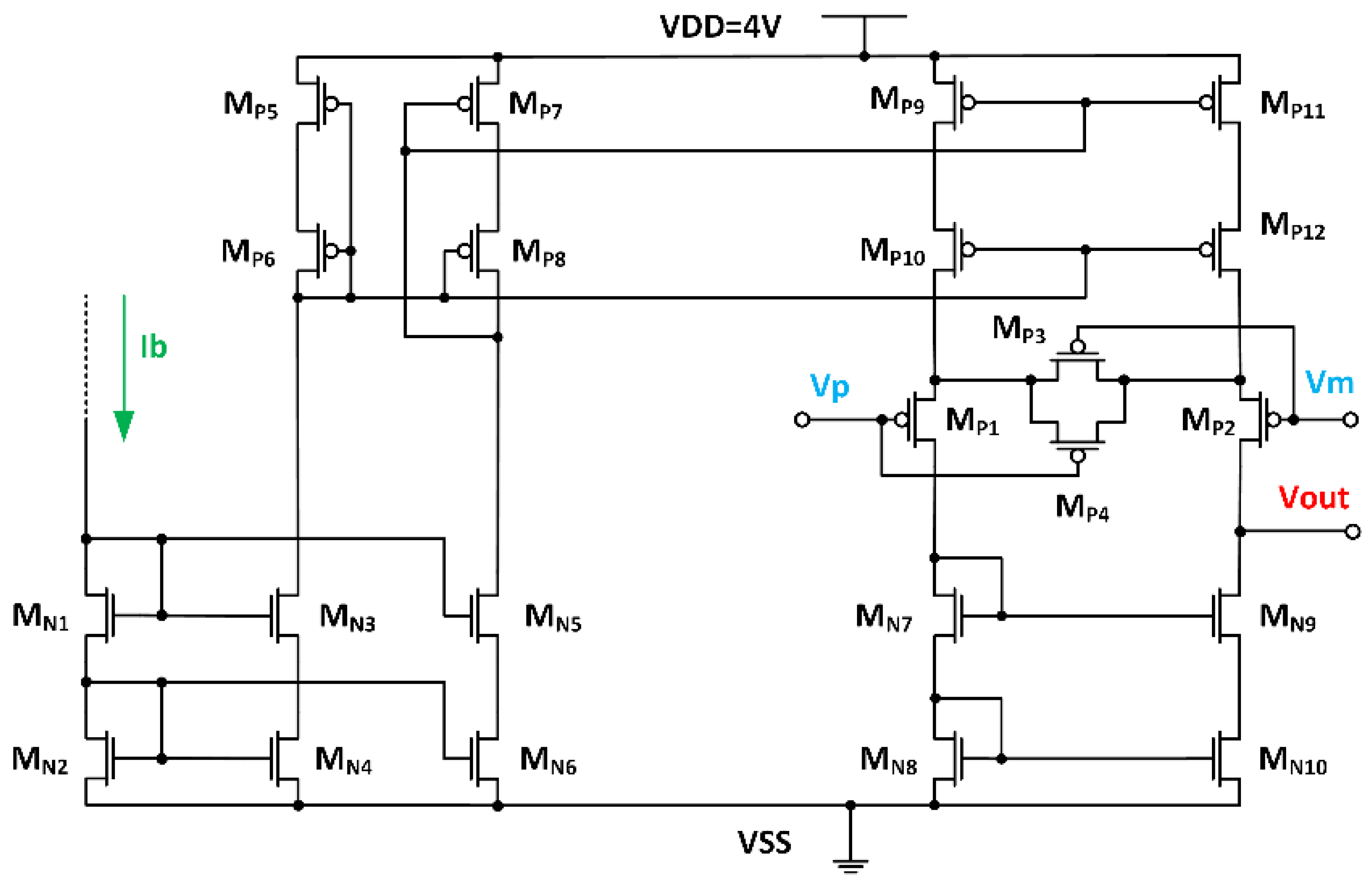

To realise the given value of the transconductance, we decide between an NMOS or PMOS differential input stage, depending on the selected bias current

Ibias and the acceptable dimensions of the input transistors. For a low value of the transconductance, we will use a PMOS input differential pair. For a medium value of transconductance, we will use an NMOS input differential pair. To achieve a high

gm value and obtain a reasonable bias current, we will use an NMOS input differential pair and a symmetric CMOS OTA (see [

5] and Chapter 7 in [

34]). This means that we use three basic topologies of OTAs in our design, all of which are required to keep the bias currents within reasonable values. We distinguish between four versions of OTAs: OTA1 through OTA4. OTA1 and OTA2 are used for the realisation of medium

gm and have the same topology as shown in

Figure 11, but differ only in the dimensions of the input NMOS diff pair. OTA3, which is shown in

Figure 12, has a symmetrical CMOS OTA topology and is used for high

gm values, and OTA4, which is shown in

Figure 13, realises the low

gm values and therefore has a PMOS input diff pair.

For hand calculations, we have extracted the parameters of the AMS 0.35 μm technology: for NMOS, K’n = μnCox = 117 [μA/V2], VTn = 0.507 [V], and λn = 0.05 [V−1], and for PMOS, K’p = μpCox = −42 [μA/V2], VTp = −0.697 [V], and λn = −0.08 [V−1].

We distinguish between three steps in the design of a single-stage OTA for our application:

- (1)

In the case of the input transistors

MN1 and

MN2 in the input differential pair, we use:

For the degeneration transistors

MN3 and

MN4 (which operate in the triode region) in the input differential pair, we then have:

Here we can also calculate the gate overdrive voltage (or saturation voltage):

- (2)

In the case of transistors in wide swing cascode current mirrors in the sources of the input pair, we start our calculation with a selected (realistic) overdrive voltage

VDsat between 100 mV and 200 mV and calculate

gm with

and then the required transistor dimensions follow:

- (3)

In the case of transistors that form current mirrors in the drains of an input pair (active load), we perform our calculation in the same way as in case 2 and use the same Equations (28) and (29). The only difference that needs to be noted is that the transistors in this case are of opposite polarity than in case 2.

The

W/

L values, which were calculated with the above design equations and then simulated by Cadence for the OTAs in our circuit, can be found in

Table 4,

Table 5 and

Table 6. We have obtained three groups of OTAs. Tuning for different CPE angles is performed by changing

Ibias with all transistors operating safely in saturation. The required bias current

Ibias to obtain the required transconductances in

Table 3 for different orders

α can be found in

Table 7. To reduce the spread of

Ibias currents, we need to include OTAs with higher transconductances. In the previous publication in [

26], where only one type of OTA was used, the ratio of the critical bias current

Ibias is between the maximum of 280 μA and the minimum of 0.9 μA and is higher than 300. In our design, where we chose different OTA topologies, the ratio between the maximum and minimum required bias current

Ibias is 10, which is a 30-fold improvement. The dimensions of the MOS transistors in OTAs are given below each of the circuits in the tables. The final topology of the realised CPE is shown in

Figure 14.

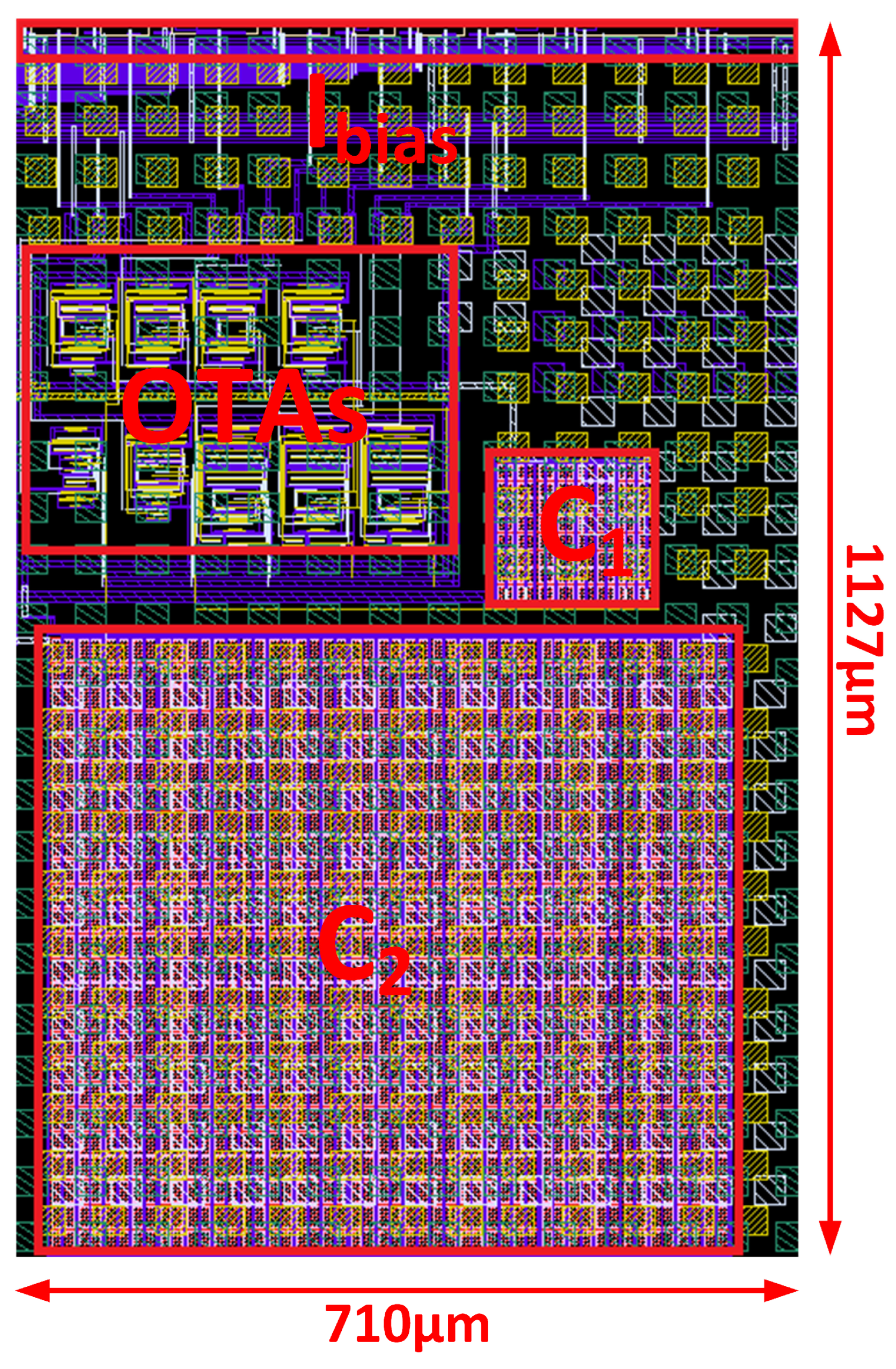

The MOSFET transistors used as nmos cells are NMOS4, which are designed with 4 fingers and 1 multiplier, and the pmos cells used are PMOS4, which are designed with 8 fingers and 1 multiplier from the PRIMLIB library in the AMS C35B4C3 technology. This technology has no defined multipliers, so instead of multipliers, unit transistors must be copied and connected in parallel. To reduce the influence of the process on the mismatch, the input diff pair has been designed for common centroid matching (A B B A/B A A B) and the current mirrors for interdigitation or linear centroid matching (C C B B A A A A B B C C); the current starts in the centre and flows in a line to the left and right.

The capacitors are realised as linear “cpoly” capacitors, whereby C1 is an 8 × 8 array of 64 unit cells with a capacitance of 156.25 fF (12.85 μm × 13.7 μm) and thus forms 10.0 pF. Capacitor C2 is a 25 × 25 array of 256 unit cells with a capacitance of 346.6 fF (19.5 μm × 20.25 μm) and thus forms 216.56 pF.

In our design, we chose the following bias currents Ibias for MOS transistors in OTAs:

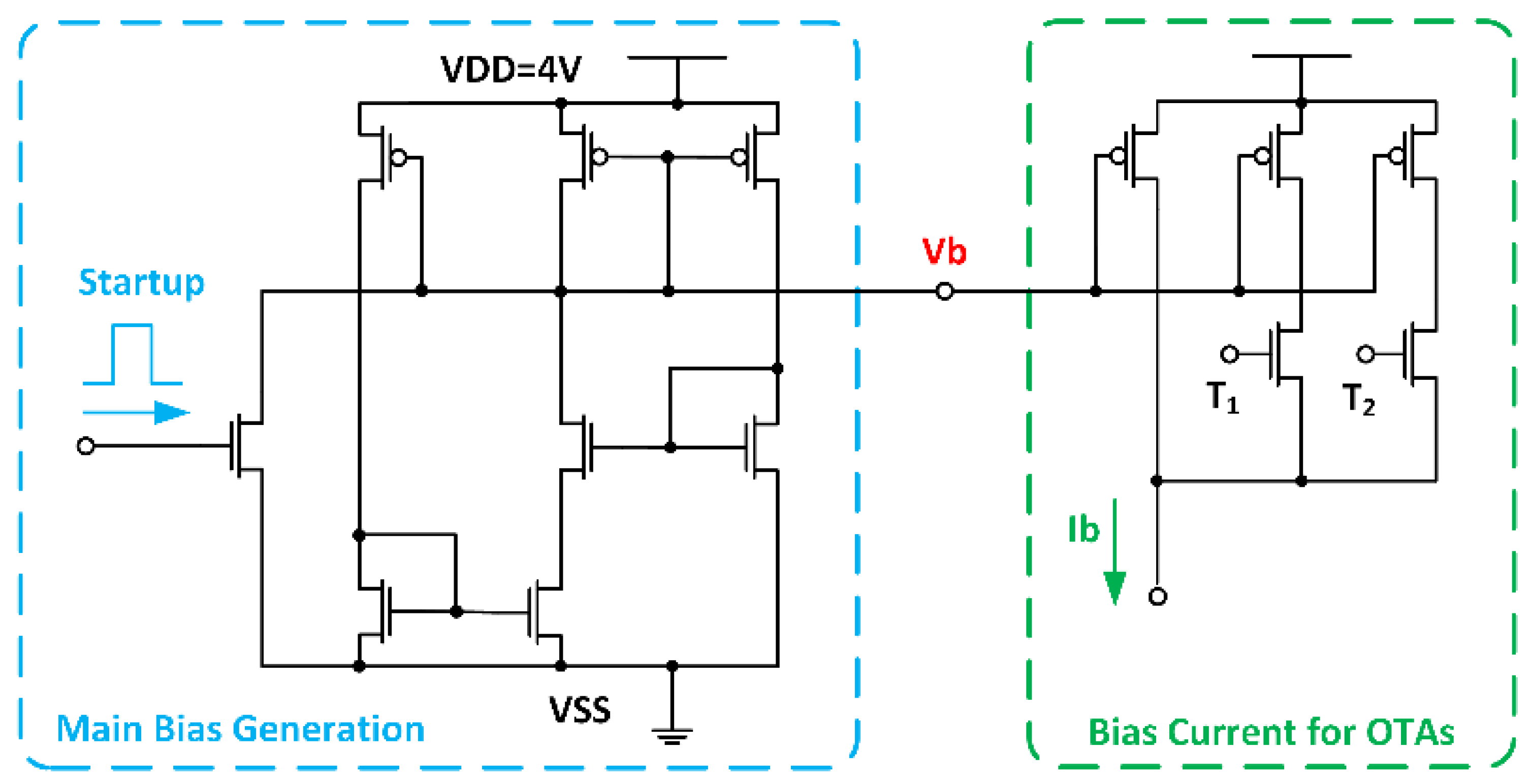

The circuit in

Figure 15 is used to provide bias currents. The main bias generation circuit (blue block) is used to generate a stable bias current, which is later mirrored (green block) with a factor suitable for the individual OTAs. Since each OTA needs 3 different currents to implement different phases (30°, 45°, and 60°), the mirroring factor can be digitally controlled with 2 bits (T1 and T2). A manual startup was implemented as a failsafe mechanism to ensure the necessary initial conditions.

The whole system was implemented in the AMS 350 nm technology node using Cadence Virtuoso tools for the design process. The layout showing the size and location of the subcircuits is presented in

Figure 16, indicating a total area of 710 × 1127 µm

2. The post-layout study with corresponding simulated results was conducted as a proof of concept, and it is presented in the following

Section 4.