A Broadband Three-Way Series Doherty Power Amplifier with Deep Power Back-Off Efficiency Enhancement for 5G Application

Abstract

1. Introduction

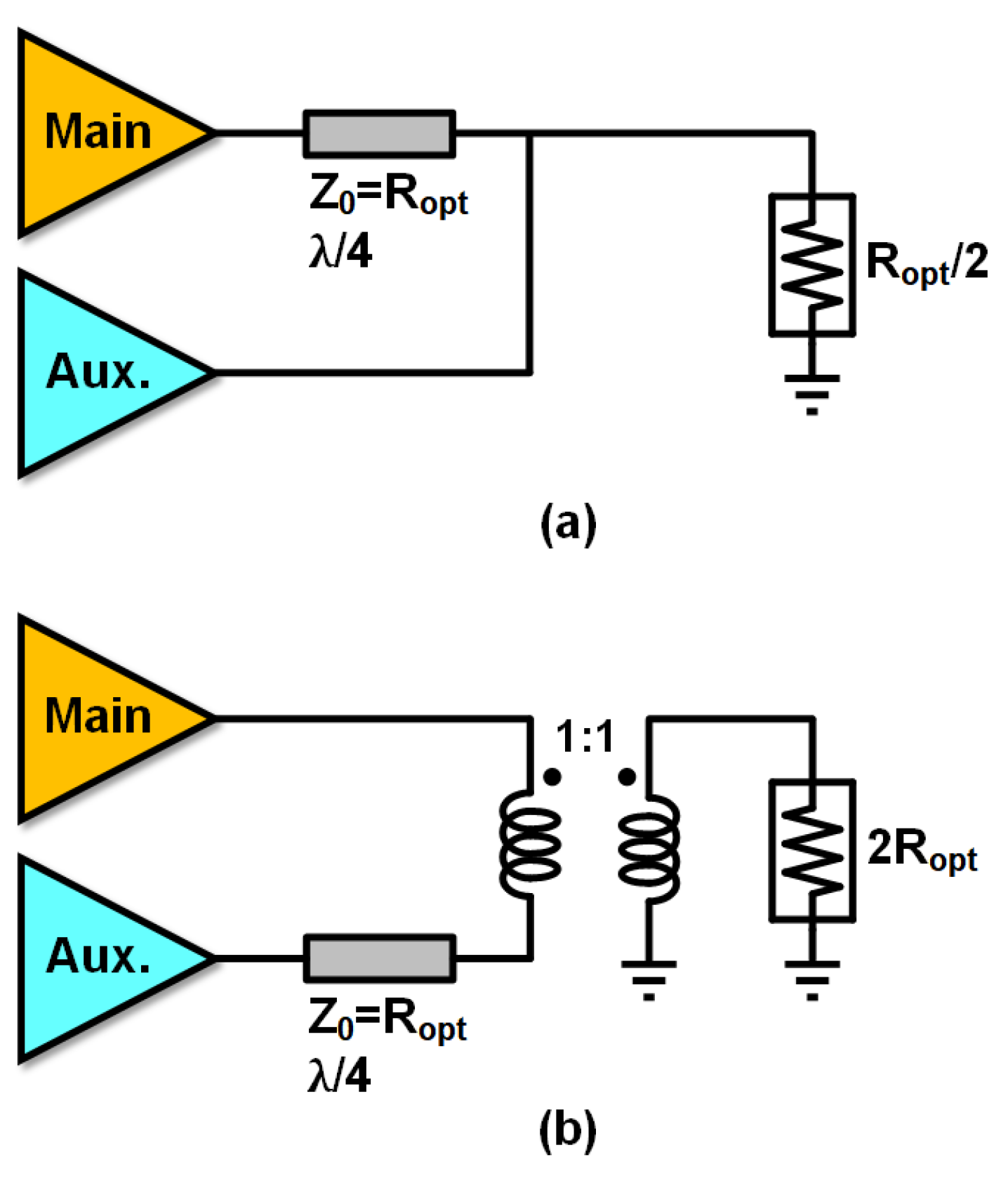

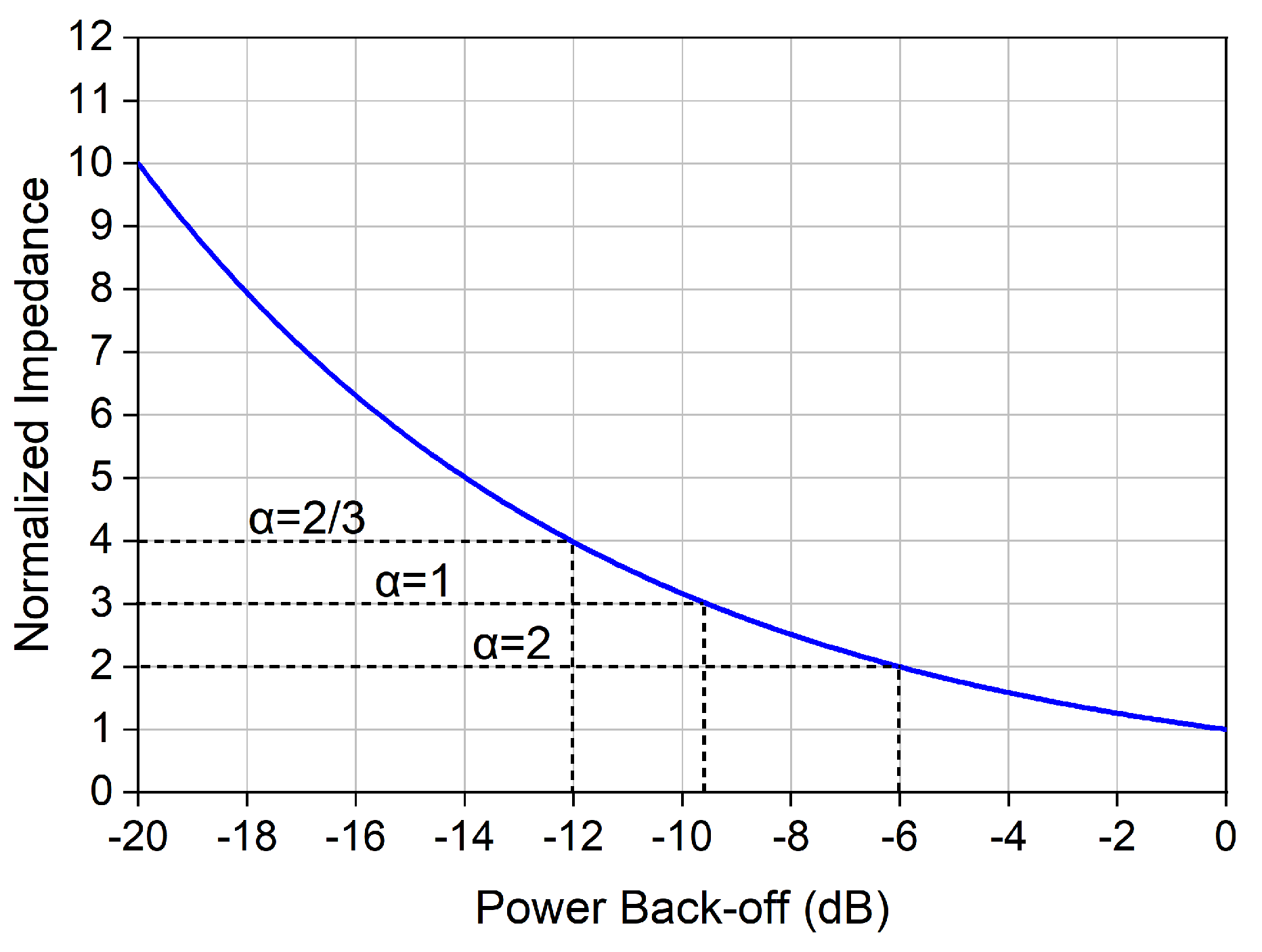

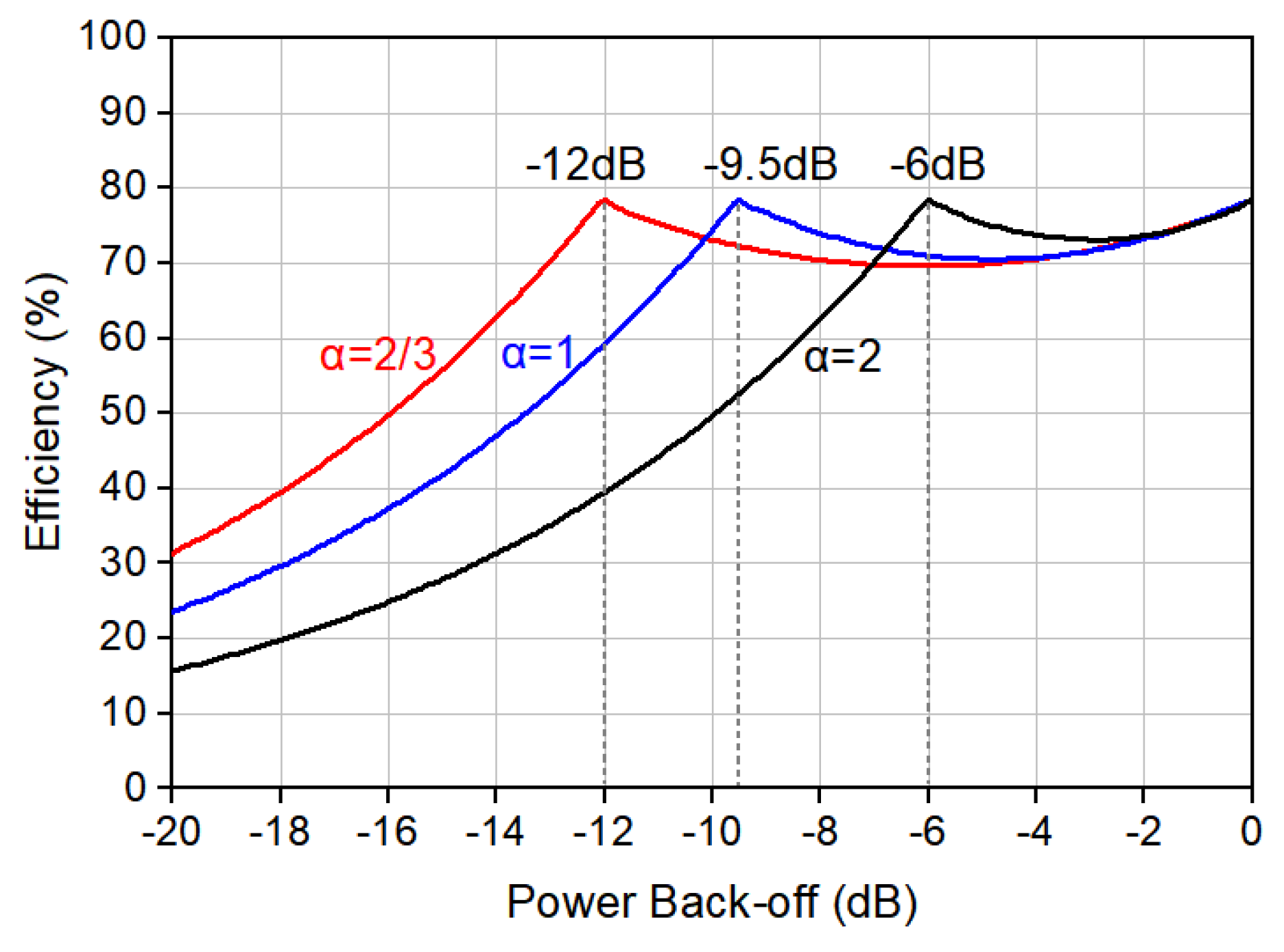

2. Analysis of Proposed Three-Way DPA

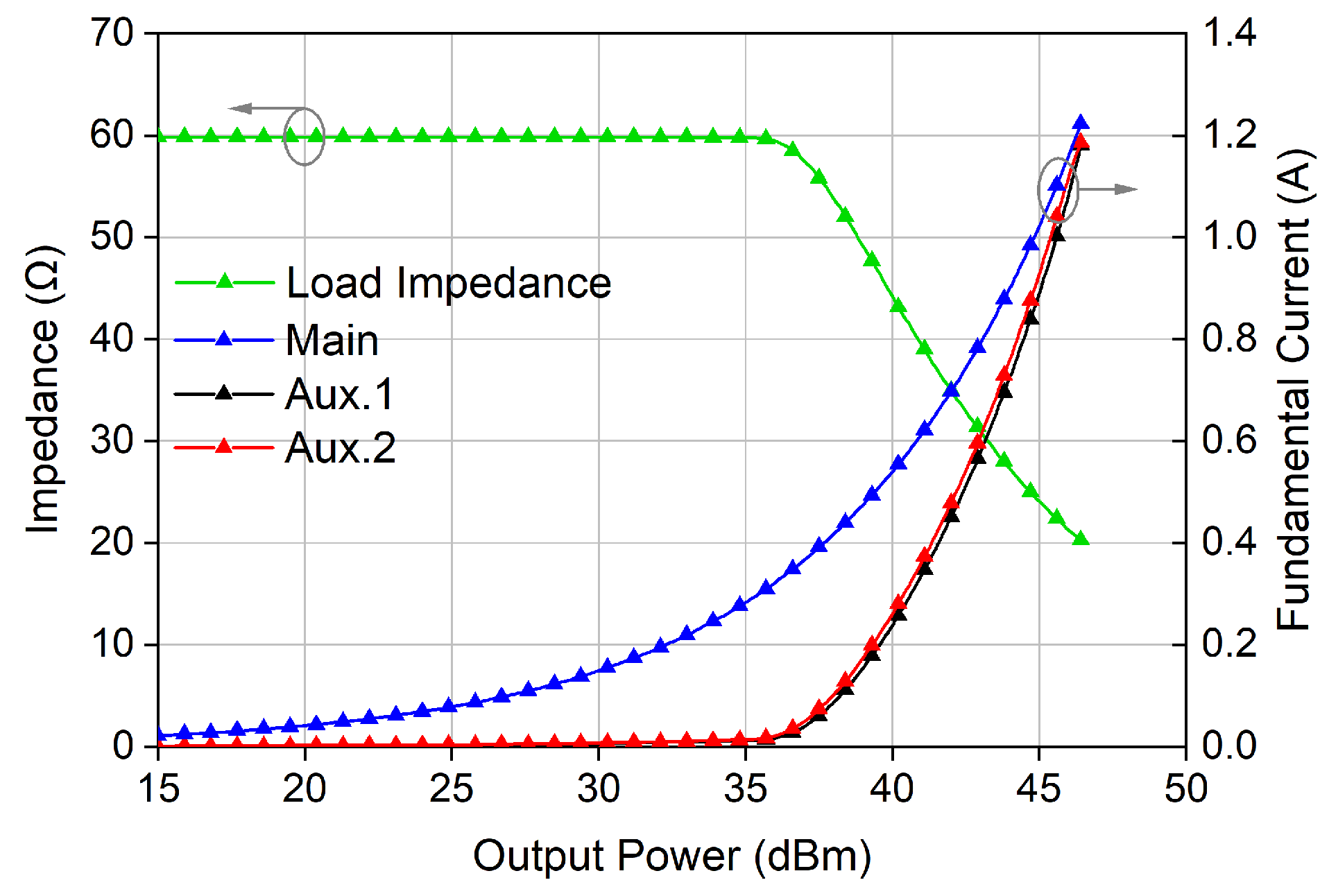

2.1. Load Modulation Analysis

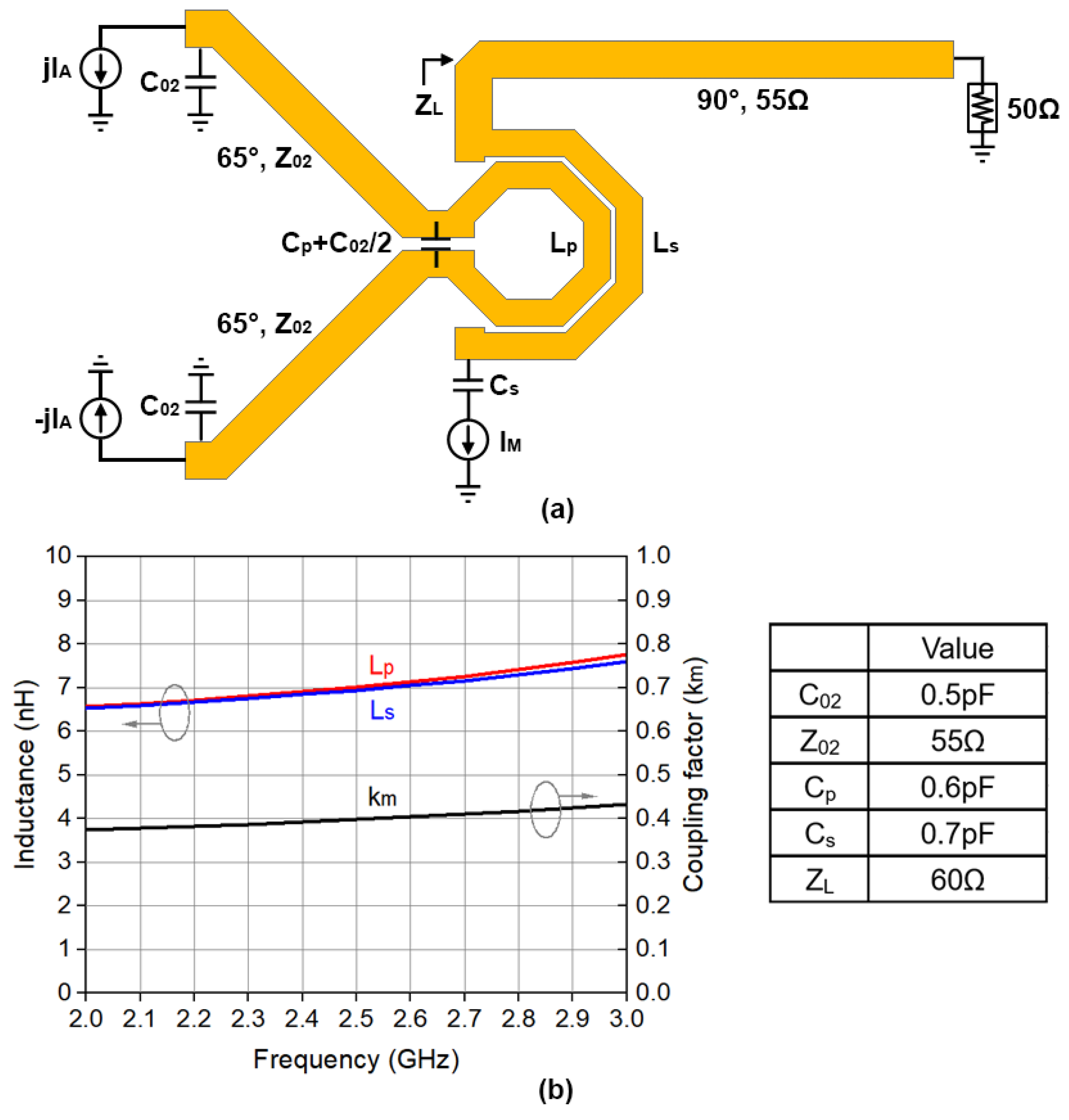

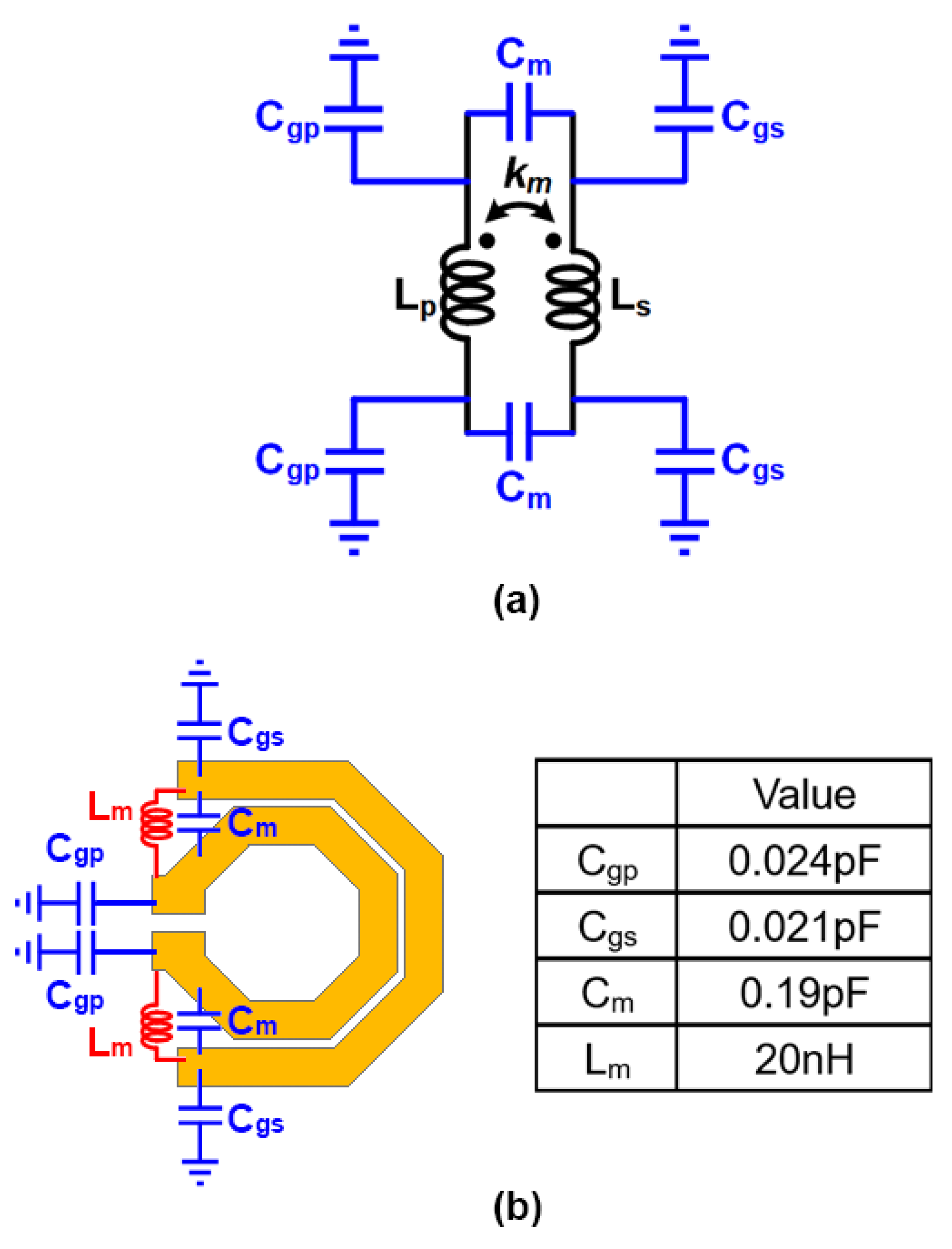

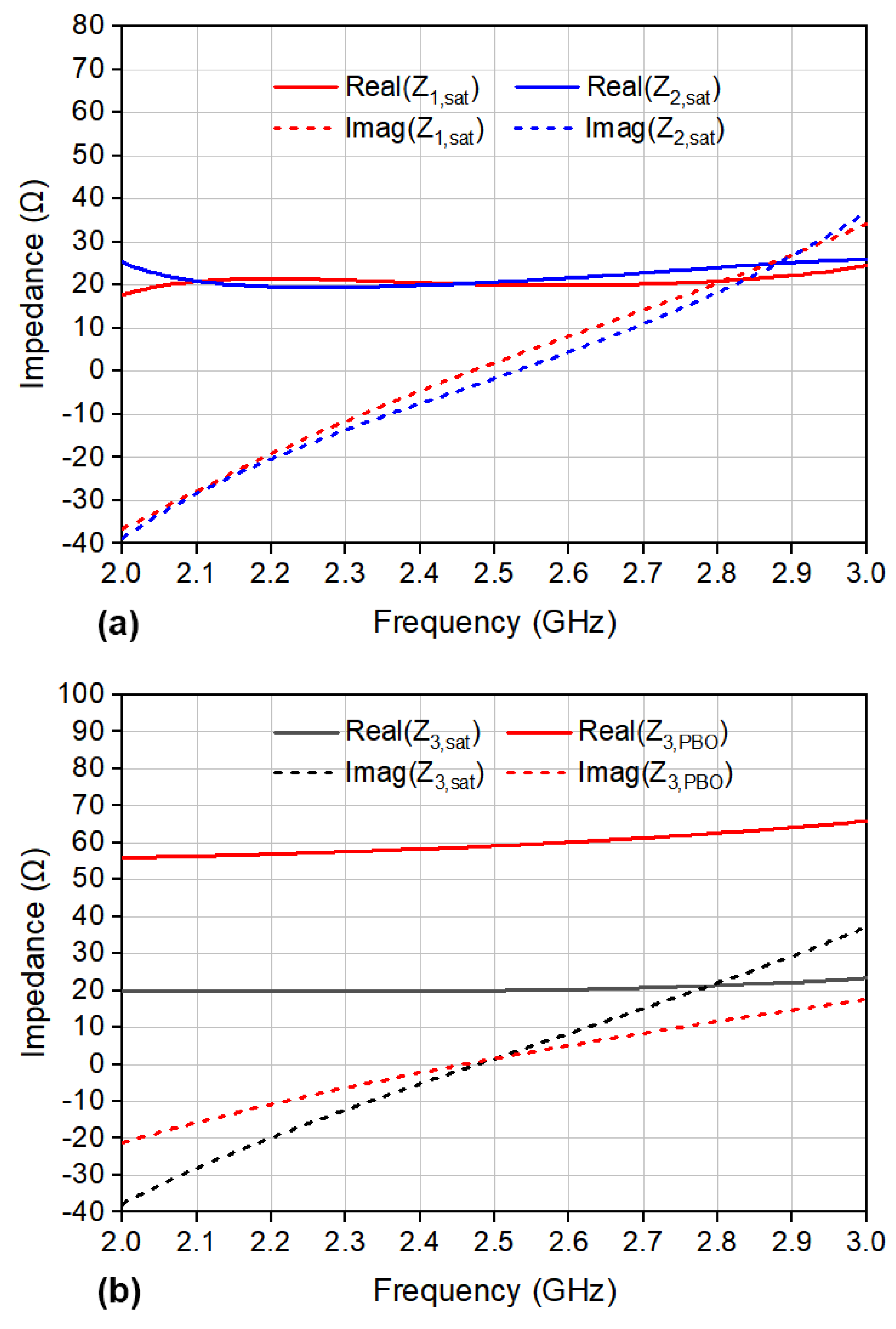

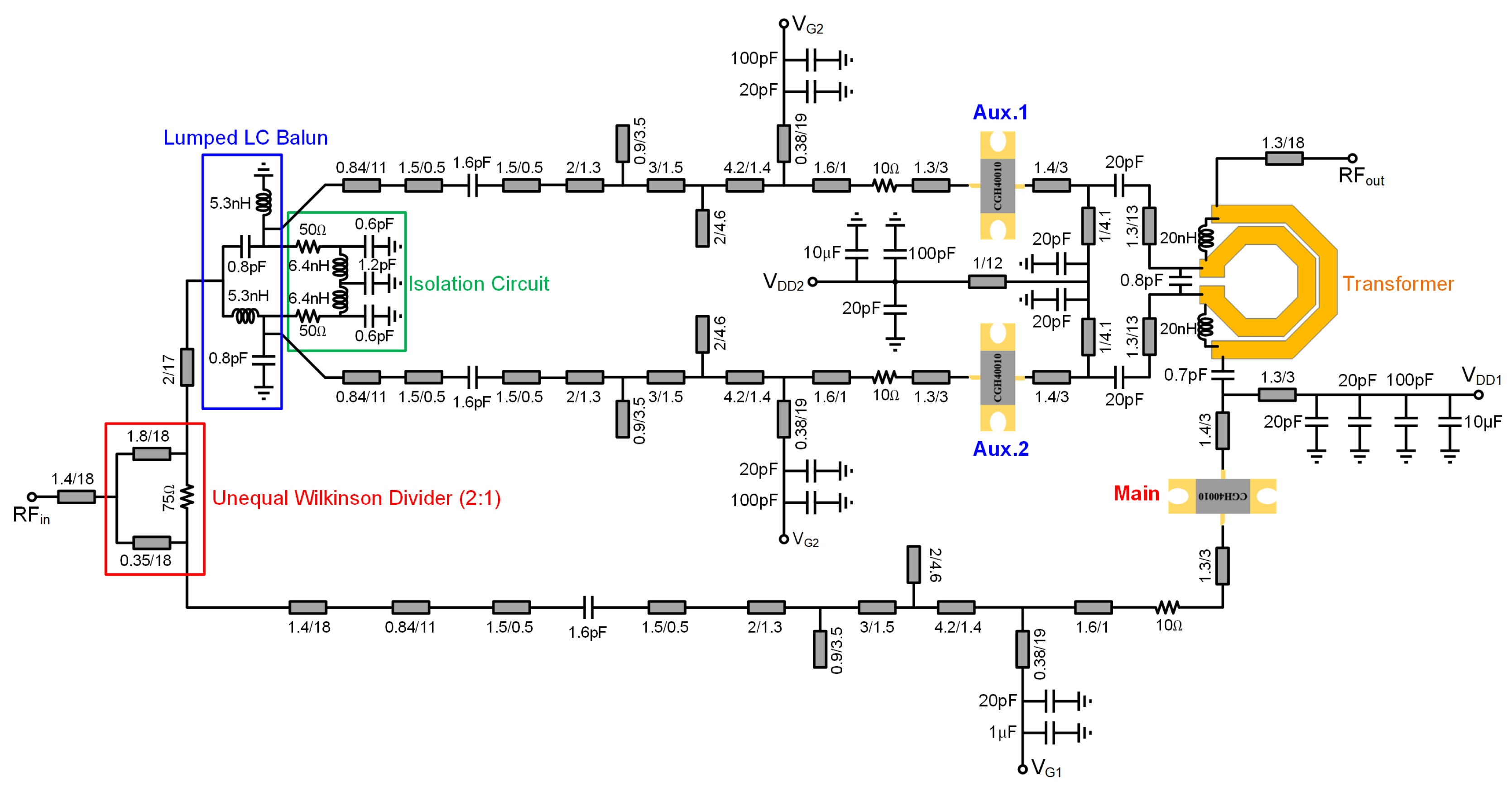

2.2. Implementation

3. Design Procedure

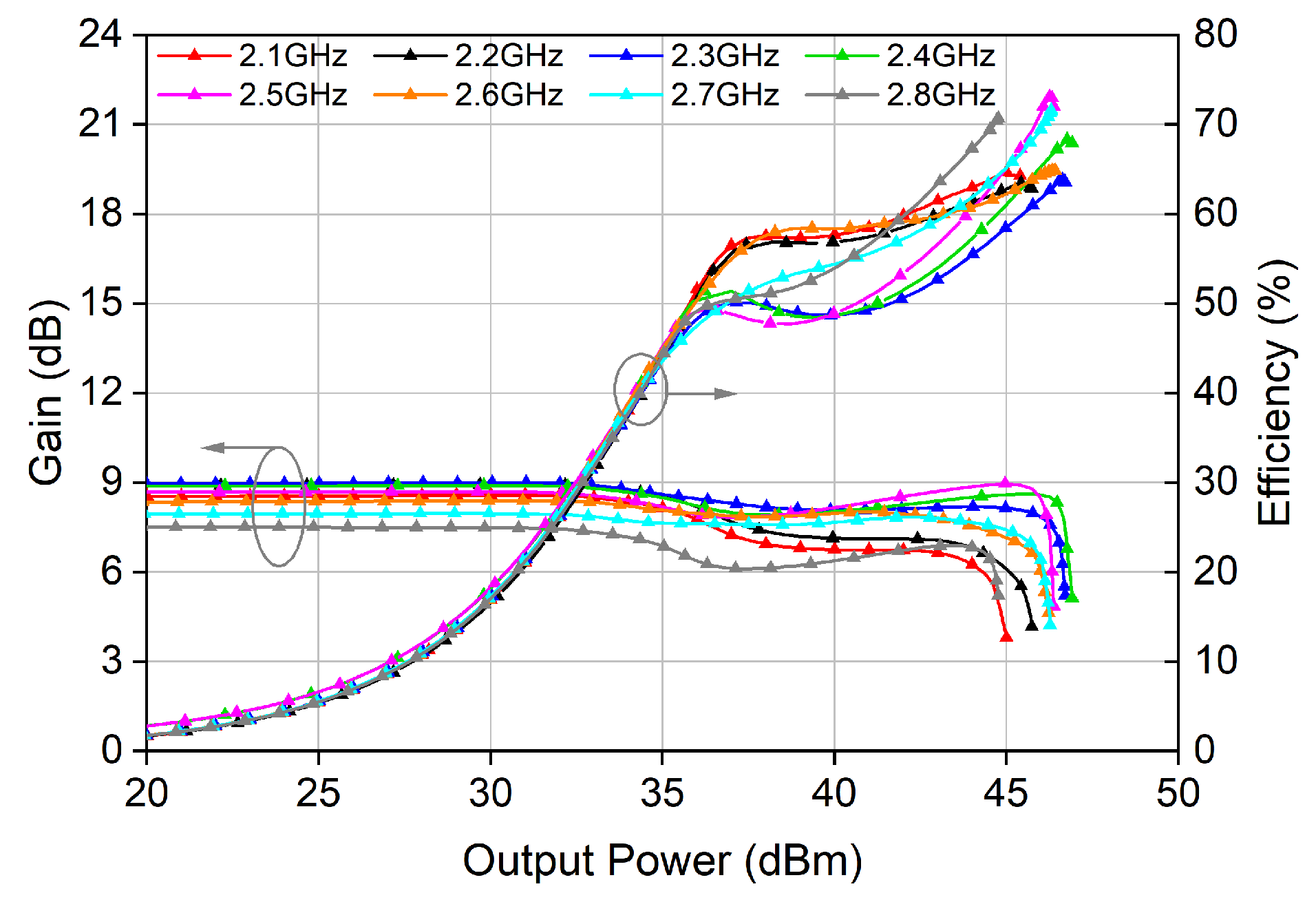

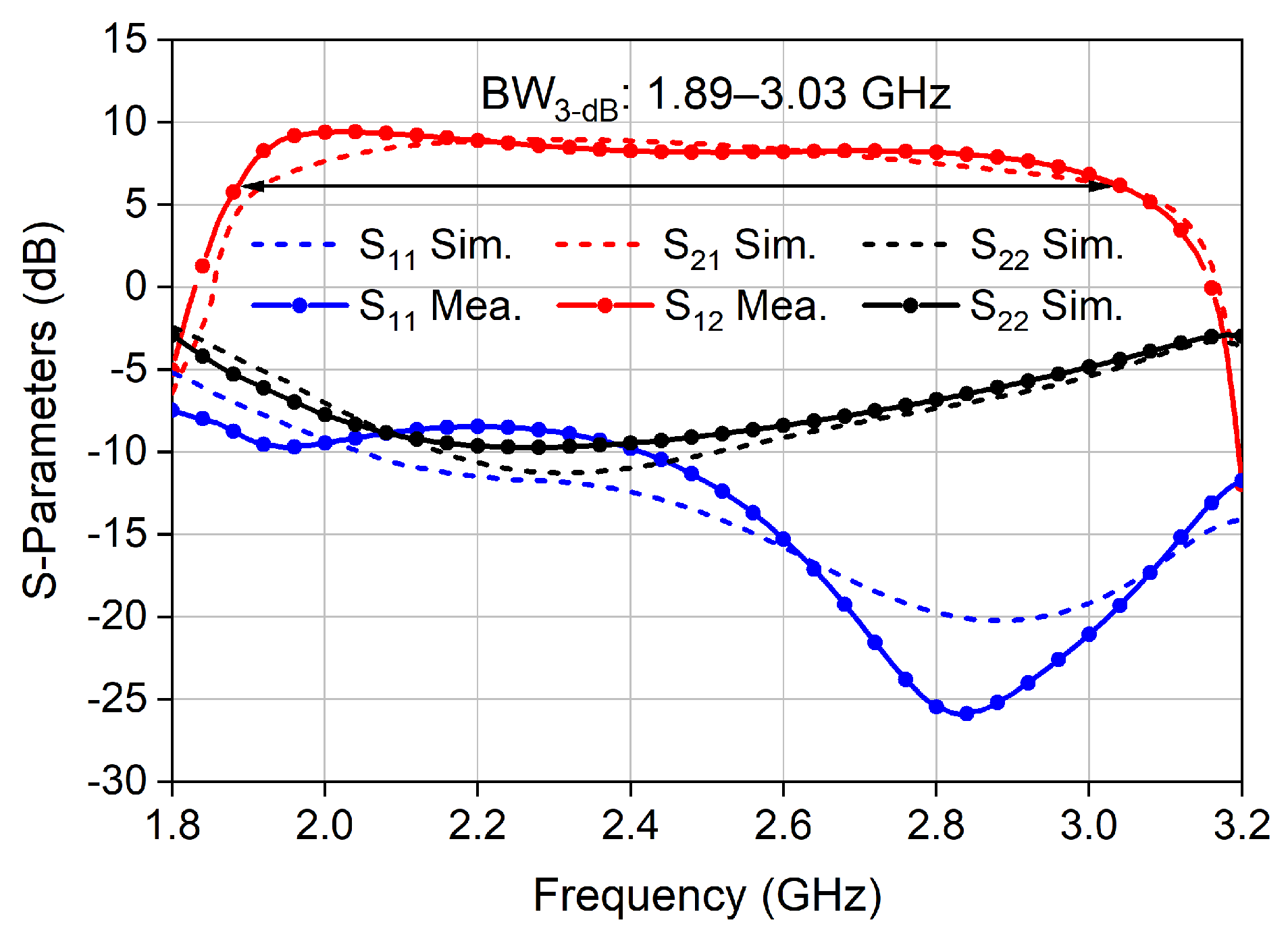

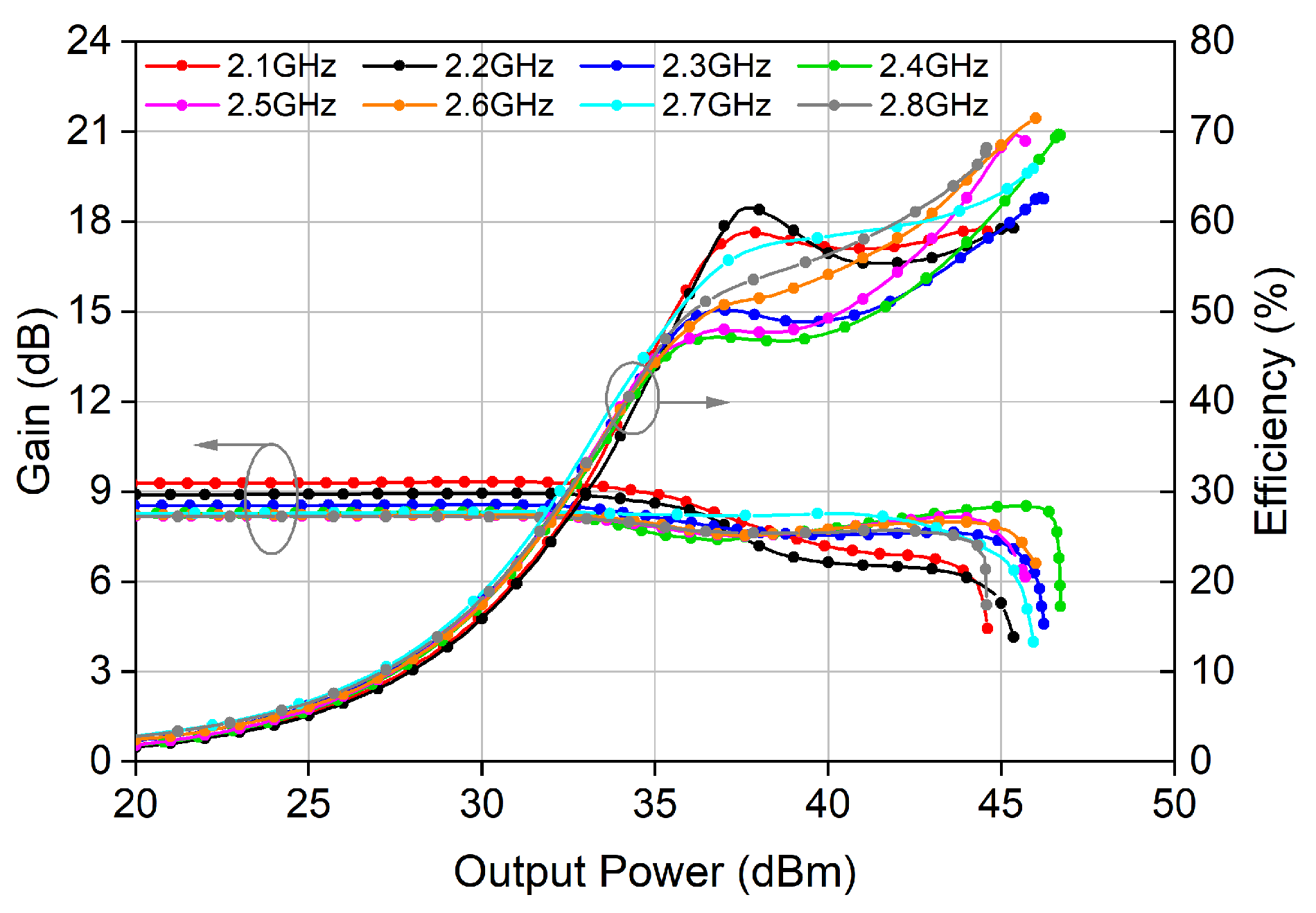

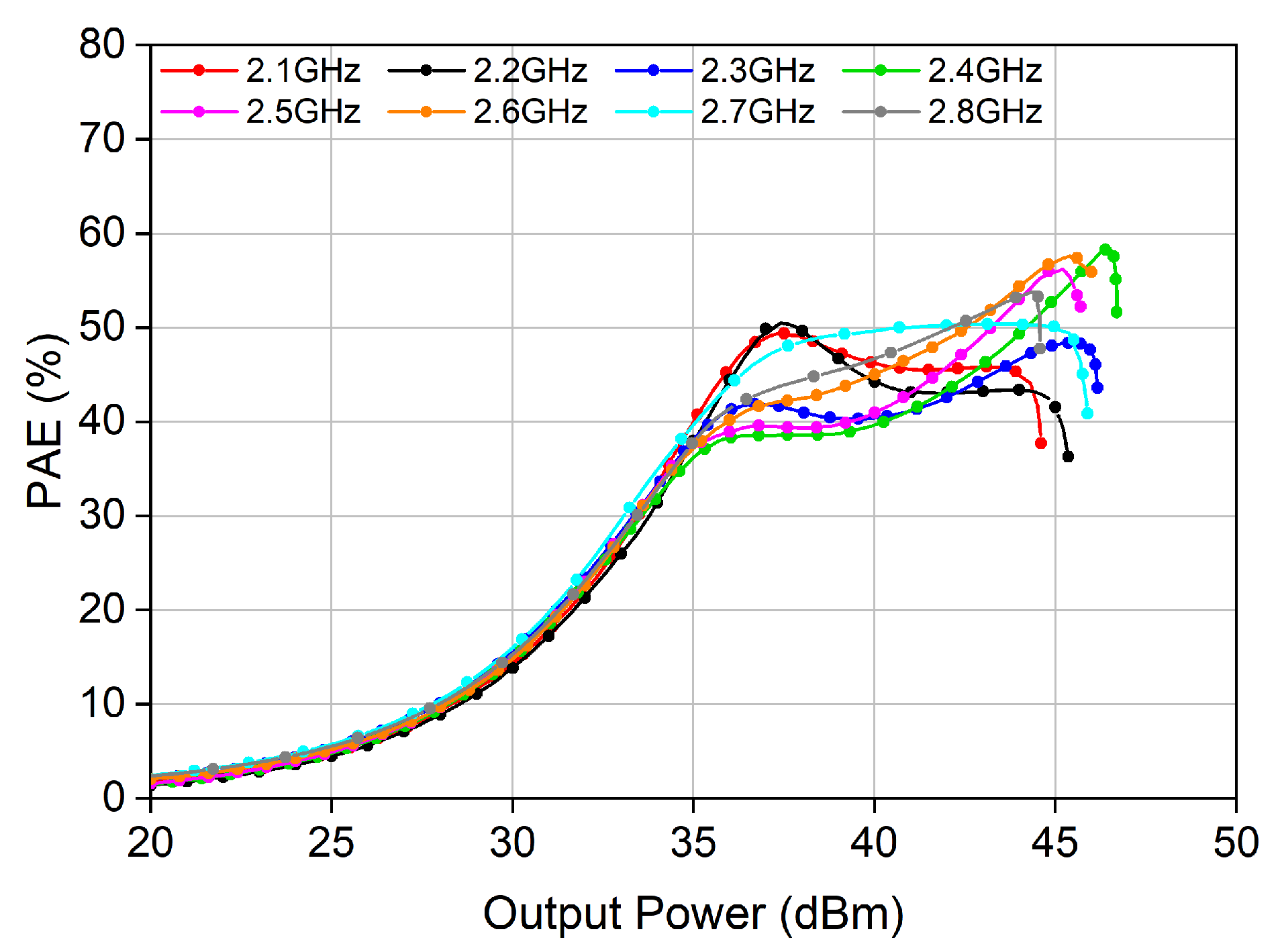

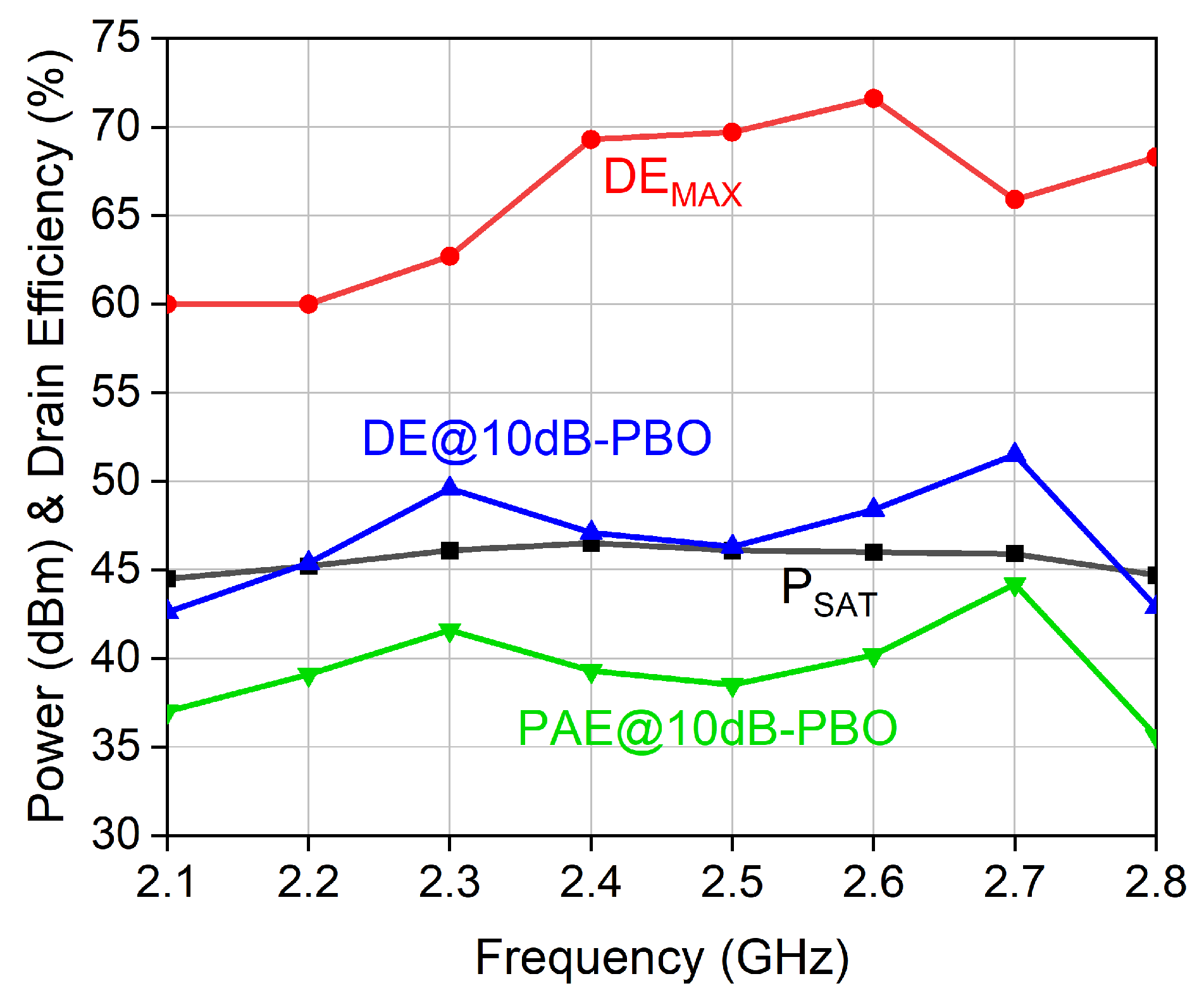

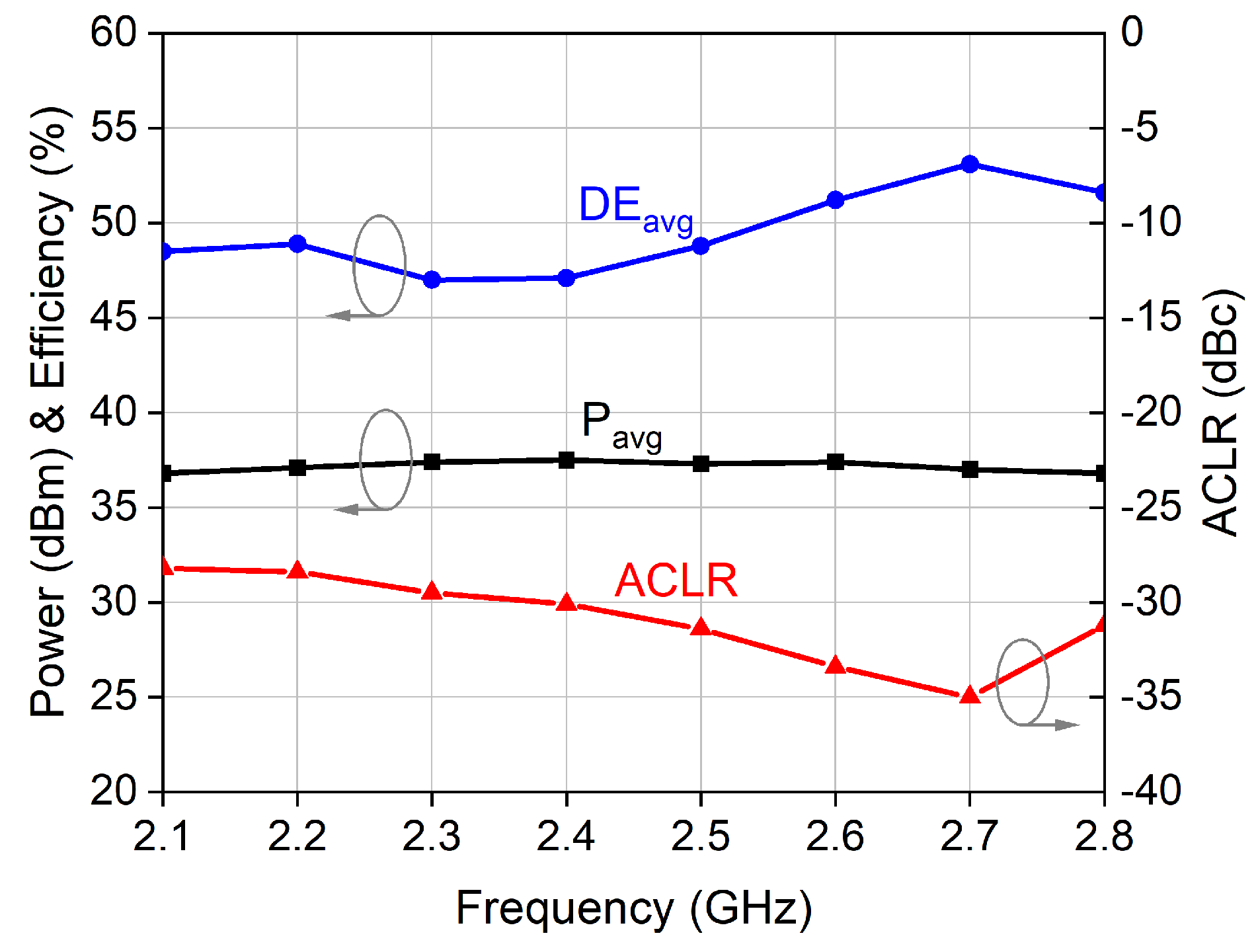

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Yang, B.; Yu, Z.; Lan, J.; Zhang, R.; Zhou, J.; Hong, W. Digital beamforming-based massive MIMO transceiver for 5G millimeter-wave communications. IEEE Trans. Microw. Theory Techn. 2018, 66, 3403–3418. [Google Scholar] [CrossRef]

- Zaidi, A.; Baldemair, R.; Molés-Cases, V.; He, N.; Werner, K.; Cedergren, A. OFDM numerology design for 5G new radio to support IoT, eMBB, and MBSFN. IEEE Commun. Stand. Mag. 2018, 2, 78–83. [Google Scholar] [CrossRef]

- Wang, F.; Wang, H. A broadband linear ultra-compact mm-wave power amplifier with distributed-balun output network: Analysis and design. IEEE J. Solid-State Circuits 2021, 56, 2308–2323. [Google Scholar] [CrossRef]

- Garay, E.F.; Munzer, D.J.; Wang, H. A mm-wave power amplifier for 5G communication using a dual-drive topology exhibiting a maximum PAE of 50% and maximum DE of 60% at 30GHz. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 13–22 February 2021; pp. 258–260. [Google Scholar]

- Park, H.-C.; Kim, S.; Lee, J.; Jung, J.; Baek, S.; Kim, T.; Kang, D.; Minn, D.; Yang, S.-G. Single transformer-based compact Doherty power amplifiers for 5G RF phased-array ICs. IEEE J. Solid-State Circuits 2022, 57, 1267–1279. [Google Scholar] [CrossRef]

- de Almeida, J.V.; Gu, X.; Hussain, I.; Wu, K. High-efficiency moderate-power amplifier using packaged GaN transistor with improved average PAE and gain for batteryless IoT applications. IEEE Trans. Microw. Theory Techn. 2023, 71, 628–639. [Google Scholar] [CrossRef]

- Cho, Y.; Kang, D.; Kim, J.; Moon, K.; Park, B.; Kim, B. Linear Doherty power amplifier with an enhanced back-off efficiency mode for handset applications. IEEE Trans. Microw. Theory Techn. 2014, 62, 567–578. [Google Scholar] [CrossRef]

- Pashaeifar, M.; de Vreede, L.C.; Alavi, M.S. A millimeter-wave CMOS series-Doherty power amplifier with post-silicon inter-stage passive validation. IEEE J. Solid-State Circuits 2022, 57, 2999–3013. [Google Scholar] [CrossRef]

- Zong, Z.; Tang, X.; Khalaf, K.; Yan, D.; Mangraviti, G.; Nguyen, J.; Liu, Y.; Wambacq, P. A 28-GHz SOI-CMOS Doherty power amplifier with a compact transformer-based output combiner. IEEE Trans. Microw. Theory Techn. 2021, 69, 2795–2808. [Google Scholar] [CrossRef]

- Cho, Y.; Moon, K.; Park, B.; Kim, J.; Kim, B. Voltage-combined CMOS Doherty power amplifier based on transformer. IEEE Trans. Circuits Syst. II Exp. Briefs 2016, 64, 3612–3622. [Google Scholar] [CrossRef]

- Zhao, C.; Liu, H.; Wu, Y.; Kang, K. Analysis and design of CMOS Doherty power amplifier based on voltage combining method. IEEE Access 2017, 5, 5001–5012. [Google Scholar] [CrossRef]

- Mortazavi, M.; Shen, Y.; Mul, D.; de Vreede, L.C.N.; Spirito, M.; Babaie, M. A four-way series Doherty digital polar transmitter at mm-wave frequencies. IEEE J. Solid-State Circuits 2022, 57, 803–817. [Google Scholar] [CrossRef]

- Wang, F.; Wang, H. A high-power broadband multi-primary DAT-based Doherty power amplifier for mm-wave 5G applications. IEEE J. Solid-State Circuits 2021, 56, 1668–1681. [Google Scholar] [CrossRef]

- Li, J.; Yin, Y.; Chen, H.; Lin, J.; Li, Y.; Jia, X.; Hu, Z.; Liu, Z.; Zhang, X.; Xu, H. A transformer-based quadrature Doherty digital power amplifier with 4.1 W peak power in 28 nm bulk CMOS. J. Solid-State Circuits 2023, 58, 3296–3307. [Google Scholar] [CrossRef]

- Shi, W.; Shi, W.; Peng, J.; Feng, L.; Gao, Y.; He, S.; Yue, C.P. Design and analysis of continuous-mode Doherty power amplifier with second harmonic control. IEEE Trans. Circuits Syst. II Exp. Briefs 2021, 68, 2247–2251. [Google Scholar] [CrossRef]

- Liu, R.-J.; Zhu, X.-W.; Xia, J.; Zhao, Z.-M.; Dong, Q.; Chen, P.; Zhang, L.; Jiang, X.; Yu, C.; Hong, W. A 24-28-GHz GaN MMIC synchronous Doherty power amplifier with enhanced load modulation for 5G mm-wave applications. IEEE Trans. Microw. Theory Techn. 2022, 70, 3910–3922. [Google Scholar] [CrossRef]

- Nasri, A.; Estebsari, M.; Toofan, S.; Piacibello, A.; Pirola, M.; Camarchia, V.; Ramella, C. Design of a wideband Doherty power amplifier with high efficiency for 5G application. Electronics 2021, 10, 873. [Google Scholar] [CrossRef]

- Donati Guerrieri, S.; Catoggio, E.; Bonani, F. Analysis of Doherty power amplifier matching assisted by physics-based device modelling. Electronics 2023, 12, 2101. [Google Scholar] [CrossRef]

- Liang, C.; Roblin, P.; Hahn, Y.; Martinez-Lopez, J.I.; Chang, H.-C.; Chen, V. Single-input broadband hybrid Doherty power amplifiers design relying on a phase sliding-mode of the load modulation scheme. IEEE Trans. Microw. Theory Techn. 2023, 71, 1550–1562. [Google Scholar] [CrossRef]

- Grebennikov, A. A high-efficiency 100-W four-stage Doherty GaN HEMT power amplifier module for WCDMA systems. In Proceedings of the 2011 IEEE MTT-S International Microwave Symposium, Baltimore, MD, USA, 5–10 June 2011; pp. 1–10. [Google Scholar]

- Chen, S.; Wang, W.; Xu, K.; Wang, G. A reactance compensated three-device Doherty power amplifier for bandwidth and back-off range extension. Wirel. Commun. Mobile Comput. 2018, 2018, 8418165. [Google Scholar] [CrossRef]

- Zhou, H.; Perez-Cisneros, J.-R.; Hesami, S.; Buisman, K.; Fager, C. A generic theory for design of efficient three-stage Doherty power amplifiers. IEEE Trans. Microw. Theory Techn. 2022, 70, 1242–1253. [Google Scholar] [CrossRef]

- Dietrich, F.; Wei, M.-D.; Heidebrecht, E.; Bierbüsse, D.; Negra, R. Load and frequency independent Doherty power amplifier back-off extension. IEEE Trans. Microw. Theory Techn. 2024; in press. [Google Scholar] [CrossRef]

- Pang, J.; Li, Y.; Li, M.; Zhang, Y.; Zhou, X.Y.; Dai, Z.; Zhu, A. Analysis and design of highly efficient wideband RF-input sequential load modulated balanced power amplifier. IEEE Trans. Microw. Theory Techn. 2020, 68, 1741–1753. [Google Scholar] [CrossRef]

- Sun, J.; Lin, F.; Sun, H.; Chen, W.; Negra, R. Broadband three-stage pseudoload modulated balanced amplifier with power back-off efficiency enhancement. IEEE Trans. Microw. Theory Techn. 2022, 70, 2710–2722. [Google Scholar] [CrossRef]

- Quaglia, R.; Cripps, S. A load modulated balanced amplifier for telecom applications. IEEE Trans. Microw. Theory Techn. 2018, 66, 1328–1338. [Google Scholar] [CrossRef]

- Cao, Y.; Chen, K. Pseudo-Doherty load-modulated balanced amplifier with wide bandwidth and extended power back-off range. IEEE Trans. Microw. Theory Techn. 2020, 68, 3172–3183. [Google Scholar] [CrossRef]

- Cao, Y.; Chen, K. Hybrid asymmetrical load modulated balanced amplifier with wide bandwidth and three-way-Doherty efficiency enhancement. IEEE Trans. Microw. Theory Techn. 2021, 31, 721–724. [Google Scholar] [CrossRef]

- Chu, C.; Sharma, T.; Dhar, S.K.; Darraji, R.; Wang, X.; Pang, J.; Zhu, A. Waveform engineered sequential load modulated balanced amplifier with continuous Class-F-1 and Class-J operation. IEEE Trans. Microw. Theory Techn. 2022, 70, 1269–1283. [Google Scholar] [CrossRef]

- Que, X.; Wang, Y.; Huang, S. A 6-/12-dB back-off reconfigurable Doherty-like load modulated balanced amplifier with compact area and wide bandwidth. Microelectron. J. 2024, 148, 106198. [Google Scholar] [CrossRef]

- Maktoomi, M.H.; Ren, H.; Marbell, M.N.; Klein, V.; Wilson, R.; Arigong, B. A wideband isolated real-to-complex impedance transforming uniplanar microstrip line balun for push–pull power amplifier. IEEE Trans. Microw. Theory Techn. 2020, 68, 4560–4569. [Google Scholar] [CrossRef]

- Smolarz, R.; Gruszczynski, S.; Wincza, K. Multisection ultra-broadband directional coupler designed in MMIC technology. IEEE Access 2021, 9, 33478–33486. [Google Scholar] [CrossRef]

- Standard IPC-2221A; Generic Standard on Printed Board Design—A Standard Developed by IPC. IPC: Northbrook, IL, USA, 2003.

- El-Gharniti, O.; Kerherve, E.; Begueret, J.-B. Modeling and characterization of on-chip transformers for silicon RFIC. IEEE Trans. Microw. Theory Techn. 2007, 55, 607–615. [Google Scholar] [CrossRef]

| Ref. | Architecture | Freq. (GHz) | FBW (%) | Gain (dB) | (dBm) | (%) | OBO (dB) | DE@OBO (%) |

|---|---|---|---|---|---|---|---|---|

| This work | three-way series DPA | 2.1–2.8 | 28.6 | 8.2–9.3 | 44.5–46.5 | 60–72 | 10 | 43–52 |

| [21] | three-way parallel DPA | 2.0–2.6 | 26 | 8–12 | 43.6–45.4 | 53–76 | 8 | 41–48 |

| [22] | three-way parallel DPA | 2.04–2.24 | 9.3 | 8 | 43.7–45.3 | 50–68 | 10 | 29–56 |

| [23] | reflective-type DPA | 2.1–3.0 | 35 | 7.5–11 | 46.6–49 | 48–58 | 19/9 | 33–50 |

| [24] | SLMBA a | 3.05–3.55 | 15.2 | 9.5–10.3 | 42.3–43.7 | 61–75 | 10 | 43–51 |

| [25] | pseudo-LMBA | 1.6–2.0 | 22.2 | 8.5–9.7 | 43.4–44 | 65–75 | 10 | 49–62 |

| Ref. | Freq. (GHz) | Modulation | PAPR (dB) | (dBm) | (%) | (dBc) |

|---|---|---|---|---|---|---|

| This work | 2.1–2.8 | 20 MHz LTE | 8.5 | 36.8–37.5 | 47–53 | −35–−28.2 |

| [21] | 2.3 | 20 MHz LTE | 8 | 36.6 | 46 | −29 |

| [22] | 2.14 | 20 MHz LTE | 8.5 | 36.8 | 56.6 | −28.6 |

| [23] | 2.1–3.0 | 20 MHz LTE | 9 | 40 | 45–52 | −27–−23 |

| [24] | 3.05–3.55 | 40 MHz LTE | 8 | 35.5 | 57.8 | −26 |

| [25] | 1.6–2.0 | 20 MHz LTE | 10.32 | 33.6–34.5 | 42.8–54.6 | −30.76–−23.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Que, X.; Li, J.; Wang, Y. A Broadband Three-Way Series Doherty Power Amplifier with Deep Power Back-Off Efficiency Enhancement for 5G Application. Electronics 2024, 13, 1882. https://doi.org/10.3390/electronics13101882

Que X, Li J, Wang Y. A Broadband Three-Way Series Doherty Power Amplifier with Deep Power Back-Off Efficiency Enhancement for 5G Application. Electronics. 2024; 13(10):1882. https://doi.org/10.3390/electronics13101882

Chicago/Turabian StyleQue, Xianfeng, Jun Li, and Yanjie Wang. 2024. "A Broadband Three-Way Series Doherty Power Amplifier with Deep Power Back-Off Efficiency Enhancement for 5G Application" Electronics 13, no. 10: 1882. https://doi.org/10.3390/electronics13101882

APA StyleQue, X., Li, J., & Wang, Y. (2024). A Broadband Three-Way Series Doherty Power Amplifier with Deep Power Back-Off Efficiency Enhancement for 5G Application. Electronics, 13(10), 1882. https://doi.org/10.3390/electronics13101882