A Wide-Range Four-Phase All-Digital DLL with De-Skew Circuit

Abstract

1. Introduction

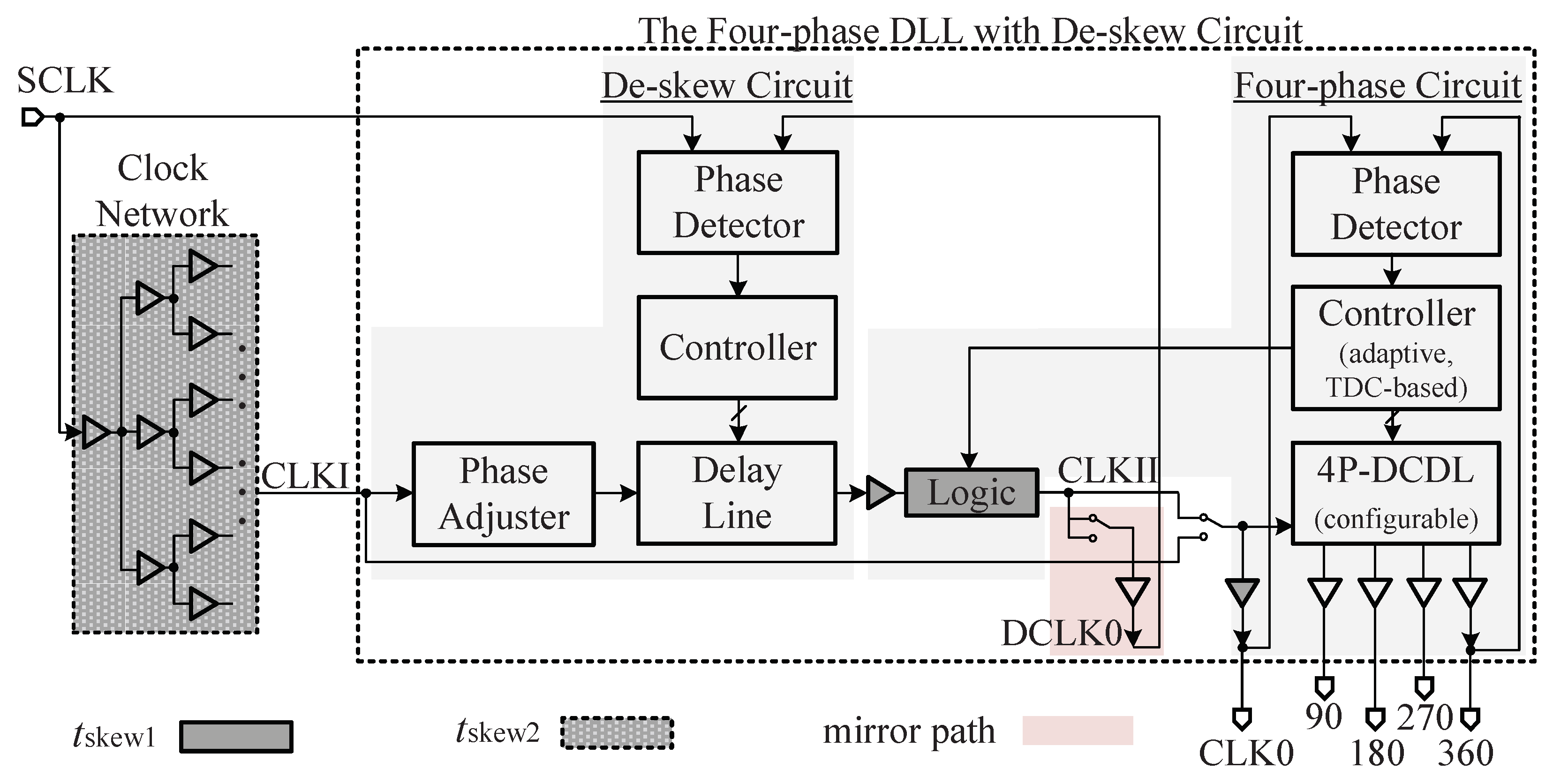

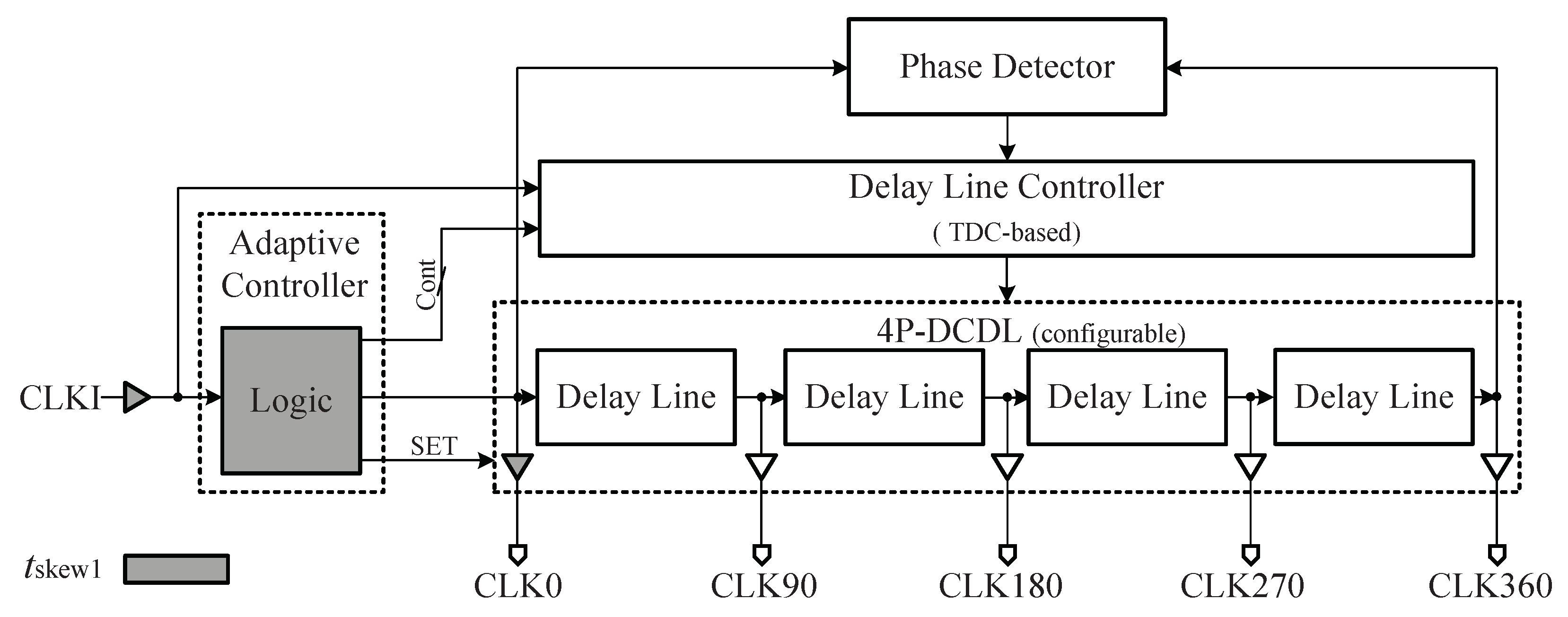

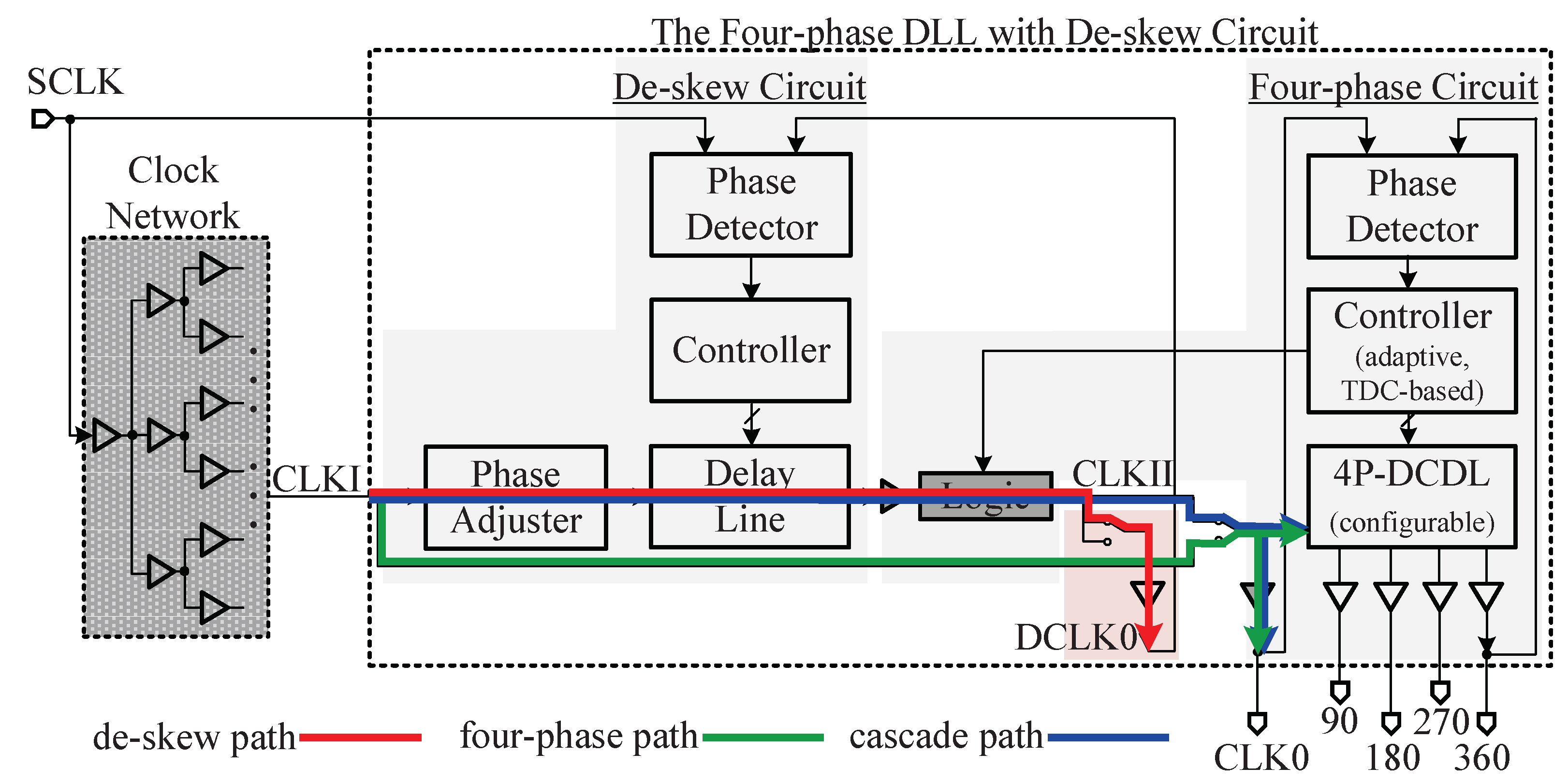

2. The Proposed Four-Phase All-Digital DLL with De-Skew Circuit Architecture

3. Critical Circuit Description

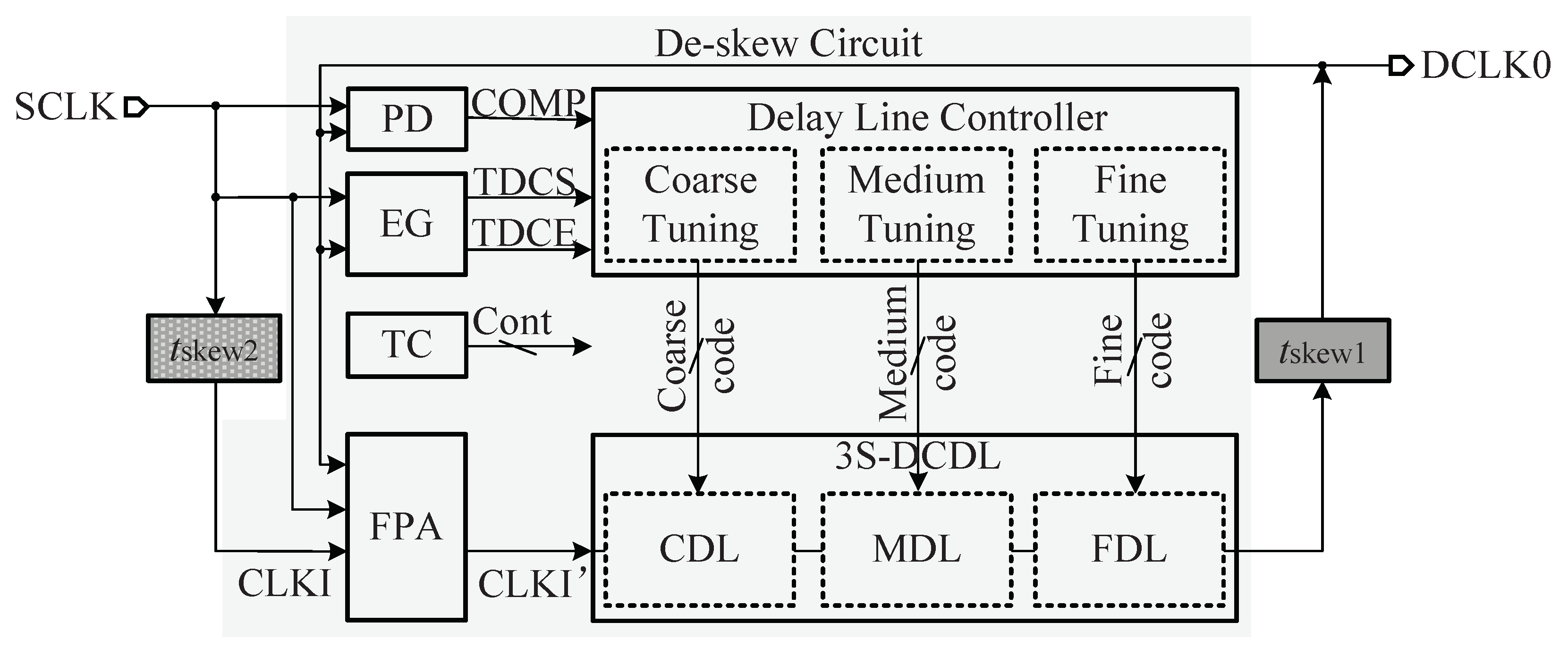

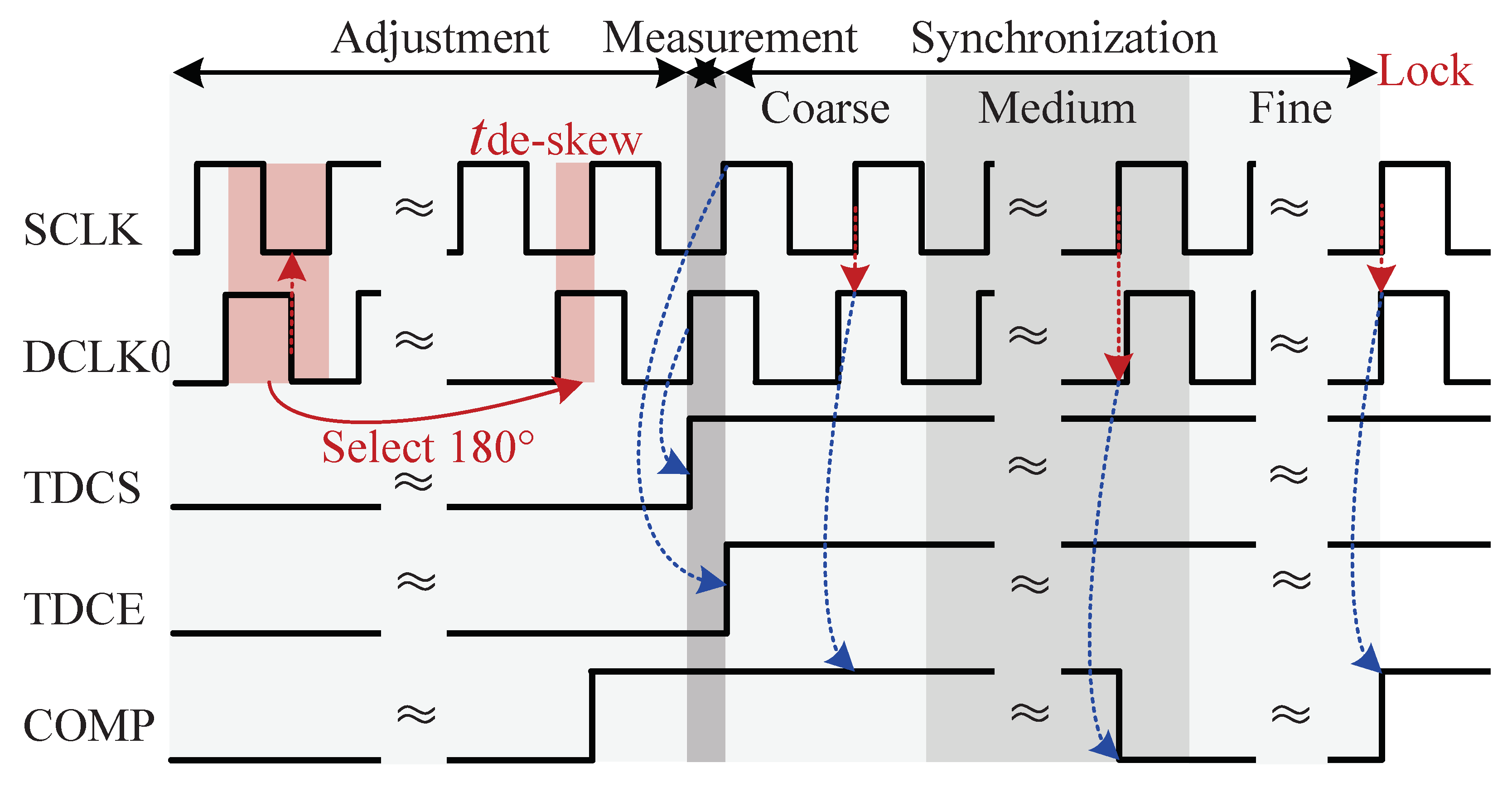

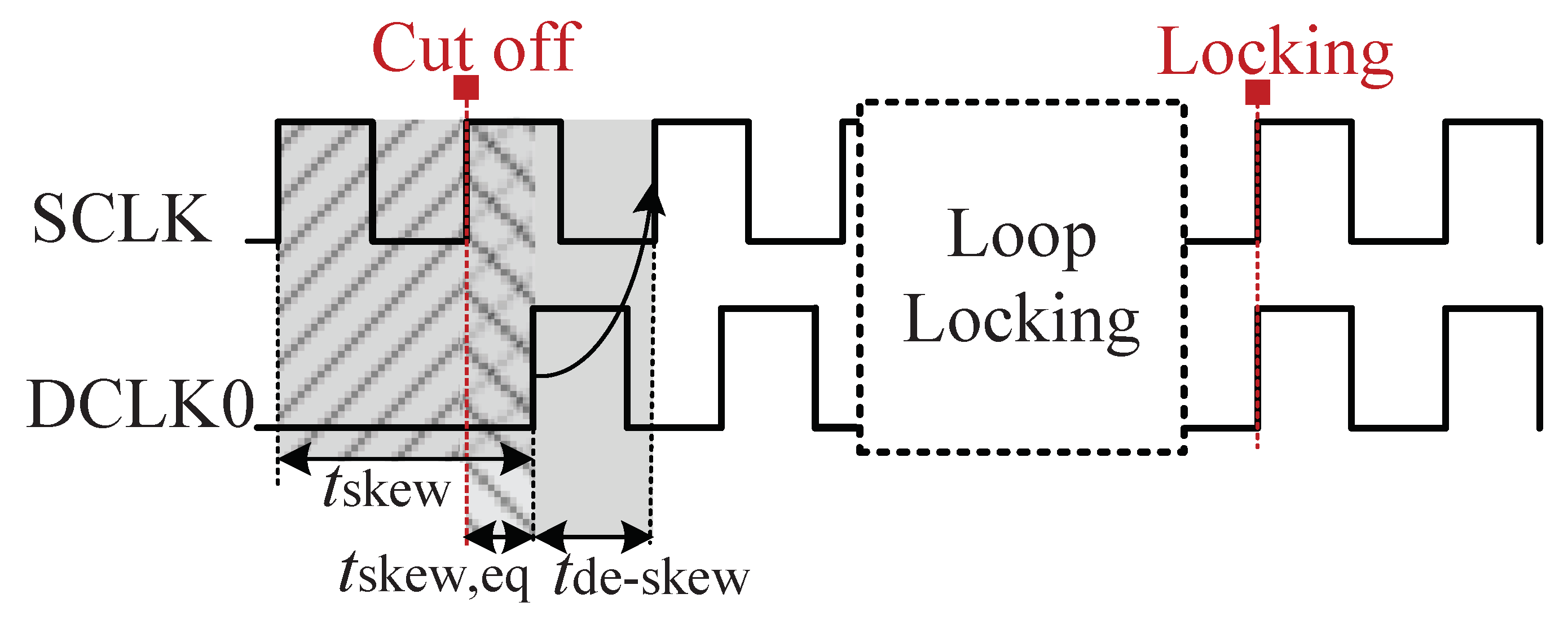

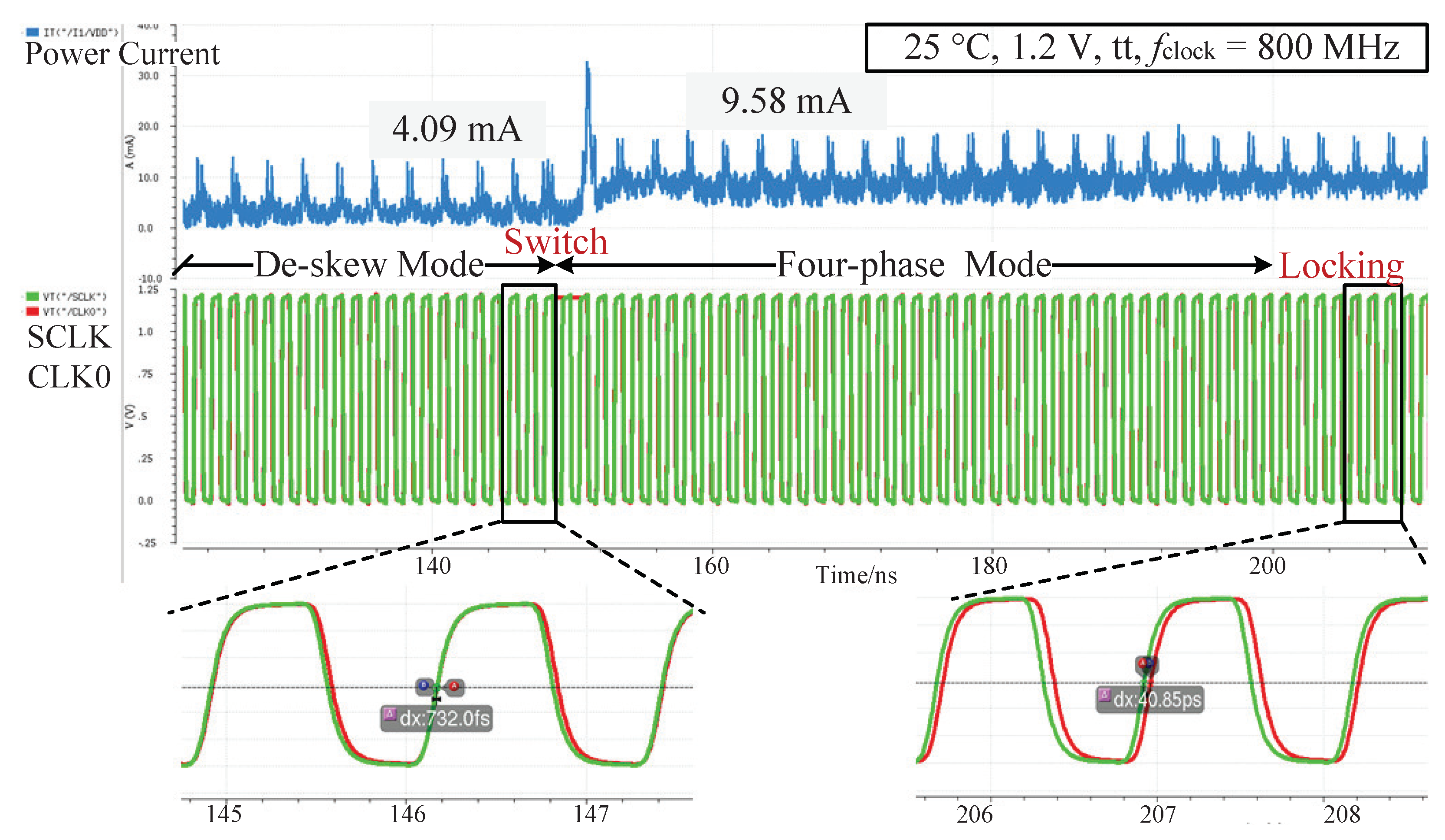

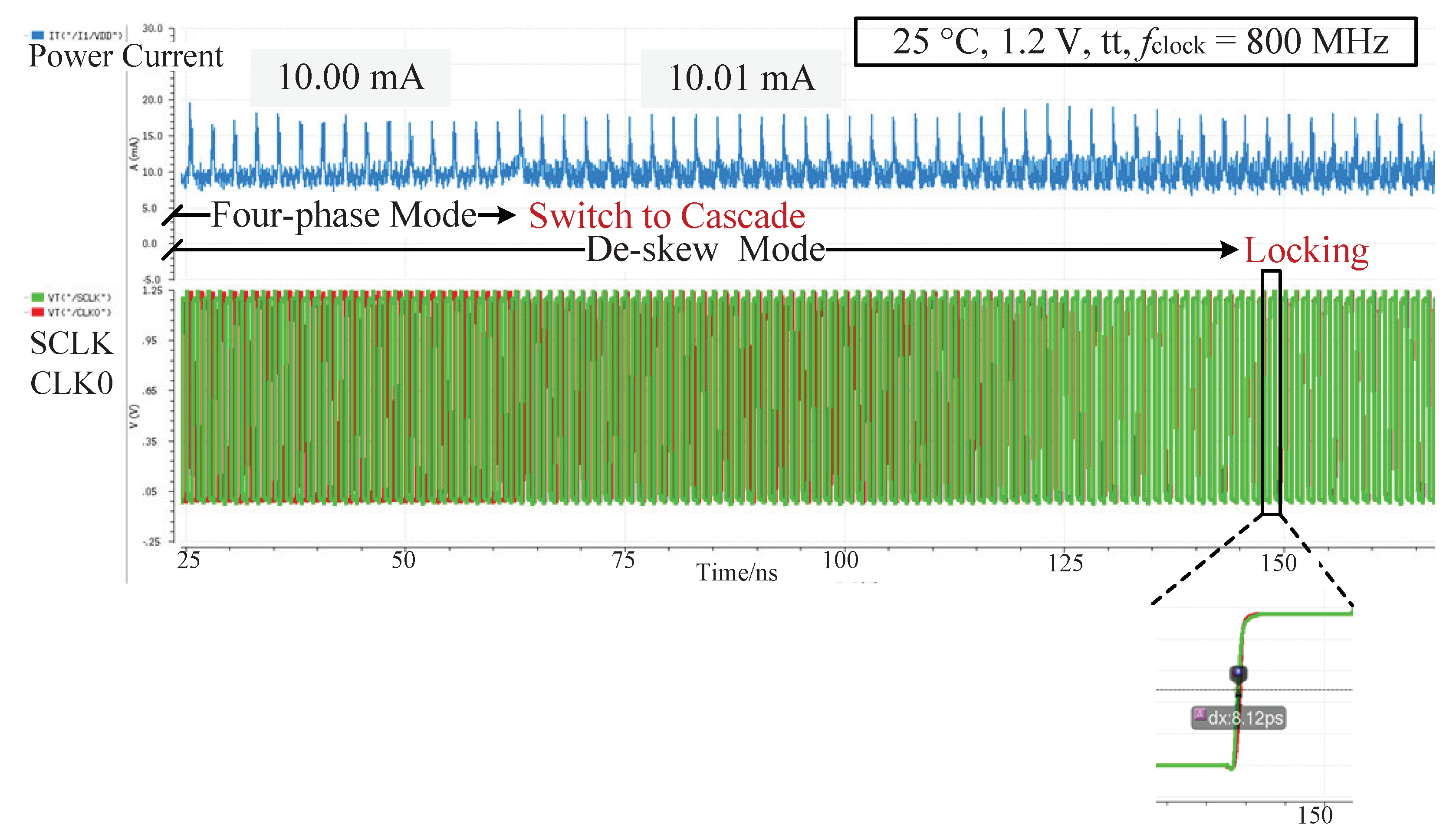

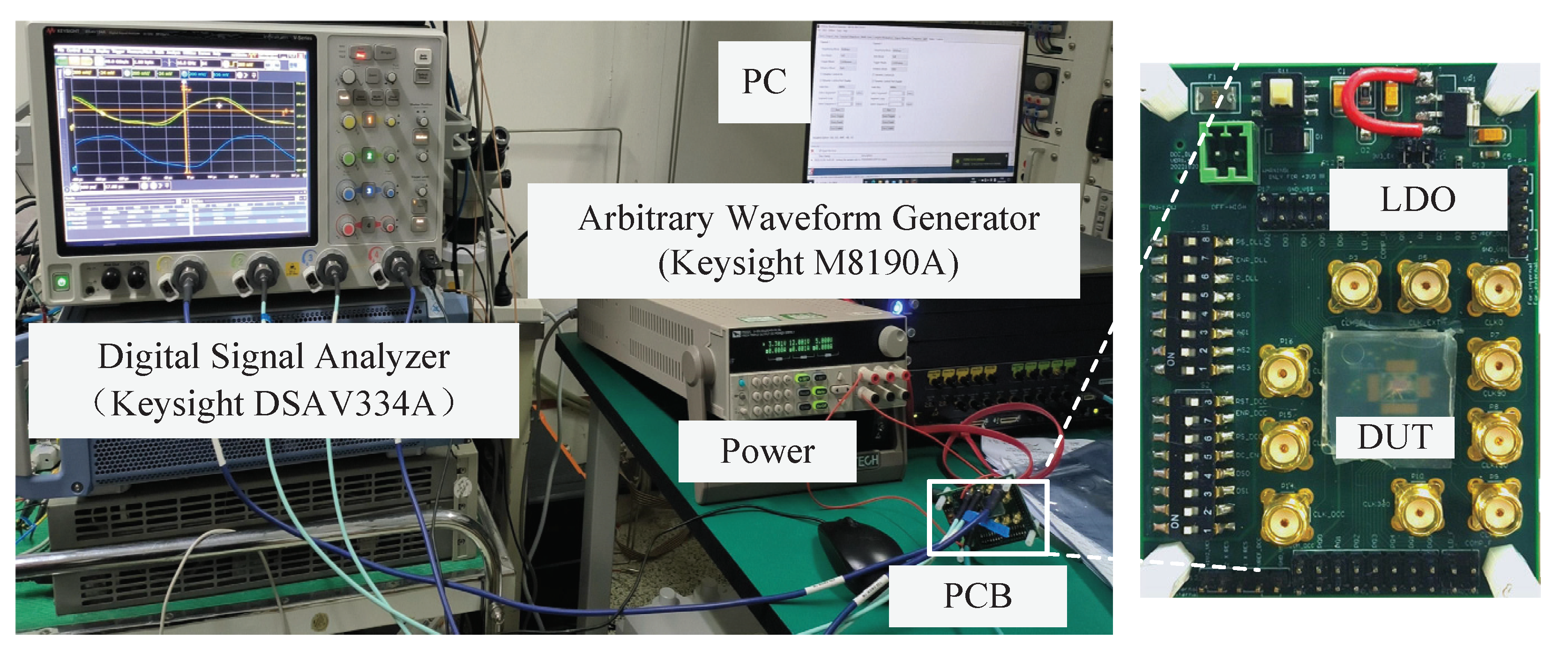

3.1. The Specific Structure of the De-Skew Circuit

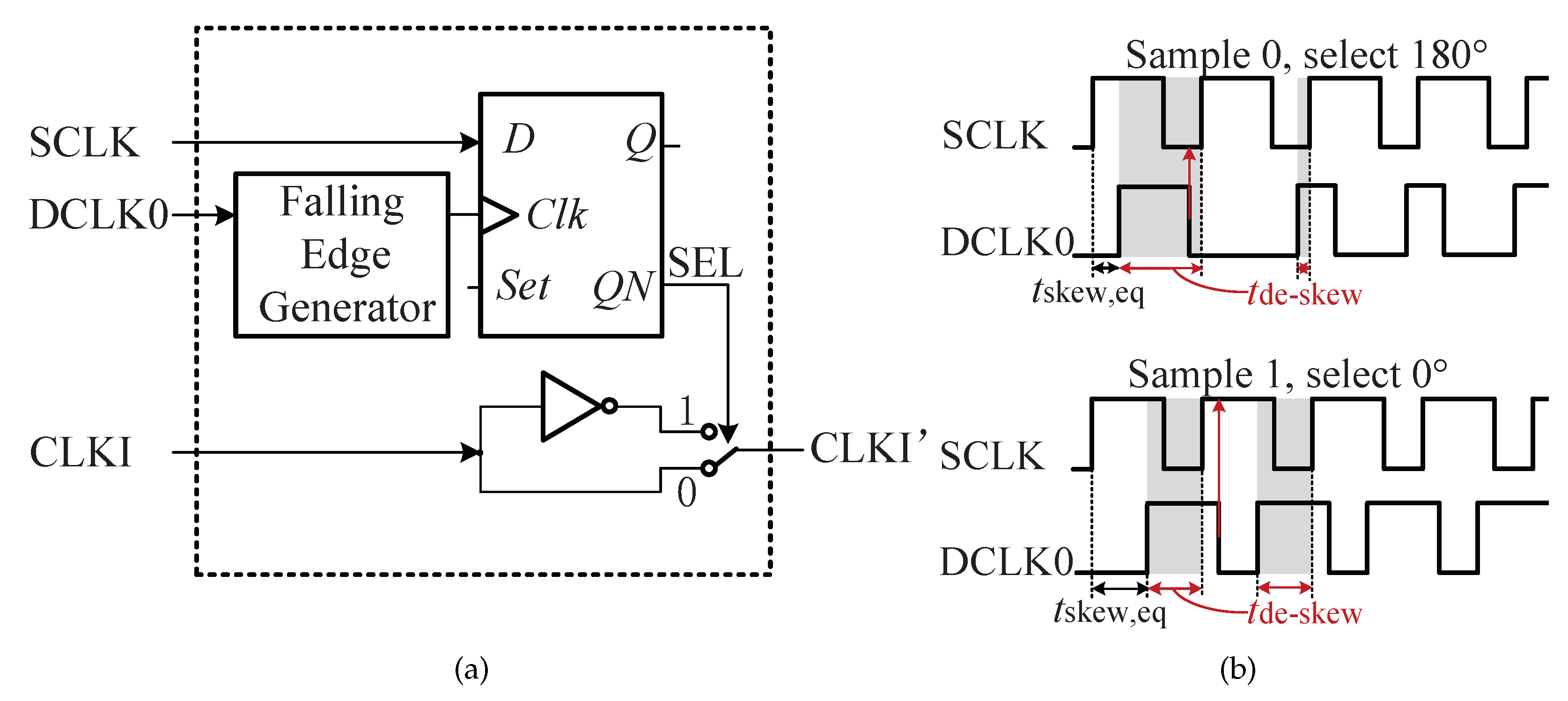

3.2. The Proposed Fall-Edge-Judgment Phase Adjuster

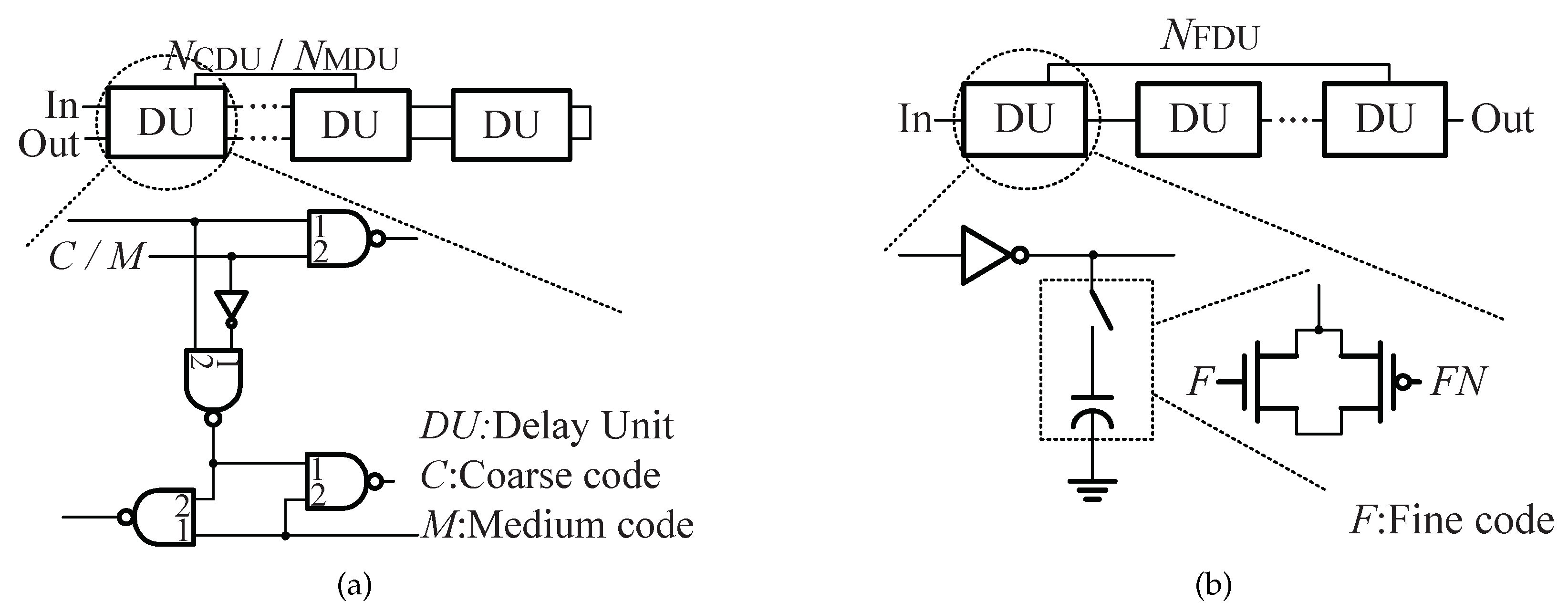

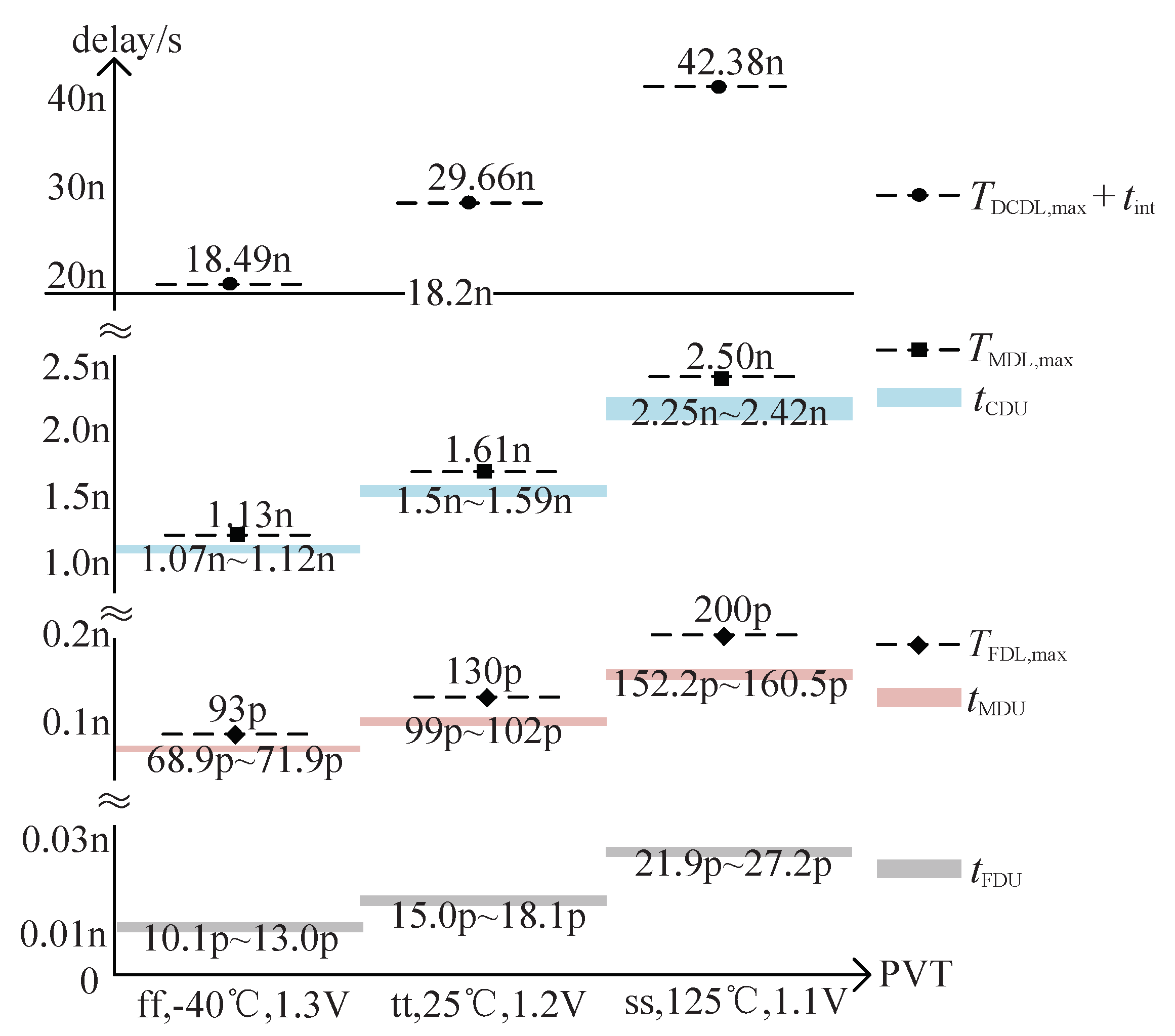

3.3. The Three-Stage Digitally Controlled Delay Line

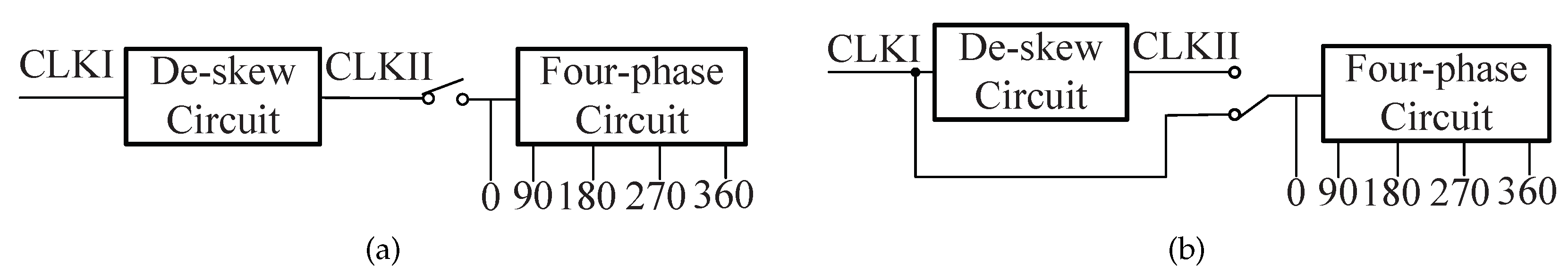

4. The Proposed Parallel-Cascade Configuration

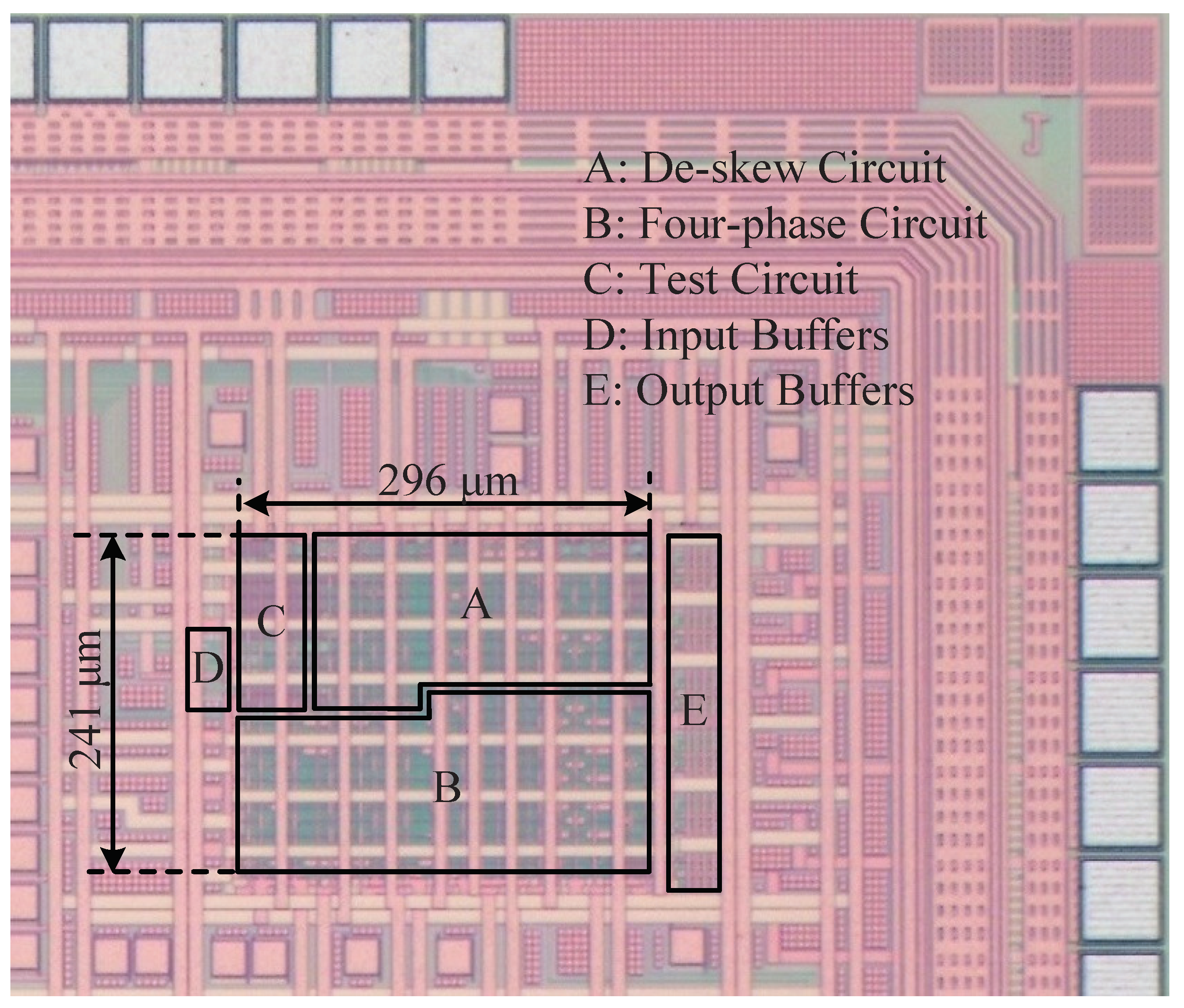

5. The Experimental Results

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| DLL | Delay-locked loop |

| FPA | Fall-edge-judgment phase adjuster |

| 3S-DCDL | Three-stage digitally controlled delay line |

| ADDLL | All digital delay-locked loop |

| DDR | Double data rate |

| ONFI | Open NAND Flash Interface Specification |

| NV-DDR | Non-volatile double data rate |

| DQS | Data strobe signal |

| DQ | Data signal |

| PVT | Process, voltage and temperature |

| BER | Bit error rate |

| 4P-DCDL | Four-phase digitally controlled delay line |

| PD | Phase detector |

| EG | Edge generator |

| TDC | Time-to-digital converter |

| CDL | Coarse delay line |

| MDL | Medium delay line |

| FDL | Fine delay line |

| TG | Transmission gate |

| PCB | Printed circuit board |

| LDO | Low dropout regulator |

References

- Liang, C.K.; Yang, R.J.; Liu, S.I. An All-Digital Fast-Locking Programmable DLL-Based Clock Generator. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 361–369. [Google Scholar] [CrossRef]

- Tsai, C.W.; Chiu, Y.T.; Tu, Y.H.; Cheng, K.H. A wide-range all-digital delay-locked loop for double data rate synchronous dynamic random access memory application. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar]

- Yao, C.Y.; Ho, Y.H.; Chiu, Y.Y.; Yang, R.J. Designing a SAR-based all-digital delay-locked loop with constant acquisition cycles using a resettable delay line. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 23, 567–574. [Google Scholar] [CrossRef]

- Chen, H.; Ma, S.; Wang, L.; Zhang, H.; Pan, K.; Cheng, Y. A low-power, area-efficient all-digital delay-locked loop for DDR3 SDRAM controller. Sci. China Inf. Sci. 2014, 12, 1–8. [Google Scholar] [CrossRef]

- Keerthi Kumar, M.; Pasupathy, K.R.; Bindu, B. Design of FinFET based All-Digital DLL for multiphase clock generation. In Proceedings of the 2015 Annual IEEE India Conference (INDICON), New Delhi, India, 17–20 December 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Lo, Y.L.; Chou, P.Y.; Cheng, H.H.; Tsai, S.F.; Yang, W.B. An all-digital DLL with dual-loop control for multiphase clock generator. In Proceedings of the 2011 International Symposium on Integrated Circuits, Singapore, 12–14 December 2011; pp. 388–391. [Google Scholar]

- El-Shafie, A.H.A.; Habib, S.E.D. An all-digital DLL using novel harmonic-free and multi-bit SAR techniques. Microelectron. J. 2012, 43, 393–400. [Google Scholar] [CrossRef]

- Chae, K.; Choi, J.; Yi, S.; Lee, W.; Joo, S.; Kim, H.; Yi, H.; Nam, Y.; Choi, J.; Park, S.; et al. A 690mV 4.4 Gbps/pin all-digital LPDDR4 PHY in 10nm FinFET technology. In Proceedings of the ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, Lausanne, Switzerland, 12–15 September; pp. 461–464.

- Kim, Y.S.; Lee, S.K.; Park, H.J.; Sim, J.Y. A 110 MHz to 1.4 GHz locking 40-phase all-digital DLL. IEEE J. Solid-State Circuits 2011, 46, 435–444. [Google Scholar] [CrossRef]

- Tu, Y.H.; Liu, J.C.; Cheng, K.H.; Hsu, C.H. A 0.5-V all-digital clock-deskew buffer with I/Q phase outputs. Analog Integr. Circuits Signal Process. 2017, 93, 157–167. [Google Scholar] [CrossRef]

- Bae, J.H.; Seo, J.H.; Yeo, H.S.; Kim, J.W.; Sim, J.Y.; Park, H.J. An all-digital 90-degree phase-shift DLL with loop-embedded DCC for 1.6 Gbps DDR interface. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 373–376. [Google Scholar]

- Kumar, A.; Ardeshana, J.; Jagtap, S. Design & verification of ONFI complient high performance NAND flash controller. In Proceedings of the 2016 IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bangalore, India, 20–21 May 2016; pp. 942–945. [Google Scholar] [CrossRef]

- Yamini, N.; Sasipriya, P.; Bhaaskaran, V.K. Clock distribution network design for single phase energy recovery circuits. In Proceedings of the 2017 International Conference on Nextgen Electronic Technologies: Silicon to Software (ICNETS2), Chennai, India, 23–25 March 2017; pp. 413–418. [Google Scholar]

- Chong, A.B. Hybrid Multisource Clock Tree Synthesis. In Proceedings of the 2021 28th IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Dubai, United Arab Emirates, 28 November–1 December 2021; pp. 1–6. [Google Scholar]

- Park, D.; Kim, J. A 7-GHz Fast-Lock 2-Step TDC-based All-Digital DLL for Post-DDR4 SDRAMs. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Yang, X.; Liu, F.; Huo, Z. A wide-range and high-accuracy four-phase delay-locked-loop with adaptive-bandwidth scheme. J. Xidian Univ. 2022, 49, 194–201. [Google Scholar] [CrossRef]

- Herath, V.R.; Noé, R. A simple mean clock skew estimation algorithm for clock distribution networks in presence of random process variations and nonuniform substrate temperature. In Proceedings of the 2010 5th International Conference on Industrial and Information Systems, Kauai, HI, USA, 5–8 January 2010; pp. 244–248. [Google Scholar]

- Jiang, X.; Horiguchi, S. Statistical skew modeling for general clock distribution networks in presence of process variations. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2001, 9, 704–717. [Google Scholar] [CrossRef]

- Bota, S.A.; Rossello, J.L.; De Benito, C.; Keshavarzi, A.; Segura, J. Impact of thermal gradients on clock skew and testing. IEEE Des. Test Comput. 2006, 23, 414–424. [Google Scholar] [CrossRef]

- Kang, H.; Ryu, K.; Lee, D.; Lee, W.; Kim, S.; Choi, J.; Jung, S.O. Process variation tolerant all-digital multiphase DLL for DDR3 interface. In Proceedings of the IEEE Custom Integrated Circuits Conference 2010, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar]

- Yoon, Y.; Park, H.; Kim, C. A DLL-based quadrature clock generator with a 3-stage quad delay unit using the sub-range phase interpolator for low-jitter and high-phase accuracy DRAM applications. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2342–2346. [Google Scholar] [CrossRef]

- Wang, Y.M.; Wang, J.S. A low-power half-delay-line fast skew-compensation circuit. IEEE J. Solid-State Circuits 2004, 39, 906–918. [Google Scholar] [CrossRef]

- Yang, R.J.; Liu, S.I. A 40–550 MHz harmonic-free all-digital delay-locked loop using a variable SAR algorithm. IEEE J. Solid-State Circuits 2007, 42, 361–373. [Google Scholar] [CrossRef]

- Angeli, N.; Hofmann, K. A low-power and area-efficient digitally controlled shunt-capacitor delay element for high-resolution delay lines. In Proceedings of the 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 9–12 December 2018; pp. 717–720. [Google Scholar]

- Chen, Y.G.; Tsao, H.W.; Hwang, C.S. A Fast-Locking All-Digital Deskew Buffer With Duty-Cycle Correction. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2013, 21, 270–280. [Google Scholar] [CrossRef]

- Zhang, D.; Yang, H.G.; Zhu, W.; Li, W.; Huang, Z.; Li, L.; Li, T. A Multiphase DLL With a Novel Fast-Locking Fine-Code Time-to-Digital Converter. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2015, 23, 2680–2684. [Google Scholar] [CrossRef]

- Tsai, C.W.; Chiu, Y.T.; Tu, Y.H.; Cheng, K.H. A Wide-Range All-Digital Delay-Locked Loop for DDR1–DDR5 Applications. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2021, 29, 1720–1729. [Google Scholar] [CrossRef]

| Reference | [25] | [26] | [27] | This Work |

|---|---|---|---|---|

| Process(nm) | 180 | 130 | 90 | 130 |

| (Hz) | 625 M | 450 M | 2.7 G | 1.55 G |

| (Hz) | 250 M | 80 M | 100 M | 26 M |

| / | 2.5 | 5.6 | 27 | 59.6 |

| Alignment error (ps) | - | 15 | - | 17 |

| Area (m) | 0.09 | 0.08 | 0.089 | 0.072 |

| Power (mW@Hz) | 10.8 @625M | 26.0@ 180 M | 49.4 @2.7 G | 18.1 @1.55 G |

| Supply (V) | 1.8 | 1.5 | 1.0 | 1.2 |

| Four-phase outputs | × | ✓ | ✓ | ✓ |

| Eliminate clock skew | ✓ | × | × | ✓ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kang, J.; Liu, F.; Hai, Y.; Wang, Y. A Wide-Range Four-Phase All-Digital DLL with De-Skew Circuit. Electronics 2023, 12, 1610. https://doi.org/10.3390/electronics12071610

Kang J, Liu F, Hai Y, Wang Y. A Wide-Range Four-Phase All-Digital DLL with De-Skew Circuit. Electronics. 2023; 12(7):1610. https://doi.org/10.3390/electronics12071610

Chicago/Turabian StyleKang, Jing, Fei Liu, Ya Hai, and Yongshan Wang. 2023. "A Wide-Range Four-Phase All-Digital DLL with De-Skew Circuit" Electronics 12, no. 7: 1610. https://doi.org/10.3390/electronics12071610

APA StyleKang, J., Liu, F., Hai, Y., & Wang, Y. (2023). A Wide-Range Four-Phase All-Digital DLL with De-Skew Circuit. Electronics, 12(7), 1610. https://doi.org/10.3390/electronics12071610