1. Introduction

High resolution analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) extensively use sigma-delta modulation. This technique conveniently provides high signal-to-quantization noise ratio (SQNR), which makes it important to use in super audio CD format. It is widely used in recent data acquisition systems, Microelectromechanical systems (MEMS), inertial sensors, image sensors, wireless technologies such as long-term evolution advanced (LTE-Advanced), global system for mobile Telecommunication (GSM) and code-division multiple-access (CDMA) etc., where high speed ADCs with wide bandwidth, low noise and less glitch-induced harmonic distortion are required [

1,

2,

3,

4,

5,

6,

7,

8,

9]. Portable audio playback devices, which perform digital-to-analog conversion also make use of it. Other applications include instrumentation, seismic activity measurements, speech, video, Integrated System digital Network (ISDN), digital cellular radio, mobile communication devices and systems by reducing the complexity of sigma-delta modulators through different designs considerations, next generation wireless telecom systems, frequency synthesizer, Chromatography and electrocortical reading in brain stimulation applications [

10,

11,

12,

13,

14]. A quantization noise is generated during analog-to-digital and digital-to-analog conversion, which is the main cause to accomplish reconstruction process inappropriate [

15]. Sigma-delta modulator (SDM) employs noise shaping and oversampling, which move this noise from the band of interest to higher frequency region [

16].

Sigma-delta modulator comprises of “sigma” and “delta” blocks [

17]. The input is passed through a feed forward filter

, which is a sigma block followed by a quantizer. If two feed forward filters are used in two stages, then it is called second order sigma-delta modulator [

18]. Delta block subtracts output from the input [

19,

20]. The feed forward filter combined with delta block is termed as a loop filter [

21]. The output can be generalized in Equation (1):

In previous research work, Multi-stage noise shaping (MASH) based SDM was widely used for high-bandwidth applications. In MASH architecture, the input is applied to the integrator (feed forward filter), which comprises of accumulator and delay blocks. The signal reaches to the quantizer after passing through the feed forward filter. The quantized output is then fed back to the delta block to subtract it from the input. The average output of the quantizer follows the average input through feedback path. However, the MASH architecture does not provide stability with time varying inputs and eventually degrades its performance. In Error feedback modulator (EFM), the quantizer saturates and overflows when the input signal is closed to full scale. The other main issue observed in 1-bit EFM is the existence of limit cycles in the frequency spectrum. In limit cycles, the output bits repeat indefinitely, and the output spectrum of SDM goes into periodic modes. If the output bit stream of SDM remains periodic and occurs after a short period, then it gives rise to short limit cycles. Due to which, strong unwanted peaks occurred in the spectrum. While in conventional hybrid models, the mapping of discrete/digital time transfer functions to the continuous time transfer functions is complex. Hence, the major issue observed in the designing of SDM is stability with low performance parameters like low SQNR and occurrence of limit cycles.

This paper proposes a new architecture named as Hybrid Multi-stage noise shaping error feedback modulator (MASH-EFM), which uses some major characteristics of both MASH and EFM architectures. Feed forward filters and error signal, which are the main attributes of MASH and EFM architectures respectively, are used in this architecture. Limiters and dithering avoid overflow and remove limit cycles, respectively. Consequently, this architecture is more stable and robust. It provides high SQNR for both time varying and non-time varying inputs and mitigates all the issues discussed in the above paragraph. Moreover, this proposed hybrid architecture seeks to eliminate the mapping of discrete time transfer function to the continuous time transfer function.

This work emphasizes on the development of a third order Hybrid MASH-EFM that can be suitable for 1-bit audio DAC applications due to its better noise shaping. As the occurrence of limit cycles are more prominent in 1-bit EFM, therefore 1-bit architecture is proposed to show that this presented architecture effectively removes limit cycles. And hence it is superior to EFM. The other main factor to emphasize 1-bit architecture is to implement 1-bit quantizer. The complexity of quantizer increases as the number of bits increases, which results in the increase of cost. This proposed architecture is designed in such a way that it provides cost effective solution with high SQNR. Two-stage Feed forward digital loop filters are used, which also reduce the complexity of mapping between discrete-time (DT) and continuous-time (CT) blocks in a Hybrid architecture. Moreover, the application of third-order Hybrid MASH-EFM can also be extended for Video DAC by improving its resolution.

This article is organized as follows.

Section 2 mentions the research work that has already been carried out to develop different variants of MASH and EFM sigma-delta modulators.

Section 3 describes the block diagram of proposed architecture and mathematically derives the important ∑Δ parameters like noise transfer function (NTF), SQNR and effective number of bits (ENOB). In

Section 4, simulation methodology has been discussed for conventional and proposed architectures. All the simulations have been performed in this section. Results have been explained in both graphical and tabular form and comparison between proposed and existing architecture have been deduced in

Section 5.

Section 6 represents the conclusions and future recommendations of this paper.

2. Related Work

A lot of work has been published on MASH, EFM and different types of hybrid SDM architectures. MASH can be easily constructed and implemented with greater accuracy delivering high performance parameters because of its aggressive noise shaping [

22,

23]. However, MASH architecture loses stability and performance during time-varying inputs. Cascaded MASH architectures are also implemented several times in different research papers. The cascaded MASH architectures were complex and complicated in terms of circuitry.

The above stability and complex circuitry issues are removed by the EFM architecture. In EFM, the error signal is obtained by subtracting the output of the EFM with the input of the quantizer and then given back to the input signal. EFM uses error signal and loop filter in the feedback path. The NTF of Nth order EFM is

[

24]. So, the third order NTF is given by:

. The EFM architecture provides greater stability with time varying inputs [

25,

26,

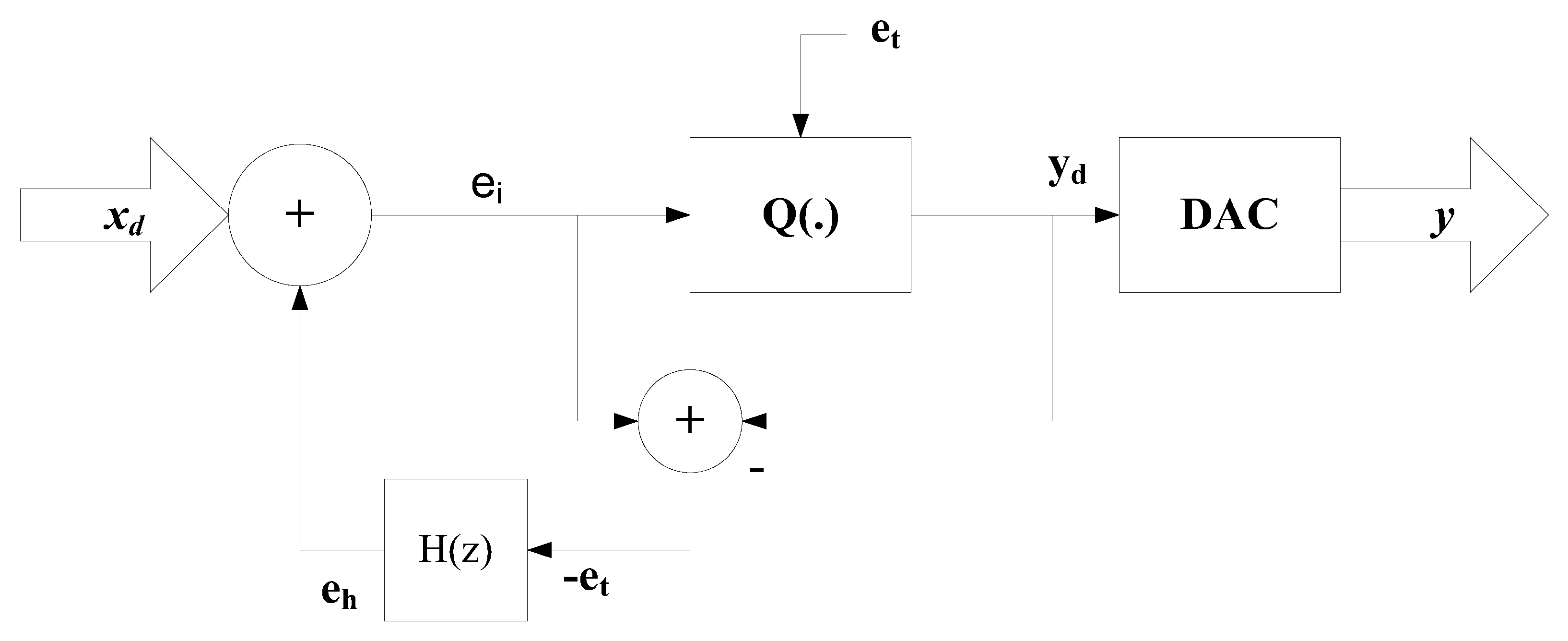

27]. The EFM architecture is shown in

Figure 1. In

Figure 1,

represents the input to the EFM,

is the error signal generated by subtracting the input signal

and feedback signal

, and Q(.) denotes the quantizer. The output of the quantizer

is converted into digital signal y by the DAC. However, the EFM architecture saturates when the input reaches to full scale.

The Hybrid audio SDM was also presented to resolve the saturation issue of the quantizer [

15,

28]. The Hybrid audio SDM consists of analog integrator, successive approximate registers (SAR), ADC, digital filter with excessive loop delay (ELD) compensator, a feedback DAC, and a dynamic element matching (DEM) block. Analog integrator is placed in the first stage and the second stage composes of the digital filters, DEM, and DAC. The output of an analog integrator is converted into digital form by SAR. A bit by bit conversion is performed by the left channel when right channel performs sampling and vice versa. Other type of hybrid SDM in which continuous and discrete time transfer functions are cascaded was also implemented [

29]. The hybrid SDM based on multi-rate down sampling, named as “multi-rate down sampling Hybrid continuous-time (CT)/discrete-time (DT) cascaded SDM”, was also presented by the researchers [

30]. Moreover, the mapping of CT and DT transfer function is complicated as the DT signal, which is the output of the quantizer is fed back to CT block. The above-mentioned drawback can be removed by using the digital filters as the input of the feedforward filter as first time introduced in the proposed architecture.

3. A New Proposed Noise Transfer Function

The major characteristics of aforementioned existing architectures are incorporated to create a new architecture, which shows better efficiency than the existing architectures.

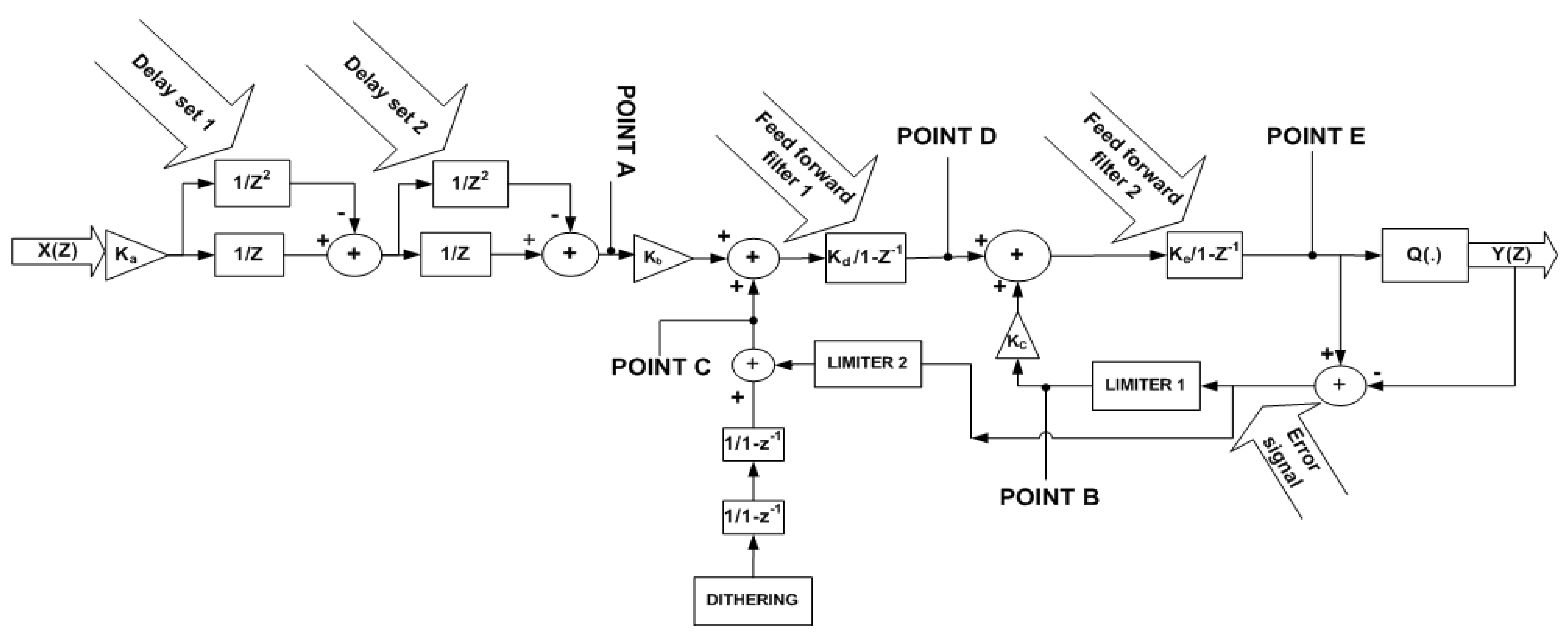

The block diagram of third-order Hybrid MASH-EFM is shown in

Figure 2. The two sets of useful delays or digital filters

and

are used in this architecture indicated as “delay set 1 and delay set 2” respectively. The feed forward filters (feed forward filter 1 and feed forward filter 2), which are the characteristics of MASH, are placed in the feed forward path in both the stages respectively. Similarly, error signal, which is the characteristic of EFM, is extracted by subtracting the output of a proposed SDM with the input of a quantizer. Limiter 1 and limiter 2 are also deployed in this feedback path. Limiter 1 improves noise shaping and avoids overflow when the input signal is closed to full scale and quantization error becomes unbounded. Limiter 2 also prevents it from an overflow by completely suppressing the feedback signal. Limiter 1 and limiter 2 are also indicated in

Figure 2. K

a, K

b, K

c, K

d and K

e are the gains. The output spectrum of proposed architecture is a spur-free at a higher gain, which shows that proposed architecture is more robust and stable due to limiter circuits.

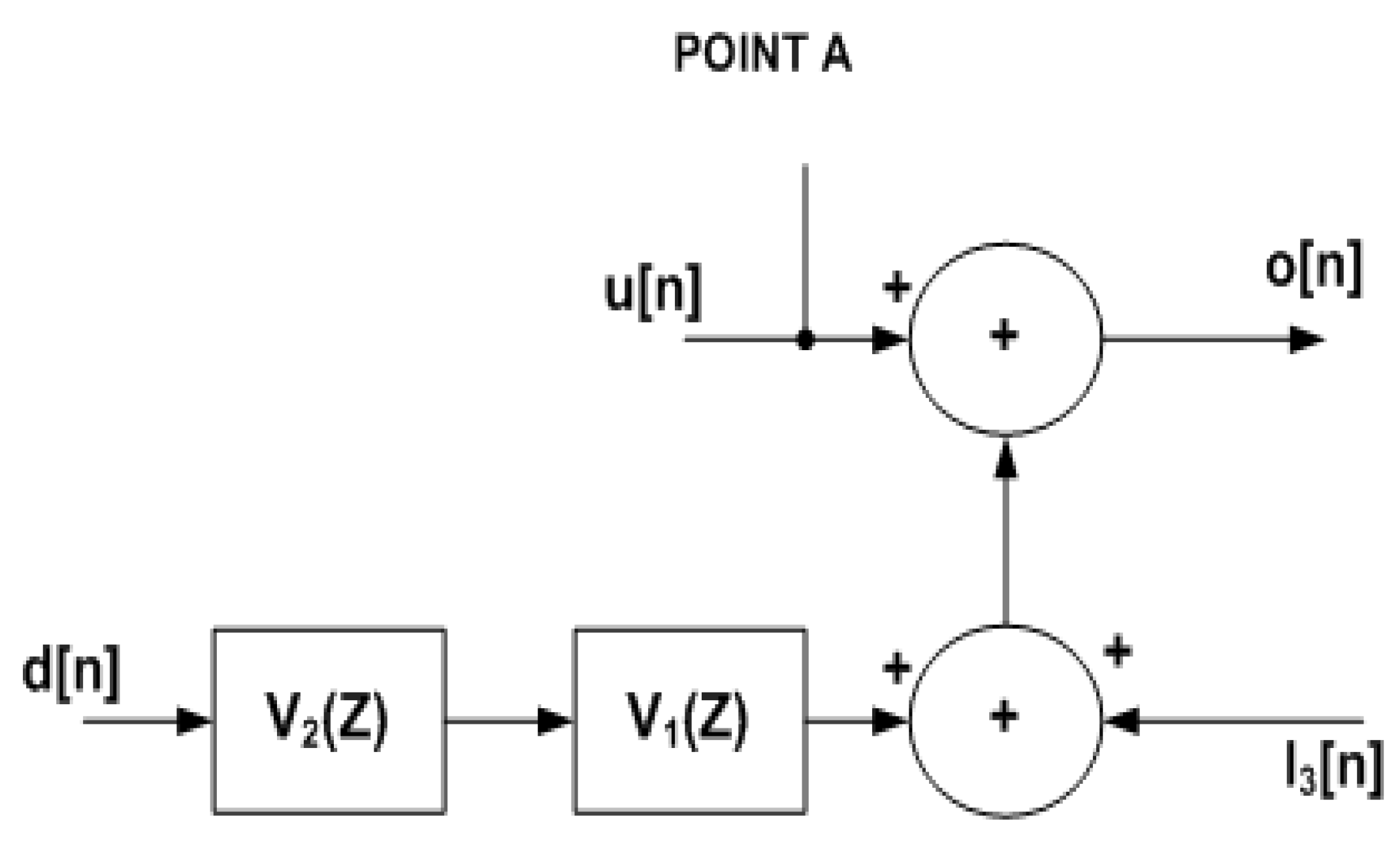

A low power random dither sequence denoted by d[n] is applied to this architecture. The output of a dither block, which is shown in

Figure 3, can be mathematically written in Equation (2):

where “∗” is convolution operator. “

V1 (z)” and “

V2 (z)” are the low pass filters, and both have transfer functions given by

.

and

are the output signals in the discrete-time domain from the limiter and two-stage feed-forward delays respectively. In higher order modulator, dithering makes the noise distribution uniform, reduces the tones, and removes limit cycles by breaking the sequence of repetitive bit stream at the output of quantizer. Usually, the minimum cycle length of SDM is very small. The overall power spectrum of quantization noise also consists of power of dither signal.

For simplicity, the quantization error

can be generically replaced by the notation

as written in Equation (3):

The output after two set of delays or at point “

A” is mathematically expressed in Equation (4):

The output of limiter 1 is mathematically represented in Equation (5):

If the Quantizer is replaced by its equivalent model, then the output

will be written in Equation (6) as:

where

D(z) represents the dither signal in z-domain.

By setting

, KaKbKdKe = K

s, and

KcKdKe = K

n. Hence, the signal transfer function (STF) and NTF can be mathematically delineated in the form of Equations (7) and (8) respectively.

The gains are adjusted in such a way that should not be greater than 4 to reduce the in-band noise gain. The third-order Hybrid MASH-EFM architecture acquires same NTF as 3rd order EFM SDM. Hence, this architecture acts as a 3rd order noise shaper.

The 3rd order NTF of proposed architecture is mathematically expressed in Equation (9):

The mathematical expression for squared magnitude of NTF is derived by replacing

to

as given in Equation (10):

The SQNR can also be determined through the NTF. It is calculated by dividing the original signal power with an in-band, shaped quantization noise power at the frequency of an input signal. Assume that the power of input signal and the noise power is represented by

and

respectively. The quantization noise power is denoted by

. Then, the power of the input signal and the noise power can be mathematically expressed in Equations (11) and (12) as:

where

A represents the amplitude of the input signal.

The sampling frequency is mapped to

.The oversampling ratio (

OSR) also have a greater impact on the noise power, thus the noise power can be expressed in terms of Equations (13) and (14) as:

Though, the

SQNR is mathematically written in the form of Equation (15) as:

The

ENOB, which depends upon the

SQNR can be defined by the Equation (16):

By solving the Equation (16), the

ENOB can be expressed by the Equation (17):

where

and

OSR are the step size and

OSR respectively. According to Equation (17), the

ENOB depends upon the step size,

OSR, and input signal power. By increasing the quantizer bits, the step size decreases. Increasing the quantizer bits and the

OSR are all the methods to improve the

ENOB in the proposed architecture. But there is a trade-off between

ENOB,

OSR and quantizer bits because increasing the

OSR and quantizer bits saturate the quantizer and become impractical for DAC. Therefore, this architecture uses single bit quantizer and

OSR is set to 64.

5. Experimental Results and Discussion

The foremost advantage of proposed architecture is that the Hybrid MASH-EFM uses two limiters to prevent a quantizer from overflow at large input signal. The effect of quantization noise becomes worst at the larger input signal. To prevent the above-mentioned issue, the output of limiter 1 which consists of quantization noise in the feedback path is fed back to the accumulator of second stage. The limiter 2 is designed in such a way that it totally suppresses the quantization noise as described in the mathematical modeling of proposed architecture so that the error signal is not summed up with the input signal again at the accumulator of first stage. Hence, a proposed Hybrid MASH-EFM prevents the quantizer to go into the non-linear behavior. Also, the hardware complexity and power consumption are increased due to the use of limiter circuits in third-order Hybrid MASH-EFM. But the additional increase in hardware complexity and power consumption of Hybrid MASH-EFM architecture is minor because these limiters use digital filters and delays. Hence, a proposed architecture provides greater stability and robustness at a very small cost of hardware complexity [

37]. In contrast to a proposed architecture, a conventional EFM does not possess such phenomena to limit the consequences of the error signal. In conventional EFM, the error signal is then summed up with the input signal which makes the quantizer overwhelmed at a full scale of the input signal which results in its instability.

The 3rd order EFM has NTF:

as discussed in

Section 1. While the proposed third-order architecture achieves same NTF with its scaling factor of 4. Again, the use of limiters in the feedback path helps to obtain higher order noise shaping.

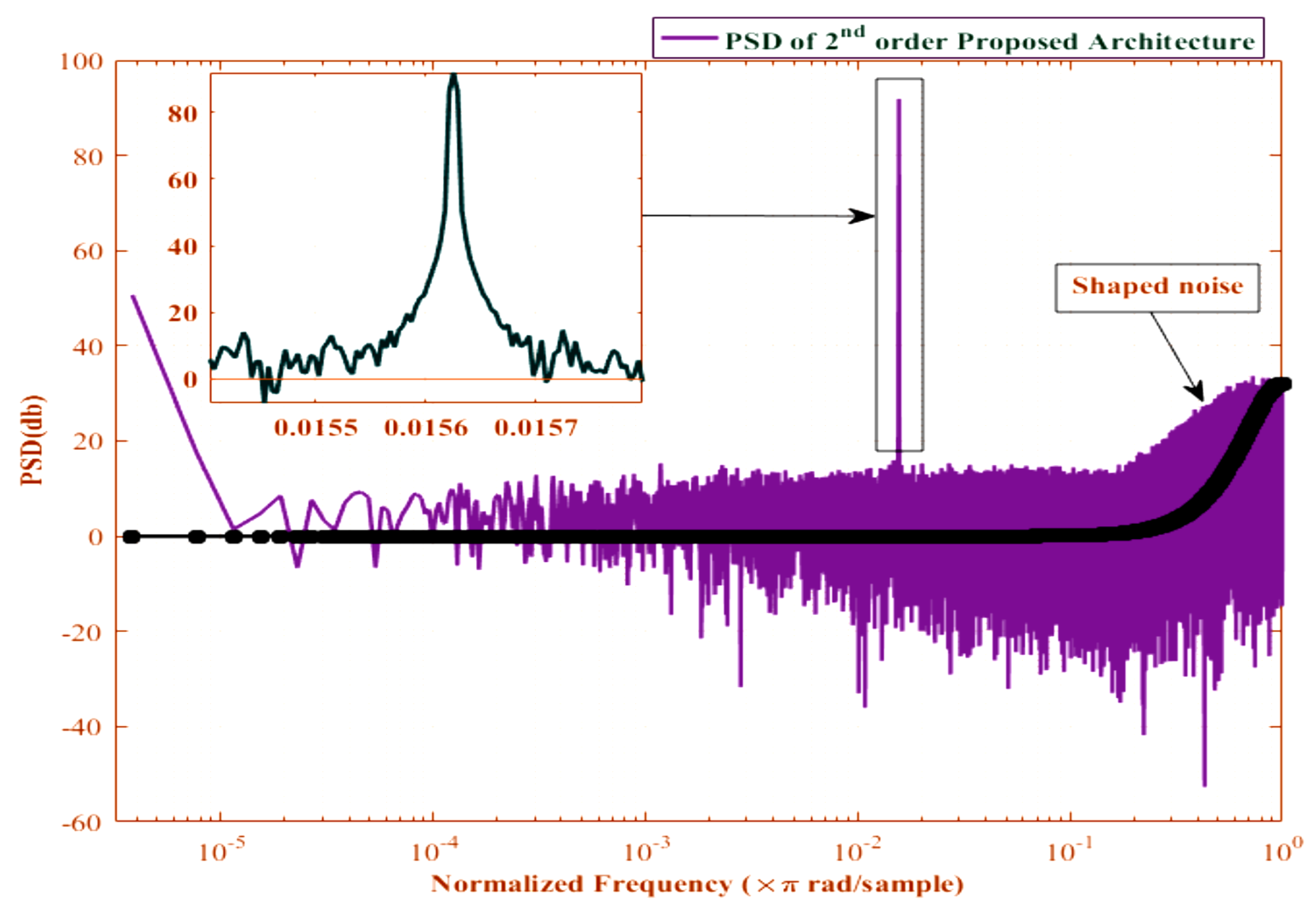

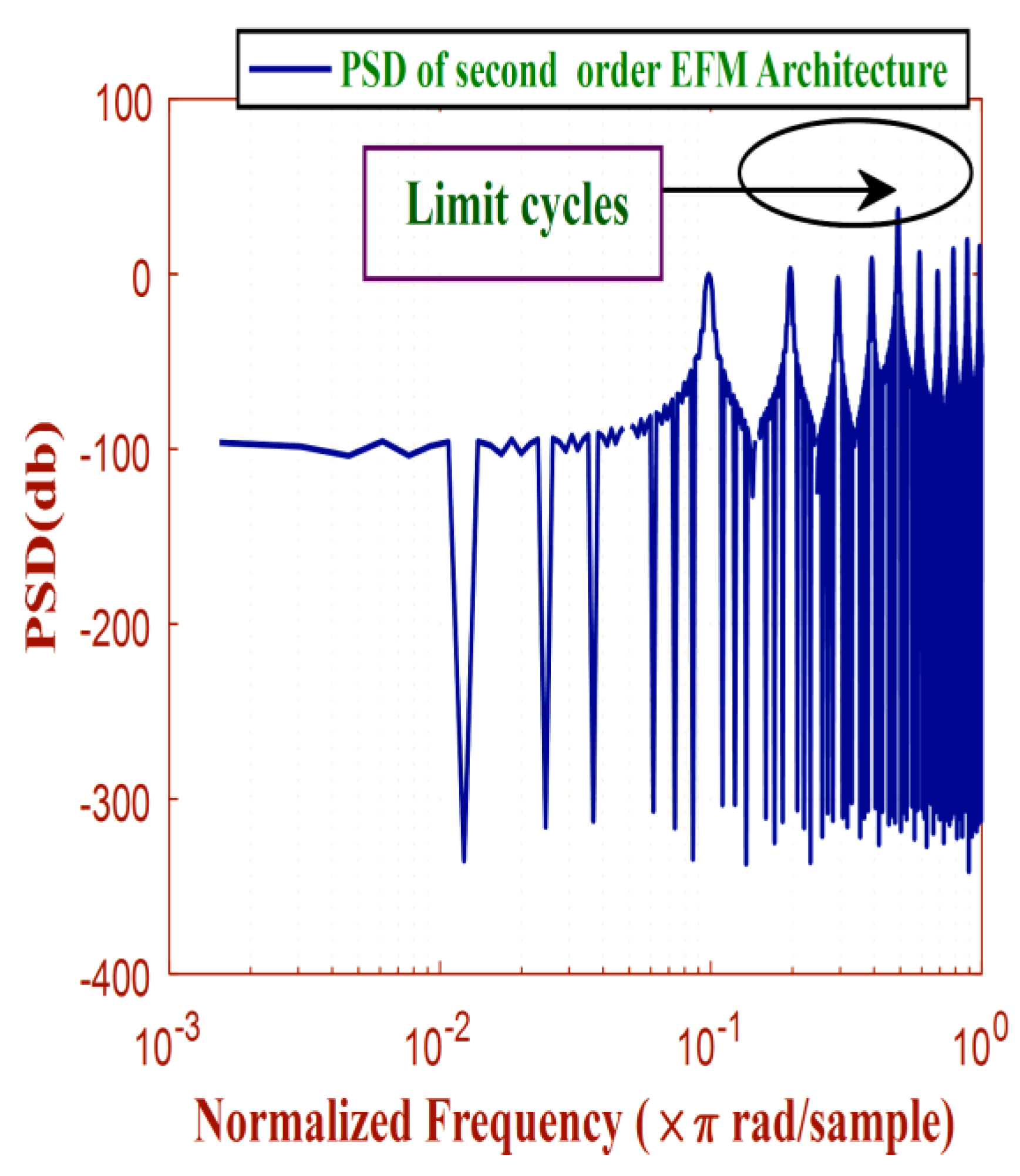

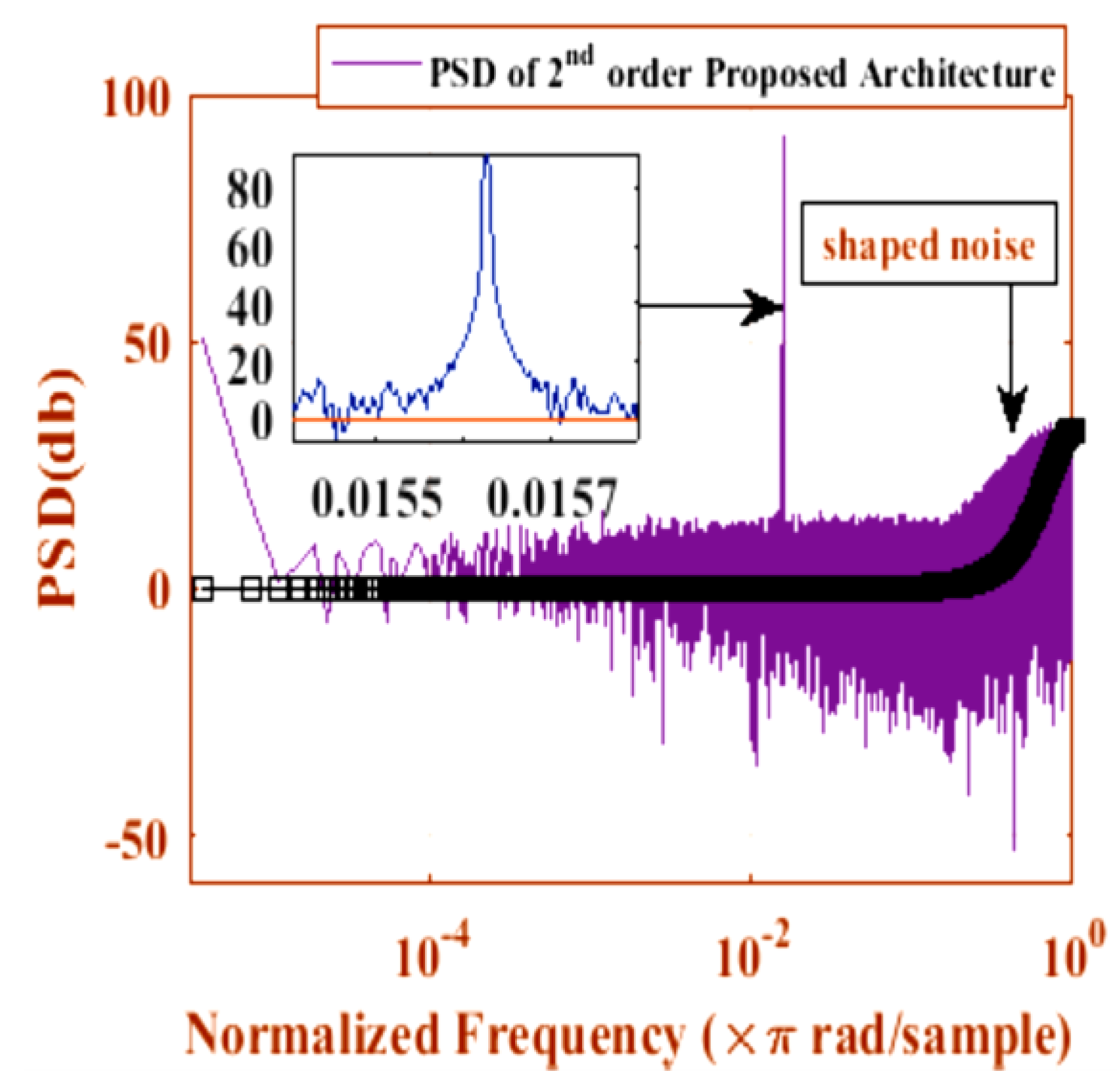

Figure 10 represents the NTF graph of 2nd order EFM, 3rd order EFM and 3rd order Hybrid MASH-EFM. The black curve represents the squared magnitude of NTF of proposed architecture. While the green and blue curves represent the squared magnitude of NTF of 2nd and 3rd order EFM respectively. The NTF graph depicts that the proposed architecture will provide higher attenuation to the quantization noise in the signal bandwidth and lower attenuation at higher frequencies than the conventional 2nd order EFM architectures due to the scaling factor of NTF of Hybrid MASH-EFM. Therefore, the Hybrid MASH-EFM assists aggressive noise shaping than 2nd and 3rd order EFM. The PSD of both conventional EFM and Hybrid MASH-EFM are shown in

Figure 11 and

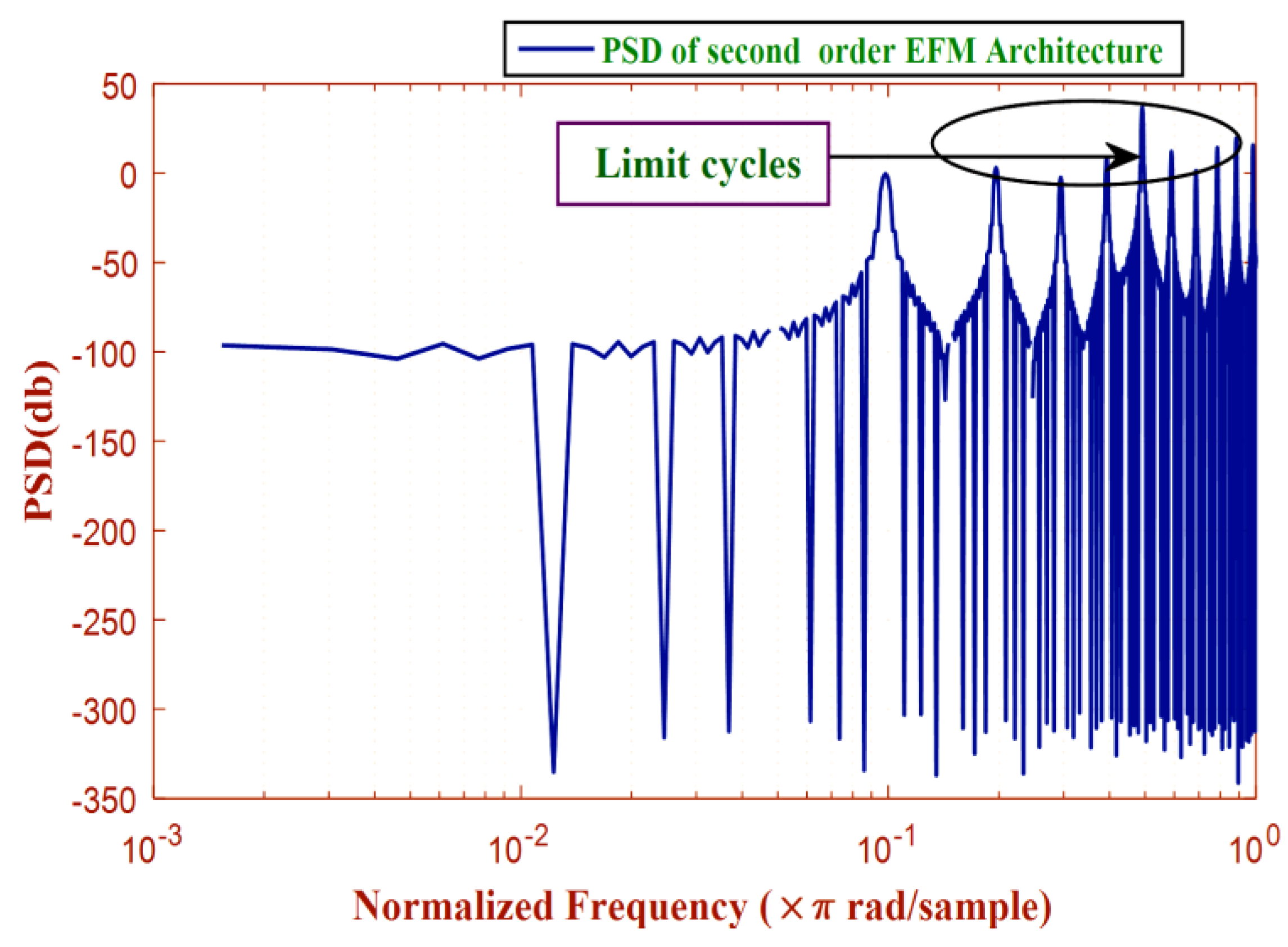

Figure 12 respectively. The PSDs of both conventional EFM and Hybrid MASH-EFM suggest that the noise shaping is more prominent in the proposed architecture.

Moreover, some tones are also being observed at lower frequencies in EFM as presented in the PSD of 2nd order EFM in the

Figure 11. In contrast, the NTF of proposed architecture makes the distribution of quantization noise smooth and free from idle tones. The dark black curve is the NTF in the PSD of proposed architecture. The quantization noise is perfectly matched with the NTF curve. The STF of proposed architecture behaves like a low pass filter as in the case of EFM. The PSD of Hybrid MASH-EFM reveals that the quantization noise is completely suppressed in the DC frequency region. The STF provides lower attenuation to the signal in the baseband and higher attenuation in the higher frequency region. As the frequency increases, the quantization noise also increases in the spectrum.

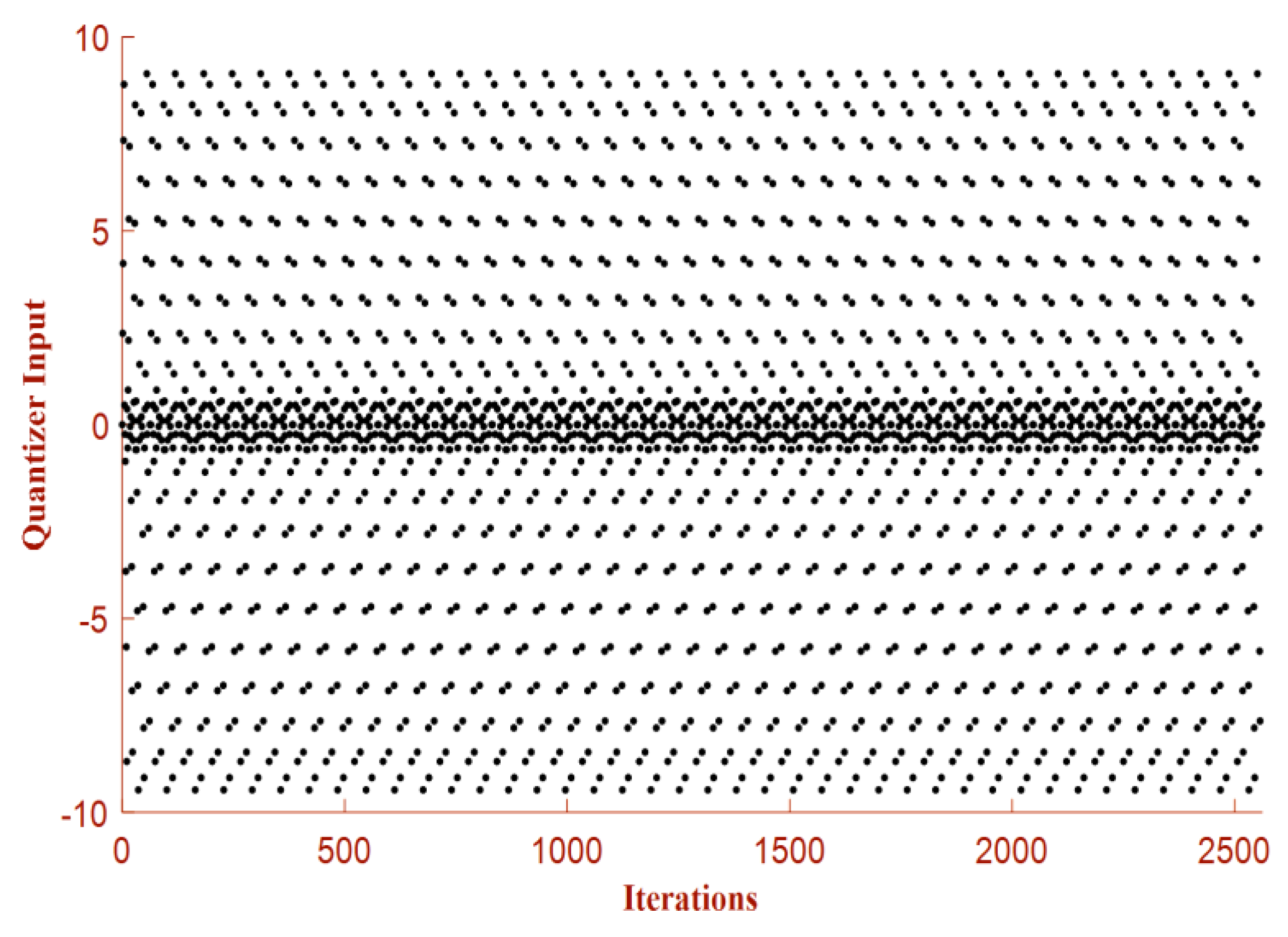

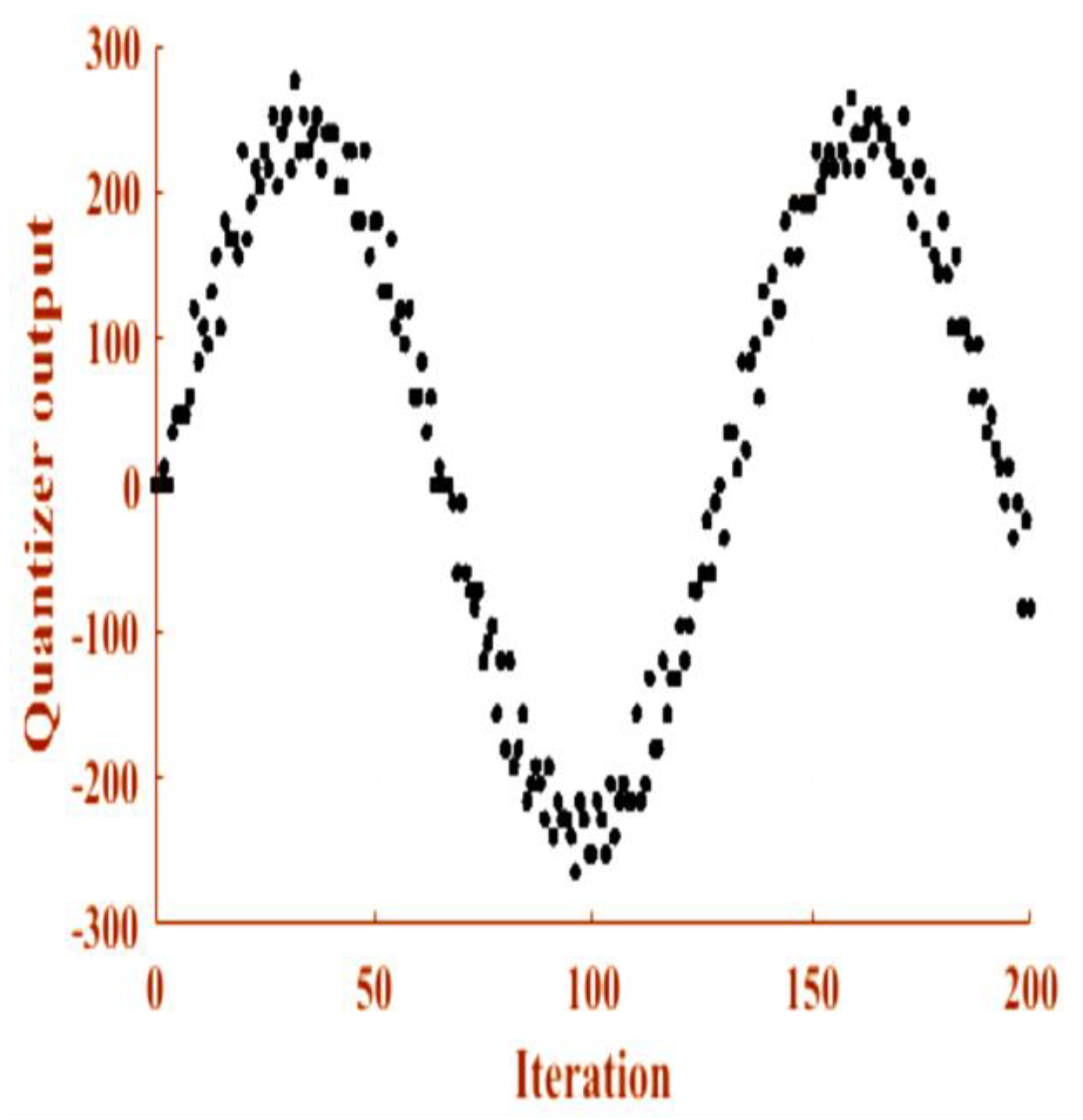

The other main cause of instability is the occurrence of limit cycles in conventional EFM. To demonstrate the above discussed issue in EFM, the graph between number of iterations and the input to the quantizer is plotted, which is already shown in the

Figure 5. The scattered plot of quantizer input bit stream tells that the quantizer does not experience the recurrence of same bit. In contrast to the

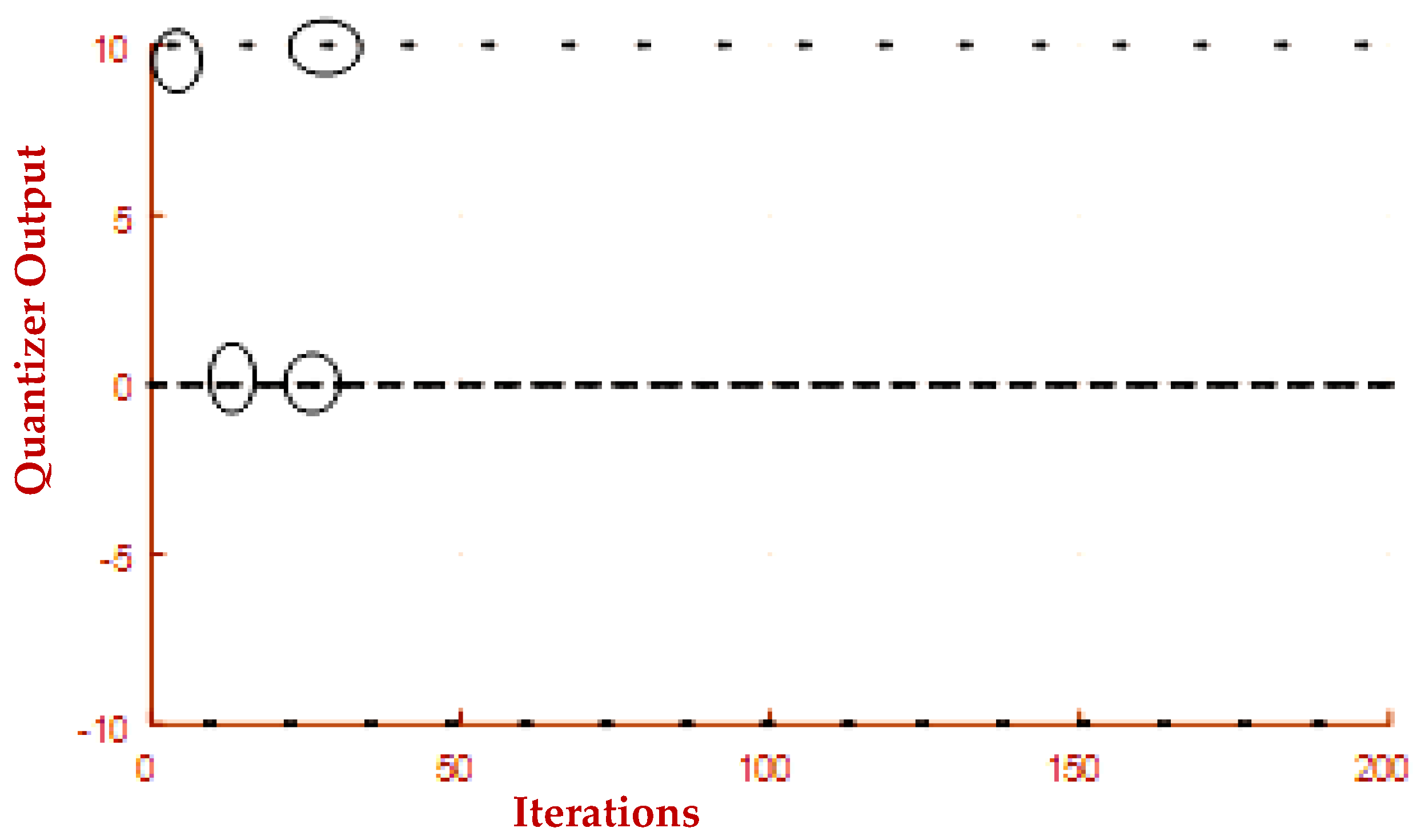

Figure 5,

Figure 6 suggests that the duplication of same bits is observed in the output bit stream indicated by black circles which produces limit cycles. The first 200 iterations are plotted in the

Figure 6 to analyze the results clearly. The PSD of EFM proves that limit cycles are observed due to these duplications as shown in

Figure 11. Thus, a 1-bit conventional EFM is more prone to limit cycles. This problem is mitigated in a proposed architecture. This work demonstrates that if the pseudorandom dither (a disturbance) is added at the output of Limiter 2 in the feedback path in 3rd order Hybrid MASH-EFM, which effectively disturbs the repetitive bit pattern at the output of quantizer. The scattered pattern of output bit stream of quantizer in Hybrid MASH-EFM determines the absence of reappearance of same bit as indicated in the

Figure 9. The output bit stream of Hybrid MASH-EFM follows the pattern of input signal after removing the repetitive bits.

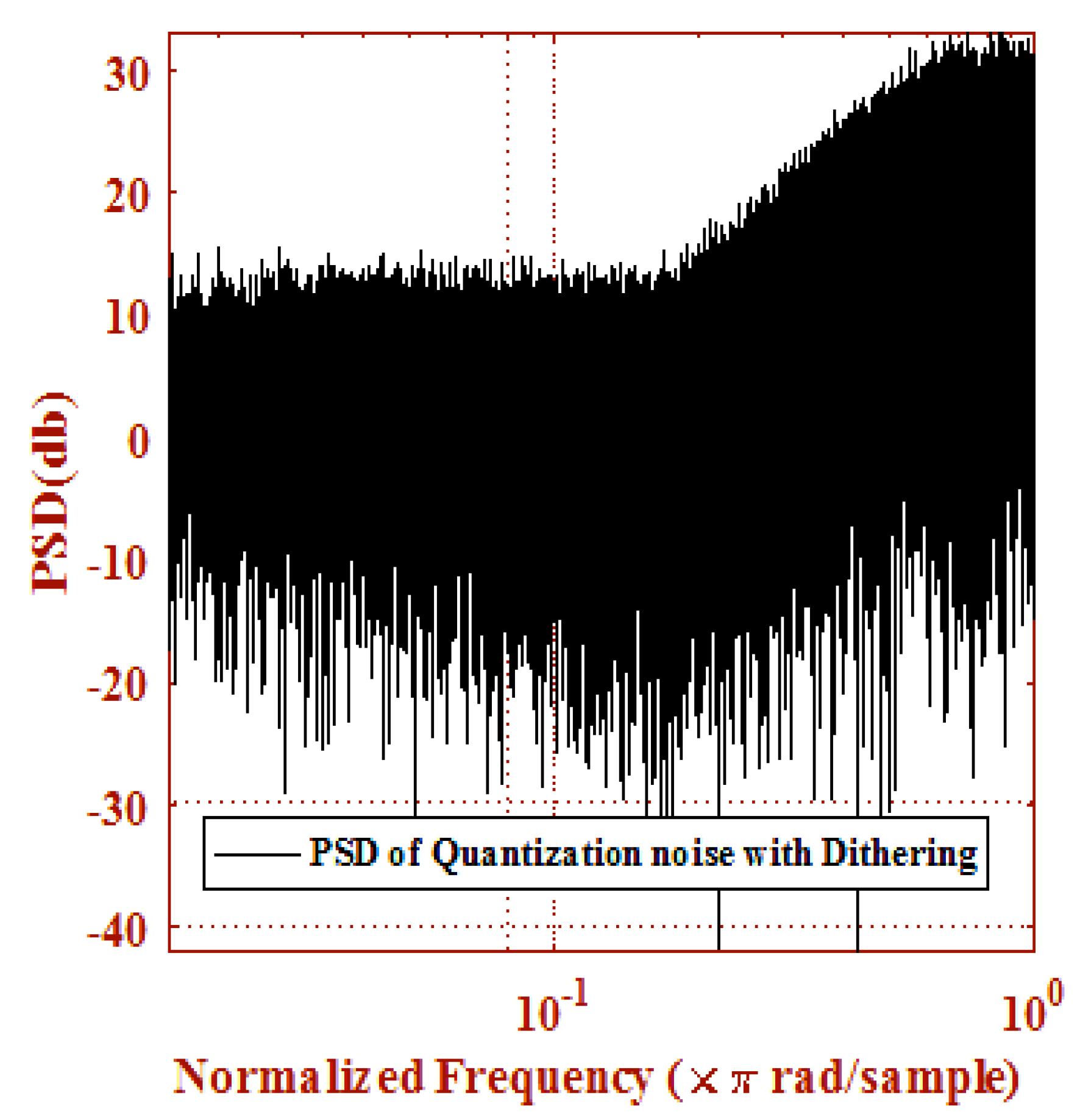

Figure 13 represents the PSD of quantization noise with dithering in proposed architecture and

Figure 14 makes comparison of quantization noise between existing and the proposed architecture. The quantization noise, which is in black curve in the

Figure 14, is free from limit cycle while conventional EFM architecture experiences limit cycles in its quantization noise (in red color). Equation (9) also reveals that the application of dither signal at the output of Limiter 2 does not affect the STF and NTF, which is another main advantage. Hence the proposed architecture is more stable in order to resist limit cycles.

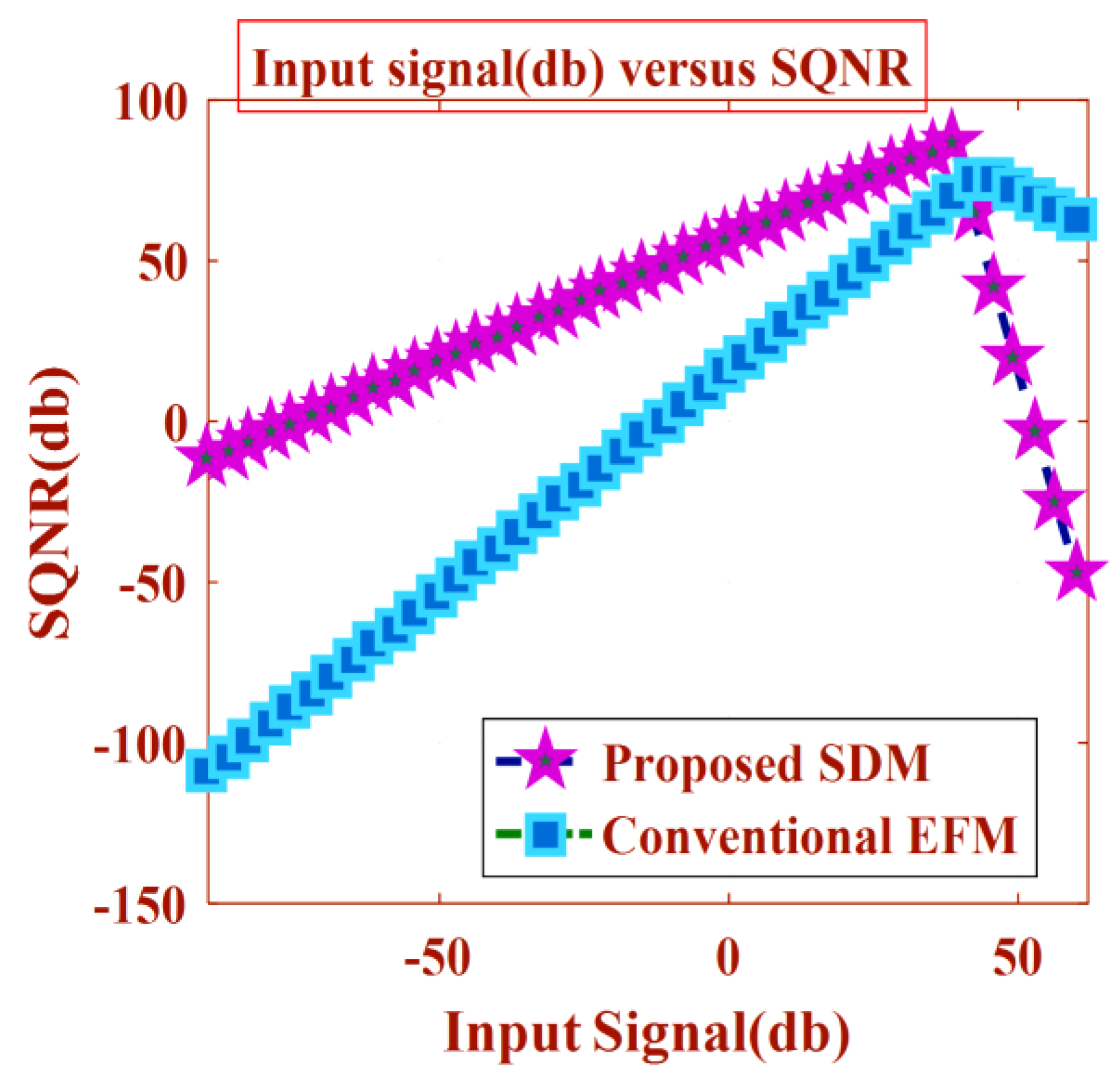

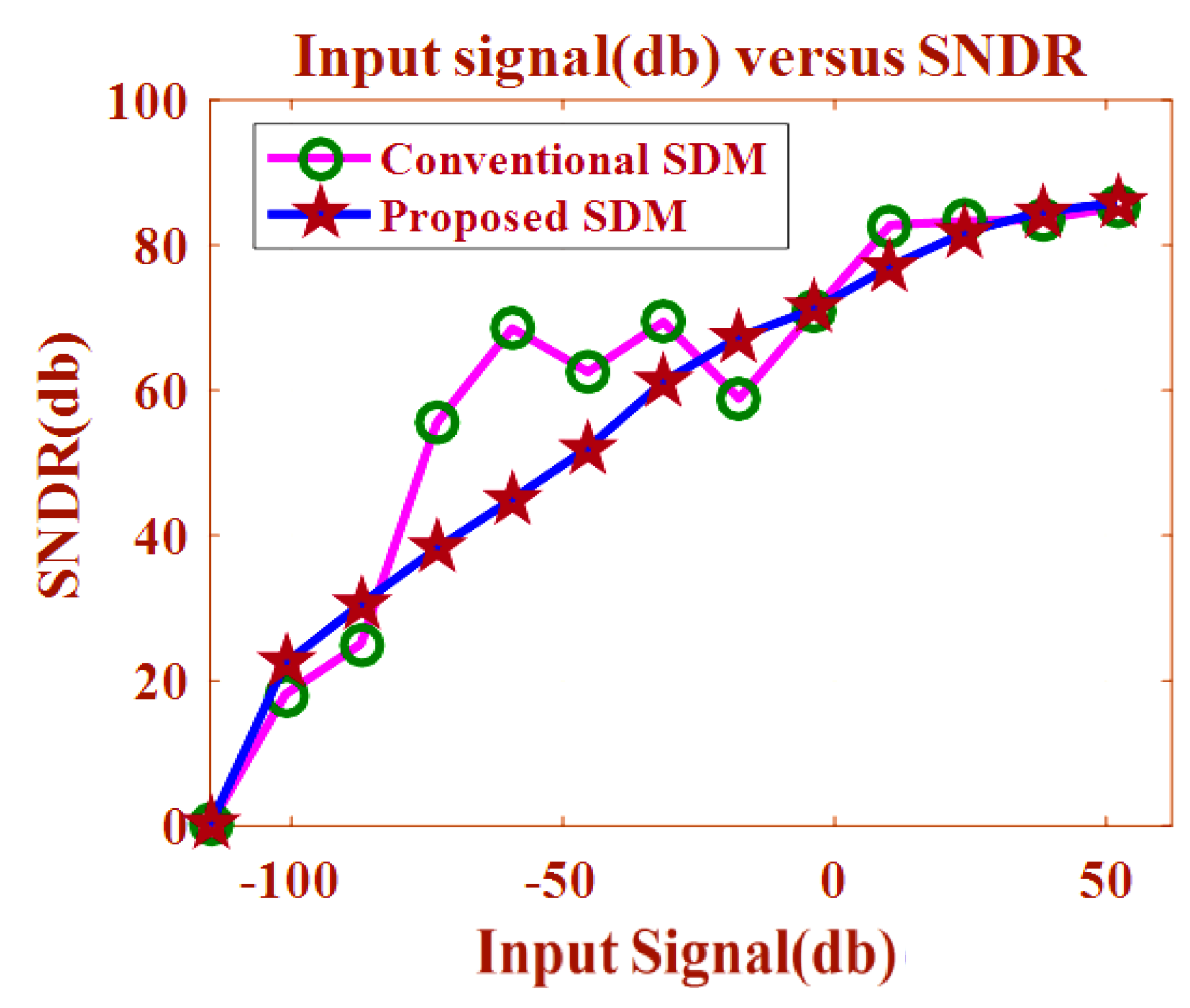

Simulation results also predict that the proposed architecture obtains higher SQNR as compared to 2nd order EFM due to aggressive noise shaping and stability as acknowledged in

Table 1. The SQNR versus input signal level are also plotted for 2nd order EFM and 3rd order Hybrid MASH-EFM as displayed in

Figure 15. The SQNR value in Hybrid MASH-EFM architecture reaches to 86.68 dB which is greater than EFM for the same input signal.

As discussed earlier, the proposed architecture effectively mitigates the problem of limit cycle which results in the improvement of spurious-free dynamic range (SFDR). SFDR is defined as the ratio of the RMS amplitude of the digital signal to the RMS value of the strongest spurious components. In

Figure 16, the red and blue curves represent the SFDR of proposed and conventional architecture respectively. The peak SFDR achieved during simulation is about 76.53 dB, which is much greater than EFM. The minimum and maximum value of SFDR is 75 dB and 76.53 dB respectively, which show that the deviation of SFDR during the whole conversion process is negligible. Therefore, the next positive point in terms of its stability is that it doesn’t degrade its SFDR. While the minimum and maximum value of SFDR of existing EFM architecture is −38 dB and −36 dB, which represents the poor control over the stability issues. Also, the blue curve demonstrates that the SFDR decreases during the whole conversion process which eventually degrades its SFDR. Hence the proposed architecture provides more stability than the conventional architecture. The simulation results emphasize that it reduces spurious tones and limit cycles in its spectrum quite effectively.

The next parameter which indicates the efficiency of any digital-to-analog converter is signal-to-noise and distortion ratio (SNDR) [

38]. The red and blue curves represent the SNDR of EFM and 2-stage feed forward filters based Hybrid MASH-EFM respectively in

Figure 17. The maximum SNDR of EFM reaches to 84.56 dB. It can also be seen that the EFM offers degradation in SNDR due to increased noise floor at some higher frequencies. While the proposed architecture achieves the SNDR equals to 85. 24 dB. Once again, dithering proves to be very useful in order to get rid of SNDR degradation by making the noise floor uniform over the whole spectrum.

Usually, the overloading effect of the quantizer increases as the ENOB increases. Due to the increase in SNDR in a proposed architecture, the ENOB increases to 14.16. While in the case of 2nd order conventional EFM, the ENOB is 12.20. There is a minor difference between the ENOB of these two architectures. Hence, the proposed architecture achieves outstanding improvement in the performance metrics without overloading the quantizer.

Another main advantage of two-stage feed forward delays and Hybrid MASH-EFM architecture is the use of digital filters and discrete transfer functions. Therefore, this architecture gets rid of complications of mapping of discrete transfer functions to continuous transfer functions. Hence, this architecture reduces hardware complexity issues due to the use of digital filters.

6. Conclusions and Future Recommendations

This work demonstrates that the proposed architecture is effective as compared to existing EFM architecture due to its prominent noise shaping technique. The digital delays are used efficiently to prevent the quantizer from saturation at the higher input levels. Dithering is effectively used to remove limit cycles, idle tones and restricting the noise floor uniform over the entire spectrum. Similarly, the quantization noise follows the NTF curve, which reveals that the proposed architecture does not behave non-linearly at the higher input levels. The SQNR reaches to 86.68 db which shows significant improvement than conventional EFM, which attains SQNR of 75.25 dB, due to the better suppression of quantization noise in the signal bandwidth. Similarly, the superiority of the proposed architecture can also be observed by the improvement of SNDR value up to 85.24 dB, which is higher than the SNDR of the conventional EFM, while the conventional EFM obtains SNDR of 84.56 dB.. The other performance parameters are also super-eminent as illustrated in

Table 1. The proposed architecture also avoids the mapping of continuous transfer functions to discrete transfer functions as it is completely designed in the z-domain. The other main aspect of the proposed architecture is that the ENOB achieved by the third-order Hybrid MASH-EFM is below 15 (not high), which ensures less transistor count because of using only one bit quantizer and digital loop filters. This modulator gains high performance metrics with greater stability for both time varying and non-time varying inputs. Because it avoids the overflow conditions which make it more robust.

In future, the new proposed SDM architecture will be implemented on hardware. Digital filters will consist of integrators, which can easily be employed using adders and the feedback path. The delays will be implemented using counters. Similarly, 1-bit quantizer will consist of only few comparators. So, system level designing of this architecture will require some digital logic functions. The next work will involve its FPGA implementation.