Abstract

In this study, a frequency doubler that consists of a tunnel field-effect transistor (TFET) with dual pocket doping is proposed, and its operation is verified using technology computer-aided design (TCAD) simulations. The frequency-doubling operation is important to having symmetrical current characteristics, which eliminate odd harmonics and the need for extra filter circuitry. The proposed TFET has intrinsically bidirectional and controllable currents that can be implemented by pocket doping, which is located at the junction between the source/drain (S/D) and the channel region, to modify tunneling probabilities. The source-to-channel (ISC) and channel-to-drain currents (ICD) can be independently changed by managing each pocket doping concentration on the source and drain sides (NS,POC and ND,POC). After that, the current matching process was investigated through NS,POC and ND,POC splits, respectively. However, it was found that the optimized doping condition achieved at the device level (namely, a transistor evaluation) is not suitable for a frequency doubler operation because the voltage drop generated by a load resistor in the frequency doubler circuit configuration causes the currents to be unbalanced between ISC and ICD. Therefore, after symmetrical current matching was performed by optimizing NS,POC and ND,POC at the circuit level, it was clearly seen that the output frequency was doubled in comparison to the input sinusoidal signal. In addition, the effects of the S/D and pocket doping variations that can occur during process integration were investigated to determine how much frequency multiplications are affected, and these variations have the immunity of S/D doping and pocket doping length changes. Furthermore, the impact of device scaling with gate length (LG) variations was evaluated. Based on these findings, the proposed frequency doubler is anticipated to offer benefits for circuit design and low-power applications compared to the conventional one.

1. Introduction

In wireless communication systems, a frequency doubler, which is composed of nonlinear devices such as a Schottky device and transistors, is essential to make a stable radio frequency (RF) source with a reliable low-frequency crystal oscillator [1,2,3,4]. However, these nonlinear elements generate unwanted odd harmonics beyond the intended frequency, requiring the use of additional filtering to prevent signal distortion [5,6,7]. As a result, circuit configurations can become complex. Therefore, a single transistor-based frequency doubler, which utilizes bidirectional current characteristics, has been extensively researched with two-dimensional transition metal dichalcogenides (TDMC), graphene, carbon nanotube (CNT) devices, and tunneling field-effect transistors (TFETs). Due to their ambipolar device characteristics, which can fundamentally eliminate the odd harmonic components in the output signal, there is no requirement for additional filter circuitry [8,9,10,11,12]. For TDMC materials, MoS2 and WSe2 are representative n-type and ambipolar semiconductors, which indicate higher mobility values of 200–500 cm2 V−1 s−1 with good switching characteristics (on- and off-current ratio of 108). However, to make the circuit with those devices, a higher operating voltage is required compared to the conventional complementary MOS (CMOS) device. In addition, graphene- and CNT-based frequency doublers have high power dissipations by poor leakage current control due to their small energy bandgap.

Recently, a new concept for a frequency doubler has been proposed using a single ferroelectric FET (FeFET) with a doped hafnium oxide layer (HfO2) [13]. The operation principle of this device is that the current can be modulated by biasing to the gate due to the polarization effect caused by dipole changes in the ferroelectric layer like the conventional FeFET. Then, to realize the ambipolar characteristics, this proposed device used a gate-induced drain leakage (GIDL) current with a drain voltage (VD) control. Hence, to make the symmetrical current characteristics, the change in threshold voltage and currents, depending on the polarization up and down, is firstly required, and then the GIDL current generated between the gate and drain overlap region has to be optimized by controlling the VD. For these methodologies, it is inevitable to increase the leakage power because a high VD should be applied to make a higher GIDL current during the frequency-doubling operation, meaning that this scheme is not effective for circuit designs in terms of low-power applications.

Therefore, we proposed a new frequency doubler based on a single TFET transistor. Inherently, it is well known that TFETs have low leakage currents and steep subthreshold slopes (SSs), making them a good candidate for low-power applications [14,15,16,17,18,19,20,21,22]. This TFET differs from the metal-oxide-semiconductor field-effect transistor (MOSFET) in that it uses band-to-band tunneling (BTBT) as the carrier injection mechanism, eliminating the SS limitation (>60 mV/dec) associated with thermionic emission in MOSFETs at room temperature. In the case of an n-type TFET, its structure includes a p-type source, intrinsic channel, and n-type drain region, making it compatible with a conventional MOSFET process integration where the modification is limited to the source dopant type. Although TFETs have lower leakage current and lower temperature sensitivity compared to MOSFETs, they face a trade-off that manifests itself in a lower on-current due to increased tunneling resistance, resulting from a smaller tunneling region.

Furthermore, without any process changes, they have ambipolar current characteristics because of two types of tunneling components: a source-to-channel tunneling current (ISC) at VG > 0 and a channel-to-drain tunneling current (ICD) at VG < 0, for n-type device operations. In the conventional TFETs, it has been reported that only the source-to-channel tunneling contributes to the on-current related to the switching characteristics, while the channel-to-drain tunneling is considered to be suppressed as a leakage current. In contrast, the proposed frequency doubler utilizes both source-to-channel and channel-to-drain tunneling components to generate an output signal with doubled frequency. However, ISC and ICD are not exactly the same because of the gap in the tunneling resistance. Therefore, dual pocket doping technologies, which are applied at the interfaces between the channel and source/drain regions, are adapted to control ISC and ICD, independently, leading to symmetric current matching. Those electrical characteristics are verified with a technology computer-aided design (TCAD) device and circuit simulations with well-calibrated model parameters.

2. Device Parameters and Models

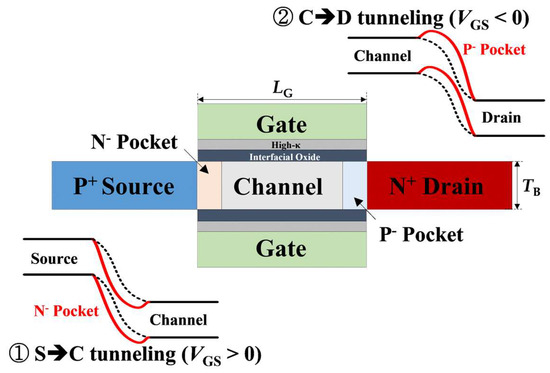

Figure 1 shows the proposed TFET structure with the dual pocket doping technologies (n-type operation). These pocket doping regions are to introduce additional dopants, either n-type (energy band down) or p-type (energy band up), into a specific region of the device, changing tunneling probabilities. In order to investigate the electrical characteristics, a gate length (LG) of 50 nm, interfacial layer thickness (Tox) of 0.7 nm, high-κ thickness (THK) of 1.5 nm, and body thickness (TB) of 10 nm were chosen. Additionally, the doping concentrations of the source (1 × 1020 cm−3), channel (5 × 1017 cm−3), and drain (1 × 1020 cm−3) were employed, respectively. To implement symmetrical current characteristics, the n− pocket doping is added between the p+ source and channel regions to control ISC while the p− pocket doping is applied between the channel and n+ drain region for changing ICD. Each pocket doping length is defined as 9 nm and the concentration is varied to perform current matching for frequency doubling. All device simulations were carried out using commercial TCAD tools of Synopsys SentaurusTM [23].

Figure 1.

Schematic of an n-type operation tunneling field-effect transistor (TFET) with dual pocket doping regions to independently control tunneling currents, source-to-channel tunneling (ISC), and channel-to-drain tunneling current (ICD). The black dotted line indicates the process condition without pocket doping and the red solid line shows the process condition with docket doping.

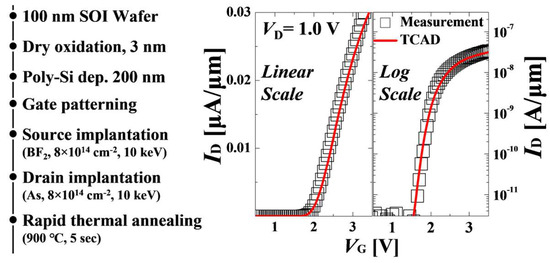

In order to accurately calculate tunneling currents, a planar TFET was fabricated on a (100) p-type silicon-on-insulator (SOI) wafer. The gate stack underwent a precise dry oxidation process at 800 °C for 30 s, resulting in the formation of a 3 nm SiO2 gate dielectric. The subsequent step involved depositing n+-doped polycrystalline silicon as a gate electrode through a Low-Pressure Chemical Vapor Deposition (LPCVD) process. Following gate patterning, the source and drain regions were achieved through a careful ion-implantation process. Notably, source and drain implantations were executed separately, employing BF2 with a dose of 8 × 1014 cm−2, a 7° tilt, and an energy of 10 keV for both the source and drain. The subsequent activation of dopants was achieved through a Rapid Thermal Process (RTP) conducted at 900 °C for 5 s. To predict the band-to-band tunneling (BTBT) generation rate (G) per unit volume in the uniform electric field, Kane’s model is used, and the fitted parameters are as follows [19]:

where F0 = 1 V/m, P = 2.5, Aind = 4.0 × 1014 cm−3·s−1, and Bind = 9.9 × 106 V·cm−1 were used to reflect the indirect tunneling components. Figure 2 shows that the simulated transfer curves (linear and log scale) are well-matched to the measured data of the fabricated TFET after the calibration process. Additionally, the OldSlotboom model was used to consider the effects of heavy doping on bandgap narrowing in the source/drain (S/D) regions. Also, Fermi statistics and the Shockley–Read–Hall recombination model were applied. The performance evaluations were conducted at a VD of 1.0 V.

Figure 2.

Process sequence of the fabricated planar TFET on a silicon-on-insulator (SOI) wafer and the calibrated drain current (ID)-gate voltage (VG) characteristics with measured results and TCAD device simulations.

3. Result and Discussions

3.1. Dual Pocket Doping Effects

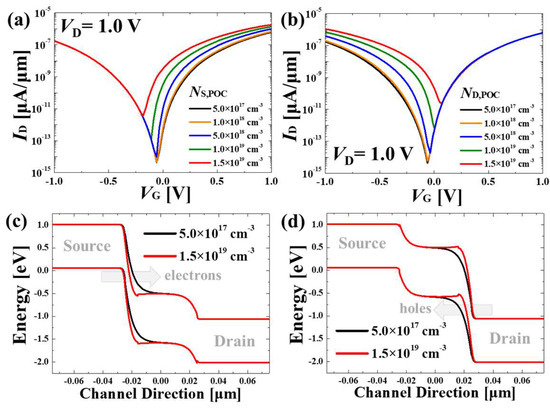

The effects of the dual pocket doping on the source and drain sides were investigated to achieve symmetrical current matching. First, Figure 3a shows the drain current (ID)-gate voltage (VG) characteristics of the proposed TFET with varying n− pocket doping concentrations on the source side (NS,POC), while the pocket doping was not applied on the drain side. As NS,POC was varied from 5.0 × 1017 cm−3 to 1.5 × 1019 cm−3, it was clearly observed that the threshold voltage for ISC (VTH,SC) becomes shifted by modulating tunneling resistances, resulting in gradual ISC changes. However, ICD hardly changed regardless of NS,POC. To understand this phenomenon induced by NS,POC, the energy band diagrams were illustrated in the channel direction at VD = 1.0 V and VG = 0.5 V with NS,POC = 5.0 × 1017 cm−3 and 1.5 × 1019 cm−3 as shown in Figure 3c. Then, it was understood that the tunneling width becomes thinner on the source side by increasing NS,POC, and there is no electrical effect on the drain side, which means that ICD is little changed. Next, the p− pocket doping concentration on the drain side (ND,POC) was examined for ICD modulation, excluding the pocket doping on the source side. Figure 3b indicates the ID-VG characteristics with VD = 1.0 V and changing ND,POC from 5.0 × 1017 cm−3 to 1.5 × 1019 cm−3. As ND,POC went up, the threshold voltage for ICD (VTH,CD) decreased and ICD increased. Compared to the NS,POC variation, it showed completely opposite characteristics. Then, the energy band diagrams were also checked with respect to different ND,POC values (Figure 3d). It was confirmed that only the drain side was locally changed with higher ND,POC, whereas little change on the source side was observed. As a result, this pocket doping technique can achieve the required ISC and ICD values independently, making it suitable for implementing current matching for frequency doublers.

Figure 3.

ID-VG characteristics with various pocket doping concentrations (a) on the source side and (b) on the drain side. Energy band diagrams at 5 nm underneath the interfacial oxide (c) for n− pocket doping concentrations on the source side were (NS,POC) = 5.0 × 1017 cm−3 and 1.5 × 1019 cm−3 at drain voltage (VD) = 1.0 V and VG = 0.5 V, and (d) for p−, the pocket doping concentrations on the drain side were (ND,POC) = 5.0 × 1017 cm−3 and 1.5 × 1019 cm−3 at VD = 1.0 V and VG = −0.5 V.

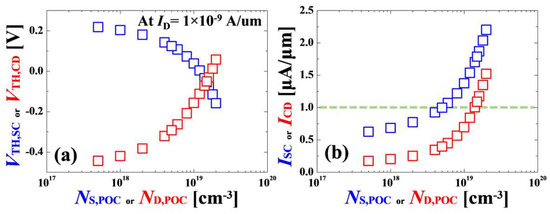

3.2. Current Matching at the Device Level

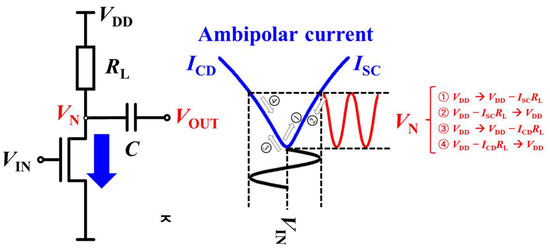

Based on dual pocket doping technology, the ISC and ICD values in the TFET device were separately optimized under the NS,POC and ND,POC conditions. Figure 4a denoted the VTH,SC and VTH,CD extracted at ID = 1.0 nA/μm, and Figure 4b showed the ISC and ICD values at VG = 1.0 V and −1.0 V with VD = 1.0 V, depending on NS,POC and ND,POC. It was obvious that both VTH and ID can be independently controlled. To conduct device level-based current matching optimization, we set the ID of 1.0 μA/μm and then selected NS,POC and ND,POC values of 5.0 × 1018 cm−3 and 1.4 × 1019 cm−3, respectively. Then, to rigorously understand the feasibility of a single TFET for performing frequency doubling, the comprehensive mixed-mode circuit level simulations with physical models were conducted with RL = 300 kΩ and C = 5 × 10−14 F as a load resistor and DC block capacitor as shown in Figure 5. The operation principle of frequency doubling is as follows. Once the sinusoidal input signal (VIN) was applied for a half cycle (0 V → VDD → 0 V), ISC flowed through the TFET and then VN was changed from VDD to VDD − ISCRL and to VDD, leading to one cycle. Subsequently, for a half-cycle VIN (0 V → −VDD → 0 V), the current flow transitioned from ISC to ICD upon reaching the minimum conduction point. Thus, ICD flowed through the TFET and VN changed from VDD to VDD − ICDRL and to VDD, resulting in one cycle. Finally, the output signal (VOUT) was obtained from VN through a DC block capacitor, and its frequency was doubled compared to VIN.

Figure 4.

(a) The threshold voltage values for ISC (VTH,SC) and ICD (VTH,CD) were extracted at ID = 1 × 10−9 A/μm using a constant current method, depending on NS,POC and ND,POC. (b) The summarized ISC (blue) and ICD (red) values were extracted at VG = 1.0 V and −1.0 V, depending on NS,POC and ND,POC.

Figure 5.

Mixed-mode circuit simulation configuration for the frequency doubler operation with a single proposed device (VDD = 1.0 V, RL = 300 kΩ, C = 5 × 10−14 F).

To evaluate the frequency doubler operation, the symmetrical ID-VG characteristics of the proposed device with the optimized condition were checked as shown in Figure 6a. Based on the mixed-mode circuit simulation, Figure 6b plotted the transient characteristics of ID according to VIN. However, it was confirmed that the ISC and ICD were unexpectedly different, even though the current matching process was performed in terms of the device level. Particularly, ICD is smaller than ISC. It was found that this phenomenon is caused by the frequency doubler circuit configuration because the VD of the proposed device was changed by VDD − IDRL, and it directly affected source-to-channel and channel-to-drain tunneling probabilities.

Figure 6.

(a) Symmetrical ID-VG characteristics with NS,POC = 5.0 × 1018 cm−3 and ND,POC = 1.4 × 1019 cm−3 at the device level. (b) Transient characteristics of VIN and ID with optimized pocket doping concentrations.

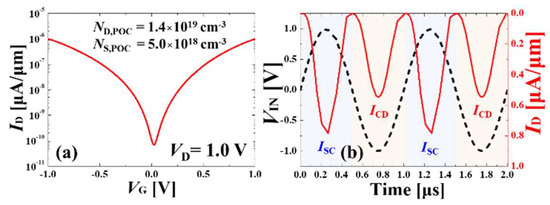

To better understand this current mismatching based on the optimized NS,POC and ND,POC conditions, the ID-VG characteristics were investigated with different RL values at the circuit configuration as shown in Figure 7a. As a reference, the optimized ID-VG characteristics at the device level, perfectly matched the ISC and ICD values, were used. Then, when RL was increased from 50 kΩ to 500 kΩ at the circuit level, it was found that the ICD was continuously reduced for a VG value higher than −0.5 V, while ISC was changed relatively less. The details of the extracted ISC and ICD are indicated in Figure 7b. It can be clearly seen that ICD variations are much greater than ISC with increasing RL. To find out the origin of this difference in variation, the energy band diagrams were examined in the channel direction with RL = 50 kΩ and 500 kΩ. To check ISC variation, once VD = 1.0 V and VG = 1.0 V were applied, the electrons in the valence band of the source started to pass through a thinned tunneling barrier between the source and channel regions as shown in Figure 7c. Since the source was directly connected to the ground, the potential energy was fixed irrespective of RL. Whereas the potential energy of the drain was affected by the voltage drop (ISCRL). Thus, as RL was increased from 50 kΩ to 500 kΩ, VD was decreased, reducing the potential difference between the source and drain. Nevertheless, the tunneling barrier near the valence band edge of the source region was changed little, allowing ISC to be slightly reduced. In the case of the ICD variation, VD = 1.0 V and VG = −1.0 V were biased to cause the holes to flow by tunneling from the drain to channel regions as shown in Figure 7d. When RL was changed from 50 kΩ to 500 kΩ, it was clearly seen that the potential energy of the drain was decreased by a higher voltage drop (ICDRL). In contrast to ISC, the tunneling barrier near the conduction band edge of the drain region was significantly modulated, allowing ICD to be remarkably reduced. Hence, the current matching, not the device-based optimization, should be required in the frequency doubler circuit configuration.

Figure 7.

For optimized pocket doping condition (NS,POC = 5.0 × 1018 cm−3 and ND,POC = 1.4 × 1019 cm−3), (a) ID-VG characteristics, and (b) summarized ISC and ICD values with various RL values at the circuit level compared to the device level. Energy band diagrams with RL = 50 kΩ and 500 kΩ (c) at VD = 1.0 V and VG = 1.0 V for ISC (d) at VD = 1.0 V and VG = −1.0 V for ICD.

3.3. Frequency Doubler Operation

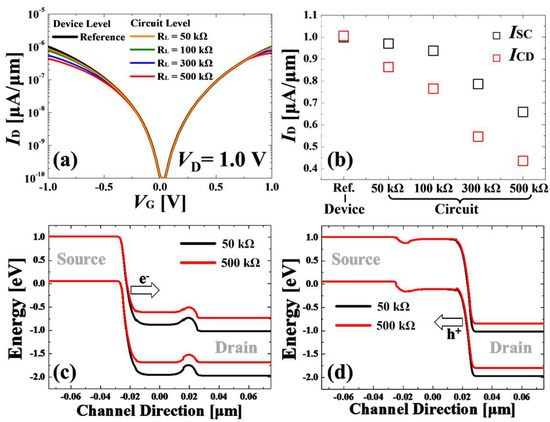

Figure 8a shows the ISC and ICD values with respect to each pocket doping concentration in terms of the device and circuit levels. The circuit level currents were extracted from the frequency doubler circuits with RL = 300 kΩ and C = 5 × 10−14 F. Here, NS,POC and ND,POC values of 1.0 × 1018 cm−3 and 1.6 × 1019 cm−3, respectively, were chosen to achieve current matching at the circuit level, and then the symmetric ID-VG characteristics were verified with the optimized doping condition as shown in Figure 8b. It was clearly seen that the ICD values at the device level are larger than those at the circuit level under the same process condition due to an ICDRL voltage drop. To check the frequency-doubling operation, the transient characteristics of ID were investigated according to VIN with a peak voltage of 1 V and a frequency of 1 MHz (Figure 8c). The changes in ISC and ICD are almost identical, making similar voltage drops. Subsequently, the output signals through a DC block capacitor were confirmed with doubled frequency compared with that of the input signal while maintaining its amplitude as shown in Figure 8d. Then, the operating frequency range of the proposed frequency doubler was evaluated. As the input frequency increases from 10 kHz to 10 MHz, it was confirmed that the output signal has a doubled frequency without signal distortions compared with the input frequency (Figure 8e,f).

Figure 8.

(a) The summarized ISC (blue) and ICD (red) values depend on NS,POC and ND,POC at the device and circuit levels. (b) Symmetrical ID-VG characteristics with NS,POC = 1.0 × 1018 cm−3 and ND,POC = 1.6 × 1019 cm−3 at the circuit level. Transient characteristics of (c) ID and (d) VOUT regarding VIN with a peak voltage of 1 V and a frequency of 1 MHz. (e) VOUT characteristics and (f) the frequency response according to VIN with different input frequencies from 10 kHz to 10 MHz.

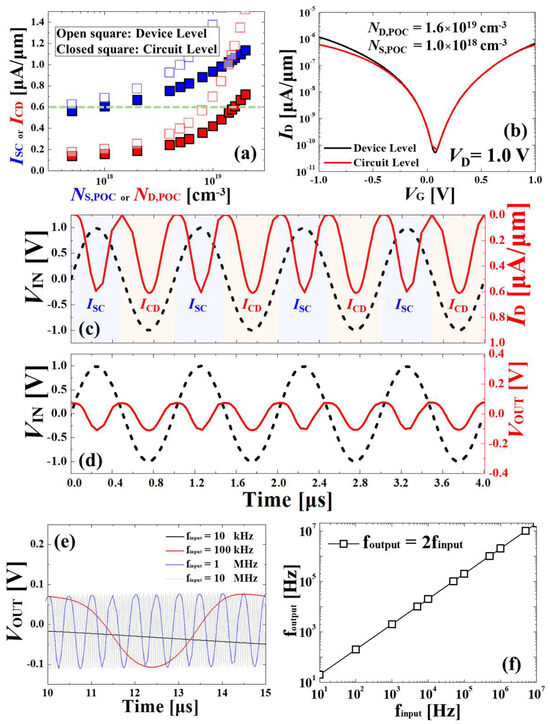

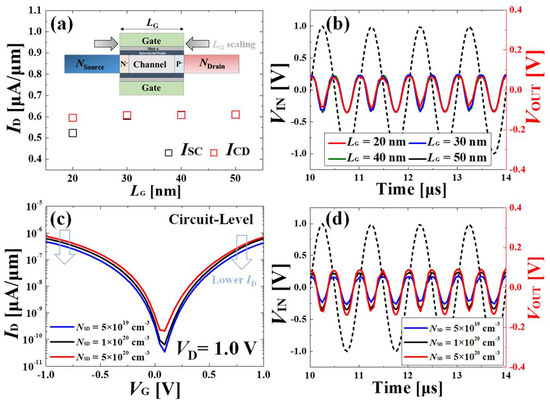

In terms of device scalability, the performance of the frequency doubler was estimated with respect to LG based on the optimized process condition. Since each pocket doping length was defined as 9 nm in the channel region, here, the minimum LG was limited to 20 nm. Therefore, as LG decreased from 50 nm to 20 nm, it was observed that both ISC and ICD were little changed as shown in Figure 9a. After that, the transient characteristics of VOUT were investigated depending on LG (Figure 9b). It was clearly seen that the frequency-doubling operations are maintained without the amplitude reduction in the output signal regardless of LG, implying that the proposed frequency doubler has the merit of exhibiting little performance degradation for device scaling, which means it is strongly immune to short channel effects (SCEs). Additionally, in order to evaluate the effects of tunneling current degradation, which directly affects the output signal, the influences of S/D doping concentration (NSD) variations, induced during process integrations, were investigated. Figure 9c indicates the transfer characteristics with NSD variations from 5 × 1019 cm−3 to 5 × 1020 cm−3, which can be varied by ion implantation and an annealing process. As the NSD became lower, the switching characteristics were degraded, leading to a reduction in ID by increasing the tunneling resistances. On the other hand, it was clearly seen that as NSD increases, ID increases due to the decreases in the tunneling barrier at the junction. Even though the magnitude of ID slightly fluctuated, it was found that the frequency doubling was properly operated as shown in Figure 9d.

Figure 9.

(a) The summarized ISC and ICD values depend on LG values from 20 nm to 50 nm, with the optimized process condition at the circuit level simulations. (b) Transient characteristics of VIN and VOUT with different LG. For the process variations, (c) the transfer and (d) transient characteristics with changing S/D doping concentrations (NSD) from 5 × 1019 cm−3 to 5 × 1020 cm−3.

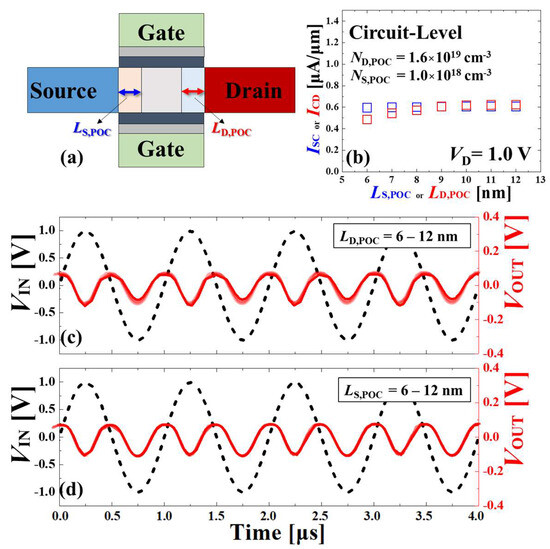

In addition, although pocket doping technology is widely used as a method to control the tunneling barrier for performance optimization, if a heavy doping concentration or diffused doping region is applied to a specific region to modulate the on-current and threshold voltage, tunneling components could occur regardless of the gate bias, resulting in performance variations. Thus, the effects of pocket doping diffusion, which can be induced during process integration, were investigated to verify the validity of the frequency doubler performance. Then, each pocket doping length on the source and drain sides (LS,POC and LD,POC) was split from 6 nm to 12 nm (Figure 10a). The ISC and ICD values, regarding LS,POC and LD,POC, were summarized in Figure 10b. As the pocket doping length was increased, both currents increased marginally. In particular, it was observed that the ICD variations appear slightly higher than the ISC variations. It was due to the doping concentration difference (ND,POC > NS,POC) determined by the current matching optimization. However, these current variations were not as large as the changes caused by NS,POC and ND,POC, which induced large VTH and ID shifts. To check how much LS,POC and LD,POC variations can affect the frequency doubler operation, the transient characteristics were evaluated. As can be seen in Figure 10c,d, it was found that LS,POC and LD,POC changes did not have a major impact on the frequency-doubling operation due to small current variations, implying that the proposed scheme has immunity against the pocket doping diffusion.

Figure 10.

(a) Schematic of pocket doping length splitting for considering dual pocket doping diffusion. (b) The summarized ISC (blue) and ICD (red) values, depending on LS,POC and LD,POC at the circuit level simulations. Transient characteristics of VOUT with changing (c) LS,POC and (d) LD,POC.

4. Conclusions

In this work, a TFET with dual pocket doping was introduced to double an input frequency, and its functionality and performances were verified using a commercial TCAD device and circuit simulations with the calibrated BTBT physical models. Achieving frequency doubling is essential to having symmetrical current characteristics because it eliminates the odd harmonics and the need for additional filter circuitry. The proposed device can have ambipolar current behavior as an intrinsic property of TFETs and can independently control the ISC and ICD by NS,POC and ND,POC changes, which modulate the tunneling barrier, respectively. The changes of the tunneling resistance on the source- and drain side were confirmed by the analysis of the energy band diagrams as well as transfer characteristics. However, although the optimized process condition, by controlling various NS,POC and ND,POC for symmetrical current matching, was found at the device level, it was unexpectedly confirmed that current mismatching occurred by VD reduction (VD = VDD − IDRD) in the frequency doubler circuit. To find out the optimized NS,POC and ND,POC values for symmetrical current matching, the circuit level should be considered. After that, the input frequency can be doubled using mixed-mode circuit simulations. From these results, it is a very meaningful result for not only the proposed one but also other devices with different channel materials and structures using the same frequency doubler circuit configuration. Moreover, it is expected that the proposed frequency doubler will be utilized for low-power applications because it has the potential to be advantageous for the circuit design due to its simple circuitry with a single tunneling device as compared to conventional frequency doublers.

Author Contributions

Conceptualization, J.H.K. and H.K.; methodology, H.K.; validation, H.K.; formal analysis, J.H.K. and H.K.; investigation, J.H.K. and H.K.; writing—original draft preparation, J.H.K. and H.K.; writing—review and editing, H.K.; visualization, J.H.K. and H.K.; supervision, H.K.; funding acquisition, H.K. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Data Availability Statement

The data presented in this study are available on request from the corresponding author.

Acknowledgments

This work was supported by the National Research Foundation of Korea (NRF) Grant funded by the Korea Government (MSIT) under Grant 2022R1G1A1009114. The EDA tool was supported by the IC Design Education Center (IDEC), Republic of Korea.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Louhi, J.; Räisänen, A.V.; Erickson, N. Cooled Schottky Varactor Frequency Multipliers at Submillimeter Wavelengths. IEEE Trans. Microw. Theory Tech. 1993, 41, 565–571. [Google Scholar] [CrossRef]

- Raisanen, A.V. Frequency Multipliers for Millimeter and Submillimeter Wavelengths. Proc. IEEE 1992, 80, 1842–1852. [Google Scholar] [CrossRef]

- Tolmunen, T.J.; Frerking, M.A. Theoretical Performance of Novel Multipliers at Millimeter and Submillimeter Wavelengths. Int. J. Infrared Millim. Waves 1991, 12, 1111–1133. [Google Scholar] [CrossRef]

- Louhi, J.; Räisänen, A. V On the Modeling and Optimization of Schottky Varactor Frequency Multipliers at Submillimeter Wavelengths. IEEE Trans. Microw. Theory Tech. 1995, 43, 922–926. [Google Scholar] [CrossRef]

- O’Ciardha, E.; Lidholm, S.U.; Lyons, B. Generic-Device Frequency-Multiplier Analysis-a Unified Approach. IEEE Trans. Microw. Theory Tech. 2000, 48, 1134–1141. [Google Scholar] [CrossRef]

- Abbasi, M.; Kozhuharov, R.; Karnfelt, C.; Angelov, I.; Kallfass, I.; Leuther, A.; Zirath, H. Single-Chip Frequency Multiplier Chains for Millimeter-Wave Signal Generation. IEEE Trans. Microw. Theory Tech. 2009, 57, 3134–3142. [Google Scholar] [CrossRef]

- Shim, D.; Kenneth, K.O. Symmetric Varactor in 130-Nm CMOS for Frequency Multiplier Applications. IEEE Electron Device Lett. 2011, 32, 470–472. [Google Scholar] [CrossRef]

- Cheng, C.; Huang, B.; Mao, X.; Zhang, Z.; Zhang, Z.; Geng, Z.; Xue, P.; Chen, H. A Graphene Based Frequency Quadrupler. Sci. Rep. 2017, 7, 46605. [Google Scholar] [CrossRef]

- Kim, T.W.; Ra, H.S.; Ahn, J.; Jang, J.; Taniguchi, T.; Watanabe, K.; Shim, J.W.; Lee, Y.T.; Hwang, D.K. Frequency Doubler and Universal Logic Gate Based on Two-Dimensional Transition Metal Dichalcogenide Transistors with Low Power Consumption. ACS Appl. Mater. Interfaces 2021, 13, 7470–7475. [Google Scholar] [CrossRef]

- Liang, B.-W.; Li, M.-F.; Lin, H.-Y.; Li, K.-S.; Chen, J.-H.; Shieh, J.-M.; Wu, C.-T.; Simbulan, K.B.; Su, C.-Y.; Kuan, C.-H.; et al. Dual-Mode Frequency Multiplier in Graphene-Base Hot Electron Transistor. Nanoscale 2023, 15, 2586–2594. [Google Scholar] [CrossRef]

- Mulaosmanovic, H.; Dünkel, S.; Trentzsch, M.; Beyer, S.; Breyer, E.T.; Mikolajick, T.; Slesazeck, S. Frequency Mixing with HfO2-Based Ferroelectric Transistors. ACS Appl. Mater. Interfaces 2020, 12, 44919–44925. [Google Scholar] [CrossRef] [PubMed]

- Madan, H.; Saripalli, V.; Liu, H.; Datta, S. Asymmetric Tunnel Field-Effect Transistors as Frequency Multipliers. IEEE Electron Device Lett. 2012, 33, 1547–1549. [Google Scholar] [CrossRef]

- Mulaosmanovic, H.; Breyer, E.T.; Mikolajick, T.; Slesazeck, S. Reconfigurable Frequency Multiplication with a Ferroelectric Transistor. Nat. Electron. 2020, 3, 391–397. [Google Scholar] [CrossRef]

- Kim, J.H.; Kim, S.; Park, B.G. Double-Gate TFET With Vertical Channel Sandwiched by Lightly Doped Si. IEEE Trans. Electron Devices 2019, 66, 1656–1661. [Google Scholar] [CrossRef]

- Han, T.; Liu, H.; Chen, S.; Wang, S.; Li, W. Design and Investigation of the High Performance Doping-Less TFET with Ge/Si0.6Ge0.4/Si Heterojunction. Micromachines 2019, 10, 424. [Google Scholar] [CrossRef]

- Kao, K.H.; Verhulst, A.S.; Vandenberghe, W.G.; Soree, B.; Groeseneken, G.; De Meyer, K. Direct and Indirect Band-to-Band Tunneling in Germanium-Based TFETs. IEEE Trans. Electron Devices 2012, 59, 292–301. [Google Scholar] [CrossRef]

- Avci, U.E.; Morris, D.H.; Hasan, S.; Kotlyar, R.; Kim, R.; Rios, R.; Nikonov, D.E.; Young, I.A. Energy Efficiency Comparison of Nanowire Heterojunction TFET and Si MOSFET at Lg = 13 nm, Including P-TFET and Variation Considerations. In Proceedings of the Technical Digest—International Electron Devices Meeting, IEDM, Washington, DC, USA, 9–11 December 2013; pp. 33.4.1–33.4.4. [Google Scholar]

- Musalgaonkar, G.; Sahay, S.; Saxena, R.S.; Kumar, M.J. Nanotube Tunneling FET with a Core Source for Ultrasteep Subthreshold Swing: A Simulation Study. IEEE Trans. Electron Devices 2019, 66, 4425–4432. [Google Scholar] [CrossRef]

- Singh, S.; Raman, A. Gate-All-Around Charge Plasma-Based Dual Material Gate-Stack Nanowire FET for Enhanced Analog Performance. IEEE Trans. Electron Devices 2018, 65, 3026–3032. [Google Scholar] [CrossRef]

- Anand, S.; Amin, S.I.; Sarin, R.K. Analog Performance Investigation of Dual Electrode Based Doping-Less Tunnel FET. J. Comput. Electron. 2016, 15, 94–103. [Google Scholar] [CrossRef]

- Singh, G.; Amin, S.I.; Anand, S.; Sarin, R.K. Design of Si0.5Ge0.5 Based Tunnel Field Effect Transistor and Its Performance Evaluation. Superlattices Microstruct. 2016, 92, 143–156. [Google Scholar] [CrossRef]

- Anam, A.; Amin, S.I.; Prasad, D.; Kumar, N.; Anand, S. Charge-Plasma-Based Inverted T-Shaped Source-Metal Dual-Line Tunneling FET with Improved Performance at 0.5 V Operation. Phys. Scr. 2023, 98, 095918. [Google Scholar] [CrossRef]

- Synopsys Inc. Sentaurus Process User Guide—v.P-2019.03; Synopsys: Mountain View, CA, USA, 2019. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).