Programming Techniques of Resistive Random-Access Memory Devices for Neuromorphic Computing

Abstract

:1. Introduction

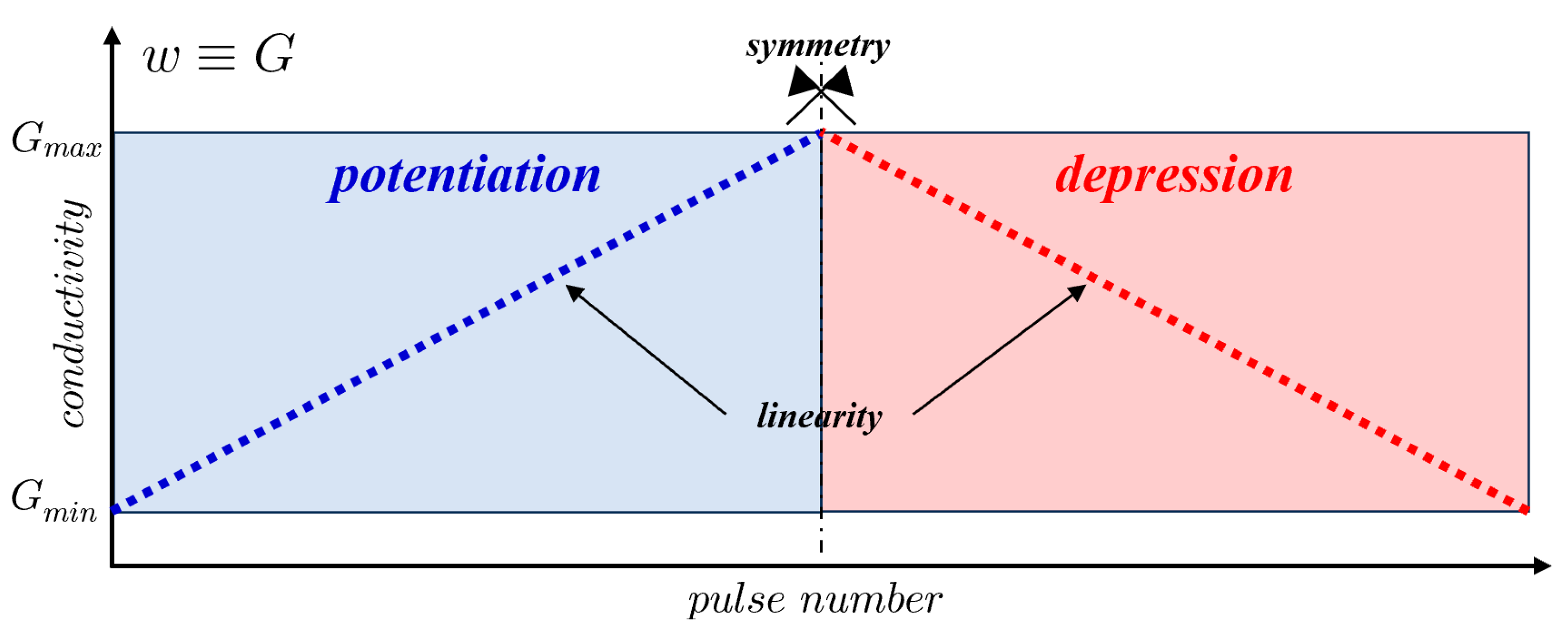

2. RRAM as a Synaptic Element

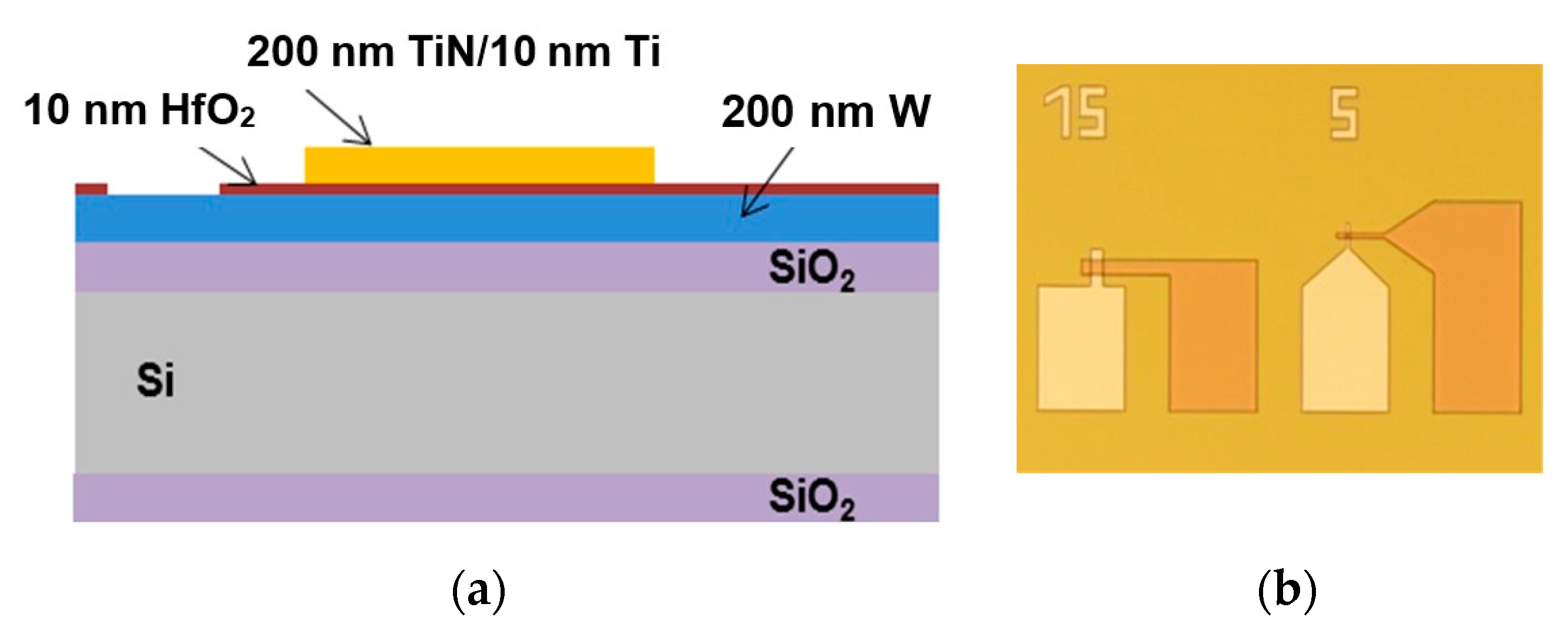

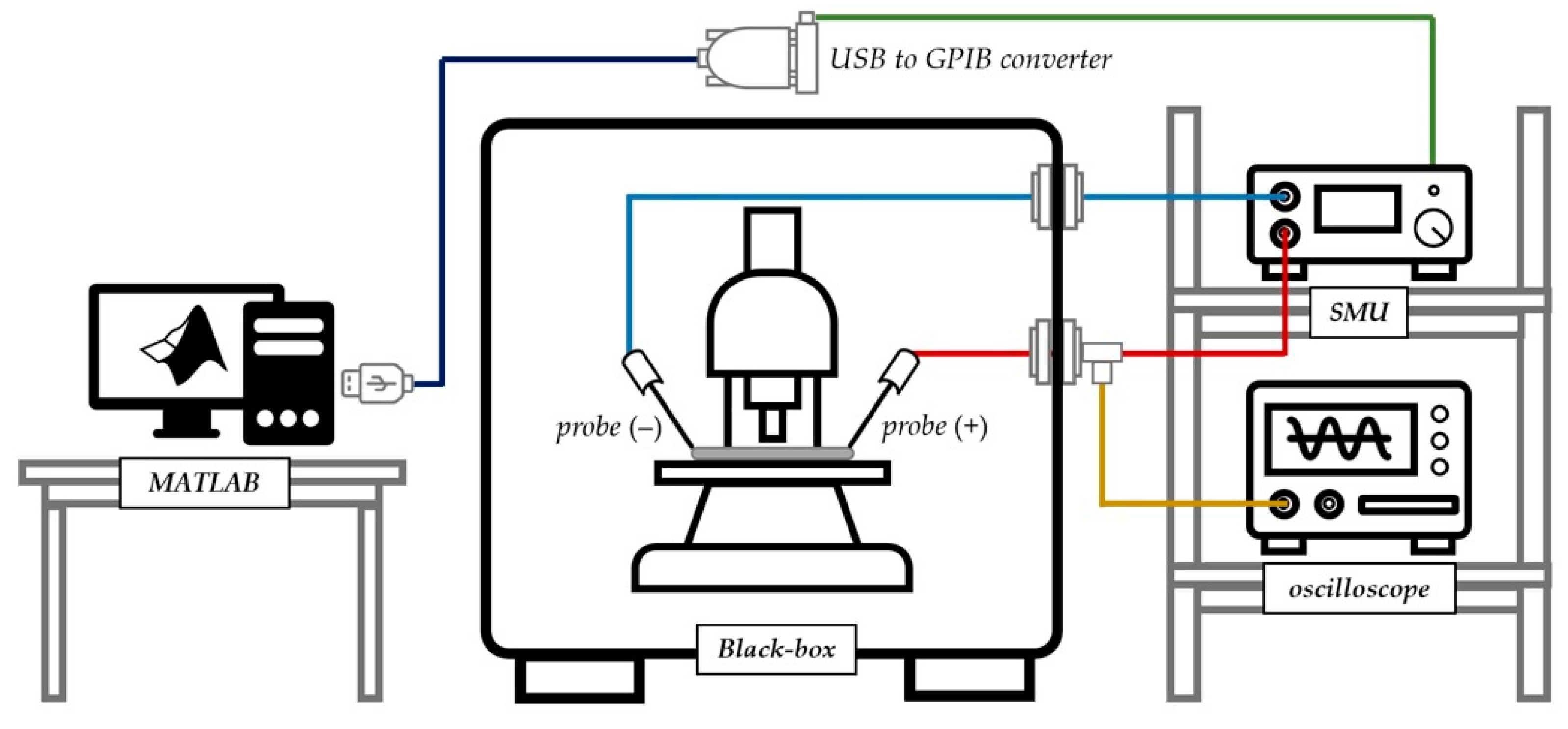

3. Materials and Methods

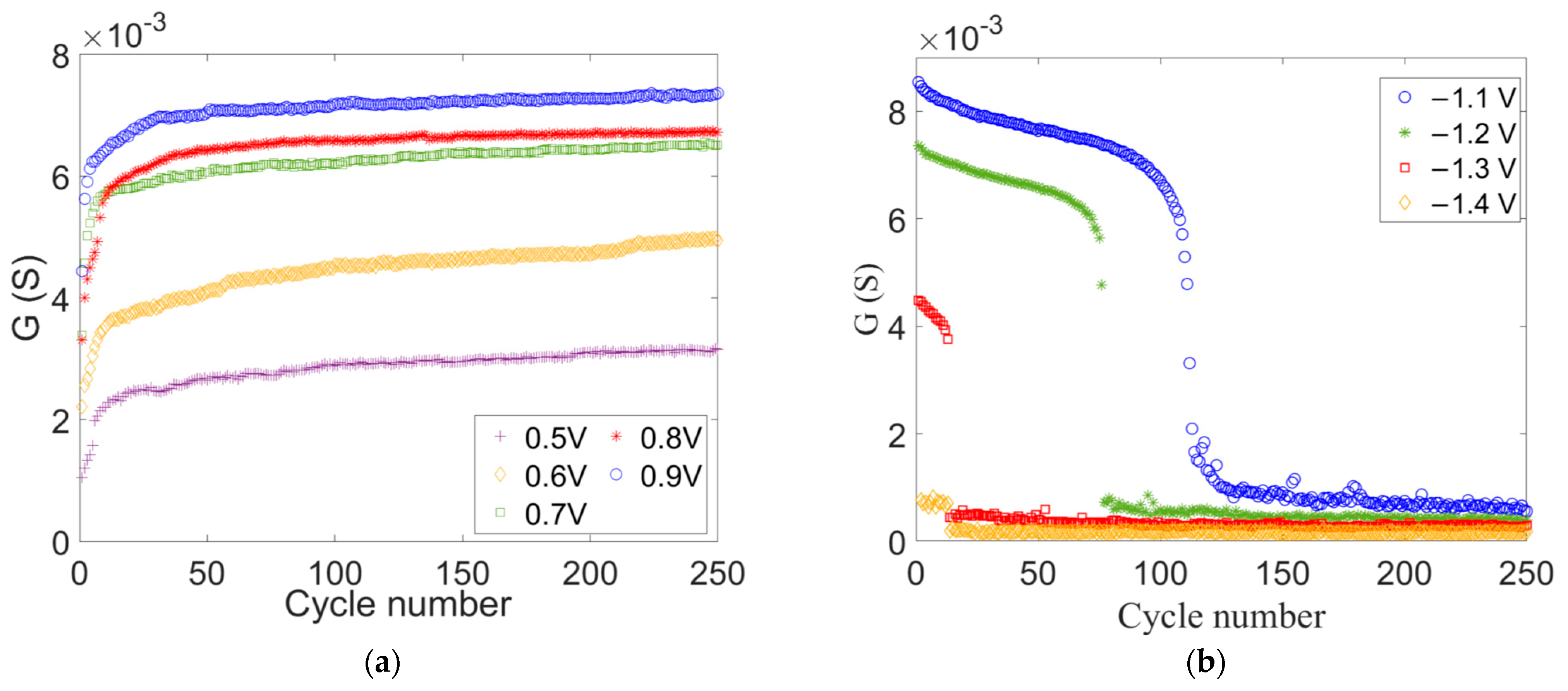

4. Experimental Results

4.1. Voltage Pulse Programming

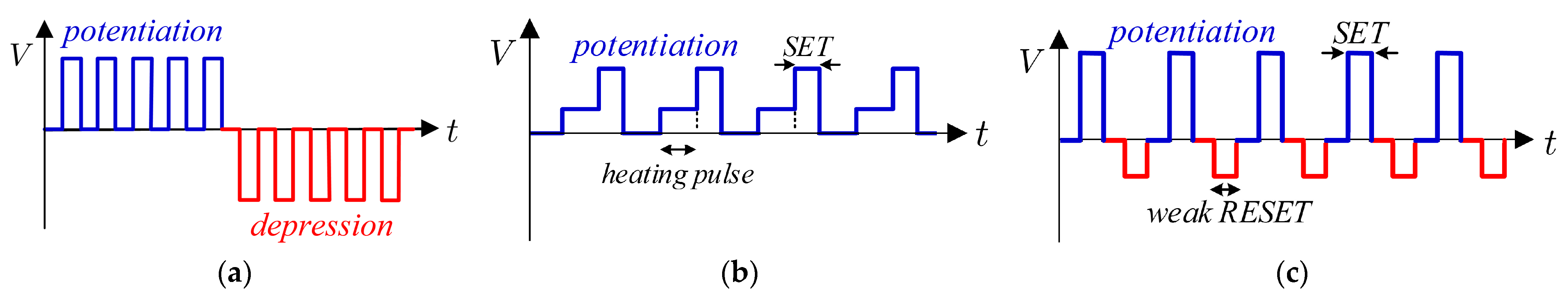

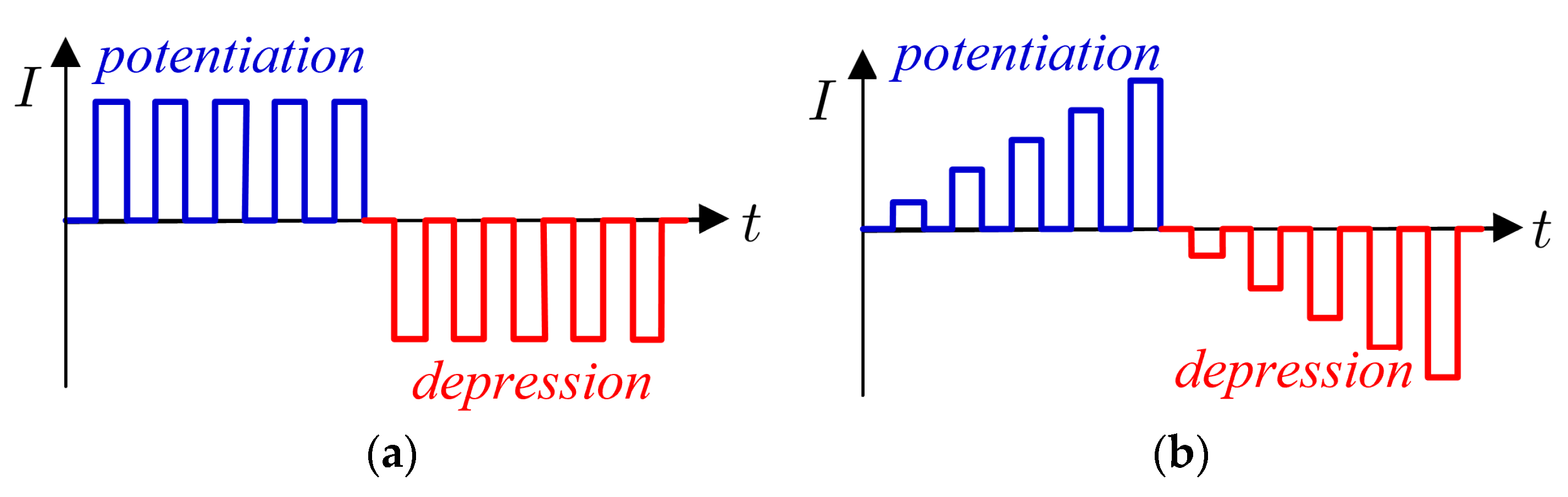

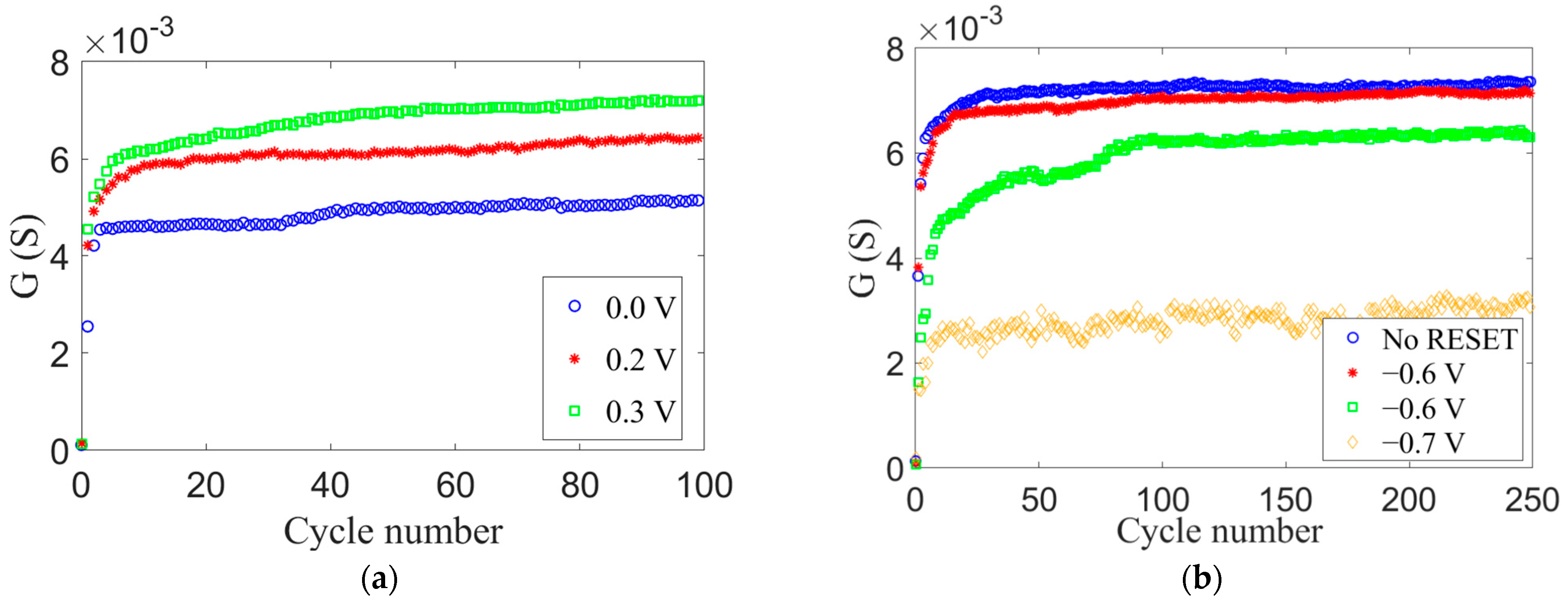

4.1.1. Identical Pulses

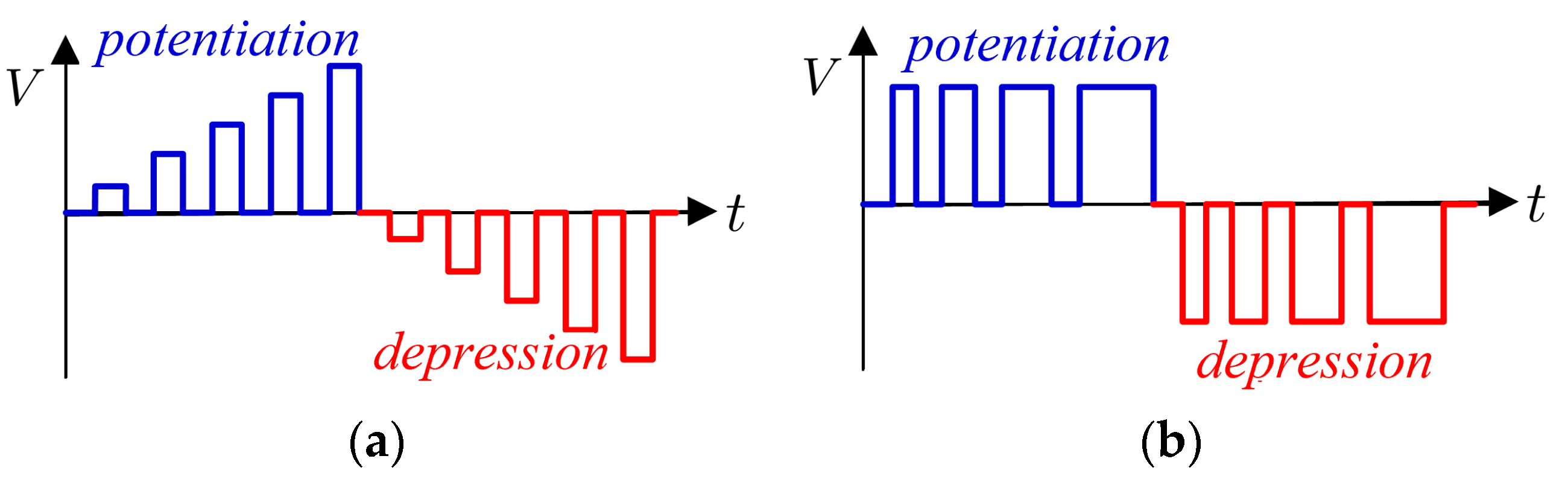

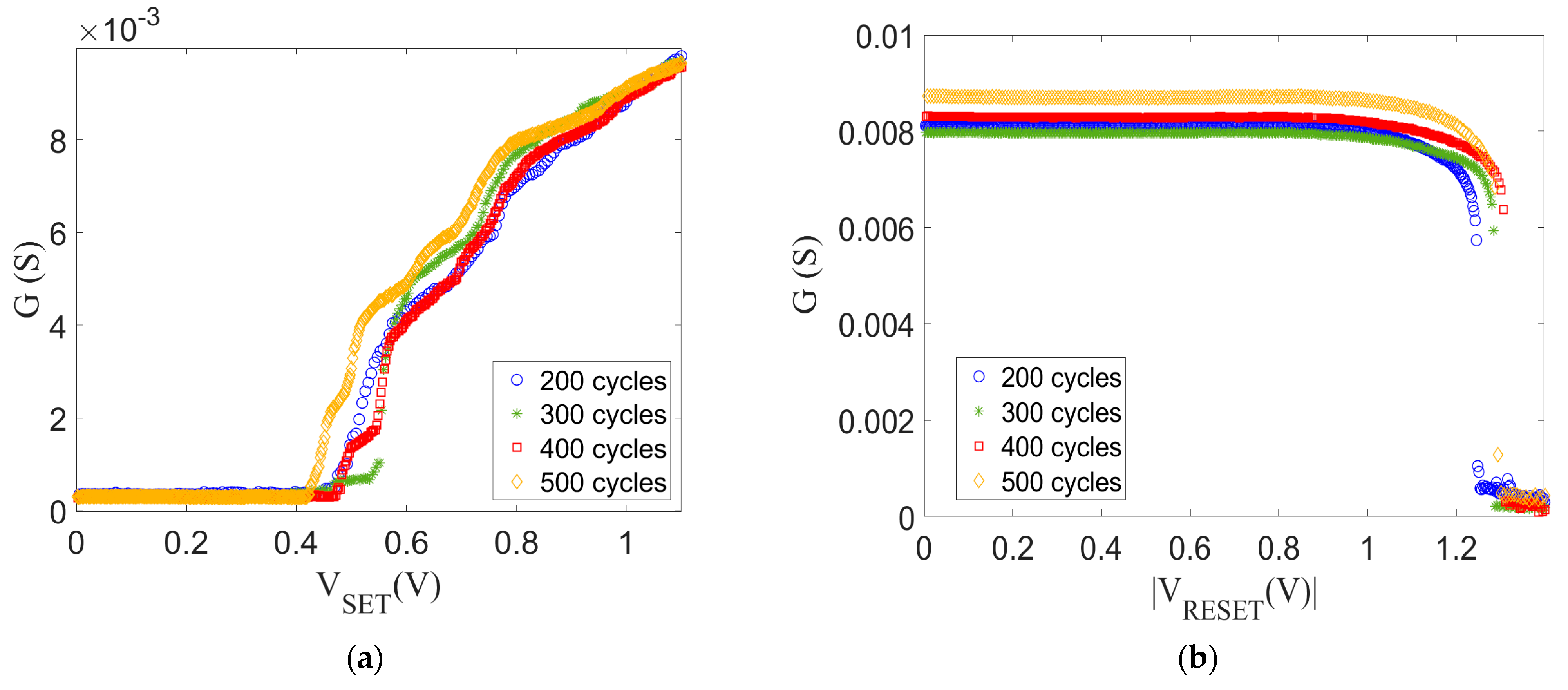

4.1.2. Nonidentical Pulses

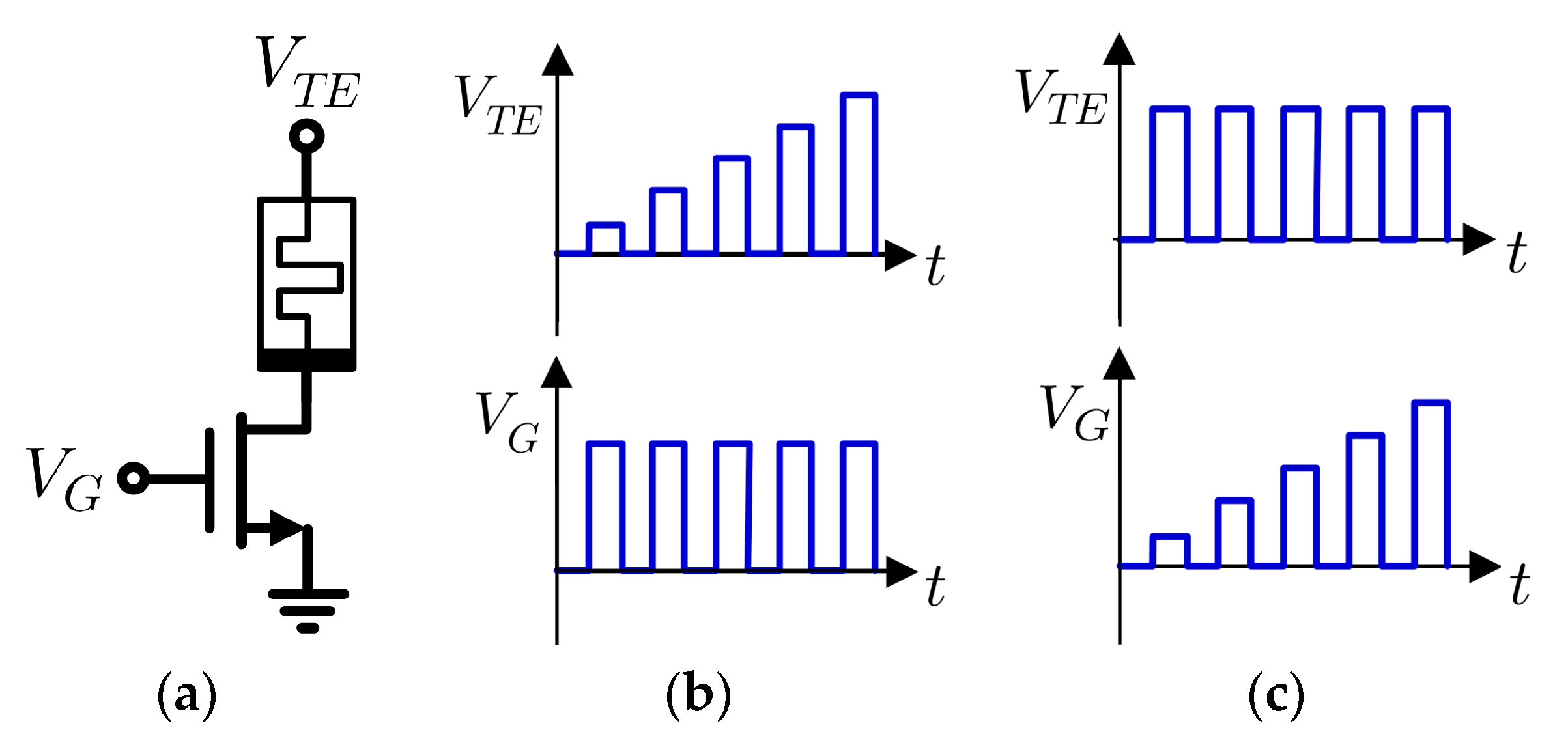

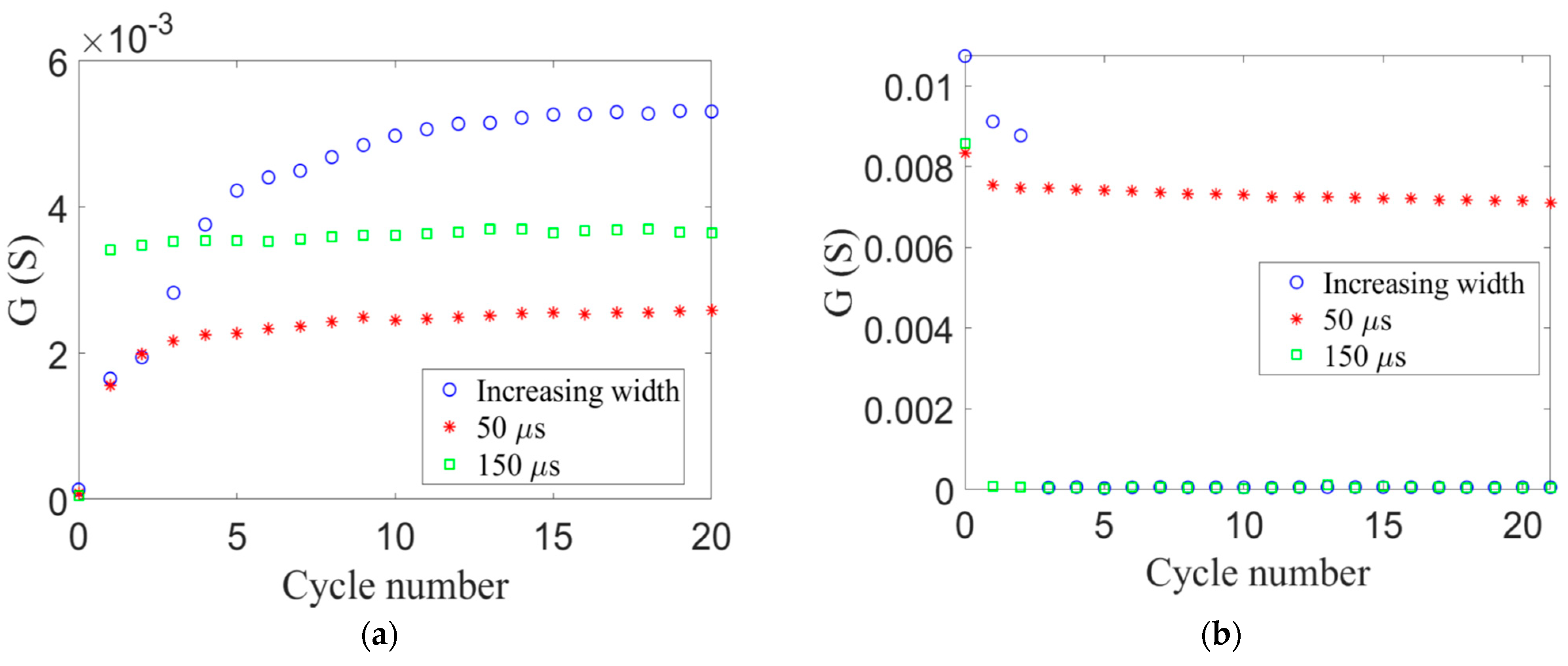

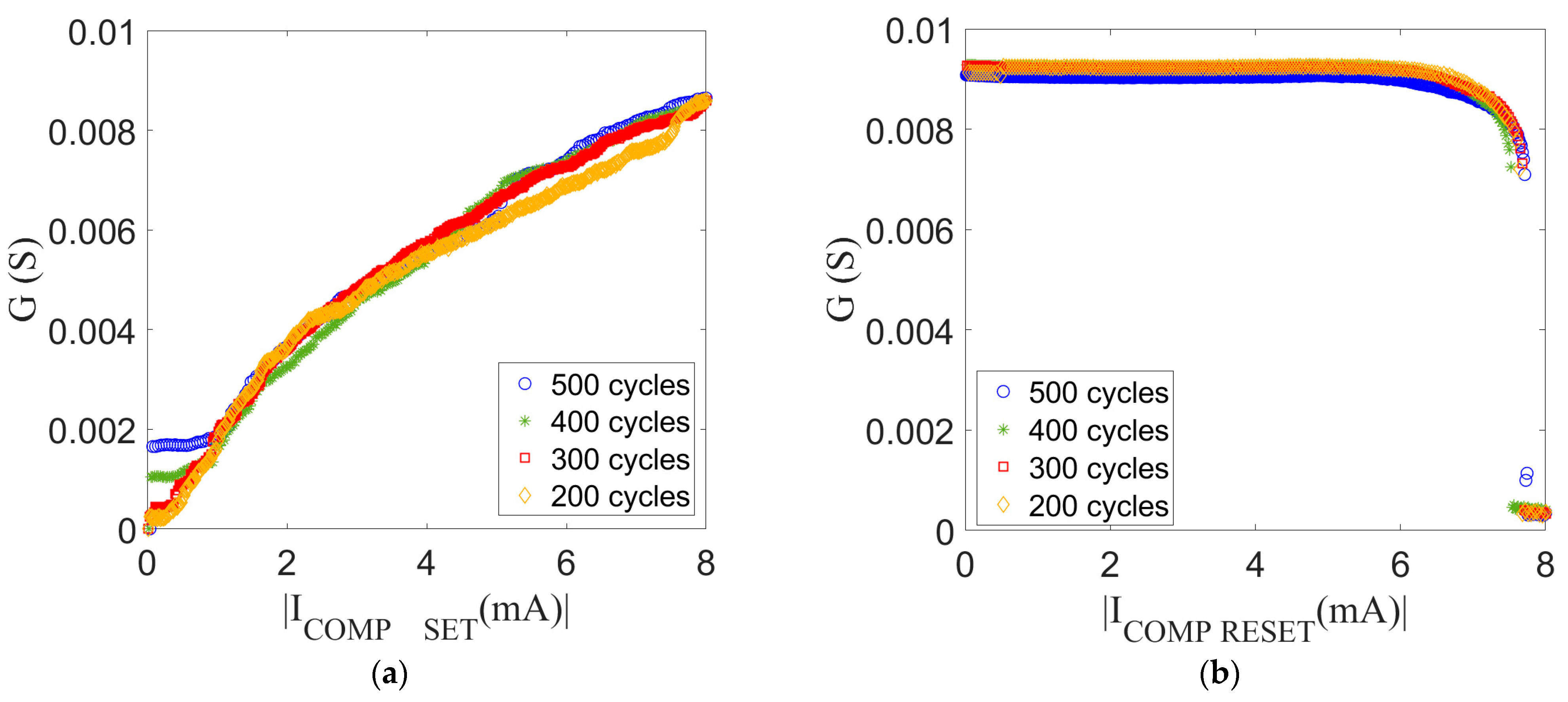

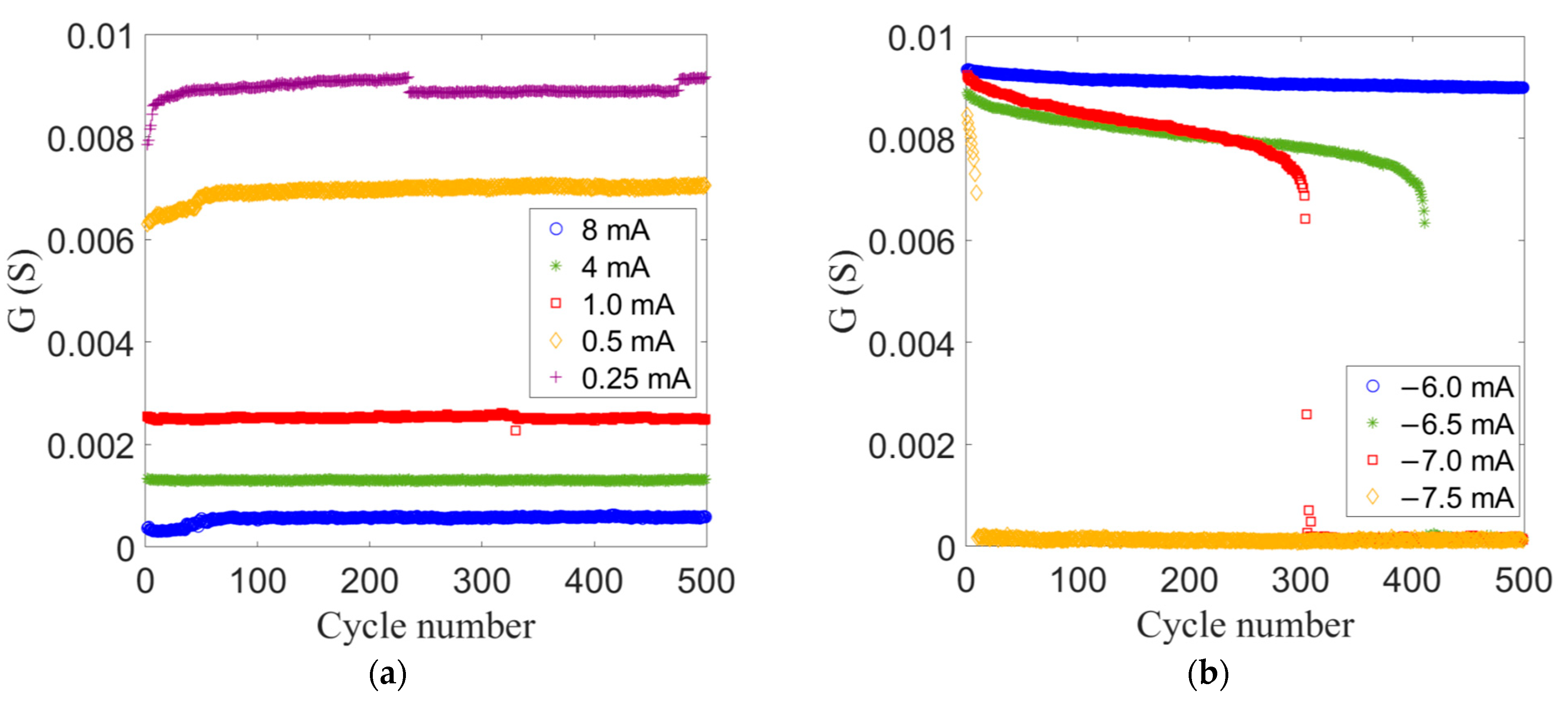

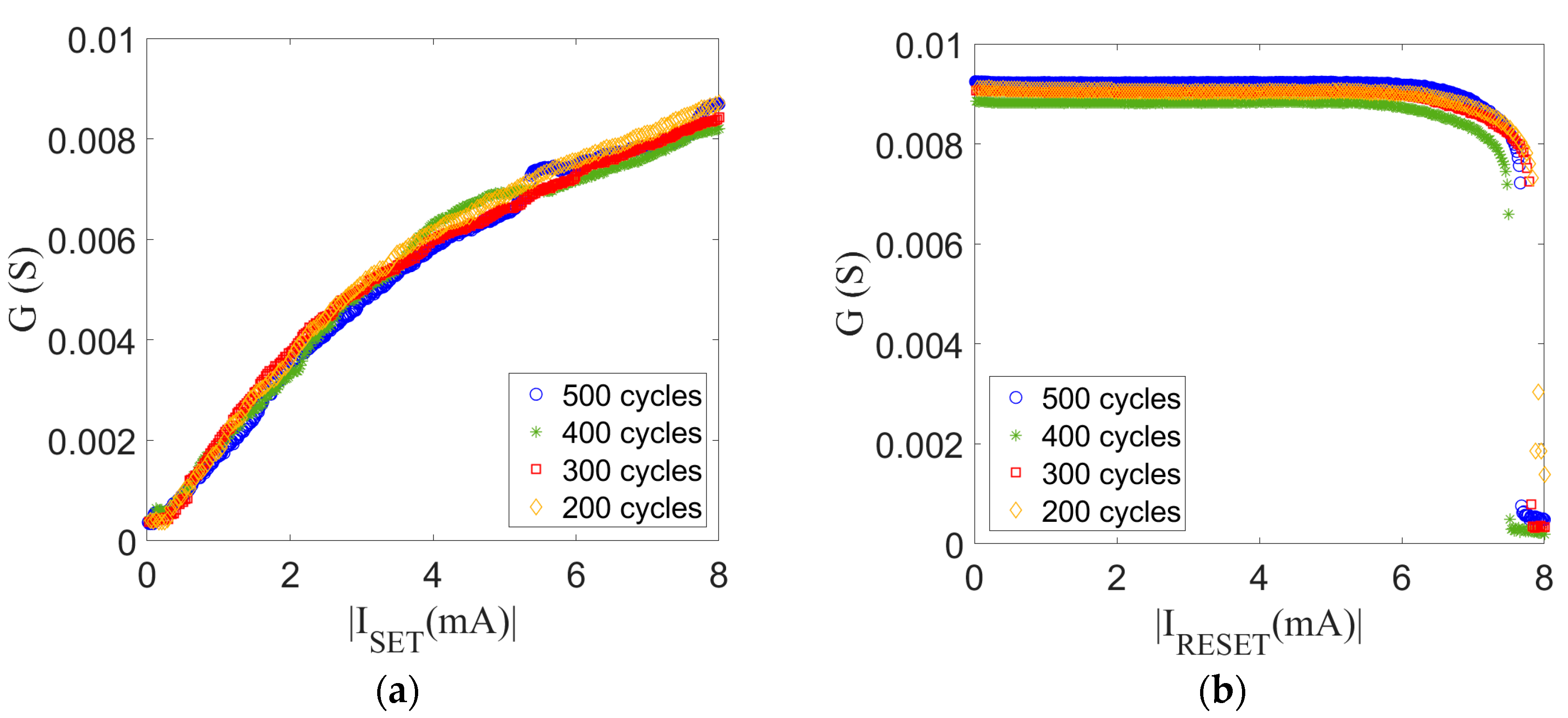

4.2. Current Pulse Programming

5. Discussion

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Furber, S. Large-scale neuromorphic computing systems. J. Neural Eng. 2016, 13, 051001. [Google Scholar] [CrossRef]

- Misra, J.; Saha, I. Artificial neural networks in hardware: A survey of two decades of progress. Neurocomputing 2010, 74, 239–255. [Google Scholar] [CrossRef]

- Yu, S.; Li, Z.; Chen, P.-Y.; Wu, H.; Gao, B.; Wang, D.; Wu, W.; Qian, H. Binary neural network with 16 Mb RRAM macro chip for classification and online training. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 16.2.1–16.2.4. [Google Scholar] [CrossRef]

- Burr, G.W.; Shelby, R.M.; Sebastian, A.; Kim, S.; Kim, S.; Sidler, S.; Virwani, K.; Ishii, M.; Narayanan, P.; Fumarola, A.; et al. Neuromorphic computing using non-volatile memory. Adv. Phys. X 2016, 2, 89–124. [Google Scholar] [CrossRef]

- Ni, Y.; Zhang, S.; Sun, L.; Liu, L.; Wei, H.; Xu, Z.; Xu, W.; Xu, W. A low-dimensional hybrid p-i-n heterojunction neuromorphic transistor with ultra-high UV sensitivity and immediate switchable plasticity. Appl. Mater. Today 2021, 25, 101223. [Google Scholar] [CrossRef]

- Ni, Y.; Liu, L.; Liu, J.; Xu, W. A High-Strength Neuromuscular System That Implements Reflexes as Controlled by a Multiquadrant Artificial Efferent Nerve. ACS Nano 2022, 16, 20294–20304. [Google Scholar] [CrossRef]

- Sun, Y.; Li, J.; Li, S.; Jiang, Y.; Wan, E.; Zhang, J.; Shi, Y.; Pan, L. Advanced synaptic devices and their applications in biomimetic sensory neural system. Chip 2023, 2, 100031. [Google Scholar] [CrossRef]

- Ielmini, D.; Ambrogio, S. Emerging neuromorphic devices. Nanotechnology 2019, 31, 092001. [Google Scholar] [CrossRef]

- Lanza, M.; Wong, H.-S.P.; Pop, E.; Ielmini, D.; Strukov, D.; Regan, B.C.; Larcher, L.; Villena, M.A.; Yang, J.J.; Goux, L.; et al. Recommended methods to study resistive switching devices. Adv. Electron. Mater. 2019, 5, 1800143. [Google Scholar] [CrossRef]

- Wong, H.S.P.; Lee, H.Y.; Yu, S.; Chen, Y.S.; Wu, Y.; Chen, P.S.; Lee, B.; Chen, F.T.; Tsai, M.J. Metal–oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Yu, S.; Guan, X.; Wong, H.-S.P. On the stochastic nature of resistive switching in metal oxide RRAM: Physical Modeling, Monte Carlo simulation, and experimental characterization. In Proceedings of the 2011 International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 17.3.1–17.3.4. [Google Scholar] [CrossRef]

- Grossi, A.; Vianello, E.; Sabry, M.M.; Barlas, M.; Grenouillet, L.; Coignus, J.; Beigne, E.; Wu, T.; Le, B.Q.; Wootters, M.K.; et al. Resistive RAM Endurance: Array-Level Characterization and Correction Techniques Targeting Deep Learning Applications. IEEE Trans. Electron Devices 2019, 66, 1281–1288. [Google Scholar] [CrossRef]

- Lee, M.J.; Lee, C.B.; Lee, D.; Lee, S.R.; Chang, M.; Hur, J.H.; Kim, Y.B.; Kim, C.J.; Seo, D.H.; Seo, S.; et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5− x/TaO2− x bilayer structures. Nat. Mater. 2011, 10, 625–630. [Google Scholar] [CrossRef] [PubMed]

- Wu, W.; Wu, H.; Gao, B.; Yao, P.; Zhang, X.; Peng, X.; Yu, S.; Qian, H. A Methodology to Improve Linearity of Analog RRAM for Neuromorphic Computing. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 103–104. [Google Scholar]

- Choi, S.; Yang, J.; Wang, G. Emerging memristive artificial synapses and neurons for energy-efficient neuromorphic computing. Adv. Mater. 2020, 32, e2004659. [Google Scholar] [CrossRef] [PubMed]

- Li, Y.; Ang, K.-W. Hardware implementation of neuromorphic computing using large-scale memristor crossbar arrays. Adv. Intell. Syst. 2020, 3, 2000137. [Google Scholar] [CrossRef]

- Woo, J.; Yu, S. Resistive Memory-Based Analog Synapse: The Pursuit for Linear and Symmetric Weight Update. IEEE Nanotechnol. Mag. 2018, 12, 36–44. [Google Scholar] [CrossRef]

- Ye, N.; Cao, L.; Yang, L.; Zhang, Z.; Fang, Z.; Gu, Q.; Yang, G.-Z. Improving the robustness of analog deep neural networks through a Bayes-optimized noise injection approach. Commun. Eng. 2023, 2, 25. [Google Scholar] [CrossRef]

- Liu, T.; Wen, W.; Jiang, L.; Wang, Y.; Yang, C.; Quan, G. A Fault-Tolerant Neural Network Architecture. In Proceedings of the 2019 56th ACM/IEEE Design Automation Conference (DAC), Las Vegas, NV, USA, 2–6 June 2019; pp. 1–6. [Google Scholar]

- Ye, N.; Mei, J.; Fang, Z.; Zhang, Y.; Zhang, Z.; Wu, H.; Liang, X. BayesFT: Bayesian Optimization for Fault Tolerant Neural Network Architecture. In Proceedings of the 2021 58th ACM/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 5–9 December 2021; pp. 487–492. [Google Scholar]

- Shen, Z.; Zhao, C.; Qi, Y.; Xu, W.; Liu, Y.; Mitrovic, I.Z.; Yang, L.; Zhao, C. Advances of RRAM Devices: Resistive Switching Mechanisms, Materials and Bionic Synaptic Application. Nanomaterials 2020, 10, 1437. [Google Scholar] [CrossRef]

- Lammie, C.; Azghadi, M.R. MemTorch: A Simulation Framework for Deep Memristive Cross-Bar Architectures. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 10–21 October 2020; pp. 1–5. [Google Scholar]

- Türel, O.; Likharev, K. CrossNets: Possible neuromorphic networks based on nanoscale components. Int. J. Circuit Theory Appl. 2003, 31, 37–53. [Google Scholar] [CrossRef]

- Minnekhanov, A.A.; Emelyanov, A.V.; Lapkin, D.A.; Nikiruy, K.E.; Shvetsov, B.S.; Nesmelov, A.A.; Rylkov, V.V.; Demin, V.A.; Erokhin, V.V. Parylene based memristive devices with multilevel resistive switching for neuromorphic applications. Sci. Rep. 2019, 9, 10800. [Google Scholar] [CrossRef]

- Wu, W.; Wu, H.; Gao, B.; Deng, N.; Yu, S.; Qian, H. Improving Analog Switching in HfOx-Based Resistive Memory with a Thermal Enhanced Layer. IEEE Electron Device Lett. 2017, 38, 1019–1022. [Google Scholar] [CrossRef]

- Alibart, F.; Sherwood, T.; Strukov, D.B. Hybrid CMOS/nanodevice circuits for high throughput pattern matching applications. In Proceedings of the 2011 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), San Diego, CA, USA, 6–9 June 2011; pp. 279–286. [Google Scholar]

- Yu, S.; Chen, P.-Y.; Cao, Y.; Xia, L.; Wang, Y.; Wu, H. Scaling-up resistive synaptic arrays for neuro-inspired architecture: Challenges and prospect. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 17.3.1–17.3.4. [Google Scholar]

- Ambrogio, S.; Balatti, S.; Cubeta, A.; Calderoni, A.; Ramaswamy, N.; Ielmini, D. Statistical Fluctuations in HfOx Resistive-Switching Memory: Part I-Set/Reset Variability. IEEE Trans. Electron Devices 2014, 61, 2912–2919. [Google Scholar] [CrossRef]

- Yao, P.; Wu, H.; Gao, B.; Eryilmaz, S.B.; Huang, X.; Zhang, W.; Zhang, Q.; Deng, N.; Shi, L.; Wong, H.-S.P.; et al. Face classification using electronic synapses. Nat. Commun. 2017, 8, 15199. [Google Scholar] [CrossRef] [PubMed]

- Frascaroli, J.; Brivio, S.; Covi, E.; Spiga, S. Evidence of soft bound behaviour in analogue memristive devices for neuromorphic computing. Sci. Rep. 2018, 8, 7178. [Google Scholar] [CrossRef] [PubMed]

- Park, S.; Sheri, A.; Kim, J.; Noh, J.; Jang, J.; Jeon, M.; Lee, B.; Hwang, H. Neuromorphic speech systems using advanced ReRAM-based synapse. In Proceedings of the 2013 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013; pp. 25.6.1–25.6.4. [Google Scholar]

- Covi, E.; Brivio, S.; Serb, A.; Prodromakis, T.; Fanciulli, M.; Spiga, S. Analog memristive synapse in spiking networks implementing unsupervised learning. Front. Neurosci. 2016, 10, 482. [Google Scholar] [CrossRef] [PubMed]

- Woo, J.; Moon, K.; Song, J.; Kwak, M.; Park, J.; Hwang, H. Optimized programming scheme enabling linear potentiation in filamentary hfo2 rram synapse for neuromorphic systems. IEEE Trans. Electron Devices 2016, 63, 5064–5067. [Google Scholar] [CrossRef]

- Jeong, Y.; Kim, S.; Lu, W.D. Utilizing multiple state variables to improve the dynamic range of analog switching in a memristor. Appl. Phys. Lett. 2015, 107, 173105. [Google Scholar] [CrossRef]

- Wang, I.-T.; Chang, C.-C.; Chiu, L.-W.; Chou, T.; Hou, T.-H. 3D Ta/TaOx/TiO2/Ti synaptic array and linearity tuning of weight update for hardware neural network applications. Nanotechnology 2016, 27, 365204–365212. [Google Scholar] [CrossRef] [PubMed]

- Milo, V.; Anzalone, F.; Zambelli, C.; Perez, E.; Mahadevaiah, M.K.; Ossorio, O.G.; Olivo, P.; Wenger, C.; Ielmini, D. Optimized programming algorithms for multilevel RRAM in hardware neural networks. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–6. [Google Scholar]

- Park, J.; Kwak, M.; Moon, K.; Woo, J.; Lee, D.; Hwang, H. TiOx-based RRAM synapse with 64-levels of conductance and symmetric conductance change by adopting a hybrid pulse scheme for neuromorphic computing. IEEE Electron Device Lett. 2016, 37, 1559–1562. [Google Scholar] [CrossRef]

- Garcia, H.; Duenas, S.; Ossorio, O.G.; Castan, H. Current Pulses to Control the Conductance in RRAM Devices. IEEE J. Electron Devices Soc. 2020, 8, 291–296. [Google Scholar] [CrossRef]

- Arumí, D.; Gómez-Pau, Á.; Manich, S.; Rodríguez-Montañés, R.; González, M.B.; Campabadal, F. Unpredictable bits generation based on RRAM parallel configuration. IEEE Electron Device Lett. 2018, 40, 341–344. [Google Scholar] [CrossRef]

- Arumí, D.; Gonzalez, M.; Campabadal, F. RRAM serial configuration for the generation of random bits. Microelectron. Eng. 2017, 178, 76–79. [Google Scholar] [CrossRef]

- Chang, C.-C.; Chen, P.-C.; Chou, T.; Wang, I.-T.; Hudec, B.; Chang, C.-C.; Tsai, C.-M.; Chang, T.-S.; Hou, T.-H. Mitigating Asymmetric Nonlinear Weight Update Effects in Hardware Neural Network Based on Analog Resistive Synapse. IEEE J. Emerg. Sel. Top. Circuits Syst. 2017, 8, 116–124. [Google Scholar] [CrossRef]

| Programming Scheme | Potentiation | Depression | |||

|---|---|---|---|---|---|

| Identical voltage pulses | ANL | Gmax − Gmin (mS) | ANL | Gmax − Gmin (mS) | |

| Identical pulses | Figure 2a | 0.871 | 1.8 | 0.5023 | 1.6 |

| Heating pulse | Figure 2b | 0.777 | 2.0 | NA 1 | NA 1 |

| Compensating weak RESET | Figure 2c | 0.789 | 3.1 | NA 1 | NA 1 |

| Nonidentical voltage pulses | |||||

| Incremental amplitude | Figure 3a | 0.392 | 9.4 | -- 2 | -- 2 |

| Incremental width | Figure 3b | 0.793 | 5.0 | -- 2 | -- 2 |

| Limiting current | Figure 4c | 0.342 | 8.5 | -- 2 | -- 2 |

| Current pulses | |||||

| Identical pulses | Figure 5a | 0.996 | 7.1 | 0.273 | 1.5 |

| Incremental amplitude | Figure 5b | 0.360 | 8.6 | -- 2 | -- 2 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Machado, P.; Manich, S.; Gómez-Pau, Á.; Rodríguez-Montañés, R.; González, M.B.; Campabadal, F.; Arumí, D. Programming Techniques of Resistive Random-Access Memory Devices for Neuromorphic Computing. Electronics 2023, 12, 4803. https://doi.org/10.3390/electronics12234803

Machado P, Manich S, Gómez-Pau Á, Rodríguez-Montañés R, González MB, Campabadal F, Arumí D. Programming Techniques of Resistive Random-Access Memory Devices for Neuromorphic Computing. Electronics. 2023; 12(23):4803. https://doi.org/10.3390/electronics12234803

Chicago/Turabian StyleMachado, Pau, Salvador Manich, Álvaro Gómez-Pau, Rosa Rodríguez-Montañés, Mireia Bargalló González, Francesca Campabadal, and Daniel Arumí. 2023. "Programming Techniques of Resistive Random-Access Memory Devices for Neuromorphic Computing" Electronics 12, no. 23: 4803. https://doi.org/10.3390/electronics12234803

APA StyleMachado, P., Manich, S., Gómez-Pau, Á., Rodríguez-Montañés, R., González, M. B., Campabadal, F., & Arumí, D. (2023). Programming Techniques of Resistive Random-Access Memory Devices for Neuromorphic Computing. Electronics, 12(23), 4803. https://doi.org/10.3390/electronics12234803