Multi-Layer QCA Shift Registers and Wiring Structure for LFSR in Stream Cipher with Low Energy Dissipation in Quantum Nanotechnology

Abstract

:1. Introduction

- Multi-layered SISO and PIPO QCA circuits using cell interactions are proposed.

- The structure, characteristics, and energy dissipation of SR structures are compared and analyzed.

- Problems with existing SR structures are presented, and ways to increase signal stability through structural improvement are proposed.

- A method for minimizing energy dissipation by changing the wiring structure is proposed.

- The novelty of the proposed research is the easy conversion of serial and parallel input and output in a multi-layer structure and the proposal of a multi-layer wiring technique.

- A modified equation that can calculate the design cost of a QCA circuit including a MUX using cell interaction is proposed.

- The performance and energy dissipation of the proposed structures and existing circuits are simulated and compared using QCADesigner and QCADesigner-E.

2. Related Works

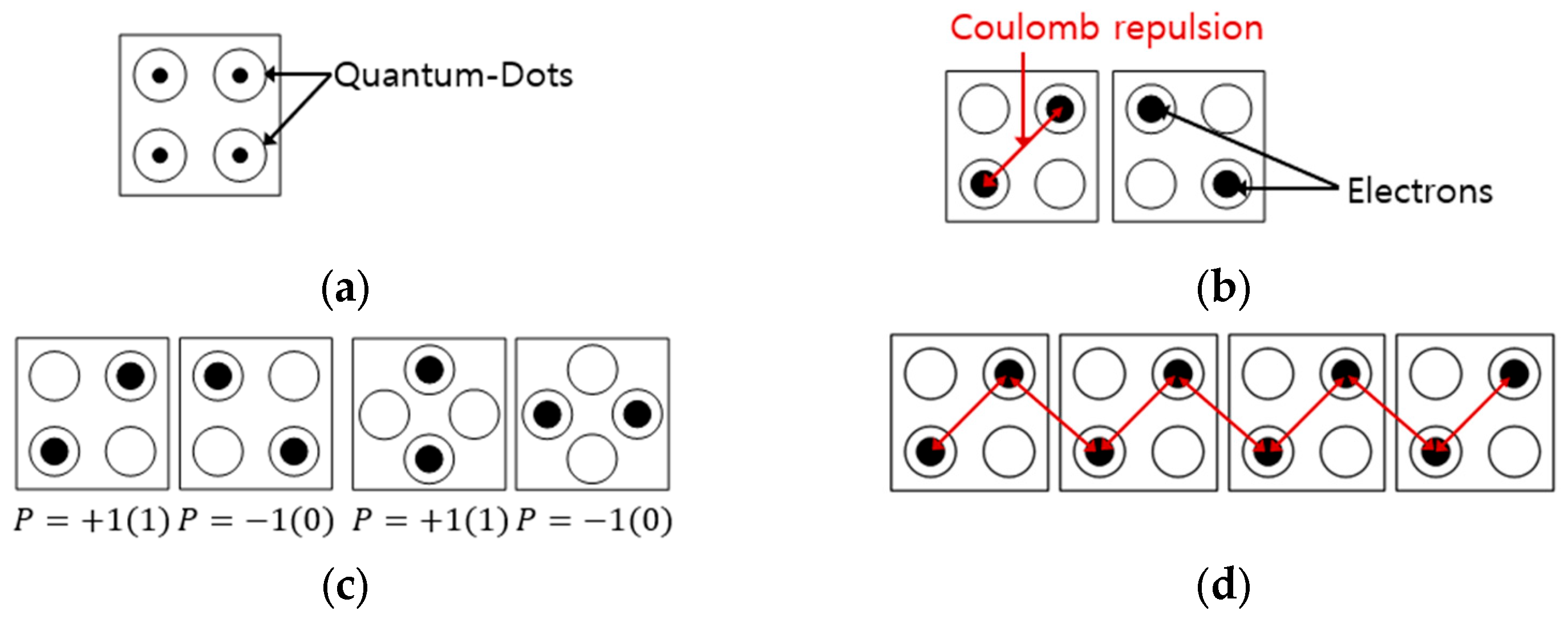

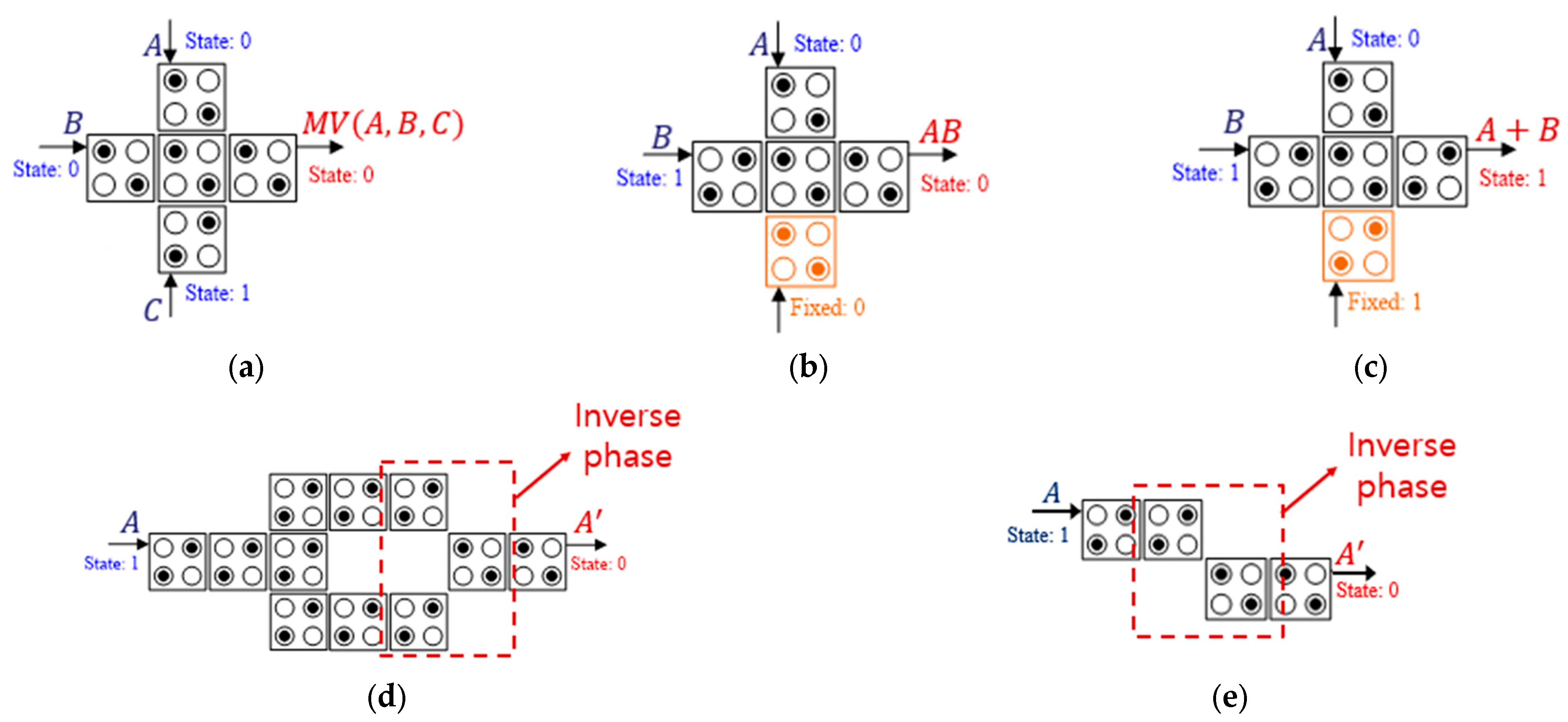

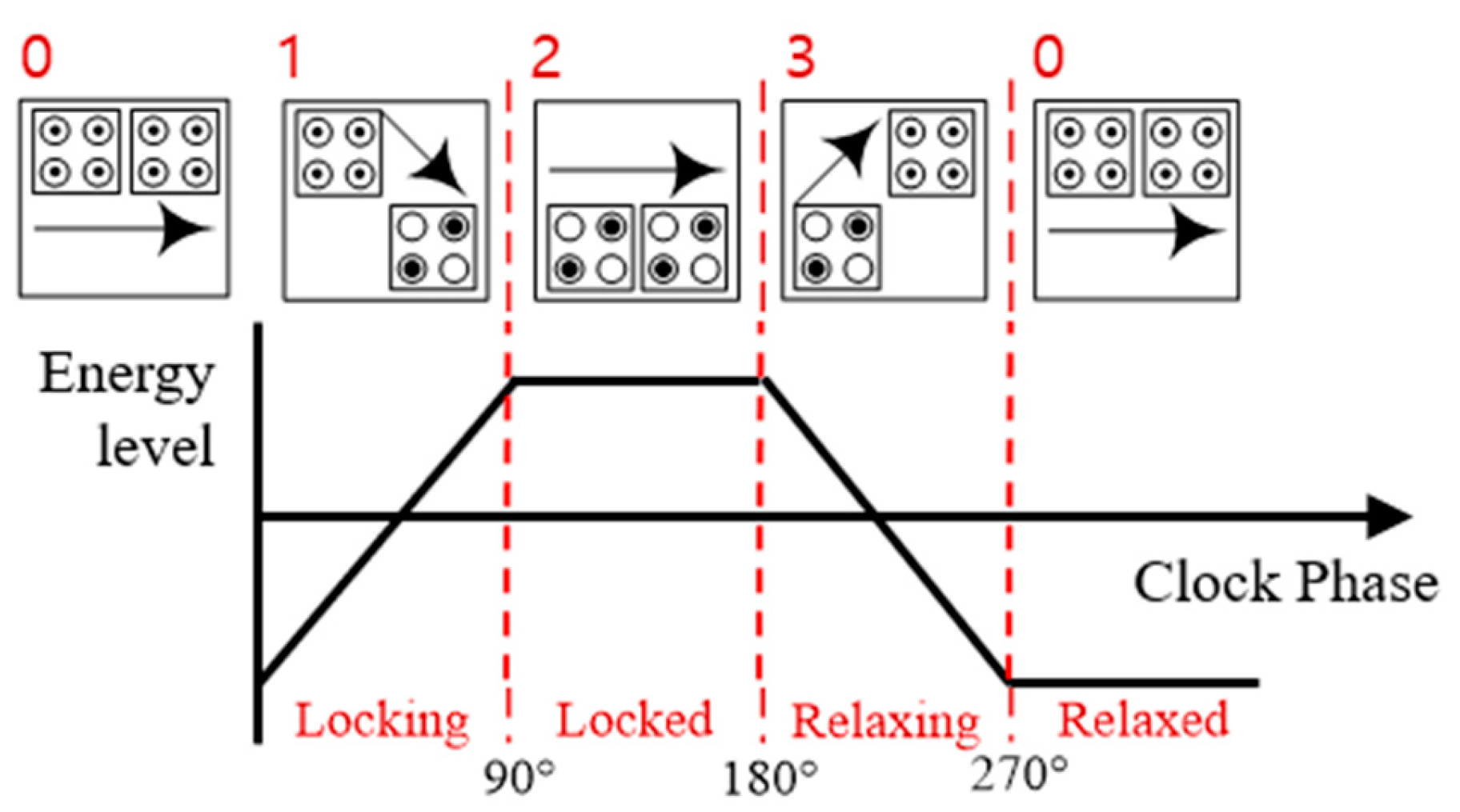

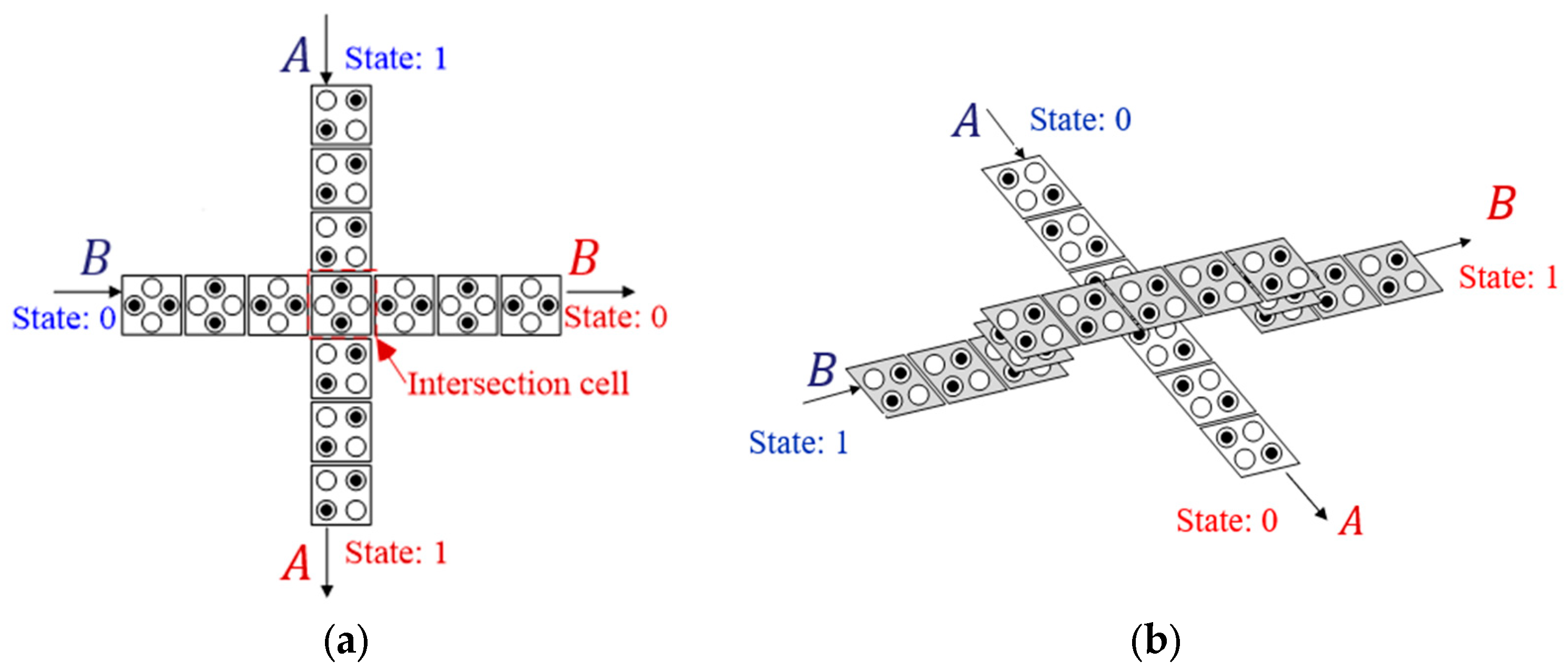

2.1. Background of QCA

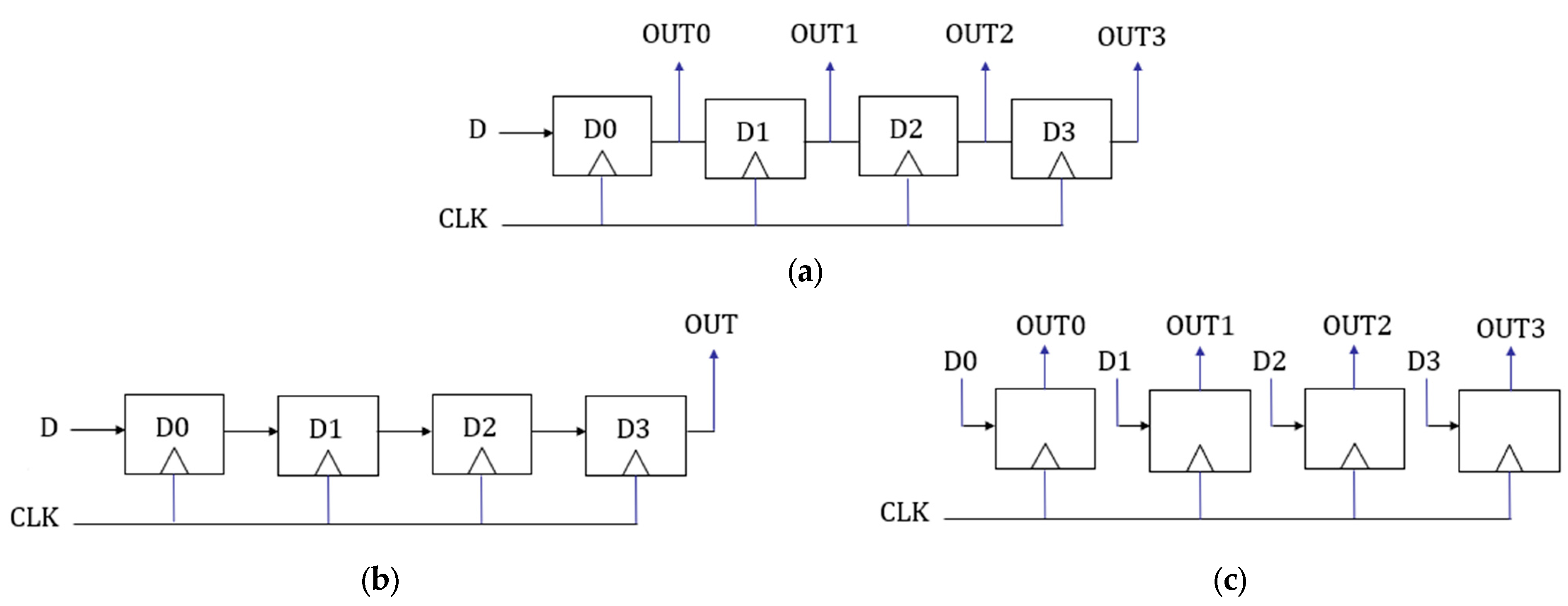

2.2. Previous QCA SR Structure

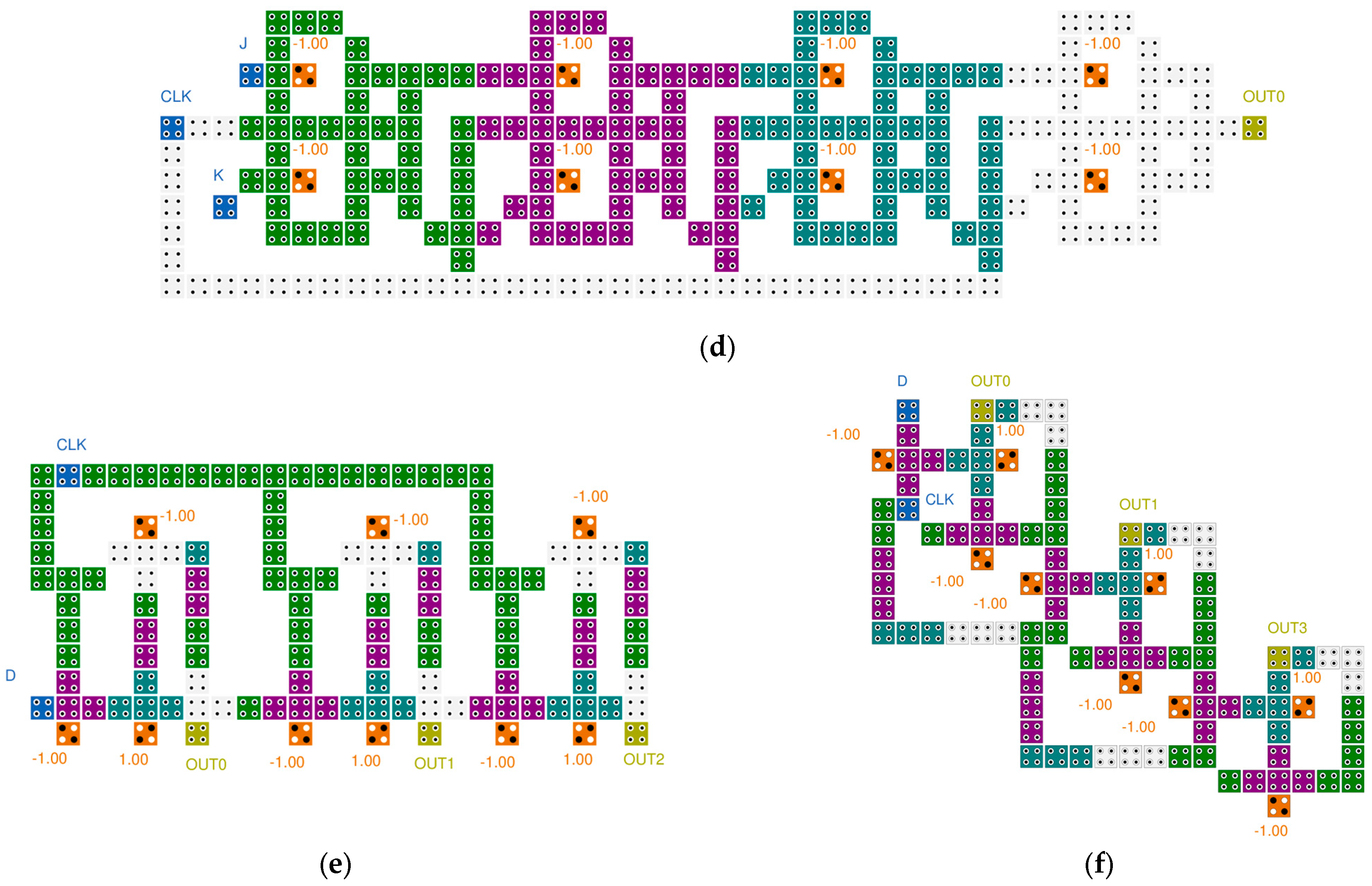

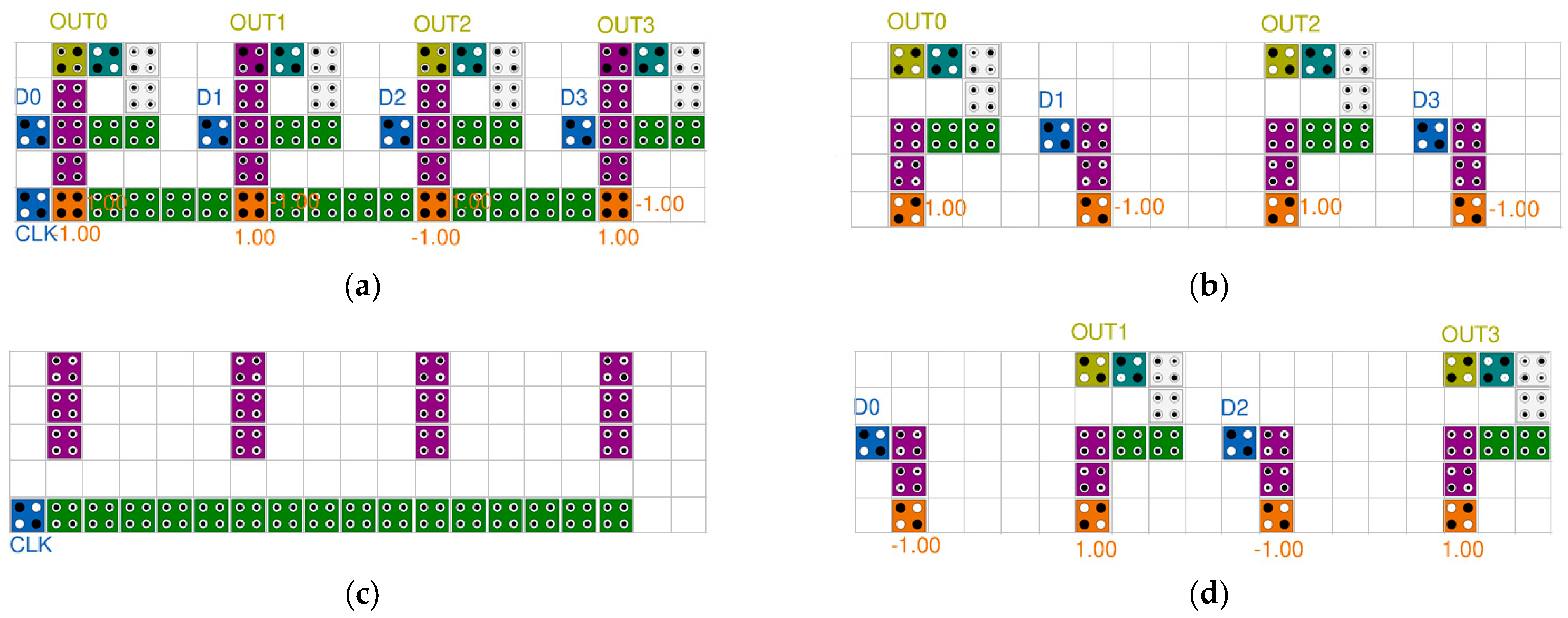

3. The Proposed Structures

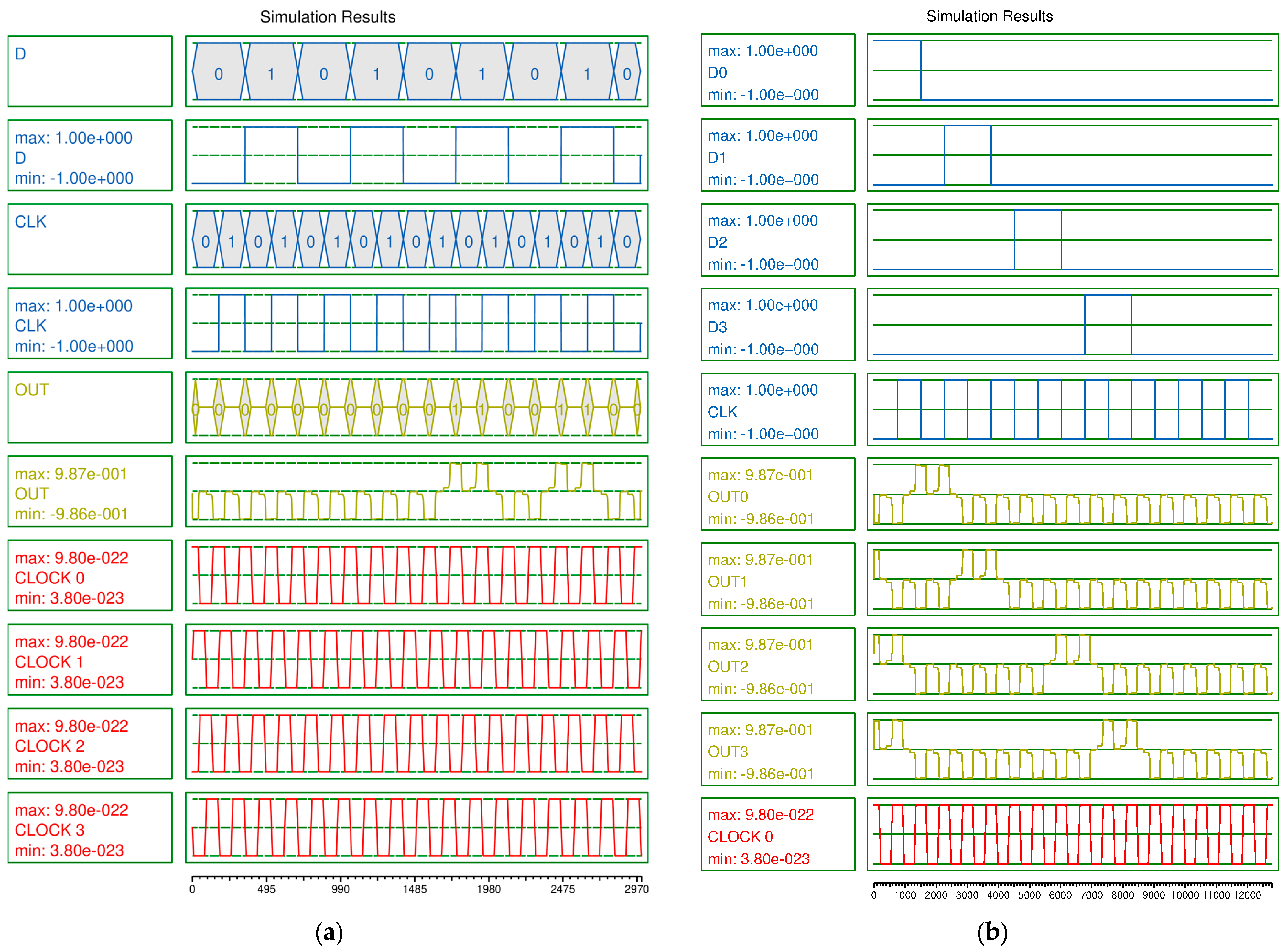

4. Structural Analysis and Simulation

4.1. Structural Analysis

4.2. Characteristic Analysis

5. Energy Dissipation Analysis

- It is useful for circuits with long single-clock phase wiring, such as SR structure clock input.

- Effective for circuits with longer wiring due to circuit expansion or relatively long wiring compared to the overall circuit size.

- Do not use it in the corner of the circuit or in the section where the clock phase changes, as it may cause problems with the overall operation of the circuit and signal stability.

- Circuits designed with existing multi-layer structures should be used carefully, considering inter-layer interference.

6. Conclusions

Funding

Data Availability Statement

Conflicts of Interest

References

- Jin, L. T5 What makes Moore’s law continue?—Recent advances in semiconductor. In Proceedings of the 7th International Conference on Asic, Guilin, China, 22–25 October 2007; p. 12. [Google Scholar] [CrossRef]

- Lent, C.S.; Tougaw, P.D.; Porod, W. Quantum cellular automata: The physics of computing with arrays of quantum dot molecules. Proc. Workshop Phys. Comput. 1994, 17, 5–13. [Google Scholar]

- Tougaw, P.D.; Lent, C.S. Logical devices implemented using quantum cellular automata. J. Appl. Phys. 1993, 75, 1818–1825. [Google Scholar] [CrossRef]

- Arden, W.M. The international technology roadmap for semiconductors—Perspectives and challenges for the next 15 years. Curr. Opin. Solid State Mater. Sci. 2002, 6, 371–377. [Google Scholar] [CrossRef]

- Seyedi, S.; Navimpipour, N.J. Ultra-efficient adders and even parity generators in nano scale. Comput. Electrcal Eng. 2021, 96, 107548. [Google Scholar]

- Vahabi, M.; Rahimi, E.; Lyakhov, P.; Otsuki, A. A novel QCA circuit-switched network with power dissipation analysis for nano communication applications. Nano Commun. Netw. 2023, 35, 100438. [Google Scholar] [CrossRef]

- Majeed, A.H. An ultra-low complexity of 2: 1 multiplexer block in QCA technology. Indones. J. Electr. Eng. Comput. Sci. 2021, 21, 1341–1346. [Google Scholar] [CrossRef]

- Rezaei, A.; Saharkhiz, H. Design of low power random number generators for quantum-dot cellular automata. Int. J. Nano Dimens. 2016, 7, 308–320. [Google Scholar]

- Kassa, S.R.; Nagaria, R.; Karthik, R. Energy efficient neoteric design of a 3-input majority gate with its implementation and physical proof in quantum dot cellular automata. Nano Commun. Netw. 2018, 15, 28–40. [Google Scholar] [CrossRef]

- Moghimizadeh, T.; Molsleh, M. A novel design of fault-tolerant RAM cell in quantum-dot cellular automata with physical verification. J. Supercomput. 2019, 75, 5688–5716. [Google Scholar] [CrossRef]

- Khosroshahy, M.B.; Moaiyeri, M.H.; Abdoli, A. Design and energy analysis of a new fault-tolerant SRAM cell in quantum-dot cellular automata. Opt. Quantum Electron. 2022, 54, 593. [Google Scholar] [CrossRef]

- Afrooz, S.; Navimipour, N.J. Fault-tolerant design of a shift register at the nanoscale based on quantum-dot cellular automata. Int. J. Theor. Phys. 2018, 57, 2598–2613. [Google Scholar] [CrossRef]

- Kassa, S.; Nema, S. Energy Efficient Novel Design of Static Random Access Memory Cell in Quantum-dot Cellular Automata Approach. Int. J. Eng. 2019, 32, 720–725. [Google Scholar]

- Majeed, A.H.; AlKaldy, E.; Albermany, S. An energy-efficient RAM cell based on novel majority gate in QCA technology. SN Appl. Sci. 2019, 1, 1354. [Google Scholar] [CrossRef]

- Gadim, M.R.; Navimipour, N.J. A new three-level fault tolerance arithmetic and logic unit based on quantum dot cellular automata. Microsyst. Technol. 2018, 24, 1295–1305. [Google Scholar] [CrossRef]

- Kim, H.I.; Jeon, J.C. Non-Restoring Array Divider Using Optimized CAS Cells Based on Quantum-Dot Cellular Automata with Minimized Latency and Power Dissipation for Quantum Computing. Nanomaterials 2022, 12, 540. [Google Scholar] [CrossRef]

- Safoev, N.; Jeon, J.C. Design and Evaluation of Cell Interaction Based Vedic Multiplier Using Quantum-Dot Cellular Autom-ata. Electronics 2020, 9, 1036. [Google Scholar] [CrossRef]

- Safoev, N.; Jeon, J.C. A novel controllable inverter and adder/subtractor in quantum-dot cellular automata using cell interac-tion based XOR gate. Microelectron. Eng. 2020, 222, 111197. [Google Scholar] [CrossRef]

- Jeon, J.C.; Almatrood, A.; Kim, H.I. Multi-Layered QCA Content-Addressable Memory Cell Using Low-Power Electronic Interaction for AI-Based Data Learning and Retrieval in Quantum Computing Environment. Sensors 2022, 23, 19. [Google Scholar] [CrossRef]

- Feng, Y.; Wang, H.; Chang, C.; Lu, H.; Yang, F.; Wang, C. A novel Nonlinear Pseudorandom Sequence Generator for the Fractal Function. Fractal Fract. 2022, 6, 589. [Google Scholar] [CrossRef]

- Roshan, M.G.; Gholami, M. Novel D Latches and D Flip-Flops with Set and Reset Ability in QCA Nanotechnology Using Minimum Cells and Area. Int. J. Theor. Phys. 2018, 57, 3223–3241. [Google Scholar] [CrossRef]

- Sasamal, T.N.; Singh, A.K.; Ghanekar, U. Design of QCA-Based D Flip Flop and Memory Cell Using Rotated Majority Gate, Smart Innovations in Communication and Computational Sciences. Adcances Intell. Syst. Comput. 2019, 670, 233–247. [Google Scholar]

- Jeon, J.C. Low-complexity QCA universal shift register design using multiplexer and D flip-flop based on electronic correlations. J. Supercomput. 2019, 76, 6438–6452. [Google Scholar] [CrossRef]

- Seyedi, S.; Navimpipour, N.J. An efficient structure for designing a nano-scale fault-tolerant 2:1 multiplexer based on quantum-dot cellular automata. Optik 2022, 251, 168409. [Google Scholar] [CrossRef]

- Jeon, J.C. Designing nanotechnology QCA–multiplexer using majority function-based NAND for quantum computing. J. Supercomput. 2021, 77, 1562–1578. [Google Scholar] [CrossRef]

- Ajitha, D.; VijayaLakshmi, K.N.V.S.; BhagyaLakshmi, K.; Mehetaj, M. 2:1 MUX Implementation Using NMV-Gate: Non Majority Gate in QCA. In Emerging Trends in Electrical, Communications, and Information Technologies; Springer: Singapore, 2020; Volume 569, pp. 557–563. [Google Scholar]

- Rezai, A.; Aliakbari, D.; Karimi, A. Novel multiplexer circuit design in quantum-dot cellular automata technology. Nano Commun. Netw. 2023, 35, 100435. [Google Scholar] [CrossRef]

- Beigh, M.R.; Mustafa, M. Novel linear feedback shift register design in quantum-dot cellular automata. Indian J. Pure Appl. Phys. (IJPAP) 2015, 52, 203–209. [Google Scholar]

- Reshi, J.I.; Banday, M.T.; Khanday, F.A. Sequential circuit design using quantum dot cellular automata (QCA). In 2015 Symposium on Computers, Communication and Electronic Engineering; University of Kashmir: Srinagar, India, 2015; pp. 143–148. [Google Scholar]

- Roshan, M.G.; Gholami, M. 4-Bit serial shift register with reset ability and 4-bit LFSR in QCA technology using minimum number of cells and delay. Comput. Electr. Eng. 2019, 78, 449–462. [Google Scholar] [CrossRef]

- Ajitha, D.; Ahmed, S.; Ahmad, F.; Rajini, G.K. Design of Area Efficient Shift Register and Scan Flip-Flop based on QCA Technology. In Proceedings of the 2021 International Conference on Emerging Smart Computing and Informatics (ESCI), Pune, India, 5–7 March 2021; pp. 716–719. [Google Scholar]

- Fan, S.; Khamesinia, M.S. An Efficient Design of Parallel and Serial Shift Registers Based on Quan-tum-Dot Cellular Automata. Int. J. Theor. Phys. 2021, 60, 2400–2411. [Google Scholar] [CrossRef]

- Kim, H.I.; Jeon, J.C. Quantum LFSR Structure for Random Number Generation Using QCA Multilayered Shift Register for Cryptographic Purposes. Sensors 2022, 22, 3541. [Google Scholar] [CrossRef] [PubMed]

- Das, J.C.; De, D. Operational efficiency of novel SISO shift register under thermal randomness in quantum-dot cellular automata design. Microsyst. Technol. 2017, 23, 4155–4168. [Google Scholar] [CrossRef]

- Divshali, M.N.; Rezai, A.; Karimi, A. Towards multilayer QCA SISO shift register based on efficient D-FF circuits. Int. J. Theor. Phys. 2018, 57, 3326–3339. [Google Scholar] [CrossRef]

- Kalyan, B.S.; Balwinder, S. Quantum dot cellular automata (QCA) based 4-bit shift register using efficient JK flip flop. Int. J. Pure Appl. Math. 2018, 118, 143–157. [Google Scholar]

- Abdullah-Al-Shafi, M.; Ziaur, R. Analysis and modeling of sequential circuits in QCA nano computing: RAM and SISO register study. Solid State Electron. Lett. 2019, 1, 73–83. [Google Scholar] [CrossRef]

- Li, T.; Kornovich, R. An Optimized Design of Serial-Input-Serial-Output (SISO) and Parallel-Input-Parallel-Output (PIPO) Shift Registers Based on Quantum Dot Cellular Automata Nanotechnology. Int. J. Theor. Phys. 2019, 58, 3684–3693. [Google Scholar] [CrossRef]

- Walus, K.; Dysart, T.J.; Jullien, G.A.; Budiman, R.A. QCADesigner: A rapid design and simulation tool for quantum-dot cel-lular automata. IEEE Trans. Nanotechnol. 2004, 3, 26–31. [Google Scholar] [CrossRef]

- Liu, W.; Lu, L.; O’Neill, M.; Swartzlander, E.E., Jr. A First Step toward Cost Functions for Quantum-Dot Cellular Automata Designs. IEEE Trans. Nanotechnol. 2014, 12, 476–487. [Google Scholar]

- Timler, J.; Lent, C.S. Power gain and dissipation in quantum-dot cellular automata. J. Appl. Phys. 2002, 91, 823–831. [Google Scholar] [CrossRef]

- Srivastava, S.; Sarkar, S. Estimation of upper bound of power dissipation in QCA circuits. IEEE Trans. Nanotechnol. 2009, 8, 116–127. [Google Scholar] [CrossRef]

- Torres, F.S.; Wille, R.; Niemann, P.; Drechsler, R. An energy-aware model for the logic synthesis of quantum-dot cellular automata. IEEE Trans. CAD Integr. Circuits Syst. 2018, 3, 3031–3041. [Google Scholar] [CrossRef]

- Qcadesigner-e. Available online: https://github.com/FSillT/QCADesigner-E (accessed on 24 August 2023).

| Circuit | Cell Count | Area (nm2) | Latency (Clock Phase) | AT Comp. | Bits | AT(# of Fixed Inputs)/Bit | Cost/3-Bit | Structure |

|---|---|---|---|---|---|---|---|---|

| [28] | 147 | 162,538 | 12 | 487,614 | 3 | 162,538(3) | 11,808 | coplanar |

| [29] | 191 | 174,420 | 17 | 741,285 | 4 | 185,321(3) | 14,703 | coplanar |

| [30] | 92 | 68,724 | 15 | 257,715 | 4 | 64,429(2) | 6273 | coplanar |

| [31] | 160 | 132,404 | 8 | 264,808 | 4 | 66,202(2) | 2298 | coplanar |

| [32] | 161 | 204,978 | 24 | 1,229,868 | 3 | 409,956(4) | 121,167 | coplanar |

| [33] | 80 | 33,124 | 3 | 24,843 | 4 | 6210(2) | 548 | multi-layer |

| Circuit | Cell Count | Area (nm2) | Latency (Clock Phase) | AT Comp. | Bits | AT(# of Fixed Inputs)/Bit | Cost/3-Bit | Structure |

|---|---|---|---|---|---|---|---|---|

| [29] | 191 | 174,420 | 17 | 741,285 | 4 | 185,321(3) | 14,703 | coplanar |

| [34] | 100 | 80,500 | 12 | 241,500 | 3 | 80,500(3) | 12,096 | coplanar |

| [35] | 120 | 28,124 | 12 | 84,372 | 3 | 28,124(3) | 15,696 | multi-layer |

| [36] | 226 | 182,684 | 4 | 182,684 | 4 | 45,671(2) | 1377 | coplanar |

| [37] | 128 | 108,564 | 12 | 325,692 | 3 | 108,564(3) | 21,168 | coplanar |

| [38] | 105 | 134,922 | 11 | 371,036 | 3 | 123,679(3) | 10,164 | coplanar |

| Ours | 80 | 33,124 | 15 | 124,215 | 4 | 31,054(2) | 7362 | multi-layer |

| Circuit | Cell Count | Area (nm2) | Latency (Clock Phase) | AT Comp. | Bits | AT(# of Fixed Inputs)/Bit | Cost/3-Bit | Structure |

|---|---|---|---|---|---|---|---|---|

| [29] | 173 | 153,640 | 5 | 192,050 | 4 | 48,013(3) | 2175 | coplanar |

| [38] | 115 | 92,204 | 3 | 69,153 | 3 | 23,051(3) | 756 | coplanar |

| [32] | 177 | 149,702 | 8 | 299,404 | 3 | 99,801(4) | 13,463 | coplanar |

| Ours | 81 | 38,491 | 3 | 28,868 | 4 | 7217(2) | 548 | multi-layer |

| Circuit | Feature | Pros | Cons |

|---|---|---|---|

| [28] | - week Inverter | - high modularity | - high AT complexity |

| [29] | - 45° rotated cell | - no inverter | - high AT complexity |

| [30] | - cell-interaction based D-latch | - low area | - high latency |

| [31] | - 5-input MV gate | - low latency | - no CLK input |

| [32] | - dual edge-triggered D F/F | - positive and negative triggering | - low scalability |

| [33] | - multi-layer structure (3-layer) | - minimized AT complexity | - high design complexity |

| [34] | - week Inverter | - low cell count | - forced control of CLK clocks |

| [35] | - multi-layer structure (5-layer) - Three types of D F/F | - minimized area | - high design complexity - low scalability |

| [36] | - JK F/F | - minimized latency | - CLK routing problem |

| [37] | - week Inverter | - available as SISO and SIPO | - forced control of the output |

| [38] | - week Inverter | - low design cost | - low signal stability |

| Ours | - multi-layer structure (3-layer) | - high scalability and signal stability - low AT complexity and design cost | - high design complexity |

| Energy Dissi. | STR. | [28] | [29] | [30] | [31] | [32] | [33] | [34] | [35] | [36] | [37] | [38] | Ours |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Total (10−2 eV) | SIPO | 6.08 (4.91) | 4.89 (4.18) | 2.62 (1.97) | 3.93 | 3.09 | 1.25 | ||||||

| SISO | 5.04 (4.11) | 4.09 (4.13) | 3.56 | 5.32 (5.14) | 5.32 (4.57) | 5.23 | 1.25 | ||||||

| PIPO | 5.03 (4.04) | 3.88 (3.87) | 6.94 (7.01) | 1.59 | |||||||||

| Average per cycle (10−3 eV) | SIPO | 5.52 (4.46) | 4.45 (3.80) | 2.38 (1.79) | 3.57 | 2.81 | 1.14 | ||||||

| SISO | 4.58 (3.74) | 3.72 (3.75) | 3.23 | 4.84 (4.68) | 4.84 (4.16) | 4.76 | 1.13 | ||||||

| PIPO | 4.57 (3.67) | 3.53 (3.52) | 6.31 (6.37) | 1.44 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeon, J.-C. Multi-Layer QCA Shift Registers and Wiring Structure for LFSR in Stream Cipher with Low Energy Dissipation in Quantum Nanotechnology. Electronics 2023, 12, 4093. https://doi.org/10.3390/electronics12194093

Jeon J-C. Multi-Layer QCA Shift Registers and Wiring Structure for LFSR in Stream Cipher with Low Energy Dissipation in Quantum Nanotechnology. Electronics. 2023; 12(19):4093. https://doi.org/10.3390/electronics12194093

Chicago/Turabian StyleJeon, Jun-Cheol. 2023. "Multi-Layer QCA Shift Registers and Wiring Structure for LFSR in Stream Cipher with Low Energy Dissipation in Quantum Nanotechnology" Electronics 12, no. 19: 4093. https://doi.org/10.3390/electronics12194093

APA StyleJeon, J.-C. (2023). Multi-Layer QCA Shift Registers and Wiring Structure for LFSR in Stream Cipher with Low Energy Dissipation in Quantum Nanotechnology. Electronics, 12(19), 4093. https://doi.org/10.3390/electronics12194093