IEC61131-3 Instruction List Language Processor for FPGAs

Abstract

:1. Introduction

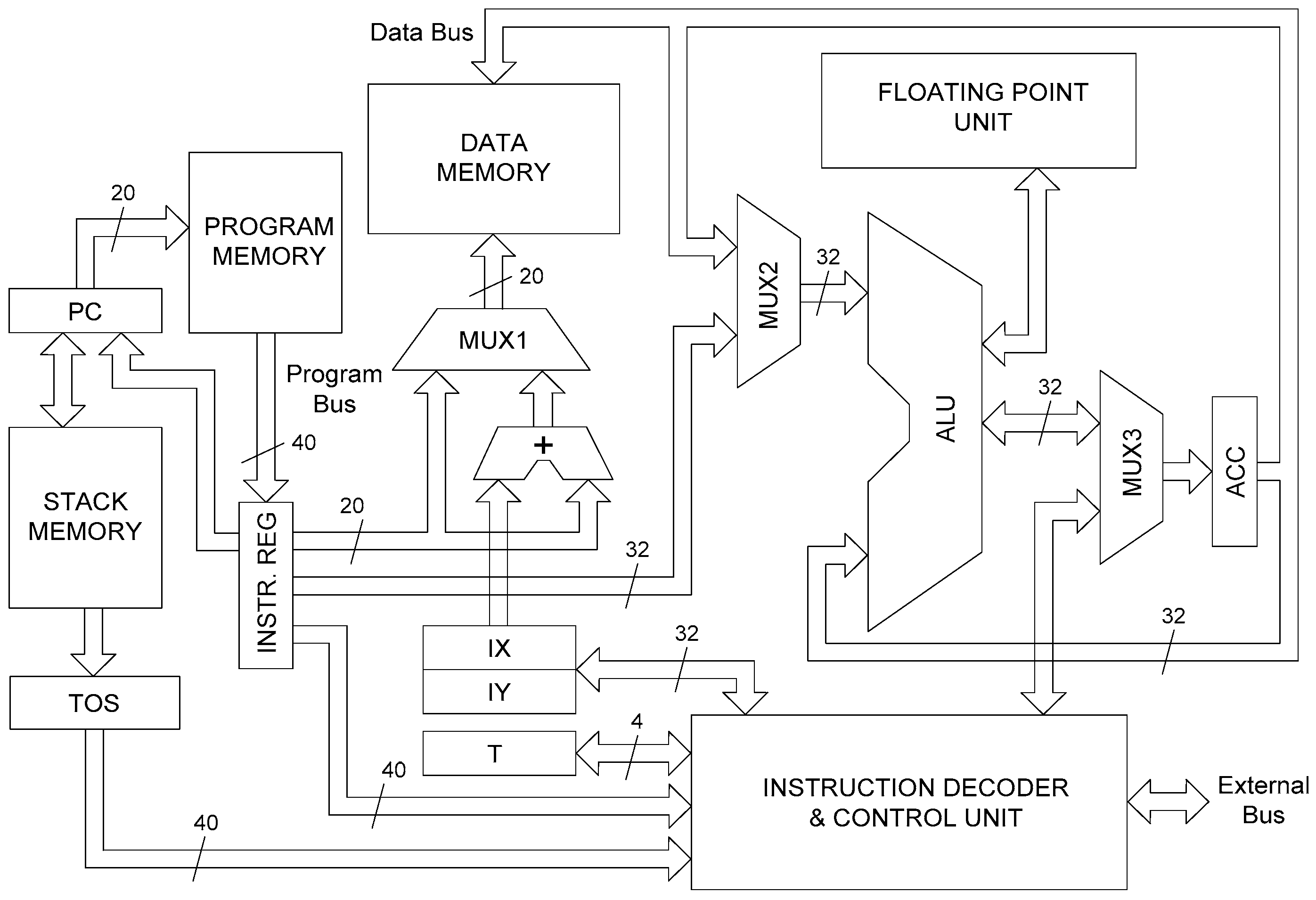

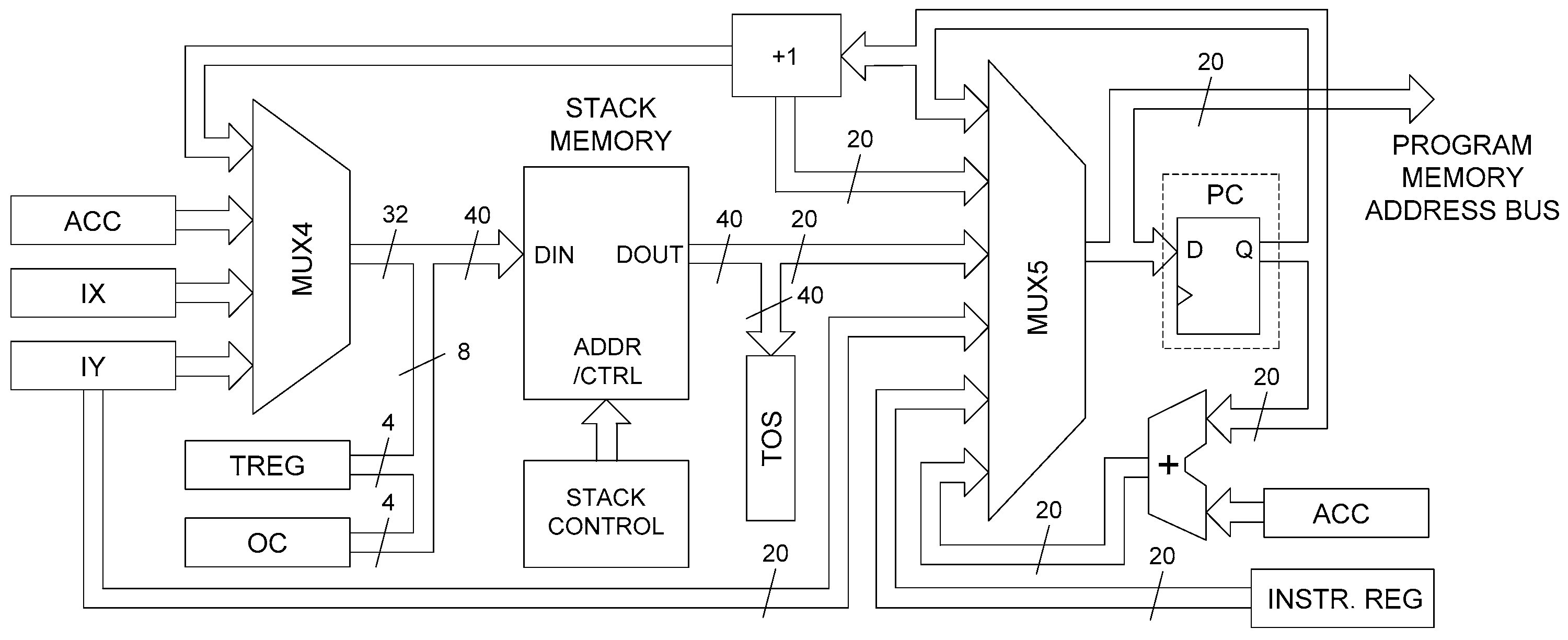

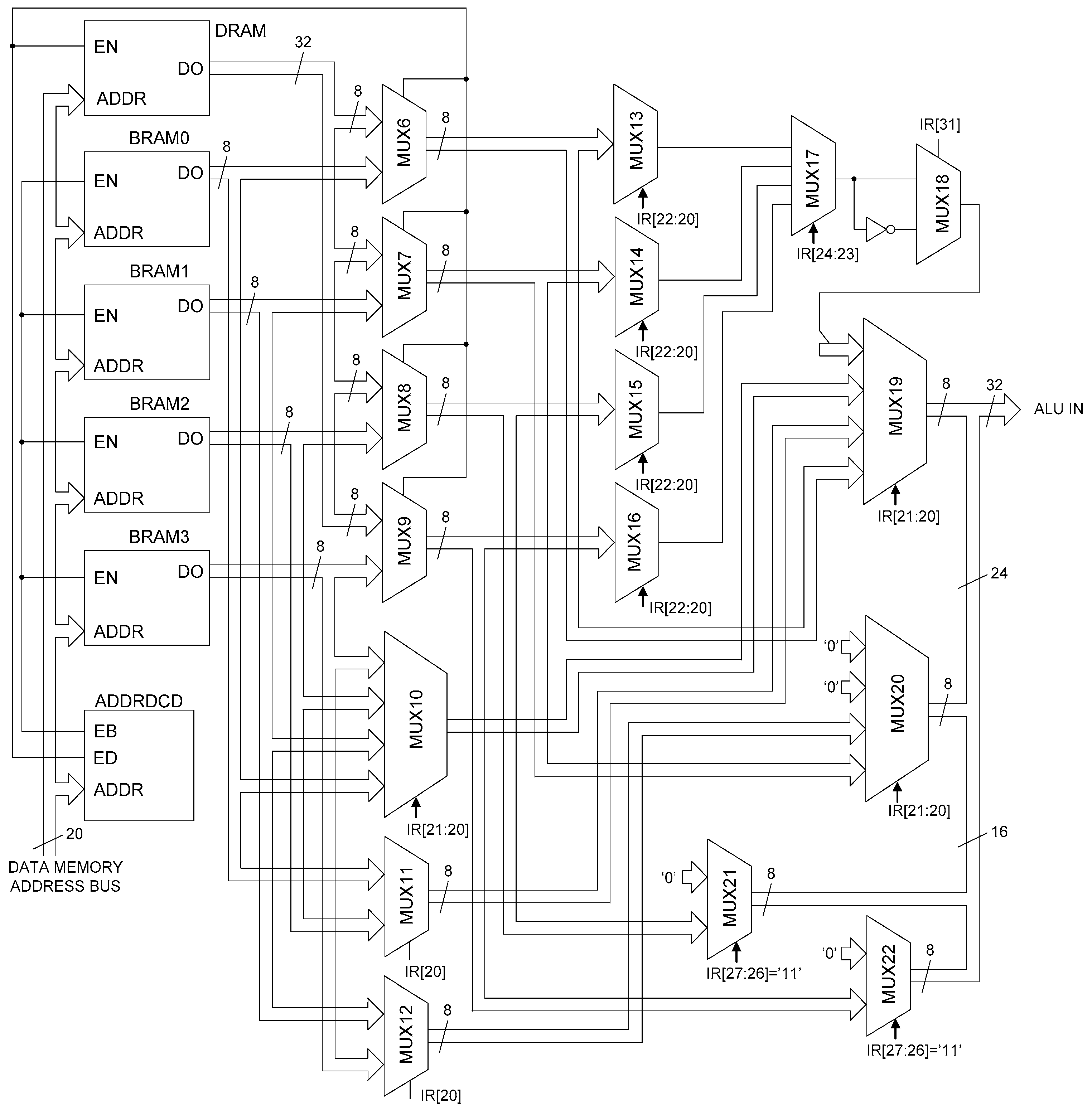

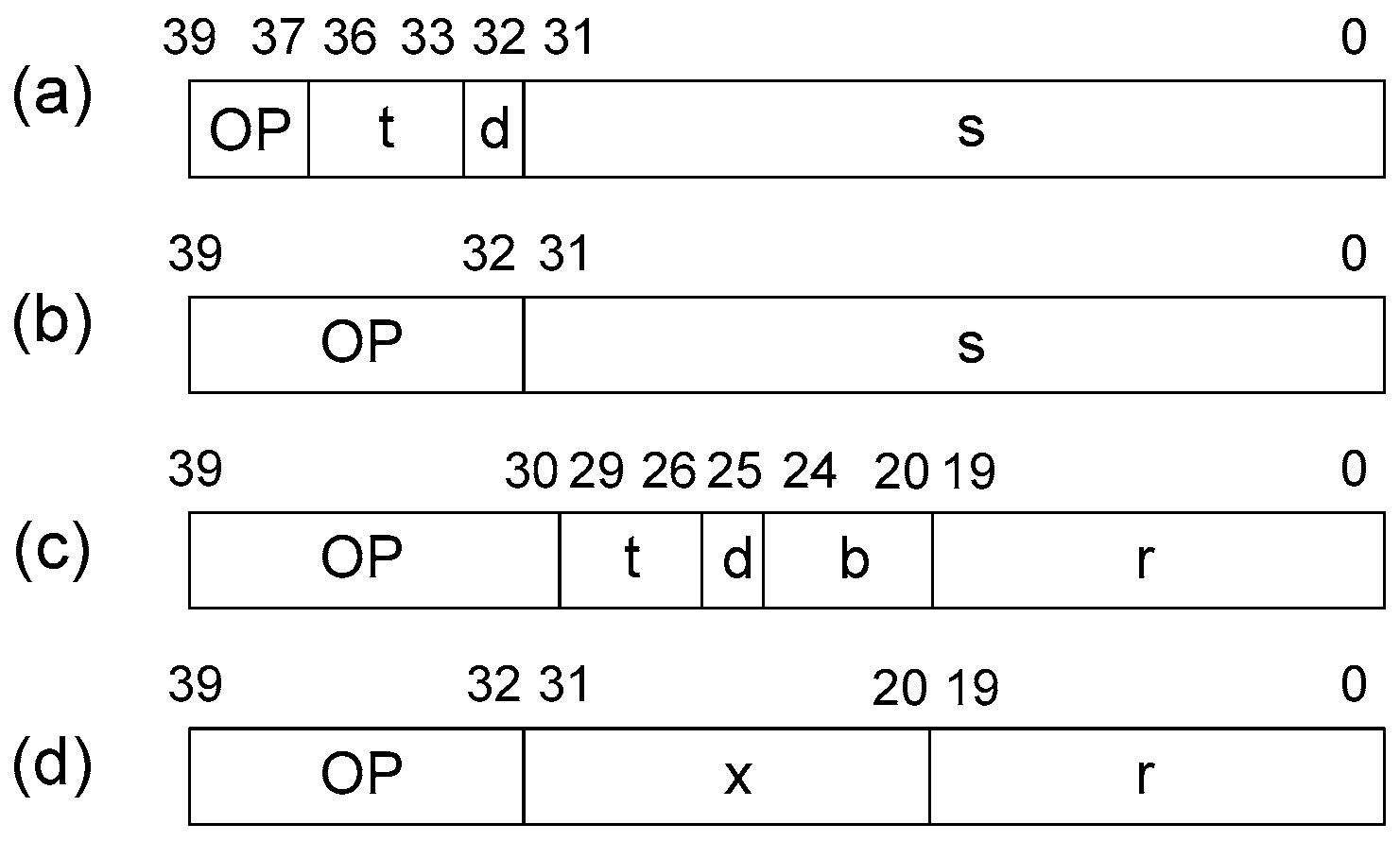

2. Architecture

3. Instruction Set

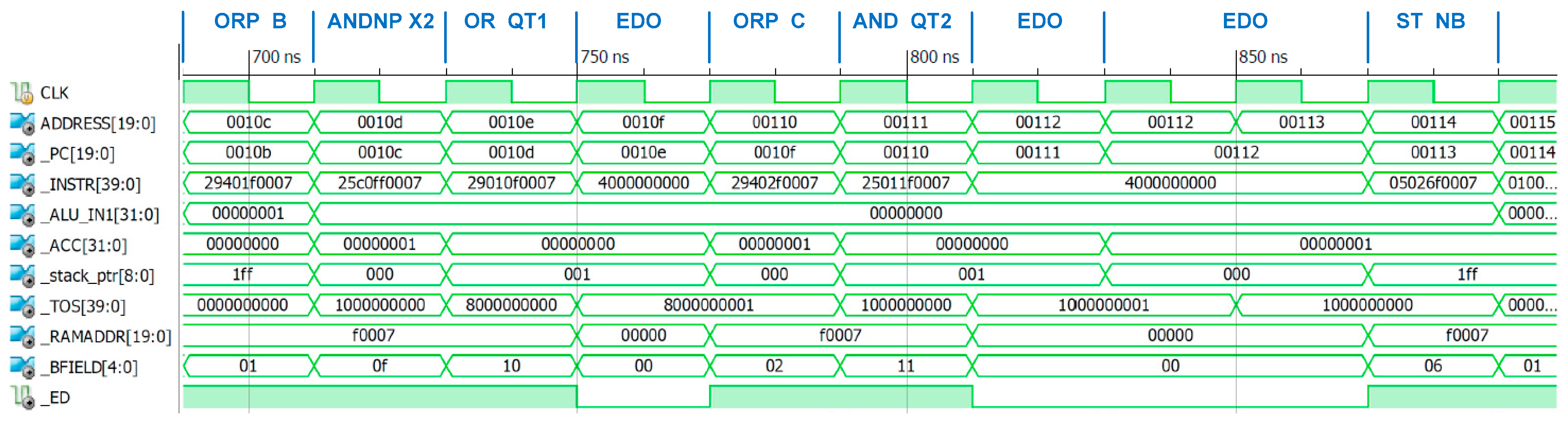

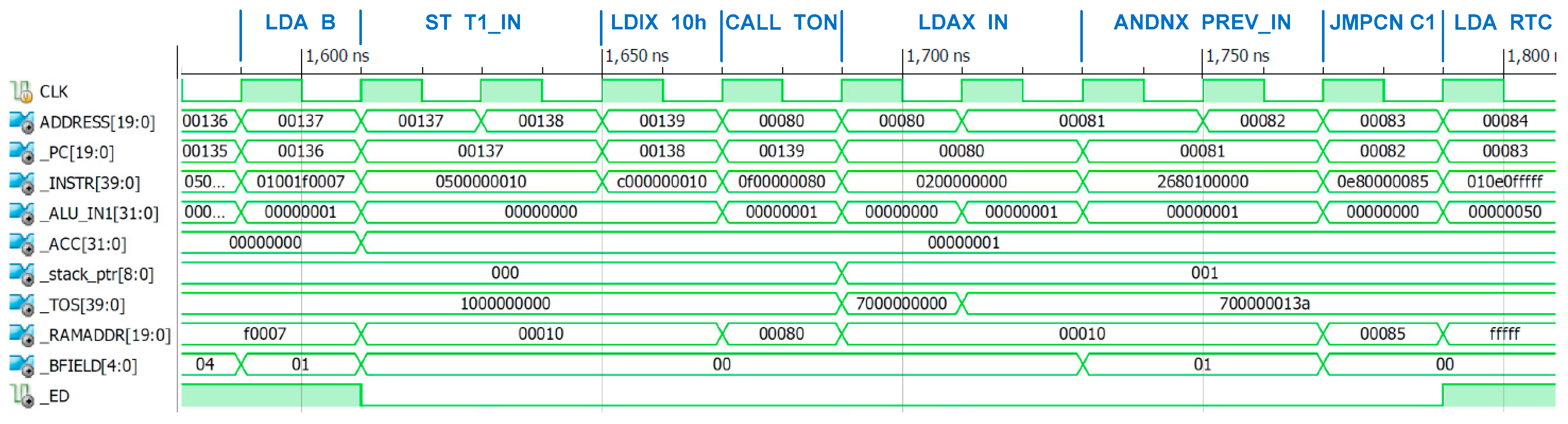

4. Implementation

5. Performance Evaluation

6. Conclusions

Funding

Data Availability Statement

Conflicts of Interest

Appendix A

| Mnemonic, Operand | IEC 61131-3 Counterpart | Description |

| LDIX s | IX<-s | |

| LDAL s.t.d | LD | ACC<-s, if d=1 then T<-t |

| LDA r.b.t.d | LD | ACC<-(r.b), if d=1 then T<-t |

| LDAN r.b.t.d | LDN | ACC<-NOT (r.b), if d=1 then T<-t |

| LDAX r.b.t.d | ACC<-(IX+r.b), if d=1 then T<-t | |

| LDANX r.b.t.d | ACC<-NOT (IX+r.b), if d=1 then T<-t | |

| LDAIO r | EXTERNAL_ADDR_BUS<-r, ACC<-EXTERNAL_DATA_BUS | |

| ST r.b | ST | (r.b)<-ACC |

| STN r.b | STN | (r.b.t)<-NOT ACC |

| STX r.b | (IX+r.b)<-ACC | |

| STNX r.b | (IX+r.b)<-NOT ACC | |

| STIO r | EXTERNAL_ADDR_BUS<-r, EXTERNAL_DATA_BUS<-ACC | |

| CST r.b | (r.b)<-CAR, CAR<-0 | |

| CSTN r.b | (r.b)<-NOT CAR, CAR<-0 | |

| CSTX r.b | (IX+r.b)<-CAR, CAR<-0 | |

| CSTNX r.b | (IX+r.b)<-NOT CAR, CAR<-0 | |

| S r.b | S | if ACC=1 then (r.b)<-1 |

| SX r.b | if ACC=1 then (IX+r.b)<-1 | |

| R r.b | R | if ACC=1 then (r.b)<-0 |

| RX r.b | if ACC=1 then (IX+r.b)<-0 | |

| JMP r | JMP | PC<-r |

| JMPC r | JMPC | if ACC=1 then PC<-r |

| JMPCN r | JMPCN | if ACC=0 then PC<-r |

| JMP IY | PC<-IY | |

| JMPC IY | if ACC=1 then PC<-IY | |

| JMPCN IY | if ACC=0 then PC<-r | |

| CALL r | CAL | TOS<-PC+1, PC<-r |

| CALLC r | CALC | if ACC=1 then TOS<-PC+1, PC<-r |

| CALLCN r | CALCN | if ACC=0 then TOS<-PC+1, PC<-r |

| CALLAA r | TOS<-PC+1, PC<-r | |

| RET | RET | PC<-TOS |

| RETC | RETC | if ACC=1 then PC<-TOS |

| RETCN | RETCN | if ACC=0 then PC<-TOS |

| RETLA s | PC<-TOS, ACC<-s | |

| PUSHA | TOS<-ACC | |

| PUSHX | TOS<-IX | |

| POPA | ACC<-TOS | |

| POPX | IX<-TOS | |

| AND s | AND | ACC<-ACC AND s |

| AND r.b.t.d | AND | ACC<-ACC AND (r.b), if d=1 then T<-t |

| ANDX r.b.t.d | AND | ACC<-ACC AND (IX+r.b), if d=1 then T<-t |

| ANDN r.b.t.d | ANDN | ACC<-ACC AND NOT (r.b), if d=1 then T<-t |

| ANDNX r.b.t.d | ACC<-ACC AND NOT (IX+r.b), if d=1 then T<-t | |

| ANDP r.b.t.d | AND( | TOS<-{ACC,”AND”}, ACC<-(r.b), if d=1 then T<-t |

| ANDPX r.b.t.d | TOS<-{ACC,”AND”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| ANDNP r.b.t.d | ANDN( | TOS<-{ACC,”AND NOT”}, ACC<-(r.b), if d=1 then T<-t |

| ANDNPX r.b.t.d | TOS<-{ACC,”AND NOT”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| CAND r.b | ACC<-ACC AND (r.b), CAR<-CAR OR ACC | |

| CANDX r.b | ACC<-ACC AND (IX+r.b), CAR<-CAR OR ACC | |

| OR s | OR | ACC<-OR AND s |

| OR r.b.t.d | OR | ACC<-ACC OR (r.b), if d=1 then T<-t |

| ORX r.b.t.d | OR | ACC<-ACC OR (IX+r.b), if d=1 then T<-t |

| ORN r.b.t.d | ORN | ACC<-ACC OR NOT (r.b), if d=1 then T<-t |

| ORNX r.b.t.d | ACC<-ACC OR NOT (IX+r.b), if d=1 then T<-t | |

| ORP r.b.t.d | OR( | TOS<-{ACC,”OR”}, ACC<-(r.b), if d=1 then T<-t |

| ORPX r.b.t.d | TOS<-{ACC,”OR”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| ORNP r.b.t.d | ORN( | TOS<-{ACC,”OR NOT”}, ACC<-(r.b), if d=1 then T<-t |

| ORNPX r.b.t.d | TOS<-{ACC,”OR NOT”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| XOR s | XOR | ACC<-ACC XOR s |

| XOR r.b.t.d | XOR | ACC<-ACC XOR (r.b), if d=1 then T<-t |

| XORX r.b.t.d | ACC<-ACC XOR (IX+r.b), if d=1 then T<-t | |

| XORN r.b.t.d | XORN | ACC<-ACC XOR NOT (r.b), if d=1 then T<-t |

| XORNX r.b.t.d | ACC<-ACC XOR NOT (IX+r.b), if d=1 then T<-t | |

| XORP r.b.t.d | XOR( | TOS<-{ACC,”XOR”}, ACC<-(r.b), if d=1 then T<-t |

| XORPX r.b.t.d | TOS<-{ACC,”XOR”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| XORNP r.b.t.d | XORN( | TOS<-{ACC,”XOR NOT”}, ACC<-(r.b), if d=1 then T<-t |

| XORNPX r.b.t.d | TOS<-{ACC,”XOR NOT”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| ADD s | ADD | ACC<-ACC + s |

| ADD r.b.t.d | ADD | ACC<-ACC + (r.b), if d=1 then T<-t |

| ADDX r.b.t.d | ACC<-ACC + (IX+r.b), if d=1 then T<-t | |

| ADDP r.b.t.d | ADD( | TOS<-{ACC,”+”}, ACC<-(r.b), if d=1 then T<-t |

| ADDPX r.b.t.d | TOS<-{ACC,”+”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| SUB s | SUB | ACC<-ACC—s |

| SUB r.b.t.d | SUB | ACC<-ACC—(r.b), if d=1 then T<-t |

| SUBX r.b.t.d | SUB | ACC<-ACC—(IX+r.b), if d=1 then T<-t |

| SUBP r.b.t.d | SUB( | TOS<-{ACC,”-”}, ACC<-(r.b), if d=1 then T<-t |

| SUBPX r.b.t.d | TOS<-{ACC,”-”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| MUL s | MUL | ACC<-ACC * s |

| MUL r.b.t.d | MUL | ACC<-ACC * (r.b), if d=1 then T<-t |

| MULX r.b.t.d | ACC<-ACC * (IX+r.b), if d=1 then T<-t | |

| MULP r.b.t.d | MUL( | TOS<-{ACC,”*”}, ACC<-(r.b), if d=1 then T<-t |

| MULPX r.b.t.d | TOS<-{ACC,”*”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| DIV s | DIV | ACC<-ACC/s |

| DIV r.b.t.d | DIV | ACC<-ACC/(r.b), if d=1 then T<-t |

| DIVX r.b.t.d | ACC<-ACC/(IX+r.b), if d=1 then T<-t | |

| DIVP r.b.t.d | DIV( | TOS<-{ACC,”/”}, ACC<-(r.b), if d=1 then T<-t |

| DIVPX r.b.t.d | TOS<-{ACC,”/”}, ACC<-(IX+r.b), if d=1 then T<-t | |

| GT s | GT | if ACC > s then ACC<-1 else ACC<-0 |

| GT r.b | GT | if ACC > (r.b) then ACC<-1 else ACC<-0 |

| GTX r.b | GT | if ACC > (IX+r.b) then ACC<-1 else ACC<-0 |

| GTE s | GTE | if ACC >= s then ACC<-1 else ACC<-0 |

| GTE r.b | GTE | if ACC >= (r.b) then ACC<-1 else ACC<-0 |

| GTEX r.b | if ACC >= (IX+r.b) then ACC<-1 else ACC<-0 | |

| EQ s | EQ | if ACC = s then ACC<-1 else ACC<-0 |

| EQ r.b | EQ | if ACC = (r.b) then ACC<-1 else ACC<-0 |

| EQX r.b | if ACC = (IX+r.b) then ACC<-1 else ACC<-0 | |

| NE s | NE | if ACC <> s then ACC<-1 else ACC<-0 |

| NE r.b | NE | if ACC <> (r.b) then ACC<-1 else ACC<-0 |

| NEX r.b | if ACC <> (IX+r.b) then ACC<-1 else ACC<-0 | |

| LT s | LT | if ACC < s then ACC<-1 else ACC<-0 |

| LT r.b | LT | if ACC < (r.b) then ACC<-1 else ACC<-0 |

| LTX r.b | if ACC < (IX+r.b) then ACC<-1 else ACC<-0 | |

| LTE s | LTE | if ACC <= s then ACC<-1 else ACC<-0 |

| LTE r.b | LTE | if ACC <= (r.b) then ACC<-1 else ACC<-0 |

| LTEX r.b | if ACC <= (IX+r.b) then ACC<-1 else ACC<-0 | |

| EDO | ) | {TMPA,OP}<-TOS, ACC<-TMPA OP A |

| SHLA | ACC<- SHIFT_LEFT ACC | |

| SHL r.b | ACC<- SHIFT_LEFT (r.b) | |

| SHLX r.b | ACC<- SHIFT_LEFT (IX+r.b) | |

| SHRA | ACC<- SHIFT_RIGHT ACC | |

| SHR r.b | ACC<- SHIFT_RIGHT (r.b) | |

| SHRX r.b | ACC<- SHIFT_RIGHT (IX+r.b) | |

| ROLA | ACC<- ROTATE_LEFT ACC | |

| ROL r.b | ACC<- ROTATE_LEFT (r.b) | |

| ROLX r.b | ACC<- ROTATE_LEFT (IX+r.b) | |

| RORA | ACC<- ROTATE_RIGHT ACC | |

| ROR r.b | ACC<- ROTATE_RIGHT (r.b) | |

| RORX r.b | ACC<- ROTATE_RIGHT (IX+r.b) |

References

- IEC 61131-3; International Standard Edition 3.0. International Electrotechnical Commission: Geneva, Switzerland, 2013.

- John, K.H.; Tiegelkamp, M. IEC 61131-3: Programming Industrial Automation Systems; Springer: Berlin/Heidelberg, Germany, 2010. [Google Scholar]

- Rho, G.S.; Koo, K.H.; Chang, N.; Park, J.; Kim, J.G.; Kwon, W.H. Implementation of a RISC microprocessor for programmable logic controllers. Microprocess. Microsyst. 1995, 19, 599–608. [Google Scholar] [CrossRef]

- Snaider Carrillo, L.; Agenor Polo, Z.; Mario Esmeral, P. Design and Implementation of an Embedded Microprocessor Compatible with IL Language in Accordance to the Norm IEC 61131-3. In Proceedings of the International Conference on Reconfigurable Computing and FPGAs (ReConFig), Puebla, Mexico, 28–30 September 2005. [Google Scholar]

- Xu, M.; Ran, F.; Chen, Z.; Kang, S.; Li, R. IP Core Design of PLC Microprocessor with Boolean Module. In Proceedings of the International Symposium on High Density Packaging and Microsystem Integration (HDP), Shanghai, China, 27–29 June 2005. [Google Scholar]

- Zeng, S.; Yang, Z. A high performance architecture design of PLC dedicated processor. In Proceedings of the International Conference on Advanced Computer Theory and Engineering (ICACTE), Chengdu, China, 20–22 August 2010. [Google Scholar]

- Chmiel, M.; Mocha, J.; Hrynkiewicz, E.; Milik, A. Central Processing Units for PLC implementation in Virtex-4 FPGA. IFAC Proc. Vol. 2011, 44, 7860–7865. [Google Scholar] [CrossRef]

- Chodorowski, P.; Chmiel, M. IEC 61131-3 Compliant PLC Structure Based on FPGA Multi-Core Solution. In Proceedings of the International Conference on Signals and Electronic Systems (ICSES), Krakow, Poland, 5–7 September 2016. [Google Scholar]

- Chmiel, M.; Kloska, W.; Polok, D.; Mocha, J. FPGA-based two-processor CPU for PLC. In Proceedings of the International Conference on Signals and Electronic Systems (ICSES), Krakow, Poland, 5–7 September 2016. [Google Scholar]

- Shedge, D.K.; Chogale, S.; Pachpande, S. Instruction List Processor replacing general purpose processor in PLC for Industrial Application. Int. J. Sci. Eng. Res. 2017, 8, 663–666. [Google Scholar]

- Shedge, S.; Tade, S.L. Implementation of IEC 61131-3 Standard Compatible Instruction List Processor on FPGA Platform. Int. J. Adv. Res. Innov. Ideas Educ. 2018, 4, 1220–1227. [Google Scholar]

- Shedge, S.; Tade, S.L. Design of Instruction List Processor for Industrial Applications. In Proceedings of the Fourth International Conference on Computing Communication Control and Automation (ICCUBEA), Pune, India, 16–18 August 2018. [Google Scholar]

- Eassa, H.; Adly, I.; Issa, H.H. RISC-V based implementation of Programmable Logic Controller on FPGA for Industry 4.0. In Proceedings of the International Conference on Microelectronics (ICM), Cairo, Egypt, 15–18 December 2019. [Google Scholar]

- Rudrawar, S.K.; Sakhare, D. High Performance Instruction List Processor on FPGA Platform. In Proceedings of the Third International Conference on Computing Methodologies and Communication (ICCM), Erode, India, 27–29 March 2019; pp. 145–152. [Google Scholar]

- Hajduk, Z.; Trybus, B.; Sadolewski, J. Architecture of FPGA Embedded Multiprocessor Programmable Controller. IEEE Trans. Ind. Electron. 2015, 62, 2952–2961. [Google Scholar] [CrossRef]

- Rzońca, D.; Sadolewski, J.; Stec, A.; Świder, Z.; Trybus, B.; Trybus, L. CPDev engineering environment for control programming. In Trends in Advanced Intelligent Control, Optimization and Automation, KKA 2017, Advances in Intelligent Systems and Computing; Mitkowski, W., Kacprzyk, J., Oprzędkiewicz, K., Skruch, P., Eds.; Springer: Cham, Switzerland, 2017; Volume 577. [Google Scholar]

- Hajduk, Z. An FPGA embedded microcontroller. Microprocess. Microsyst. 2014, 38, 1–8. [Google Scholar] [CrossRef]

- Kluska, J. Analytical method in fuzzy modeling and control. In Studies in Fuzziness and Soft Computing; Springer: New York, NY, USA, 2009; Volume 241. [Google Scholar]

| Version 1: | Version 2: | Version 3: |

|---|---|---|

| LDA A | LDA A | LDA A |

| AND X1 | AND X1 | CAND X1 |

| ST TMP1 | ORP B | LD X2 |

| LDA X2 | ANDNP X2 | OR QT1 |

| OR QT1 | OR QT1 | XOR TRUE |

| XOR TRUE | EDO | CAND B |

| AND B | ORP C | LDA C |

| OR TMP1 | AND QT2 | CAND QT2 |

| ST TMP1 | EDO | CST NB |

| LDA C | EDO | |

| AND QT2 | ST NB | |

| OR TMP1 | ||

| ST NB |

| FPGA Chip | LUTs | FFs | Max Clock Freq. [MHz] |

|---|---|---|---|

| Spartan-6 XC6SLX100 | 3744 (5.9%) | 2292 (1.8%) | 64.5 |

| Artix-7 XC7A100T | 3675 (5.7%) | 2276 (1.8%) | 74.1 |

| Kintex-7 XC7K325T | 3705 (1.8%) | 2276 (0.6%) | 102.5 |

| Test Algorithm | Number of Clock Cycles | Time [μs] Spartan-6 @64.286 MHz | Time [μs] Artix-7 @74.099 MHz | Time [μs] Kintex-7 @102.500 MHz |

|---|---|---|---|---|

| LC1 | 218 | 3.39 | 2.94 | 2.13 |

| LC2 | 143 | 2.22 | 1.93 | 1.40 |

| LC3 | 138 | 2.15 | 1.86 | 1.35 |

| LC4 | 119 | 1.85 | 1.61 | 1.16 |

| LC5 | 103 | 1.60 | 1.39 | 1.00 |

| LC6 | 115 | 1.79 | 1.55 | 1.12 |

| LC7 | 70 | 1.09 | 0.94 | 0.68 |

| P1TS | 1779 | 27.67 | 24.01 | 17.36 |

| Test Algorithm | Beckhoff CP6607 @533 MHz (TwinCAT 2) | Beckhoff CX5140 @1.91 GHz (TwinCAT 3) | Raspberry PI 4 @1.8 GHz (CODESYS) | |||

|---|---|---|---|---|---|---|

| Time [μs] | EC | Time [μs] | EC | Time [μs] | EC | |

| LC4 | 1.45 | 773 | 0.31/0.27 | 592/516 | 0.54/0.12 | 972/216 |

| LC6 | 1.32 | 704 | 0.29/0.25 | 554/477 | 0.49/0.10 | 882/180 |

| P1TS | 206.7 | 110,171 | 1.82 | 3476 | 1.06 | 1908 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hajduk, Z. IEC61131-3 Instruction List Language Processor for FPGAs. Electronics 2023, 12, 4052. https://doi.org/10.3390/electronics12194052

Hajduk Z. IEC61131-3 Instruction List Language Processor for FPGAs. Electronics. 2023; 12(19):4052. https://doi.org/10.3390/electronics12194052

Chicago/Turabian StyleHajduk, Zbigniew. 2023. "IEC61131-3 Instruction List Language Processor for FPGAs" Electronics 12, no. 19: 4052. https://doi.org/10.3390/electronics12194052

APA StyleHajduk, Z. (2023). IEC61131-3 Instruction List Language Processor for FPGAs. Electronics, 12(19), 4052. https://doi.org/10.3390/electronics12194052