Effect of Non-Ideal Cross-Sectional Shape on the Performance of Nanosheet-Based FETs

Abstract

:1. Introduction

2. Device Structure and Simulation Methodology

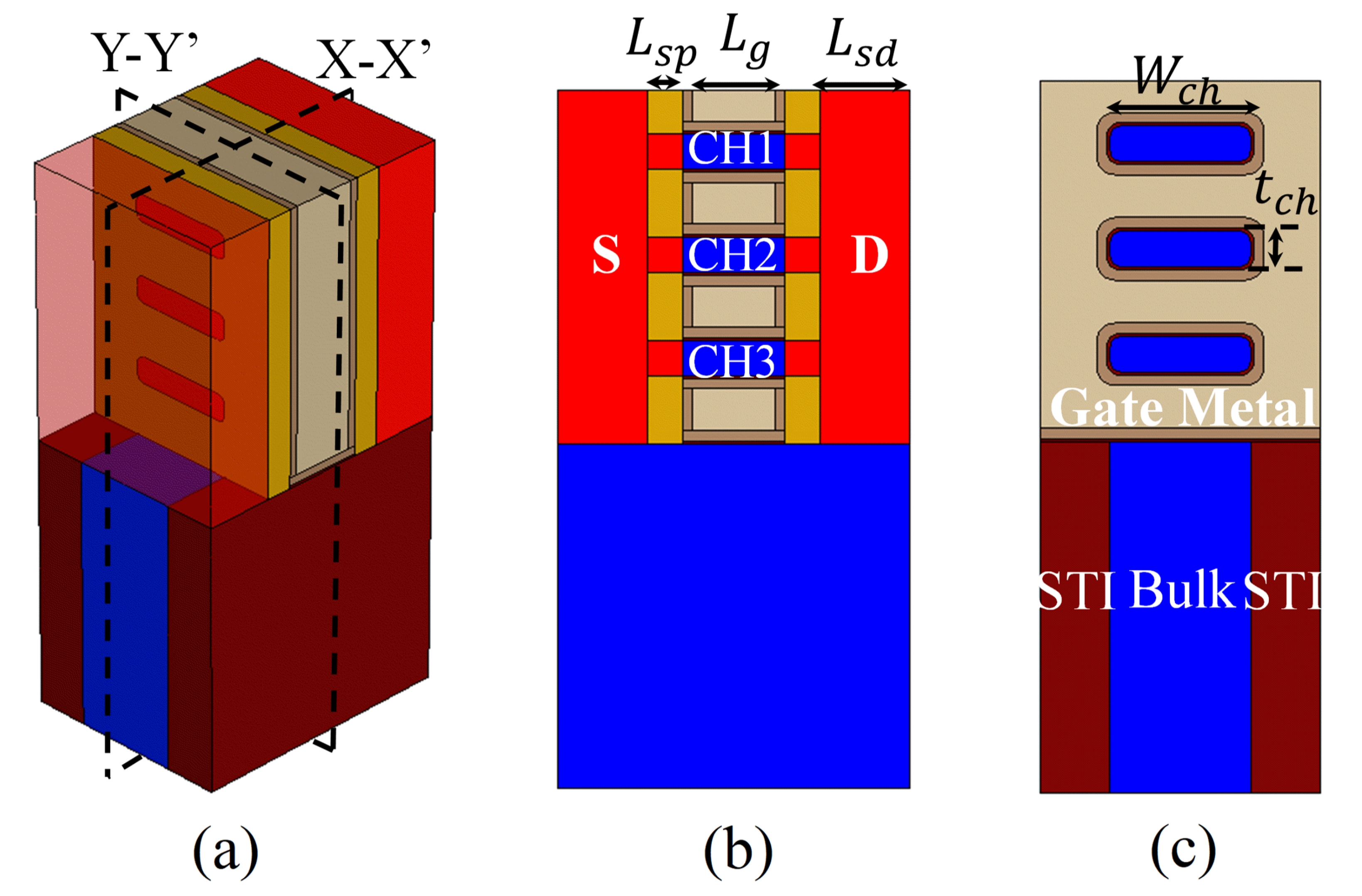

2.1. Device Structure

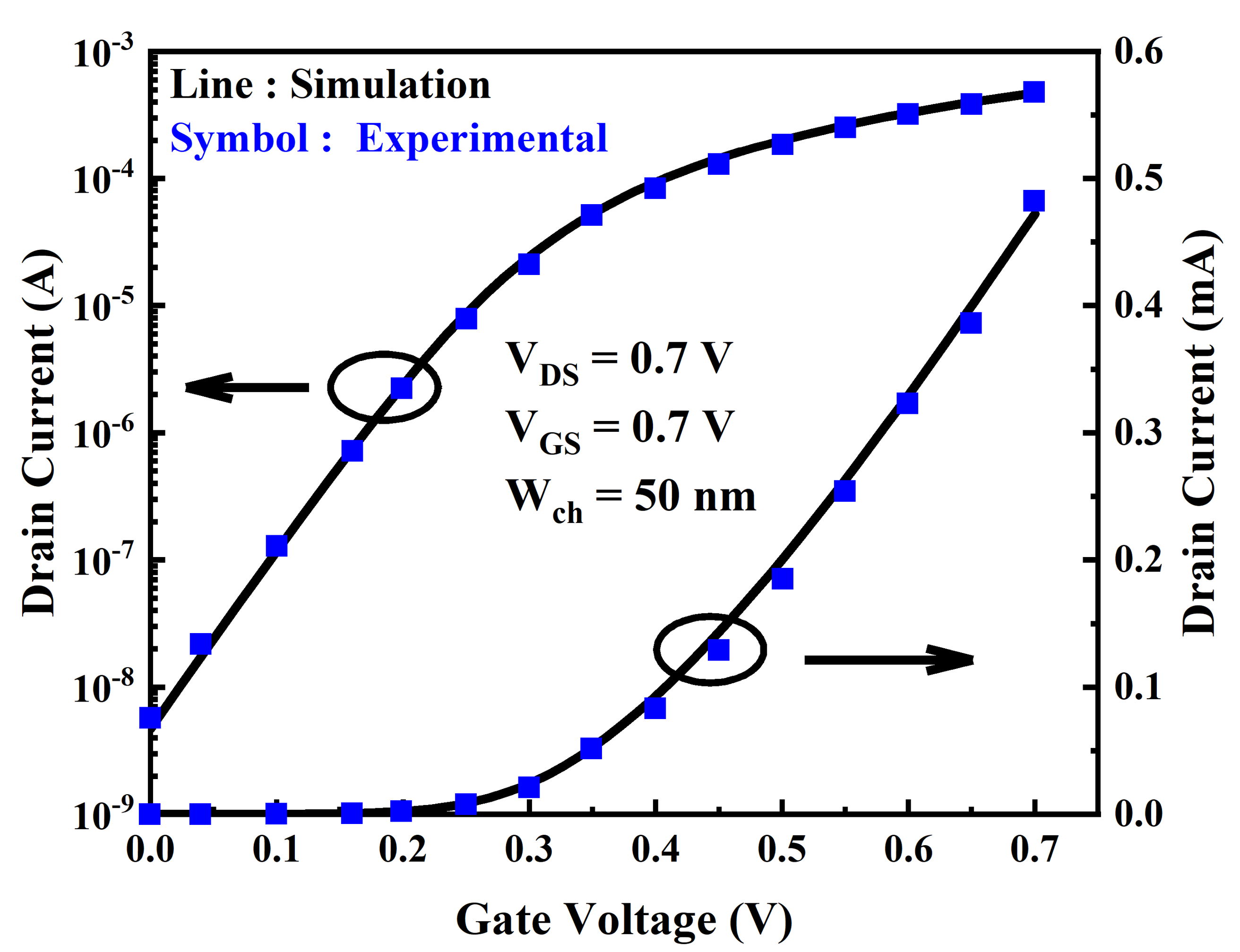

2.2. Simulation Settings

3. Results and Discussion

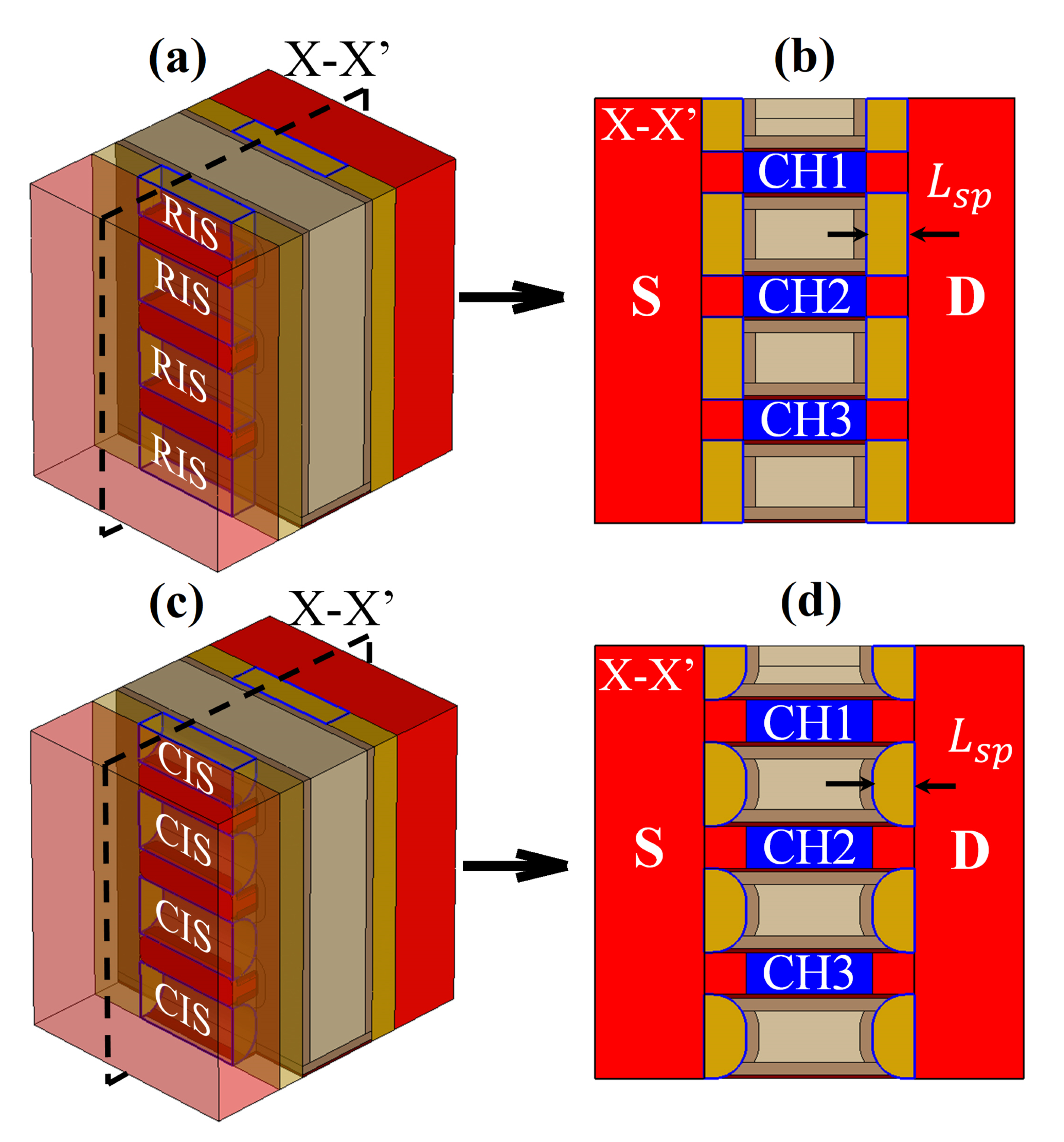

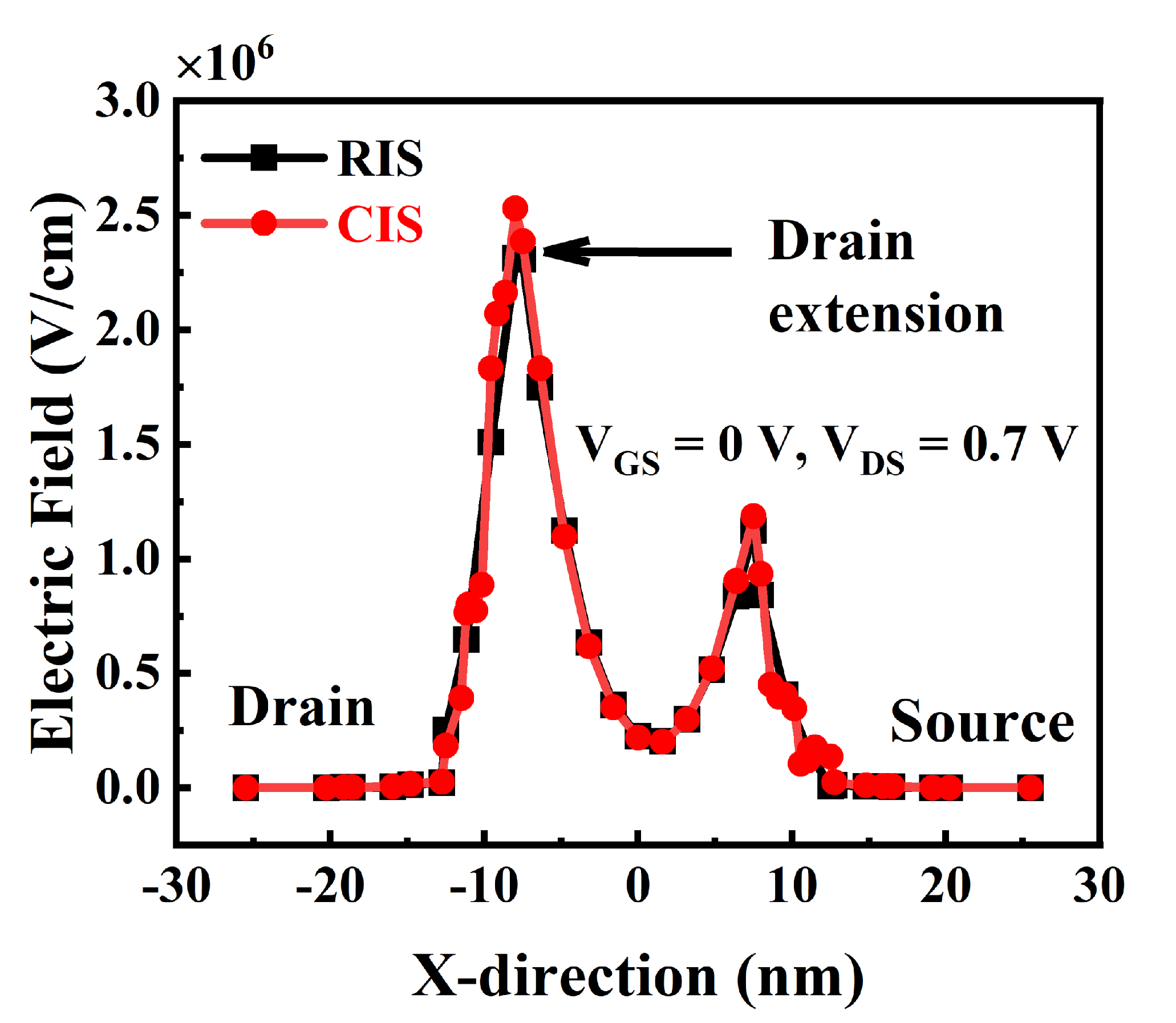

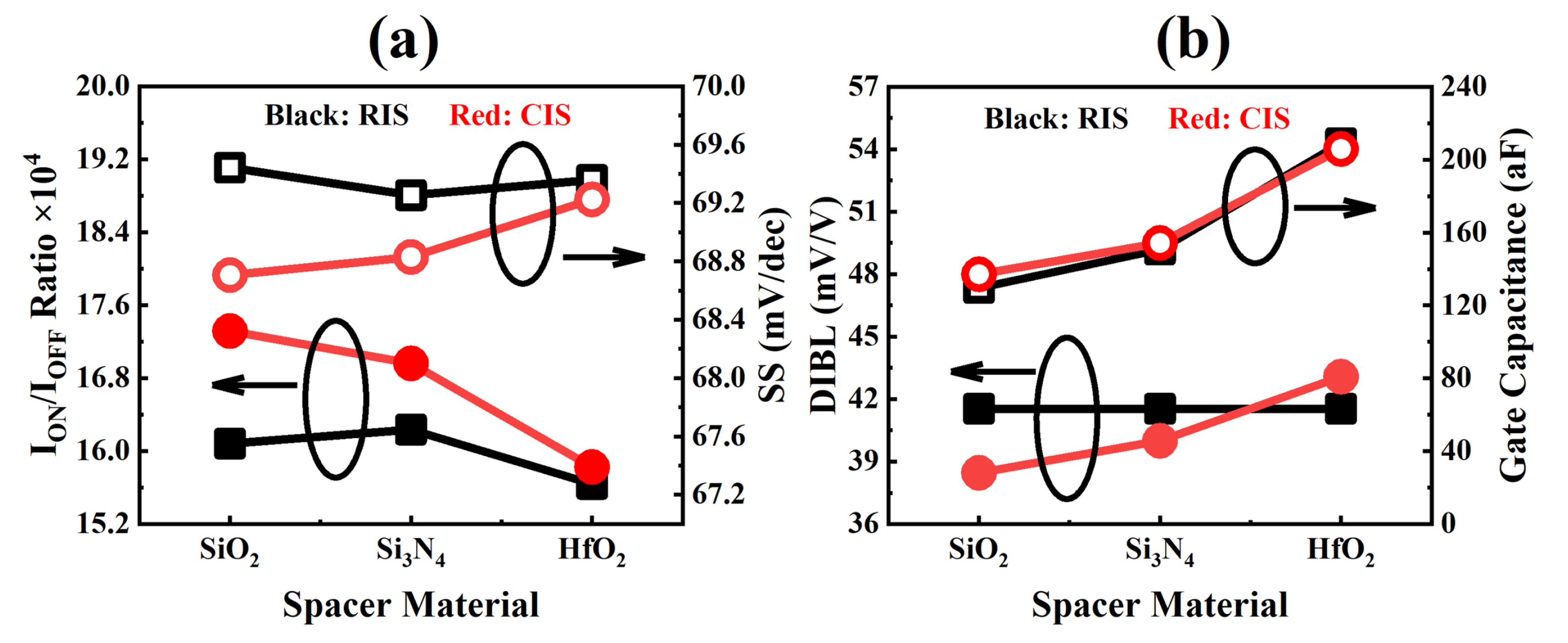

3.1. Inner Spacer

3.2. Stacked NS Channel

3.3. Fin-Shaped IB Channel

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lee, K.S.; Park, J.Y. Inner Spacer Engineering to Improve Mechanical Stability in Channel-Release Process of Nanosheet FETs. Electronics 2021, 10, 1395. [Google Scholar] [CrossRef]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T230–T231. [Google Scholar] [CrossRef]

- Sun, Y.; Li, X.; Liu, Z.; Liu, Y.; Li, X.; Shi, Y. Vertically Stacked Nanosheets Tree-Type Reconfigurable Transistor with Improved ON-Current. IEEE Trans. Electron Devices 2022, 69, 370–374. [Google Scholar] [CrossRef]

- Wang, D.; Sun, X.; Liu, T.; Chen, K.; Yang, J.; Wu, C.; Xu, M.; Zhang, W.D. Investigation of Source/Drain Recess Engineering and Its Impacts on FinFET and GAA Nanosheet FET at 5 nm Node. Electronics 2023, 12, 770. [Google Scholar] [CrossRef]

- Yoon, J.S.; Jeong, J.; Lee, S.; Baek, R.H. Optimization of nanosheet number and width of multi-stacked nanosheet FETs for sub-7-nm node system on chip applications. Jpn. J. Appl. Phys. 2019, 58, SBBA12. [Google Scholar] [CrossRef]

- Kim, S.; Lee, K.; Kim, S.; Kim, M.; Lee, J.H.; Kim, S.; Park, B.G. Investigation of Device Performance for Fin Angle Optimization in FinFET and Gate-All-Around FETs for 3 nm-Node and Beyond. IEEE Trans. Electron Devices 2022, 69, 2088–2093. [Google Scholar] [CrossRef]

- Rathore, S.; Jaisawal, R.K.; Kondekar, P.N.; Bagga, N. Design Optimization of Three-Stacked Nanosheet FET from Self-Heating Effects Perspective. IEEE Trans. Device Mater. Reliab. 2022, 22, 396–402. [Google Scholar] [CrossRef]

- Liu, R.; Li, X.; Sun, Y.; Li, F.; Shi, Y. Thermal Coupling Among Channels and Its DC Modeling in Sub-7-nm Vertically Stacked Nanosheet Gate-All-Around Transistor. IEEE Trans. Electron Devices 2021, 68, 6563–6570. [Google Scholar] [CrossRef]

- Venkateswarlu, S.; Nayak, K. Hetero-Interfacial Thermal Resistance Effects on Device Performance of Stacked Gate-All-Around Nanosheet FET. IEEE Trans. Electron Devices 2020, 67, 4493–4499. [Google Scholar] [CrossRef]

- Yoo, S.; Kim, S. Leakage Optimization of the Buried Oxide Substrate of Nanosheet Field-Effect Transistors. IEEE Trans. Electron Devices 2022, 69, 4109–4114. [Google Scholar] [CrossRef]

- Lee, K.S.; Shin, W.C.; Yeon, J.W.; Park, J.Y. Impact of device-to-device interference in nanosheet field-effect transistors. Microelectron. Reliab. 2023, 145, 114995. [Google Scholar] [CrossRef]

- Santos, A.; Deen, M.J.; Marsal, L.F. Low-cost fabrication technologies for nanostructures: State-of-the-art and potential. Nanotechnology 2015, 26, 042001. [Google Scholar] [CrossRef] [PubMed]

- Mukesh, S.; Zhang, J. A Review of the Gate-All-Around Nanosheet FET Process Opportunities. Electronics 2022, 11, 3589. [Google Scholar] [CrossRef]

- Loubet, N.; Kal, S.; Alix, C.; Pancharatnam, S.; Zhou, H.; Durfee, C.; Belyansky, M.; Haller, N.; Watanabe, K.; Devarajan, T.; et al. A Novel Dry Selective Etch of SiGe for the Enablement of High Performance Logic Stacked Gate-All-Around NanoSheet Devices. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.4.1–11.4.4. [Google Scholar] [CrossRef]

- Durfee, C.; Kal, S.; Pancharatnam, S.; Bhuiyan, M.; Otto, I., IV; Flaugh, M.; Smith, J.; Chanemougame, D.; Alix, C.; Zhou, H.; et al. Highly Selective SiGe Dry Etch Process for the Enablement of Stacked Nanosheet Gate-All-Around Transistors. ECS Meet. Abstr. 2021, MA2021-02, 943. [Google Scholar] [CrossRef]

- Zhao, Y.; Iwase, T.; Satake, M.; Hamamura, H. Formation Mechanism of a Rounded SiGe-Etch-Front in an Isotropic Dry SiGe Etch Process for Gate-All-Around (GAA)-FETs. In Proceedings of the 2021 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Chengdu, China, 8–11 April 2021; pp. 1–3. [Google Scholar] [CrossRef]

- Zhao, Y.; Iwase, T.; Satake, M.; Hamamura, H. Formation Mechanism of Rounded SiGe-Etch Front in Isotropic SiGe Plasma Etching for Gate-All-Around FETs. IEEE J. Electron Devices Soc. 2021, 9, 1112–1116. [Google Scholar] [CrossRef]

- Schmidt, D.; Cepler, A.; Durfee, C.; Pancharatnam, S.; Frougier, J.; Breton, M.; Greene, A.; Klare, M.; Koret, R.; Turovets, I. Development of SiGe Indentation Process Control for Gate-All-Around FET Technology Enablement. IEEE Trans. Semicond. Manuf. 2022, 35, 412–417. [Google Scholar] [CrossRef]

- Liu, R.; Li, X.; Sun, Y.; Shi, Y. A Vertical Combo Spacer to Optimize Electrothermal Characteristics of 7-nm Nanosheet Gate-All-Around Transistor. IEEE Trans. Electron Devices 2020, 67, 2249–2254. [Google Scholar] [CrossRef]

- Ryu, D.; Kim, M.; Kim, S.; Choi, Y.; Yu, J.; Lee, J.H.; Park, B.G. Design and Optimization of Triple-k Spacer Structure in Two-Stack Nanosheet FET from OFF-State Leakage Perspective. IEEE Trans. Electron Devices 2020, 67, 1317–1322. [Google Scholar] [CrossRef]

- Jeong, J.; Yoon, J.S.; Lee, S.; Baek, R.H. Novel Trench Inner-Spacer Scheme to Eliminate Parasitic Bottom Transistors in Silicon Nanosheet FETs. IEEE Trans. Electron Devices 2023, 70, 396–401. [Google Scholar] [CrossRef]

- Yoon, J.S.; Jeong, J.; Lee, S.; Baek, R.H. Punch-Through-Stopper Free Nanosheet FETs with Crescent Inner-Spacer and Isolated Source/Drain. IEEE Access 2019, 7, 38593–38596. [Google Scholar] [CrossRef]

- Lee, S.; Jeong, J.; Yoon, J.S.; Lee, S.; Lee, J.; Lim, J. Sensitivity of Inner Spacer Thickness Variations for Sub-3-nm Node Silicon Nanosheet Field-Effect Transistors. Nanomaterials 2022, 12, 3349. [Google Scholar] [CrossRef]

- Jegadheesan, V.; Sivasankaran, K.; Konar, A. Optimized Substrate for Improved Performance of Stacked Nanosheet Field-Effect Transistor. IEEE Trans. Electron Devices 2020, 67, 4079–4084. [Google Scholar] [CrossRef]

- Jegadheesan, V.; Sivasankaran, K.; Konar, A. Impact of geometrical parameters and substrate on analog/RF performance of stacked nanosheet field effect transistor. Mater. Sci. Semicond. Process. 2019, 93, 188–195. [Google Scholar] [CrossRef]

- Woo, S.; Jeong, H.; Choi, J.; Cho, H.; Kong, J.T.; Kim, S. Machine-Learning-Based Compact Modeling for Sub-3-nm-Node Emerging Transistors. Electronics 2022, 11, 2761. [Google Scholar] [CrossRef]

- Seon, Y.; Chang, J.; Yoo, C.; Jeon, J. Device and Circuit Exploration of Multi-Nanosheet Transistor for Sub-3 nm Technology Node. Electronics 2021, 10, 180. [Google Scholar] [CrossRef]

- Catano, C.; Joy, N.; Talone, C.; Sridhar, S.; Voronin, S.; Biolsi, P.; Ranjan, A. Peculiarities of selective isotropic Si etch to SiGe for nanowire and GAA transistors. In Advanced Etch Technology for Nanopatterning VIII; Wise, R.S., Labelle, C.B., Eds.; SPIE: Bellingham, WA, USA, 2019; Volume 10963, p. 109630E. [Google Scholar] [CrossRef]

- Tsen, C.J.; Chung, C.C.; Liu, C.W. Self-Heating Mitigation of TreeFETs by Interbridges. IEEE Trans. Electron Devices 2022, 69, 4123–4128. [Google Scholar] [CrossRef]

- Li, X.; Zhu, H.; Gan, W.; Huang, W.; Wu, Z. A Three-Dimensional Simulation Study of the Novel Comb-Like-Channel Field-Effect Transistors for the 5-nm Technology Node and Beyond. IEEE Trans. Electron Devices 2022, 69, 4786–4790. [Google Scholar] [CrossRef]

- Tu, C.T.; Hsieh, W.H.; Huang, B.W.; Chen, Y.R.; Liu, Y.C.; Tsai, C.E.; Chueh, S.J.; Liu, C.W. Experimental Demonstration of TreeFETs Combining Stacked Nanosheets and Low Doping Interbridges by Epitaxy and Wet Etching. IEEE Electron Device Lett. 2022, 43, 682–685. [Google Scholar] [CrossRef]

- Ye, H.Y.; Liu, C.W. On-Current Enhancement in TreeFET by Combining Vertically Stacked Nanosheets and Interbridges. IEEE Electron Device Lett. 2020, 41, 1292–1295. [Google Scholar] [CrossRef]

- Deen, M.; Yan, Z. DIBL in short-channel NMOS devices at 77 K. IEEE Trans. Electron Devices 1992, 39, 908–915. [Google Scholar] [CrossRef]

- Deen, M.; Yan, Z. Substrate bias effects on drain-induced barrier lowering in short-channel PMOS devices. IEEE Trans. Electron Devices 1990, 37, 1707–1713. [Google Scholar] [CrossRef]

- Wu, Y.T.; Chiang, M.H.; Chen, J.F.; Liu, T.J.K. Simulation-Based Study of High-Permittivity Inserted-Oxide FinFET With Low-Permittivity Inner Spacers. IEEE Trans. Electron Devices 2021, 68, 5529–5534. [Google Scholar] [CrossRef]

| Parameters | Values |

|---|---|

| Gate length, | 12 nm |

| Spacer length, | 5 nm |

| Source/Drain length, | 13 nm |

| Contact gate pitch, CGP | 48 nm |

| Channel width, | 20–50 nm |

| Channel thickness, | 5 nm |

| Vertical channel space, | 10 nm |

| Equivalent oxide thickness, | 0.7 nm |

| Channel doping, | cm |

| Source/Drain doping, | cm |

| PTS doping, | cm |

| Contact resistance | ·cm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kuang, F.; Li, C.; Li, H.; You, H.; Deen, M.J. Effect of Non-Ideal Cross-Sectional Shape on the Performance of Nanosheet-Based FETs. Electronics 2023, 12, 3419. https://doi.org/10.3390/electronics12163419

Kuang F, Li C, Li H, You H, Deen MJ. Effect of Non-Ideal Cross-Sectional Shape on the Performance of Nanosheet-Based FETs. Electronics. 2023; 12(16):3419. https://doi.org/10.3390/electronics12163419

Chicago/Turabian StyleKuang, Fengyu, Cong Li, Haokun Li, Hailong You, and M. Jamal Deen. 2023. "Effect of Non-Ideal Cross-Sectional Shape on the Performance of Nanosheet-Based FETs" Electronics 12, no. 16: 3419. https://doi.org/10.3390/electronics12163419

APA StyleKuang, F., Li, C., Li, H., You, H., & Deen, M. J. (2023). Effect of Non-Ideal Cross-Sectional Shape on the Performance of Nanosheet-Based FETs. Electronics, 12(16), 3419. https://doi.org/10.3390/electronics12163419