Control and Implementation of the Parallel Enhanced Commutation Integrated Nested Multilevel Inverter Topology

Abstract

1. Introduction

2. Cascaded Multilevel Inverters

2.1. Cascaded Multilevel Inverters as Reconfigurable Batteries

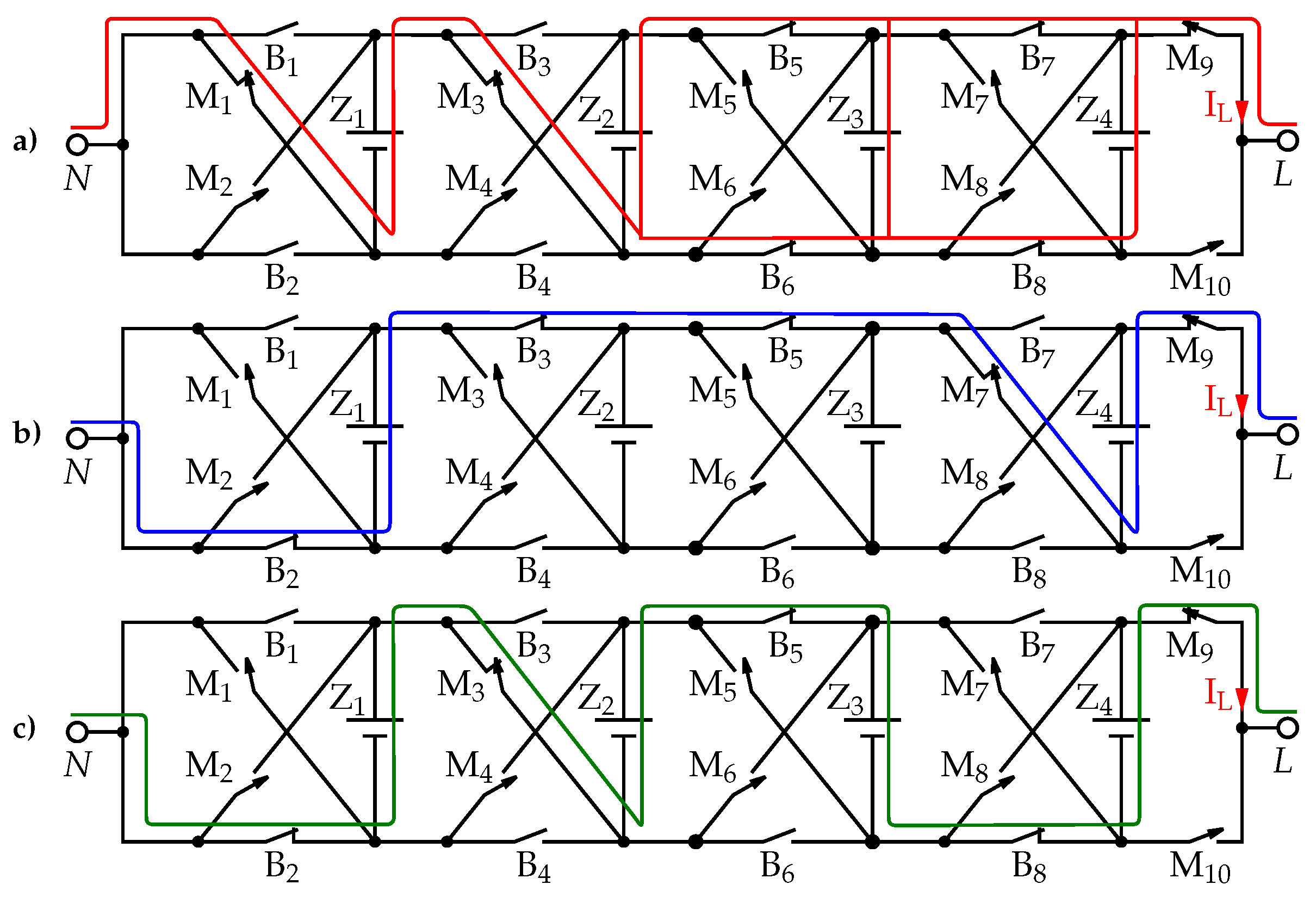

2.2. PECIN MLI

3. Elaboration of the PECIN Switching Function

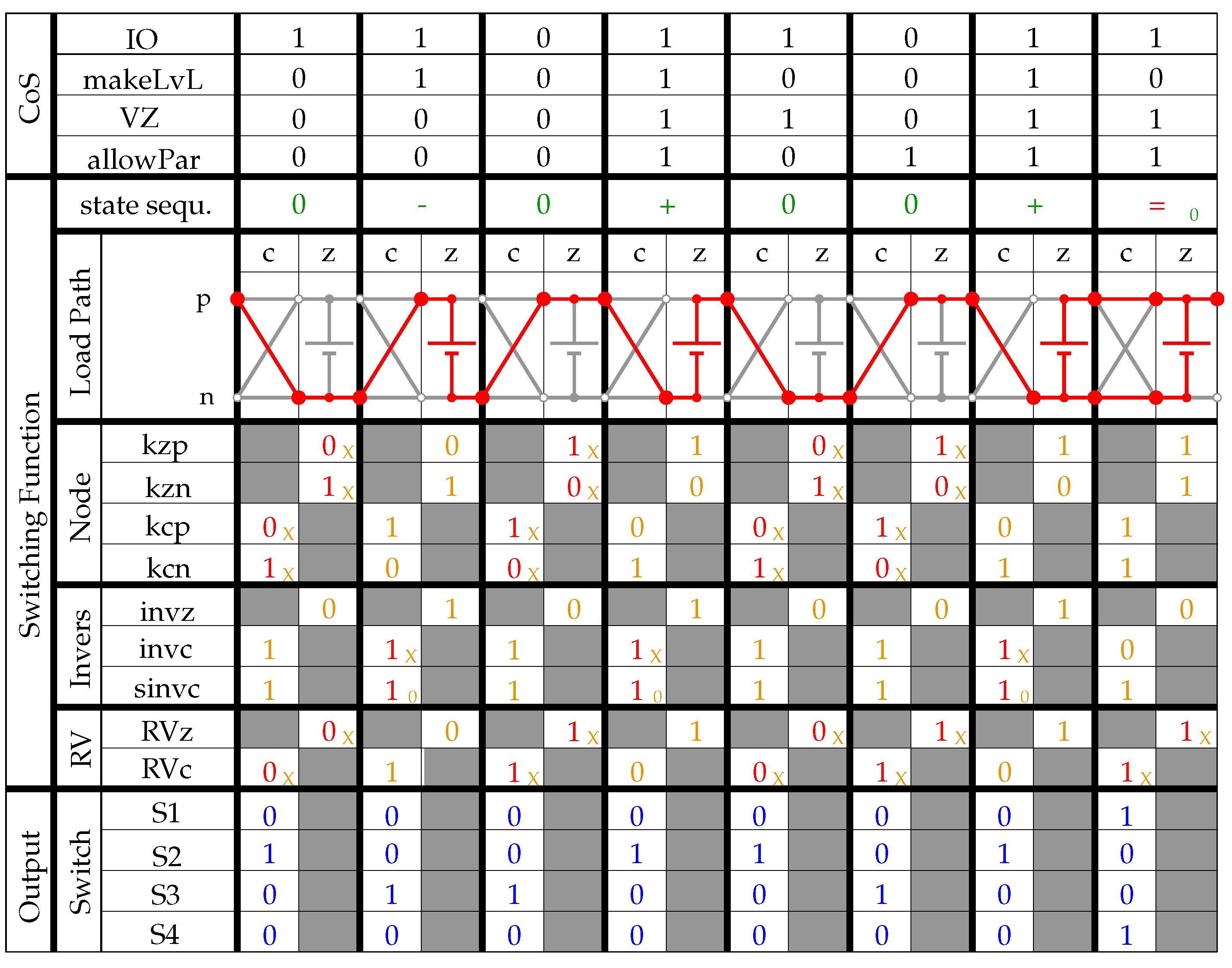

3.1. Table Lookups

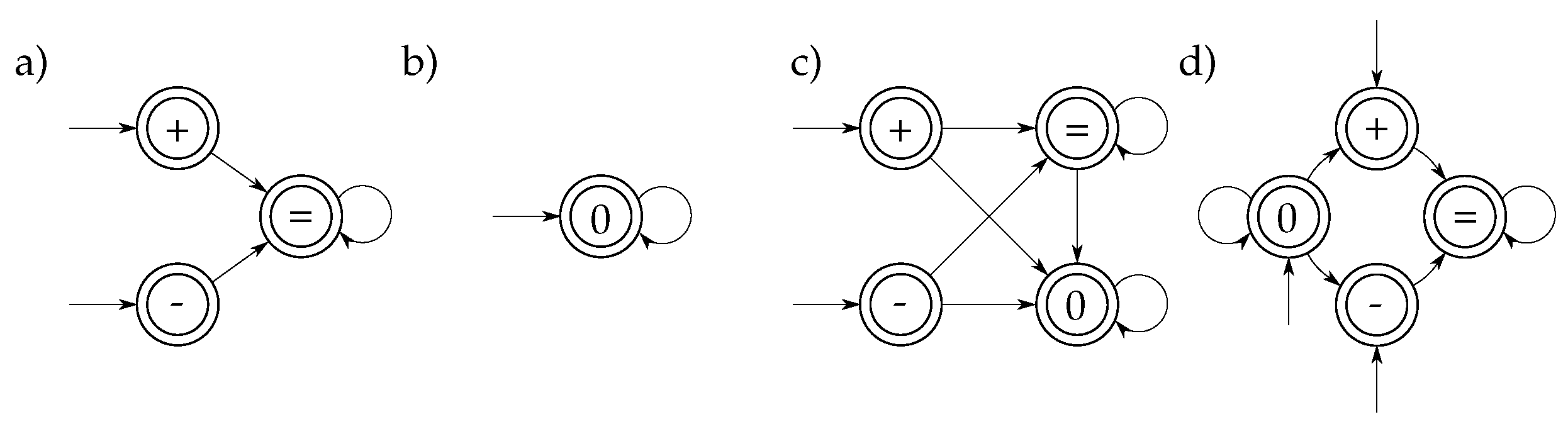

3.2. Modularisation and Switching States

3.3. PECIN Switching Function

3.3.1. Inputs of the Switching Function

Subset 1: Which Cells Can Contribute?

Subset 2: Of Those That Can, Which Cells Must Contribute?

Subset 3: How Should the Cells Contribute?

Subset 4: What Happens to the Cells That Are Not Needed?

3.3.2. Declaration of the Switching State S

| Algorithm 1 Finalisation of the cell states |

|

3.3.3. General Switching Patterns of the PECIN MLI

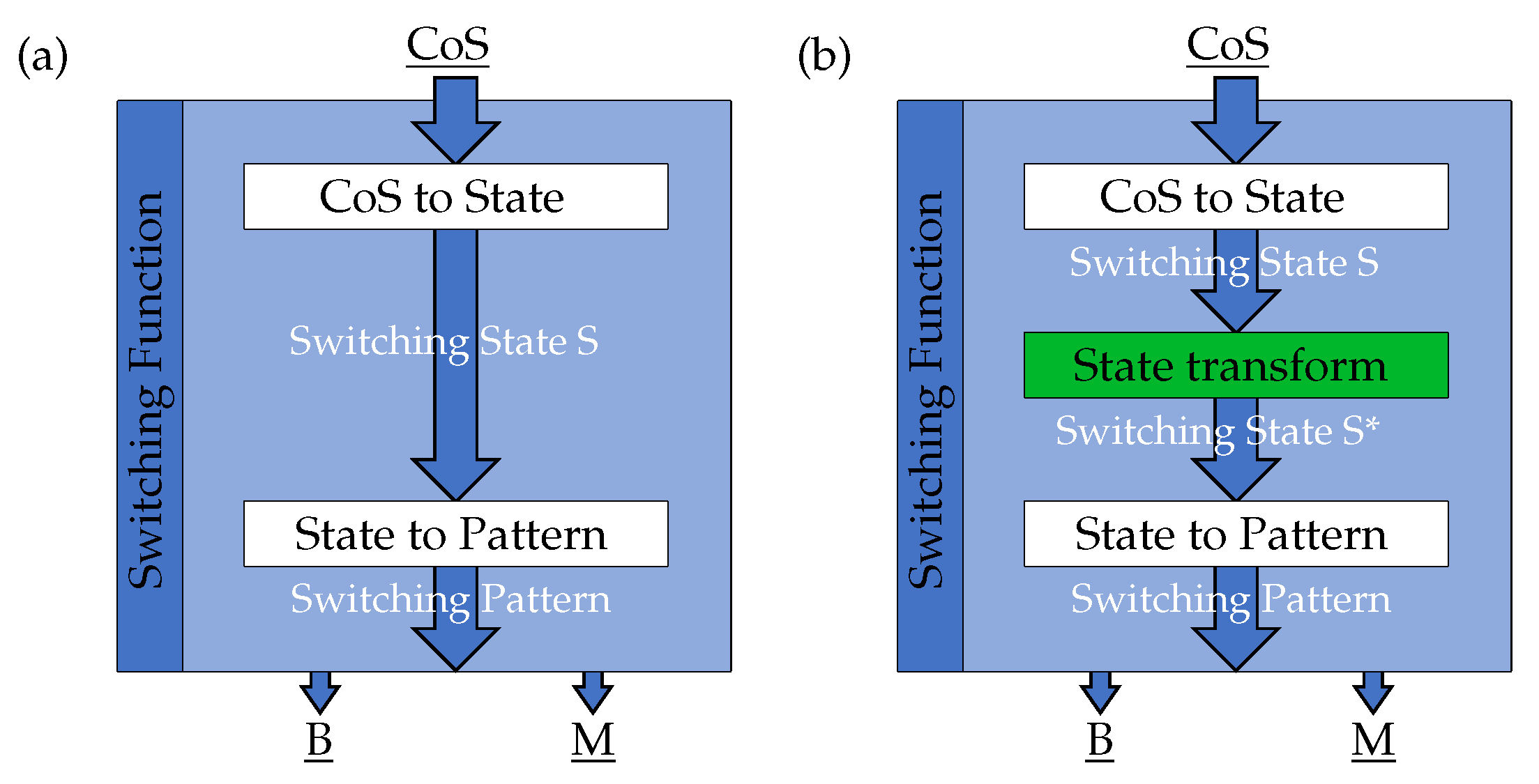

3.3.4. State Transformation and Switching State S*

3.3.5. Init Table

3.3.6. Finalisation

| Algorithm 2 Finalisation of the switching table |

|

3.3.7. Demodulation Switching State to Switching Pattern

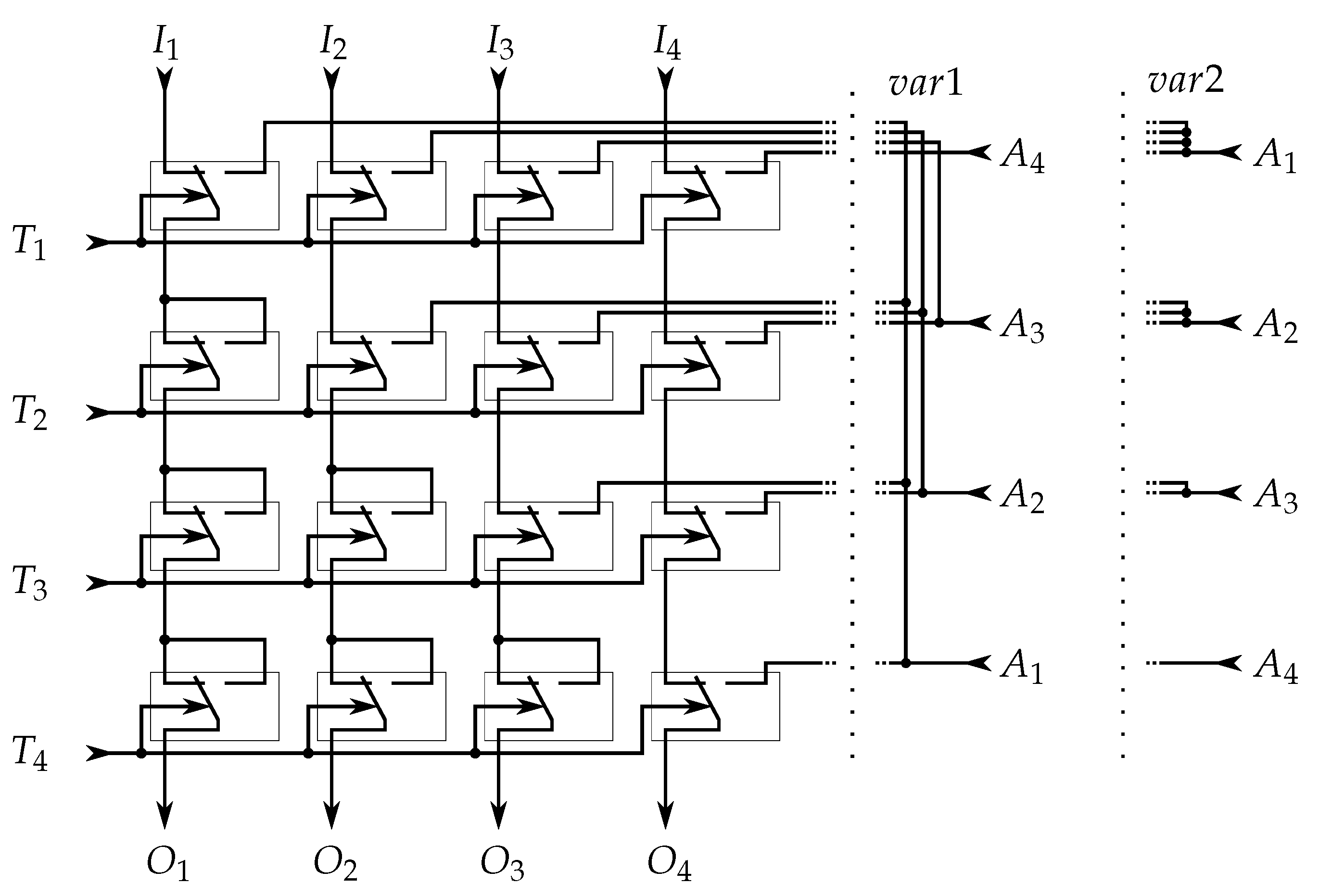

4. FPGA Parallel Solution

4.1. Solving of Dependencies between Successive Cells

4.2. Resolving Dependencies and Avoiding Iteration

| Algorithm 3 Shift and Insertion Function fct |

|

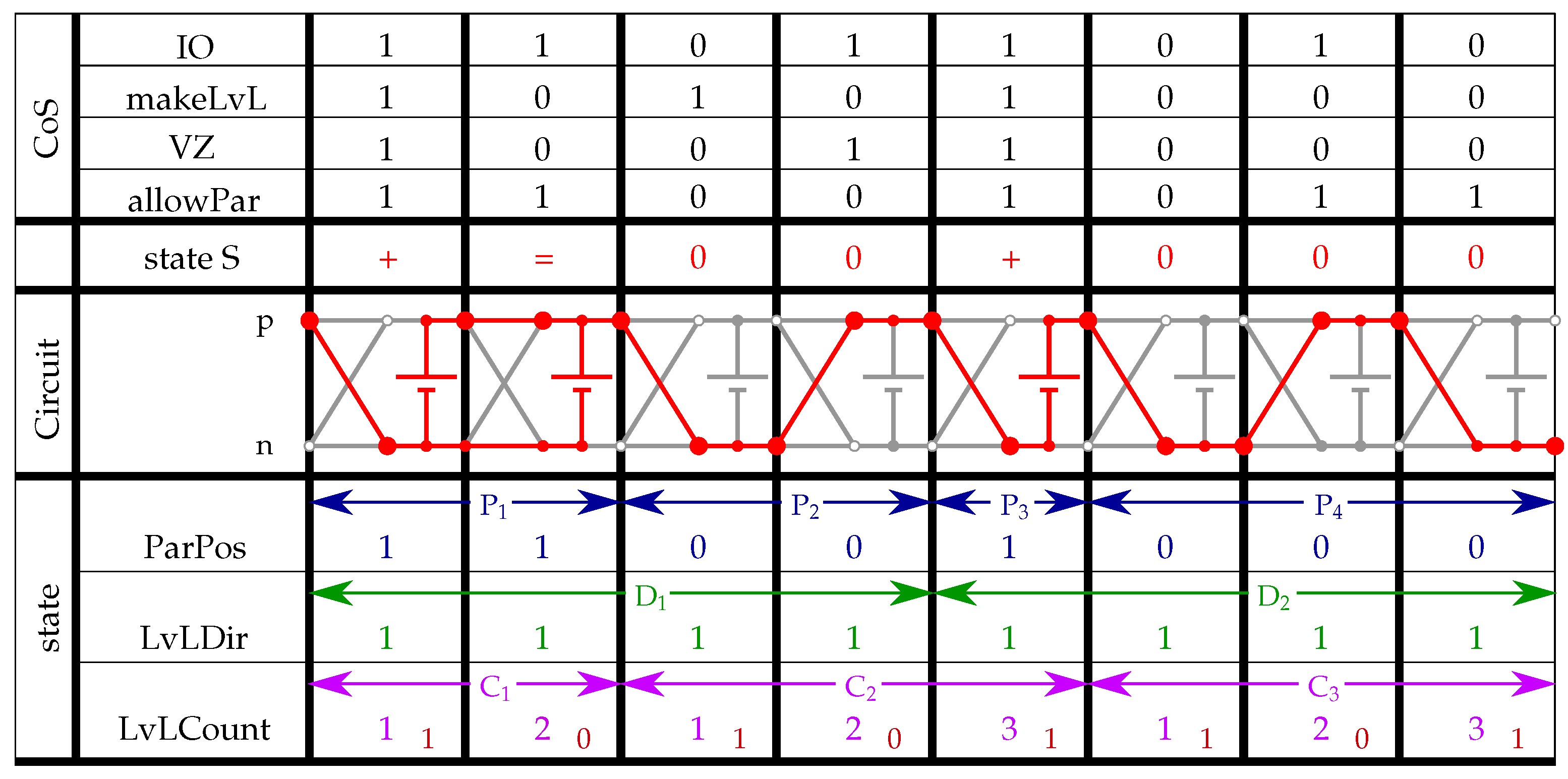

4.3. Identifying Parallel Cell Compounds (ParPos)

4.4. Identification of the Area of Influence of a Sign (LvLDir)

4.5. Identification of Cells in Bypass (LvLCount)

| Algorithm 4 PECIN MLI Switching Function |

|

4.6. Determination of the Initial RV (PreBypass)

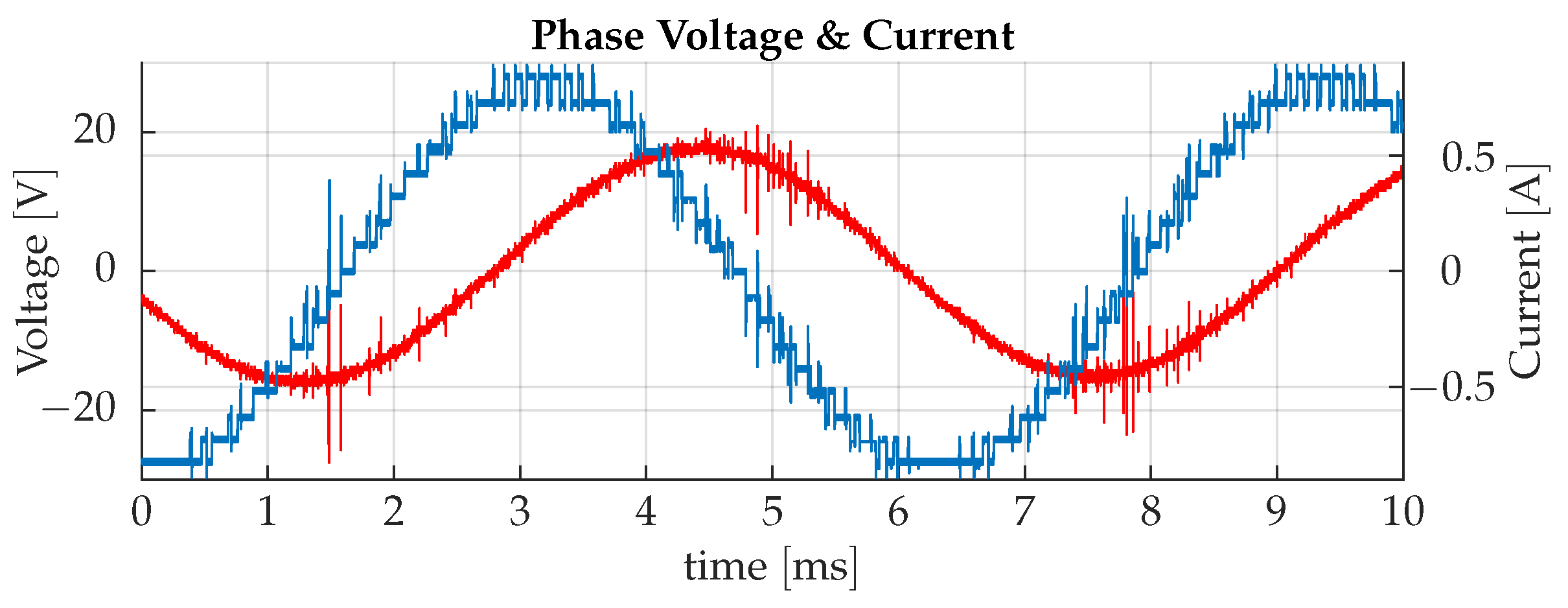

5. Practical Validation

6. Conclusions and Outlook

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| BEV | Battery Electric Vehicle |

| BCS | Bridge-Type Connected Source |

| BMS | Battery-Management System |

| BtB | Back-to-Back |

| CHB | Cascaded H-Bridge |

| ChalfB | Cascaded half Bridge |

| Cl | Closing (Unit) |

| CCS | Cascaded Cross-Switched |

| CoS | Cell operating State |

| CS | Cross-Switched |

| ECIN | Enhanced Commutation Integrated Nested |

| FPGA | Field Programmable Gate Array |

| M2B | Modular Multilevel Battery |

| MLI | Multilevel Inverter |

| MMLC | Modular Multilevel Converter |

| MMSPC | Modular Multilevel Series/Parallel Converter |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor |

| NFA | Nondeterministic Finite Automaton |

| NLC | Nearest Level Control |

| OCV | Open-Circuit Voltage |

| PCB | Printed Circuit Board |

| PECIN | Parallel Enhanced Commutation Integrated Nested |

| PWM | Pulse Width Modulation |

| RV | Routing Vector |

| SM | Submodule |

| SOC | State-of-Charge |

| SP | Switching Pattern |

| S | Switching State |

| S* | abstracted Switching State |

| SVC | Space Vector Control |

| THD | Total Harmonic Distortion |

| TU | Termination Unit |

References

- Lu, L.; Han, X.; Li, J.; Hu, J.; Ouyang, M. A review on the key issues for lithium-ion battery management in electric vehicles. J. Power Sources 2013, 226, 272–288. [Google Scholar] [CrossRef]

- Emadi, A. Advanced Electric Drive Vehicles, 1st ed.; CRC Press: Boca Raton, FL, USA, 2014. [Google Scholar]

- Sang-Hoon, K. Chapter 7—pulse width modulation inverters. In Electric Motor Control; Elsevier: Amsterdam, The Netherlands, 2017; pp. 265–340. [Google Scholar]

- Singh, G.; Garg, V.K. Thd analysis of cascaded h-bridge multi-level inverter. In Proceedings of the 2017 4th International Conference on Signal Processing, Computing and Control (ISPCC), Solan, India, 21–23 September 2017; pp. 229–234. [Google Scholar] [CrossRef]

- Marquardt, R. Modular Multilevel Converter: An universal concept for HVDC-Networks and extended DC-Bus-applications. In Proceedings of the 2010 International Power Electronics Conference—ECCE ASIA, Sapporo, Japan, 21–24 June 2010; pp. 502–507. [Google Scholar] [CrossRef]

- Nami, A.; Liang, J.; Dijkhuizen, F.; Demetriades, G.D. Modular Multilevel Converters for HVDC Applications: Review on Converter Cells and Functionalities. IEEE Trans. Power Electron. 2015, 30, 18–36. [Google Scholar] [CrossRef]

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the 2003 IEEE Bologna Power Tech Conference Proceedings, Bologna, Italy, 23–26 June 2003; Volume 3, p. 6. [Google Scholar] [CrossRef]

- Baker, R.H.; Bannister, L.H. Electric Power Converter. U.S. Patent 3867643, 18 February 1975. [Google Scholar]

- Quraan, M.; Tricoli, P.; D’Arco, S.; Piegari, L. Efficiency assessment of modular multilevel converters for battery electric vehicles. IEEE Trans. Power Electron. 2017, 32, 2041–2051. [Google Scholar] [CrossRef]

- Korte, C.; Specht, E.; Hiller, M.; Goetz, S. Efficiency evaluation of mmspc/chb topologies for automotive applications. In Proceedings of the 2017 IEEE 12th International Conference on Power Electronics and Drive Systems (PEDS), Toulouse, France, 9–12 July 2019; pp. 324–330. [Google Scholar] [CrossRef]

- Chang, F.; Ilina, O.; Lienkamp, M.; Voss, L. Improving the Overall Efficiency of Automotive Inverters Using a Multilevel Converter Composed of Low Voltage Si mosfets. IEEE Trans. Power Electron. 2019, 34, 3586–3602. [Google Scholar] [CrossRef]

- Kersten, A.; Kuder, M.; Grunditz, E.; Geng, Z.; Wikner, E.; Thiringer, T.; Weyh, T.; Eckerle, R. Inverter and battery drive cycle efficiency comparisons of chb and mmsp traction inverters for electric vehicles. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE), Genova, Italy, 3–5 September 2019; pp. 1–12. [Google Scholar] [CrossRef]

- Goetz, S.M.; Peterchev, A.V.; Weyh, T. Modular multilevel converter with series and parallel module connectivity: Topology and control. IEEE Trans. Power Electron. 2015, 30, 203–215. [Google Scholar] [CrossRef]

- Kangarlu, M.F.; Babaei, E.; Sabahi, M. Cascaded crossswitched multilevel inverter in symmetric and asymmetric conditions. IET Power Electron. 2013, 6, 1041–1050. [Google Scholar] [CrossRef]

- Komsiyska, L.; Buchberger, T.; Diehl, S.; Ehrensberger, M.; Hanzl, C.; Hartmann, C.; Hölzle, M.; Kleiner, J.; Lewerenz, M.; Liebhart, B.; et al. Critical Review of Intelligent Battery Systems: Challenges, Implementation and Potential for Electric Vehicles. Energies 2021, 14, 5989. [Google Scholar] [CrossRef]

- Goetz, S.M.; Li, Z.; Liang, X.; Zhang, C.; Lukic, S.M.; Peterchev, A.V. Control of Modular Multilevel Converter with Parallel Connectivity Application to Battery Systems. IEEE Trans. Power Electron. 2017, 32, 8381–8392. [Google Scholar] [CrossRef]

- Helling, F.; Glück, J.; Singer, A.; Weyh, T. Modular multilevel battery (m2b) for electric vehicles. In Proceedings of the 2016 18th European Conference on Power Electronics and Applications (EPE’16 ECCE Europe), Karlsruhe, Germany, 5–9 September 2016; pp. 1–9. [Google Scholar] [CrossRef]

- Babaei, E. Charge Balance Control Methods for a Class of Fundamental Frequency Modulated Asymmetric Cascaded Multilevel Inverters. J. Power Electron. 2011, 11, 811–818. [Google Scholar] [CrossRef]

- Vasiladiotis, M.; Rufer, A. Balancing control actions for cascaded H-bridge converters with integrated battery energy storage. In Proceedings of the 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–10. [Google Scholar] [CrossRef]

- Raj, N.; Jagadanand, G.; George, S. A Modified Charge Balancing Scheme for Cascaded H-Bridge Multilevel Inverter. J. Power Electron. 2016, 16, 2067–2075. [Google Scholar] [CrossRef]

- Mashayekh, A.; Kersten, A.; Kuder, M.; Estaller, J.; Khorasani, M.; Buberger, J.; Weyh, T. Proactive SoC Balancing Strategy for Battery Modular Multilevel Management (BM3) Converter Systems and Reconfigurable Batteries. In Proceedings of the 23rd European Conference on Power Electronics and Applications (EPE’21 ECCE Europe), Virtual, 6–10 September 2021; pp. 1–10. [Google Scholar] [CrossRef]

- Porras, J.S.; Ioan-Stroe, D.; Sangwongwanich, A. State-Of-Energy Balancing Control with Cascaded H-Bridge for Second-Life Batteries. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 25–29 February 2023; pp. 571–576. [Google Scholar] [CrossRef]

- Schmid, M.; Gebauer, E.; Hanzl, C.; Endisch, C. Active Model-Based Fault Diagnosis in Reconfigurable Battery Systems. IEEE Trans. Power Electron. 2021, 36, 2584–2597. [Google Scholar] [CrossRef]

- Theiler, M.; Schneider, D.; Endisch, C. Experimental Investigation of State and Parameter Estimation within Reconfigurable Battery Systems. Batteries 2023, 9, 145. [Google Scholar] [CrossRef]

- Helling, F.; Glück, J.; Singer, A.; Pfisterer, H.-J.; Weyh, T. The ac battery a novel approach for integrating batteries into ac systems. Int. J. Electr. Power Energy Syst. 2019, 104, 150–158. [Google Scholar] [CrossRef]

- Liebhart, B.; Diehl, S.; Schmid, M.; Endisch, C.; Kennel, R. Improved Impedance Measurements for Electric Vehicles with Reconfigurable Battery Systems. In Proceedings of the 2021 IEEE 12th Energy Conversion Congress & Exposition-Asia (ECCE-Asia), Singapore, 24–27 May 2021; pp. 1736–1742. [Google Scholar] [CrossRef]

- Schwitzgebel, F.; Buberger, J.; Kuder, M.; Karnehm, D.; Sorokina, N.; Wiedenmann, A.; Mashayekh, A.; Eckerle, R.; Weyh, T. Multilevel Inverter based Battery System Operation using a Decentralized Controller. In Proceedings of the 2022 International Conference on Smart Energy Systems and Technologies (SEST), Eindhoven, The Netherlands, 5–7 September 2022; pp. 1–6. [Google Scholar] [CrossRef]

- Quraan, M.; Abu-Khaizaran, M.; Sa’ed, J.; Hashlamoun, W.; Tricoli, P. Design and control of battery charger for electric vehicles usingmodular multilevel converters. IET Power Electron. 2021, 14, 140–157. [Google Scholar] [CrossRef]

- Alatai, S.; Salem, M.; Ishak, D.; Bughneda, A.; Kamarol, M.; Luta, D.N. Cascaded Multi-Level Inverter for Battery Charging-Discharging using Buck-Boost Switch. In Proceedings of the 2021 IEEE Industrial Electronics and Applications Conference (IEACon), Virtual, 3–4 October 2021; pp. 108–112. [Google Scholar] [CrossRef]

- El-Hosainy, A.; Hamed, H.A.; Azazi, H.Z.; El-Kholy, E.E. A review of multilevel inverter topologies, control techniques and applications. In Proceedings of the 2017 19th International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 19–21 December 2017; pp. 1265–1275. [Google Scholar] [CrossRef]

- Venkataramanaiah, J.; Suresh, Y.; Panda, A.K. A review on symmetric, asymmetric, hybrid and single dc sources based multilevel inverter topologies. Renew. Sustain. Energy Rev. 2017, 76, 788–812. [Google Scholar] [CrossRef]

- Terbrack, C.; Stöttner, J.; Endisch, C. Design and Validation of the Parallel Enhanced Commutation Integrated Nested Multilevel Inverter Topology. IEEE Trans. Power Electron. 2022, 37, 15163–15174. [Google Scholar] [CrossRef]

- Gupta, K.K.; Jain, S. Topology for multilevel inverters to attain maximum number of levels from given DC sources. IET Power Electron. 2012, 5, 435–446. [Google Scholar] [CrossRef]

- Kangarlu, M.F.; Babaei, E. Cross-switched multilevel inverter: An innovative topology. IET Power Electron. 2013, 6, 642–651. [Google Scholar] [CrossRef]

- Kamaldeep; Kumar, J. Switch reduction and performance analysis using different modulation technique in multilevel inverter. In Proceedings of the 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Delhi, India, 4–6 July 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Rodriguez, J.; Leeb, S. A multilevel inverter topology for inductively-coupled power transfer. In Proceedings of the 18th Annual IEEE Applied Power Electronics Conference and Exposition (APEC ’03), Miami, FL, USA, 9–13 February 2003; Volume 2, pp. 1118–1126. [Google Scholar] [CrossRef]

- Zhang, H.; Meng, Y.; Ning, L.; Zou, Y.; Wang, X.; Wang, X. Fast and simple space vector modulation method for multilevel converters. IET Power Electron. 2020, 13, 14–22. [Google Scholar] [CrossRef]

| kzp | kzn | kcp | kcn | invz | invc | sinvc | RVz | RVc | |

|---|---|---|---|---|---|---|---|---|---|

| Bypass (0) | X | X | X | X | 0 | 1 | 1 | X | X |

| Positive active (+) | 1 | 0 | 0 | 1 | 1 | X | 0 | 1 | 0 |

| Positive active (−) | 0 | 1 | 1 | 0 | 1 | X | 0 | 0 | 1 |

| Parallel (=) | 1 | 1 | 1 | 1 | 0 | 0 | 1 | X | X |

| S* | RV | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| kcp | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | |

| kcn | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | |

| SP | SP6 | SP6 | SP2 | SP5 | SP4 | SP1 | SP3 | SP3 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Terbrack, C.; Speer, S.; Endisch, C. Control and Implementation of the Parallel Enhanced Commutation Integrated Nested Multilevel Inverter Topology. Electronics 2023, 12, 3130. https://doi.org/10.3390/electronics12143130

Terbrack C, Speer S, Endisch C. Control and Implementation of the Parallel Enhanced Commutation Integrated Nested Multilevel Inverter Topology. Electronics. 2023; 12(14):3130. https://doi.org/10.3390/electronics12143130

Chicago/Turabian StyleTerbrack, Christoph, Sascha Speer, and Christian Endisch. 2023. "Control and Implementation of the Parallel Enhanced Commutation Integrated Nested Multilevel Inverter Topology" Electronics 12, no. 14: 3130. https://doi.org/10.3390/electronics12143130

APA StyleTerbrack, C., Speer, S., & Endisch, C. (2023). Control and Implementation of the Parallel Enhanced Commutation Integrated Nested Multilevel Inverter Topology. Electronics, 12(14), 3130. https://doi.org/10.3390/electronics12143130