1. Introduction

The world is increasingly interested in utilizing various types of renewable energy sources to generate electrical power, driven by concerns regarding energy security and the environmental impact resulting from carbon dioxide emissions [

1,

2]. Solar and wind energy, in particular, have gained widespread adoption worldwide [

3,

4]. For instance, photovoltaic solar panels produce variable low-voltage outputs ranging from 12–40 V, which are unsuitable for applications requiring high DC supply voltage or household appliances [

5,

6]. Therefore, DC-DC converters are employed to step up very low input voltage to high output DC voltage for various applications such as streetlights, motor drives, microgrid systems, uninterruptible power supplies, fuel cells, and medical equipment [

2,

4,

5,

6,

7,

8,

9,

10,

11,

12,

13,

14,

15,

16,

17,

18,

19,

20,

21,

22,

23,

24,

25,

26,

27,

28,

29,

30,

31,

32,

33,

34,

35]. Different converter topologies, including buck-boost, boost, and Ćuk DC-DC converters, have been introduced to achieve high voltage gain. The choice of converter depends on the specific application requirements. However, these converters encounter challenges when targeting ultra-high voltage gain. Key issues include a lower count of inductors and capacitors, reduced efficiency at high voltage gain with extremely high duty ratios, high voltage stress on power switches and diodes (equivalent to the output voltage), and increased current stress on power devices as the load current rises. In this context, current stress refers to the magnitude of current flowing through the switch during the on state and is influenced by the paths traversed by the current through the MOSFET. Moreover, these converters suffer from elevated switching and conduction losses when the duty cycle exceeds 0.9, as well as low power density [

20]. Although boost converter topologies can achieve voltage step-up with high voltage gains of up to 10, their efficiency diminishes at high duty cycles [

10,

36]. Several researchers have proposed new technologies for DC-DC converters to attain high voltage gain in renewable energy systems (RESs).

A modified DC-DC converter, interleaved with a boost converter based on soft switching between the main and auxiliary power MOSFETs, has been proposed to achieve high voltage gain and solve the inrush current problem [

1]. Another modification to the boost converter using a hybrid inductor capacitor has been proposed in [

8], and another with a switch capacitor (SC), switch inductor (SL), and voltage multiplier (VM) in [

31]. A cascaded conventional SEPIC with a boost converter has been proposed in [

24,

26], and a modified SEPIC based on an interleaved buck-boost converter in [

11]. A modified converter with multi-input has been proposed in [

9,

25]. These converters, as mentioned, are modified to achieve high voltage gain with high power density. However, they have low voltage gain and a high number of inductors and capacitors. Additionally, they require a high number of power diodes and power MOSFETs to step up the low input to a high output voltage. Furthermore, the power MOSFETs and diodes in these converters experience high voltage stress. Complex control was also required in [

8] to achieve high voltage gain. Moreover, these converters achieve high voltage gain with an extremely high duty cycle, resulting in high switching and conduction losses, as well as low performance and efficiency. Other topologies have been proposed, such as a modified DC-DC converter with coupled inductors and a voltage multiplier network (VMN) [

3], and a conventional SEPIC with a coupled inductor and VM [

23]. These converters have demonstrated high voltage gain, but they feature a high number of passive and active elements, as well as diodes. The large number of components leads to a high parasitic resistance of inductors and capacitors, resulting in reduced efficiency. Additionally, these converters operate at a low switching frequency, which necessitates the use of large values of inductors and capacitors. Moreover, the internal resistance of the power MOSFET (Ron) is high, further diminishing the voltage gain of the system. Furthermore, a major issue with coupled inductor converters is the occurrence of high spike voltages in the off state of the power switch due to the inductance with parasitic capacitance of the power MOSFET switch [

36]. To address this problem, a clamped circuit can be added to the power switch to prevent the occurrence of high spike voltages due to the coupled inductor [

2,

37]. However, adding more components to the circuit increases costs and reduces efficiency due to parasitism. In addition, the system will be heavy and large. Another problem is the pulsating input current at a low duty cycle, which makes these converters unsuitable for RES applications.

Other researchers have developed DC-DC converters to achieve high voltage gain using non-isolated coupled inductors. In [

12], a double power switch converter with double switch inductor (SL) was utilized. Additionally, in [

13], a modified converter incorporating a hybrid capacitor and inductor, and in [

14], a DC-DC converter employing the voltage lift technique, are proposed. Furthermore, in [

15,

16], a DC-DC converter based on SC with zero voltage switching, and in [

10,

17], a modified buck-boost converter featuring a single switch and pulsating input current, are described. However, these converters require an extremely high duty ratio to achieve a high voltage gain ratio. This implies high switching and conduction losses, low efficiency, low power density, and high voltage stress on the power switches, diodes, inductors, and capacitors. Additionally, these converters exhibit a high inductor count with low switching frequencies, which results in high parasitic resistance, diminished performance, and efficiency. A modified boost converter with dual power switch was proposed in [

18], a modified boost converter with a single switch, multiplier capacitor, and SL in [

19,

22], and a multi-input converter with multiple capacitors as hybrid energy storage in [

21], with the goal of attaining high voltage gain for RESs. A buck-boost converter with SC SL was developed in [

27], a pair of cascaded conventional boost converters with dual switches in [

28] and with a single switch in [

30], and a modified buck interleaved with SEPIC based on (SC) (SL) with two input sources in [

29]. These converters achieve high voltage gain; however, they have a large number of power switches and diodes, which has a high impact on system efficiency and performance. In addition, the voltage and current stress on the power switch is high. Furthermore, the gate control circuit is large and complex to implement.

In this paper, a new single-cell hybrid switched inductor-capacitor DC-DC converter is proposed to demonstrate the verification of ultra-high voltage gain in renewable energy applications (REA). The proposed modification involves incorporating a single cell of a hybrid inductor, along with a diode and double capacitors, interleaved with the main switch. This integration enables the proposed converter to attain a high voltage gain while ensuring that the input current does not experience zero pulsations at very low duty cycles. Additionally, the current stress on the main switch will reduce as the duty ratio increases, as shown in Figure 11f when the single-cell capacitor C1 charge becomes zero. Furthermore, the converter employs a modified hybrid switch inductor in dual boosting mode, working with a single switch. This arrangement allows for the realization of an ultra-high voltage gain. Moreover, one of the passive components, L2, will be open circuit, and D1 is working at zero current switching, which means a reduction in the total power loss of the converter.

2. Structure and Operation of the Proposed DC–DC Converter

The DC-DC converter is modified to achieve a high voltage gain by stepping up a low input voltage range of 20–40 V to an output voltage of 200 V. The proposed converter is based on a modified hybrid switched inductor-capacitor configuration to verify high voltage gain.

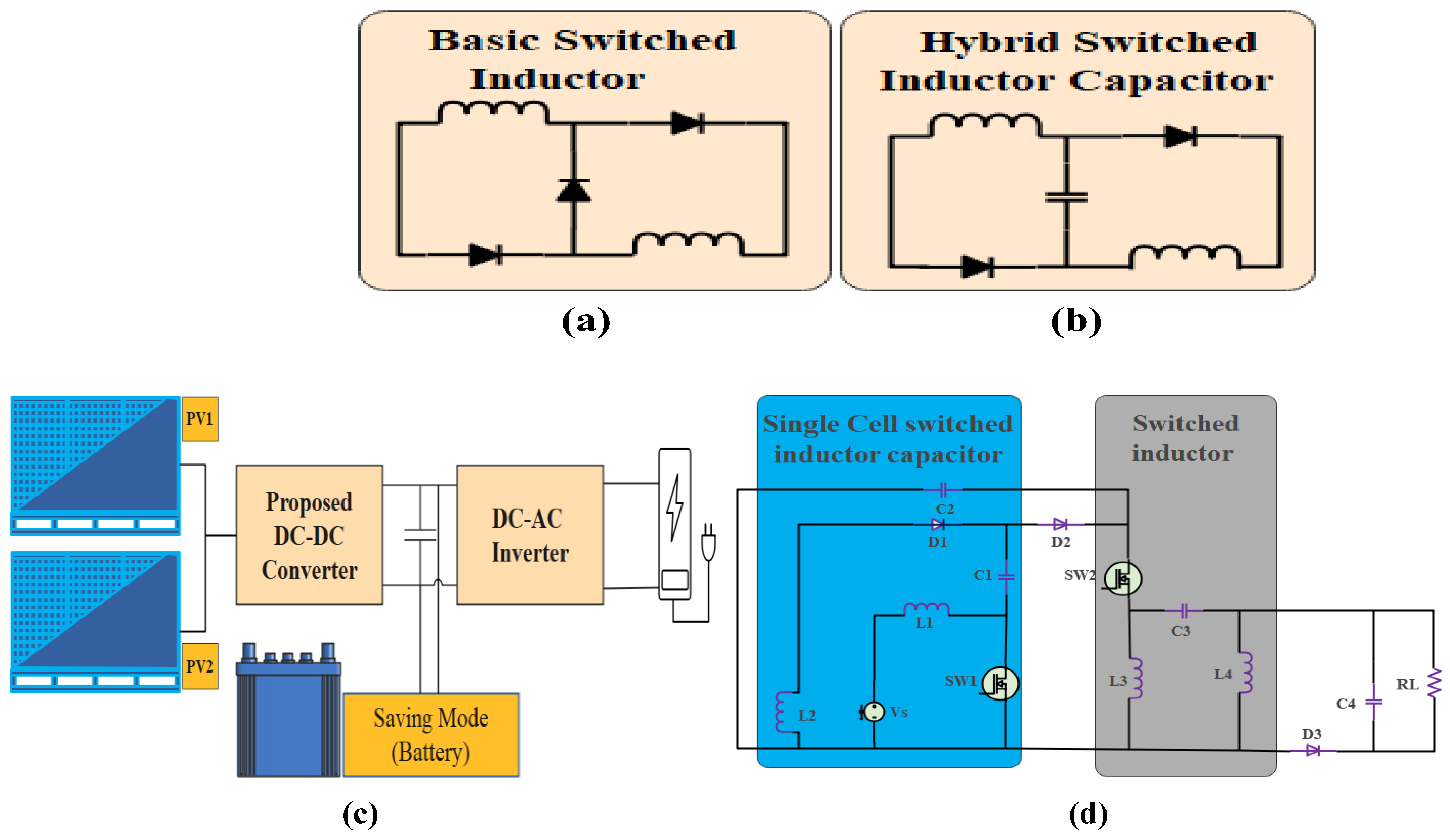

Figure 1a shows the basic connection of a switched inductor, while

Figure 1b illustrates the hybrid connection of a switched inductor and a capacitor. Consequently, the proposed converter is designed for Renewable Energy Sources (RES). In

Figure 1c, the connection of the proposed converter with PV Panels and Battery is shown for Energy Saving Mode Applications. The structure of the proposed converter includes four inductors, four capacitors, three diodes, and two power switches, as depicted in

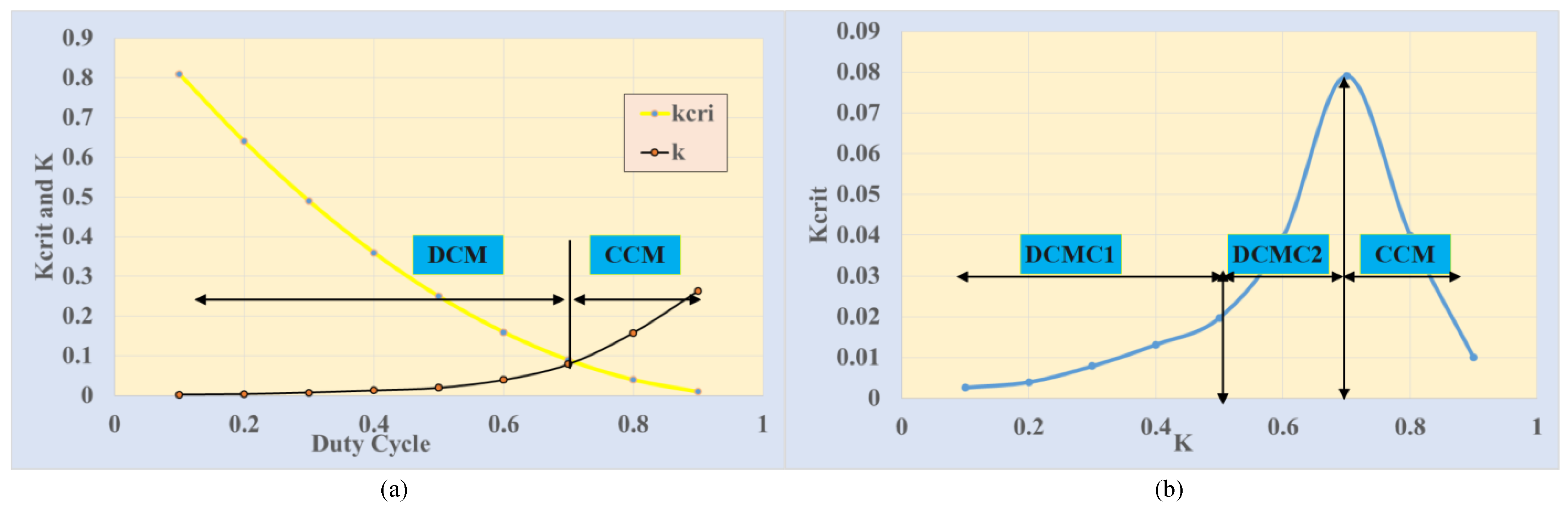

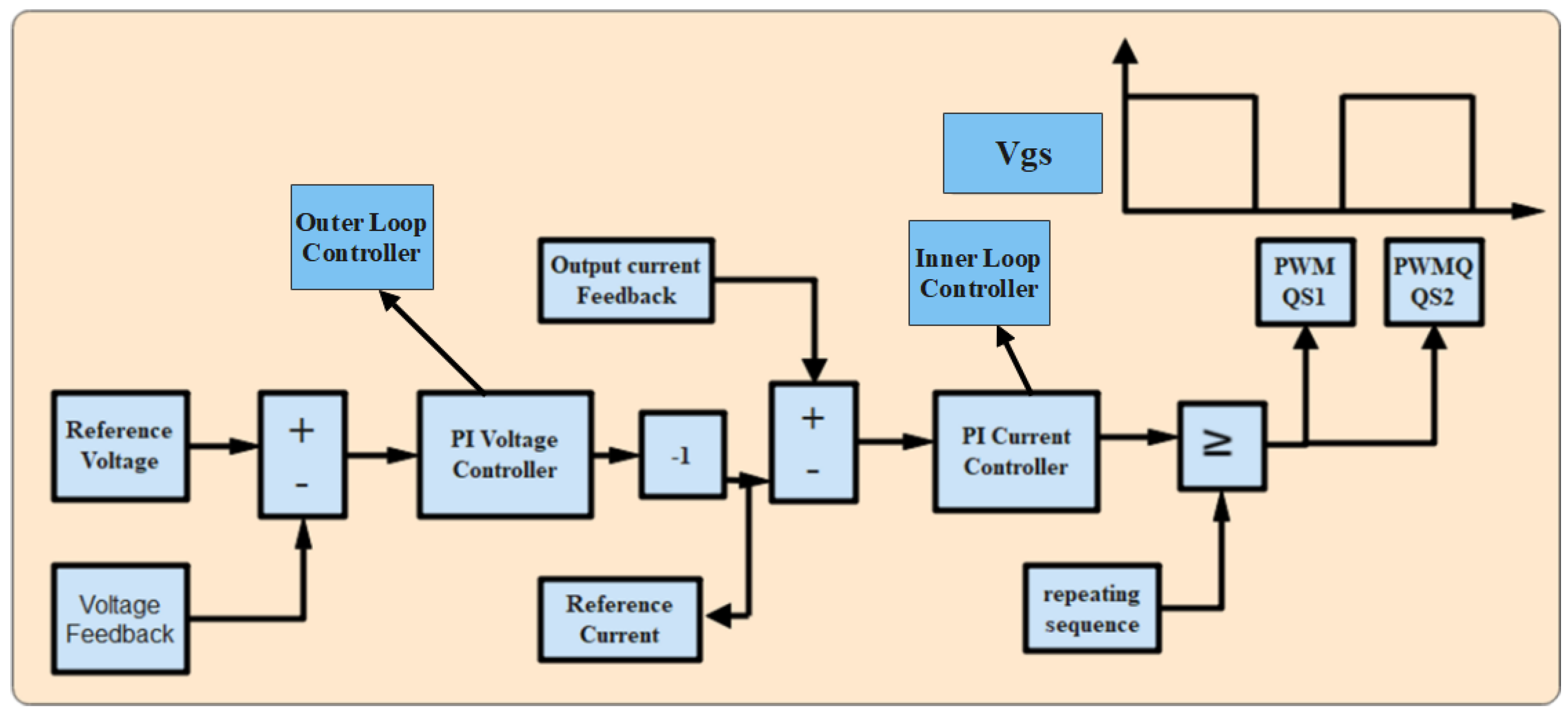

Figure 1d. The main advantages of the proposed converter are that it utilizes non-coupled inductors and is transformerless. It employs a high switching frequency to reduce the sizes of inductors and capacitors, thereby increasing its efficiency. The proposed converter has a simple structure with a straightforward control circuit. The new single cell of an inductor and capacitor, which is interleaved with the main switch, helps avoid pulsating input current at low duty cycles and minimizes voltage stress on the power switches, diodes, and inductors. Additionally, the current stress on the main switch is reduced when the duty cycle increases. Furthermore, the proposed converter achieves an ultra-high voltage gain compared to previous DC-DC converters. In terms of the power switch PWM generator, it uses a simple design where both MOSFETs turn on and off simultaneously. The proposed converter can operate in DCM under two cases. Firstly, it can function in DCM Case 1 (DCMC1) at a low duty cycle and maximum input voltage, with a duty ratio below 50%. Secondly, the proposed converter can operate in DCM Case 2 (DCMC2) when the input voltage decreases during the day at a high load current, with a duty ratio above 50%. Additionally, the converter can also operate in CCM when the load current increases and the duty ratio exceeds 70%. These scenarios are illustrated in Figure 4a,b, which demonstrates the dynamic performance of the proposed converter.

2.1. Proposed Converter Operation DCMC1

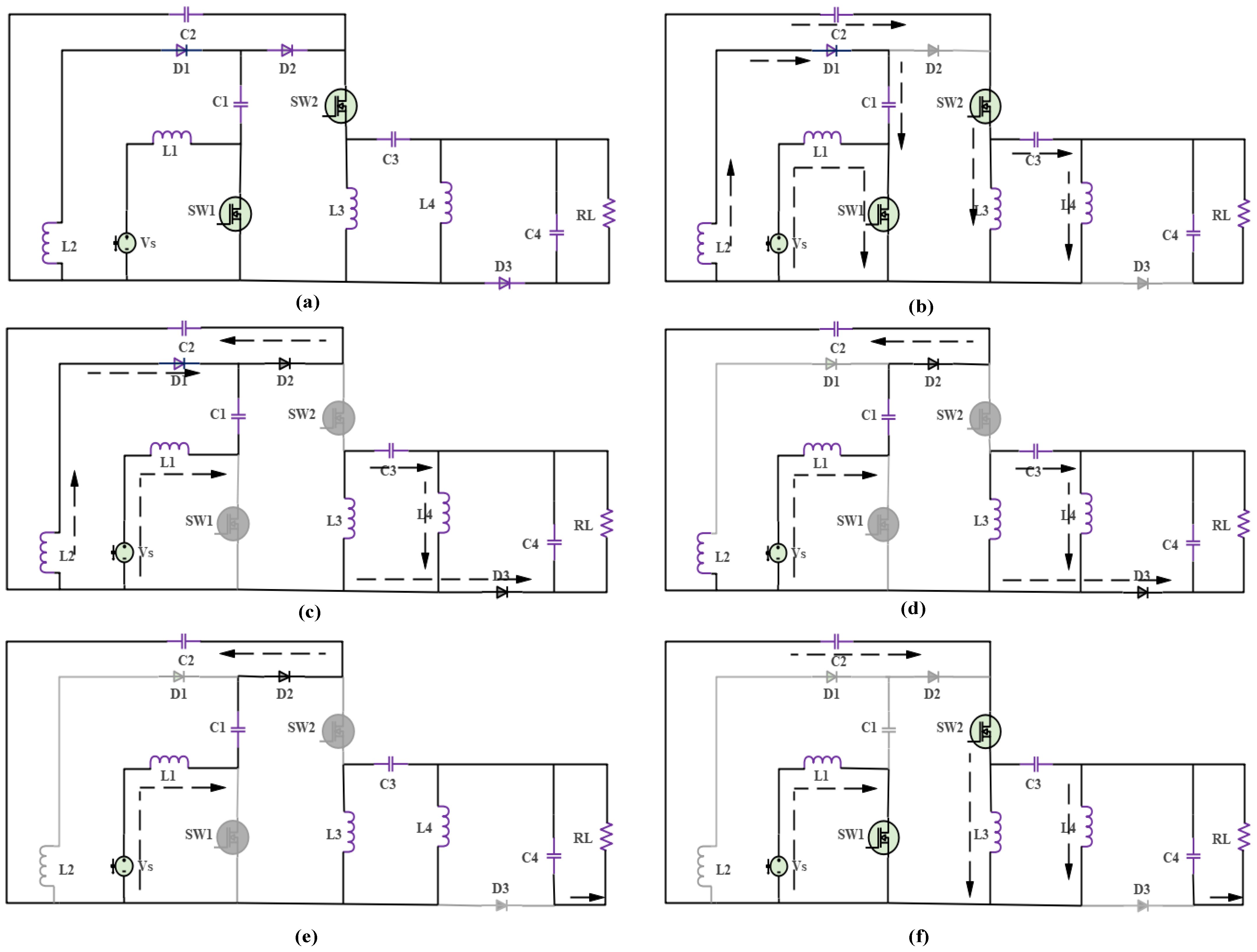

The proposed converter can operate in DCMC1 in four states of operation during one cycle when the input voltage is at its maximum, with a low duty cycle, and at light load. The waveform of this mode of operation is shown in

Figure 2a. The four states of this operational mode are listed below:

State 1: [0–t

0]: In this mode, the two power MOSFETs (Sw

1 and Sw

2) are in the on state, and a PWM generator provides a high source-to-gate voltage to turn both MOSFETs on and keep diodes D

2 and D

3 off. During this mode, L

1 charges with energy from the input source, which is connected in series with it. L

2 begins to charge from C

1, and C

1 discharges the energy stored in L

2 through Sw

1. D

1 is on during this mode, and C

2 stores a significant amount of energy, which is used to charge L

3 through Sw

2. At the same time, L

4 starts charging from C

3. C

4 supplies power to the load and forms the current path for this mode, as shown in

Figure 2b.

The voltage equations of this mode for inductors, capacitors, diodes, and MOSFETs are as follows:

The current equations of this mode for inductors, capacitors, diodes, and MOSFETs are as follows:

where VL represents the voltage across the inductor, Vc denotes the voltage across the capacitor, Isw represents the current through the power MOSFET switch during the on state, Vo signifies the output voltage, iL represents the current through the inductor, Io represents the output current, RL represents the resistive load, ID is the current through the power diode, and Ic denotes the current through the capacitor.

State 2: [t

0–t

1]: In this mode, the two power MOSFETs are in the off state, and both diodes D

2 and D

3 in the on state. L

1 discharges energy to C

1 and charges C

2. L

2 starts discharging its energy to C

2 through D

1 and remains in the on state. C

2 stores a large amount of energy from L

1 and L

2. L

3 and L

4 start discharging their energy to C

4, which supplies high power to the load and forms the current path of this mode, as shown in

Figure 3c.

The voltage equations of this mode for inductors, capacitors, diodes, and MOSFETs are as follows:

The current equations of this mode for inductors, capacitors, diodes, and MOSFETs are as follows:

where Ii is the input current, which is equal to iL

1.

State 3: [t

1–t

2]: In this mode, the two power MOSFETs are still in the off state, and both diodes D

2 and D

3 are still in the on state. L

1 continues discharging energy to C

1 and charges C

2. L

2 reaches zero charge and iL

2 and ID

1 are zero. C

2 continues receiving energy from only L

1, and D

1 is now in the off state in this mode. L

3 and L

4 continue discharging their energy to C

4, which supplies high power to the load and forms the current path of this mode, as shown in

Figure 3d.

The current equations of this mode are as follows:

State 4: [t

2–t

3]: In this mode, the two power MOSFETs are still off, the PWM generator gives zero gate-to-source voltage to keep them in the off state, and only D

2 is still on. D

3 is now changed to the off state in this mode. L

1 continues discharging energy to charge C

1 and C

2. C

2 stores a large amount of energy for the next pulse to supply it to the load. L

2 has zero charge and iL

2 and ID

1 are zero, and D

1 is still off in this mode. L

3 and L

4 will have the same current values but in opposite directions: iL

3 = −iL

4. C

4 supplies high power to the load and forms the current path of this mode, as shown in

Figure 3e.

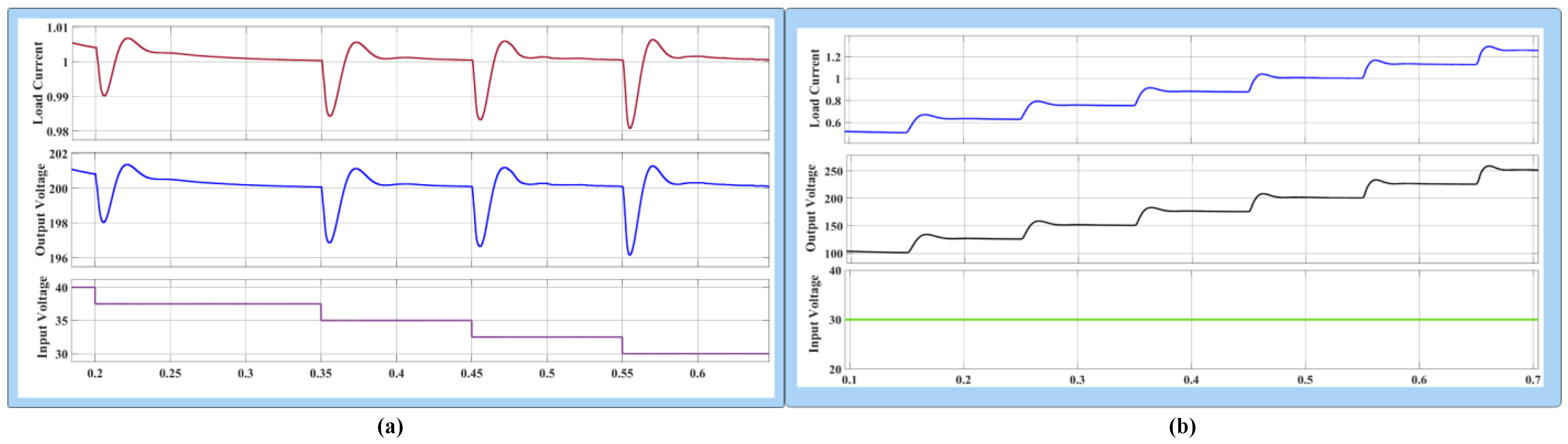

Figure 4a,b illustrate the dynamic performance of the proposed converter when operating in DCM and CCM, respectively. It is evident from the figures that the proposed converter operates in DCM for duty cycles below 70%. However, for duty cycles above 70%, the converter can operate in CCM based on the boundary condition specified in Equation (33).

2.2. Proposed Converter Operation in DCMC2

The proposed converter can operate in DCMC2 when the input voltage is reduced to the minimum value during the day, while the load current is high. In this mode, the input current is still in CCM, and L

2 will be in resonant mode with C

1, while L

3 and L

4 will continue to operate in DCM. Therefore, this mode has four states of operation, as shown in

Figure 2b: the proposed converter waveforms at DCMC2.

State 1: [0–t

0]: In this mode, the two MOSFETs Sw

1 and Sw

2 are in the on state, and both diodes D

2 and D

3 in their off states. L

1 starts charging energy from the input source, which is connected in series with it in CCM and never reaches zero. Inductor L

2 starts charging from C

1, and C

1 will discharge energy to L

2 through Sw

1 until (D − β

2), the charge across C

1 will be zero, and the current through Sw

1 will come only from IL

1 after this time, as shown in Figure 11f. D

1 is on in this mode, and C

2 stores a large amount of energy, which charges L

3 through Sw

2, and L

4 starts charging from C

3. C

4 supplies power to the load and forms the current path of this mode, as shown in

Figure 3b. The current and voltage equations of this mode are the same as for State 1 of DCM Case 1. Only the current through Sw

1 is shown below:

State 2: [t

0–t

1]: In this mode, the two power Mosfets are still in the on state. The PWM generator continues to provide a high gate-to-source voltage to keep them in the on state, and both diodes D

2 and D

3 remain off. Meanwhile, L

1 continues to charge energy from the input source, while L

2 reaches zero charge due to the charge across C

1 being zero. The current through Sw

1 comes solely from IL

1, reducing the current stress through Sw1. D

1 operates with zero current switching during this mode, meaning that L

2 will be open circuit during the time period ((D − β

2) < t < D). L

3 and L

4 continue to charge from C

2 and C

3, respectively. C4 continues to supply power to the load, and the current path of this mode is shown in

Figure 3f. The current equations remain the same as in the previous state 1.

State 3: [t

1–t

2]: in this mode, the two power MOSFETs are off, and both diodes D

2 and D

3 are now on. L

1 now starts discharging energy to C

1 and charges C

2. L

2 does not charge, and iL

2 and ID

1 are zero. L

2 is open circuit during this mode. C

2 receives a large amount of energy from L

1. L

3 and L

4 also start discharging their energy to C

4, which supplies high power to the load and forms the current path of this mode, as shown in

Figure 3d.

State 4: [t

2–t

3]: In this mode, the two power MOSFETs are still off, and only D

2 is still on. D

3 is changed to the off state in this mode. L

1 continues discharging energy to charge C

2, and C

2 will have a large amount of energy for the next pulse to supply it to the load. L

2 remains open circuit in this mode. C

2 will continue receiving energy only from L

1. L

3 and L

4 will have the same current but in opposite directions: iL

3 = −iL

4. C

4 will supply high power to the load and forms the current path of this mode, as shown in

Figure 3e.

When the proposed converter operates in DCMC2, the capacitor C1 is discharged to zero at (D − β2), reducing the current stress across Sw1. In this case, the current through Sw1 flows only from L1. Additionally, the voltage stress across Sw1 and the power diodes is significantly reduced. Furthermore, the conduction loss of Sw1 is significantly reduced when the stress current is reduced. In this mode, L2 will be in an open circuit state, and D1 will have very low voltage stress. Additionally, as mentioned above, C1 is discharged to zero. This implies that the components of the proposed converter are reduced during this mode, leading to improved performance and efficiency.

2.3. Proposed Converter Operation in CCM

This operation mode occurs when the load current increases to a duty cycle of 70%, as depicted in

Figure 4. The input current still operates in CCM, and L

2 enters a resonant mode with C

1, while L

3 and L

4 continue to operate in CCM. Additionally, the voltage gain in this mode will be increased. Thus, this mode consists of three states of operation, as illustrated in

Figure 2c, which shows the proposed converter waveforms in CCM.

State 1: [0–t0]: in this mode, same as state 1 DCMC2.

State 2: [t0–t1]: in this mode, same as state 2 DCMC2.

State 3: [t

1–t

2]: In this mode, the two power MOSFETs are off, and both diodes D

2 and D

3 are now on. L

1 will start discharging energy to C

1 and charge C

2, and iL

2 and ID

1 are zero. C

2 receives a large amount of energy from L

1. L

3 and L

4 will also start discharging their energy to C

4, and L

3 and L

4 will have the same current in CCM but in opposite directions: iL

3 = −iL

4. C

4 will supply high power to the load and forms the current path of this mode, as shown in

Figure 3d.

4. Voltage across Power Diodes, MOSFETs and Capacitor

The proposed converter has two power switches, three power diodes, and four capacitors. Therefore, in this section, the voltage stress across power MOSFETs is calculated. Furthermore, the voltages across the power diodes and capacitors of the proposed converter are also calculated.

In order to find the voltage stress across the power diodes in the proposed converter, we can use Equation (44) to determine the voltage stress across D

1, which is a very small value. Equation (45) can be used to obtain the voltage stress across D

2, while Equation (46) provides the means to find the voltage stress across D

3. It can be observed that the voltage across the power diodes is very small and depends on the input voltage, which ranges from 20 V to 40 V.

To determine the voltage stress across the Power MOSFETs, we can use Equation (47) to find the voltage across MOSFET Sw

1. This voltage is also very small and depends on the input voltage, which varies from 20 V to 40 V. Additionally, Equation (48) allow us to calculate the average voltage stress across Sw

2. During the time period D < t < D1, the voltage across Sw

2 is equal to the output voltage. During the time period D1 < t < Ts, it is equal to the average voltage across C

2.

To determine the voltage across capacitors, we can refer to Equation (49) for the voltage across C1 and Equation (50) for the voltage across C2. Additionally, Equation (51) provides the means to find the voltage across the filter capacitor, which is equal to the output voltage. By reducing the voltage stress on all power diodes and power MOSFETs, the proposed converter experiences decreased losses, leading to improved efficiency.

6. Comparison the Proposed Converter with Previous DC DC Converters

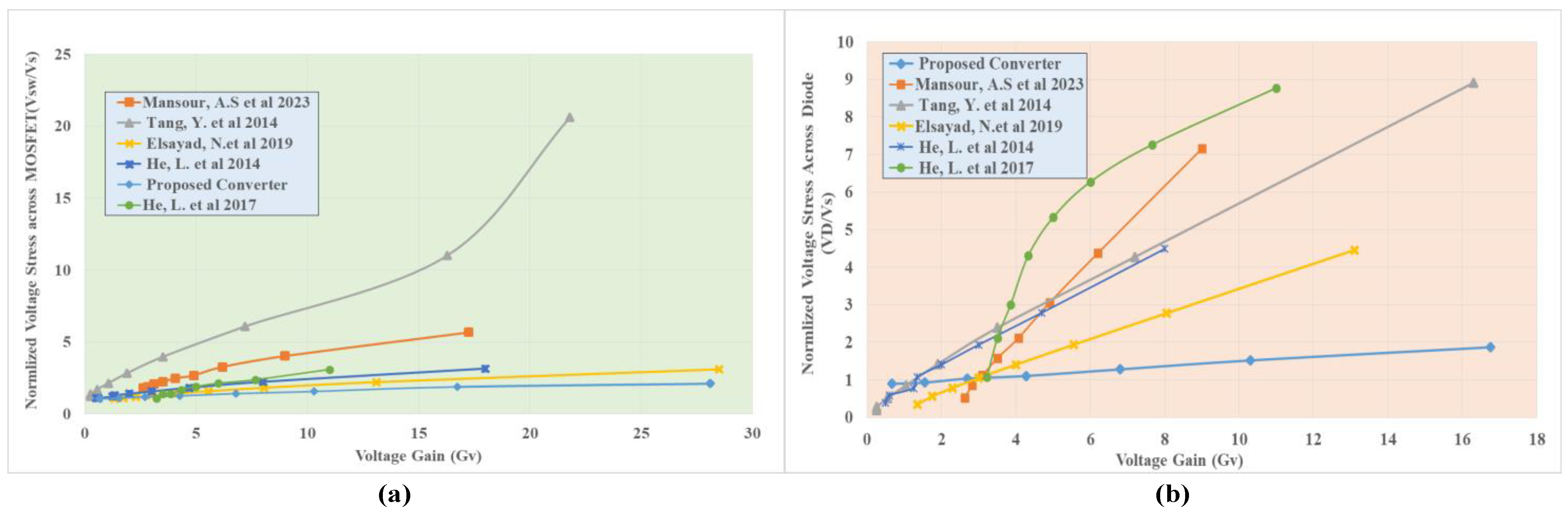

In this section, the proposed converter is compared to previous DC-DC converters. Both the previous works and the proposed converter are simulated in Matlab Simulink under the same conditions. From

Figure 5, it can be observed that the voltage gain of the proposed converter is higher than that of the previous converters. A higher gain at a low duty cycle implies lower conduction losses, lower switching losses, higher efficiency, and a reduced number of inductors and capacitors. As shown in

Figure 6a, the power MOSFET in the proposed converter experiences lower voltage stress compared to the power MOSFET in the previous converters. However, the voltage stress across the power MOSFET in the proposed converter slightly increases as the voltage gain increases. Regarding the voltage across the diodes,

Figure 6b demonstrates that the voltage stress across the diode in the proposed converter is lower than in previous DC-DC converters.

The proposed DC-DC converter is compared with the previous DC-DC converters in

Table 2. It can be seen that the proposed converter operates at a higher switching frequency than previous DC-DC converters. A low switching frequency requires high values of inductors and capacitors with high internal resistance, resulting in high switching and conduction losses, particularly at high duty cycles. Furthermore, high values of passive components result in high weight, high cost, and large size.

The proposed converter can step up a low input voltage at a duty cycle of 45% with a load of 200 W, but other converters in

Table 2 can step up a low voltage at a high duty ratio. A high diode count leads to high internal resistance and high forward voltage (Vf), limiting the voltage gain and increasing the converter losses. In addition, a high diode count increases the reverse recovery time, which also affects the system’s performance. In addition, the proposed converter has zero pulsating input current at low and high duty cycles compared to the input current in the previous DC-DC converter. In terms of the voltage gain equations of the proposed and previous DC-DC converters, as shown in

Table 2, the proposed converter can achieve a higher voltage gain than the previous DC-DC converters listed in

Table 2. Moreover, this means that the proposed converter is more efficient for applications that require high DC voltage gain at different loads, with more flexibility in the duty ratio. It achieves an efficiency of 96.5%. Additionally, the proposed converter is more suitable for RES.

8. Simulation and Experimental Results and Discussion

In this section, a 200 W PCB prototype is designed to validate the experimental results, as shown in

Figure 9a. An experimental test is performed in the laboratory for the proposed converter, as shown in

Figure 9b. Additionally, MATLAB Simulink and PLECS software are used to verify the experimental results in different cases.

Figure 10a shows the source-to-gate voltage with a duty cycle of 27% and an output voltage of 218 V, with the input voltage at 40 V. It can be seen that the load current is 0.44 A at 95 W.

Figure 10b shows the voltage across capacitors C

1, C

2, and C

3. It can be observed that Vc

1 is equal to the difference between Vs and Vc

2, while the voltage across C

2 is 54.6 V. Furthermore, the average voltage across C

3 is zero. In

Figure 10c, the current through switching Sw

1 and Sw

2 and the voltage across Sw

1 and Sw

2 are depicted. It can be seen that the current through Sw

1 is equal to iL

1 and iL

2, matching the shape of both inductor currents. Additionally, the voltage across the MOSFET significantly decreases when the converter operates at low duty cycle.

Figure 10d illustrates the current through D

1, D

2, and D

3. The current through D

1 is in series with L

2 to prevent iL

2 from starting in the reverse direction, having the same shape as the current in L

2. This prevents the input current from becoming pulsating at a low duty cycle. The current across D

2 is equal to iL

2 and iL

1 when D

2 is on, while the current through D

3 is equal to iL

3 and iL

4 when D

3 is on.

Figure 10e displays the voltage across diodes D

1, D

2, and D

3. It can be observed that the voltage across power diodes significantly decreases when the converter operates at a low duty cycle.

Figure 10f shows the voltage across inductors. The voltage across inductor L

1 is substantially reduced in the on state, equal to the input voltage, while in the off state, it is equal to half the input voltage. The voltage across L

2 in the on state has the same shape as Vc

1, and in the off state, VL

2 is equal to Vc

2 for a short period of time. VL

3 and VL

4 are equal to the value of Vc

2, which is very small during the on state and equal to the output voltage during the off state for a very short time as well. This means low voltage stress on the inductors, reducing the total losses of the proposed converter.

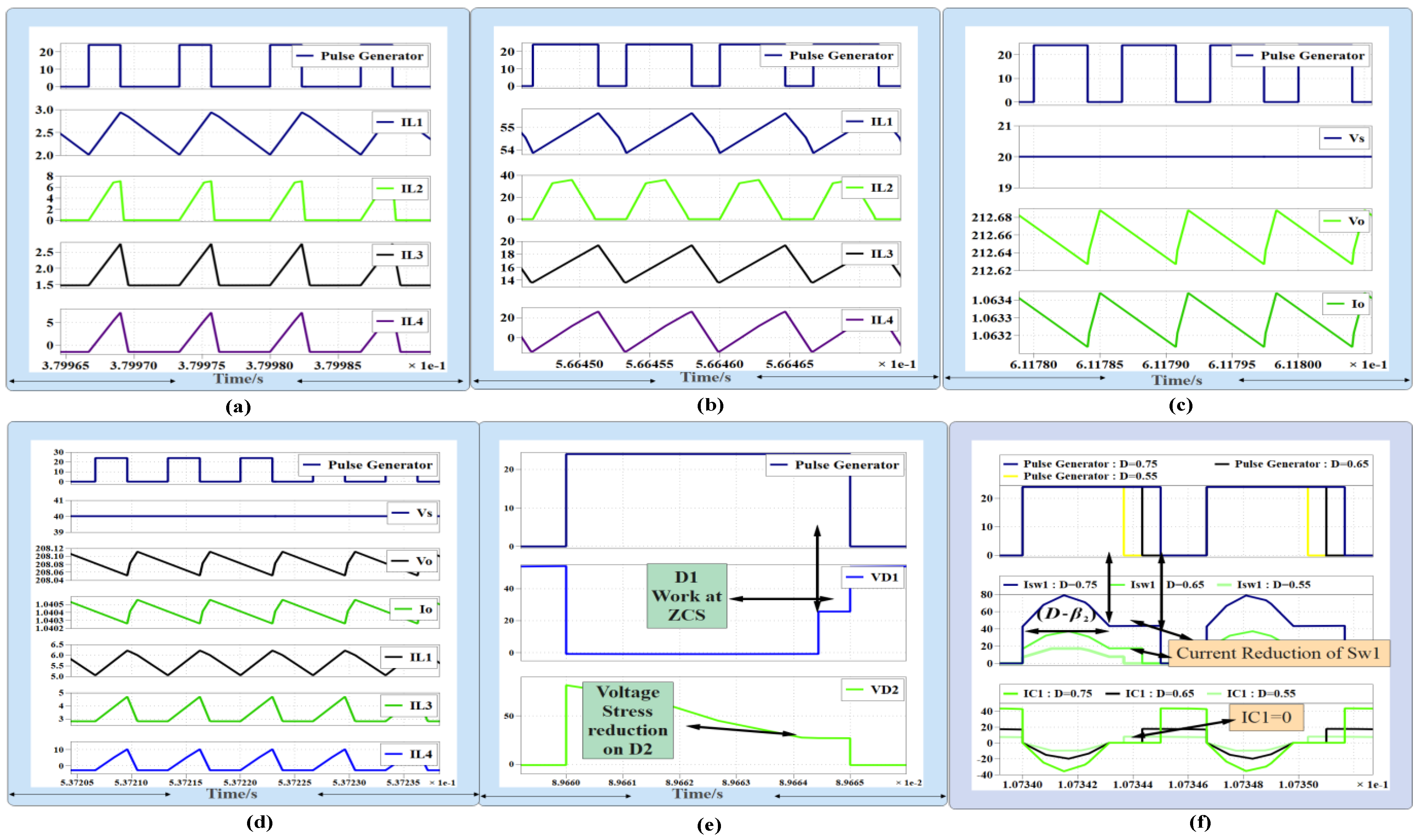

Figure 11a indicates that current flows through the inductors during the on-state period. It is evident that the discharging time of L

2 is smaller than that of L

3 and L

4. Additionally, the discharging time of L

2 is denoted as β

1 when the proposed converter operates in DCMC1. Furthermore, the discharging times of L

3 and L

4 are equal to D1, and both discharging times (D1 and β

1) depend on the values of RL, Vo, D. The inductor L

1 exhibits a long discharge time, does not reach zero, and shows no pulsation during the off states.

Figure 11b illustrates the current through the inductors when the proposed converter operates in CCM.

Figure 11c presents the load current of the proposed converter, which is 1 A at an input voltage of Vs = 20 V and an output voltage of 212 V at 200 W.

Figure 11d depicts an input voltage of Vs = 40 V and an output voltage of 208 V at a load current of 1 A at 200 W. It can be observed that the current through L

1 is still in CCM, while the current through L

3 and L

4 is in DCM at 200 W. This approach aims to reduce voltage stress across Sw

2 and inductors L

3 and L

4, thereby enhancing the performance and efficiency of the proposed converter.

Figure 11e shows the voltage across D

1, and it can be seen that in the on state, the voltage across D

1 is around 22 V during the period (D − β

2 < t < D). D

1 works in ZCS, and inductor L

2 is an open circuit during this time. Therefore, when the input voltage is decreased to the minimum value, the proposed converter can work with high performance with one power diode working in ZCS, reducing the number of passive components. In addition, the voltage stress across D

2 will be reduced when the converter works in DCMC2 when capacitor C

1‘s charge becomes zero at (D − β

2).

Figure 11f shows that the current reduction of Sw

1 occurs when capacitor C

1’s charge becomes zero at (D − β

2). After this period, the current through Sw

1 will come only from L

1. This means that the RMS current of Sw

1 will be significantly reduced when the converter operates at high current. The value of β

2 depends on the values of C

1 and L

2. This means that the proposed converter can supply high load current with high efficiency, especially for battery charging and renewable energy applications.

Figure 12a shows the inductor currents L

1 and L

2 when the converter operates in DCMC1 at D = 0.45. In

Figure 12b, the inductor currents L

1 and L

2 can be observed when the proposed converter operates in DCMC2.

Figure 12c demonstrates that the current through inductors L

3 and L

4 operates in DCM, with both inductors having the same value but in opposite directions. This method aims to reduce voltage stress across Sw

2 during the very long period of time (D

1 < t < Ts), as previously mentioned.

In

Figure 12d, the output voltage of the proposed converter is 200 V at a load current of 1 A, as shown in

Figure 12e when the proposed converter operates in DCMC2. The currents through Sw

1 and Sw

2 are depicted in

Figure 12f. It can be seen that the voltage across Sw

1 is equal to 54 V, which is a very low voltage as shown in

Figure 13a.

Figure 13b shows the voltage across Sw

2, which remains at 54 V for a long time period (D

1 < t < Ts).

Figure 13c illustrates the voltage stress across D

3. Furthermore,

Figure 13d shows the voltage across D

1, indicating that during the on state, the voltage across D

1 is around 22 V in the period (D − β

2 < t < D), with D

1 operating in ZCS, while the inductor L

2 acts as an open circuit during this time. As mentioned earlier, the voltage stress across D

2 will be reduced when the converter works in DCMC2, as capacitor C

1’s charge becomes zero at (D − β

2).

Figure 13e displays the voltage across C

2, which is equal to 52 V at D = 0.45. Additionally, the proposed converter can supply a variable output voltage, as shown in

Figure 13f, where the output voltage is 250 V. These qualities make the suggested converter highly efficient and enable it to perform exceptionally well. Moreover, it can supply high currents, even when the duty ratios vary over a wide range.

The proposed converter demonstrates a higher level of performance compared to previous DC-DC converters. Notably, the power MOSFETs in the proposed converter experience significantly reduced voltage stress when operating in Discontinuous Conduction Mode (DCM) for both cases. Additionally, the single-cell switched inductor capacitor operates in resonant mode when the duty cycle exceeds 50%.

Furthermore, one of the passive elements, L2, becomes an open circuit when the charge on capacitor C1 reaches zero at (D − β2). This approach effectively reduces the voltage stress across the power MOSFETs and all diodes, while also minimizing the current stress on the main switch. This is achieved by ensuring that the current through the main switch is solely derived from L1, which is equal to the input current.

The proposed converter also achieves a reduction in power losses, resulting in increased overall efficiency. Specifically, the efficiency of the converter reaches 96.5% at 200 W. Additionally, the input current does not reach zero at low duty cycles, making the proposed converter more efficient and well-suited for Renewable Energy Systems (RESs).

9. The Proposed Converter Efficiency Calculation

The proposed converter consists of four inductors, four capacitors, two power switches, and three diodes. These components, both passive and active, are not ideal. For example, an inductor has internal resistance, which increases as its value increases. The internal resistances of the inductors are denoted as rl

1, rl

2, rl

3, and rl

4. Similarly, the capacitors C

1, C

2, C

3, and C

4 have equivalent series resistances rc

1, rc

2, rc

3, and rc

4. The power diode also incurs power losses due to its internal resistance and forward voltage Vf. Additionally, power losses occur due to conduction and switching losses in the power MOSFET devices. Therefore, it is important to consider all of these losses for the proposed converter. The internal resistances of all active and passive elements are illustrated in

Figure 14.

To calculate the total power losses of the proposed converter, the rms current is required for calculations related to the inductors, capacitors, power MOSFET, and diodes in both the on and off states. Equation (58) represents the general equation for rms current, and Equations (59) and (60) can be used to obtain the rms current through Sw

1 and Sw

2 during the on state.

To calculate the rms current through power diodes, Equation (61) provides the rms current through D

1 during the on state, which is equivalent to the rms current through inductor L

2. Equations (62) and (63) describe the rms current across D

2 and D

3, respectively.

To calculate the rms current through capacitors C

1, C

2, C

3, and C

4, the values can be determined from Equations (64), (65), (66), and (67), respectively.

After solving the rms values in Equations (59) and (60), the resulting Equations (68) and (69) describe the rms current through Sw

1 and Sw

2, respectively.

After solving for the rms values, Equations (70)–(72) provide the rms currents through the power diodes.

Furthermore, Equations (73) and (74) provide the rms current through inductors L

1, L

3, and L

4. Equations (75)–(78) yield the rms current for capacitors C

1, C

2, C

3, and C

4, respectively.

9.1. Conduction Losses Calculation for MOSFET Devices

Conduction losses refer to the power losses that occur when current flows through a device, such as a power MOSFET or any other semiconductor device. These losses are primarily caused by the resistance of the device’s conducting path, resulting in power dissipation in the form of heat.

To calculate the conduction losses of the power MOSFET in the proposed converter, the square value of the rms current is multiplied by the internal resistance of the MOSFET, as shown in Equation (79).

From Equation (79), the power conduction losses of power MOSFETs, Pcd1, and Pcd2, can be obtained.

9.2. Switching Losses Calculation for MOSFET Devices

Switching losses, also known as dynamic losses, are the power losses that occur during the switching transitions of a power electronic device, such as a power MOSFET. These losses result from the energy dissipated as the device switches between the on and off states. Switching losses are mainly caused by the charging and discharging of internal capacitances, as well as the voltage and current overlapping during the switching process.

To calculate the switching losses of the power MOSFET in the proposed converter, half of the square of the voltage stress across the MOSFET during the off state is multiplied by the switching frequency and the output capacitor of the power MOSFET (Co).

where, (Esw) is the energy dissipated during one switching cycle. From Equation (80), the power switching losses of the MOSFETs Sw

1 and Sw

2, denoted as PSWL1,2, can be obtained.

9.3. Total Power Loss in MOSFET Devices

From Equation (81), PTML1,2 can be obtained as the total power losses of Sw1 and Sw2 by adding Equations (79) and (80).

9.4. Losses in Power Diode

Power losses in the diode can be divided into two components: losses due to internal resistance rd and losses due to the forward diode voltage Vf. Therefore, all power losses from the three diodes in the converter must be taken into account. From Equation (82), the average current (IDav) through diodes can be calculated:

In order to find the power losses due to forward voltage (Pvf), Equation (82) is multiplied by Vf, resulting in Equation (83).

To calculate the diode power losses due to internal resistance (rd), the square of the diode’s rms current is multiplied by rd, as shown in Equation (84).

The total power losses PDL

1,2,3 across the three diodes can be found in Equation (85), by adding all the losses in the power diodes.

9.5. Power Losses in Inductors and Capacitors

The inductor used in the proposed converter has a very low internal resistance, as shown in

Table 1. Additionally, the inductors and capacitors of the proposed converter are designed for high switching frequency, resulting in the converter operating with very high efficiency and performance. Calculation of the power losses due to the internal resistance of the inductors and capacitors are shown below:

From Equations (86) and (87), the power losses PL and PC in the inductors and capacitors can be found, respectively.

9.6. Total Power Losses in Proposed Converter

The proposed converter losses can be divided into MOSFET losses, diode losses, inductor losses, and capacitor losses. The total power loss (T

PPCL) of the proposed converter can be found in Equation (88), which involves summing the power losses in the power MOSFETs (P

TML1,2), the total power losses in the diodes (P

DL1,2,3), and the losses in the inductors and capacitors (P

L1,2,3,4) and (P

C1,2,3,4), respectively. The proposed converter efficiency can be obtained using Equation (89).

The use of SiC MOSFETs with very low on-state resistance is a better choice to reduce conduction losses. Additionally, using inductors with low values and very low internal resistance can increase the performance and efficiency of the proposed converter.

Figure 15a shows that the proposed converter’s output voltage increases as the switching frequency increases. This implies that the design of the proposed converter allows for boosting low voltage to high voltage at a low duty cycle, achieving high power density with an efficiency of 96.5%.

Figure 15b provides a comprehensive visual representation of the losses incurred by the proposed converter. It is worth noting that a significant proportion of these losses can be attributed to the power MOSFETs and diodes used in the converter. These losses result from the switching and conduction characteristics exhibited by these components during the converter’s operation. Furthermore, a portion of the losses can be attributed to the inherent resistance of the inductors and capacitors present in the system.

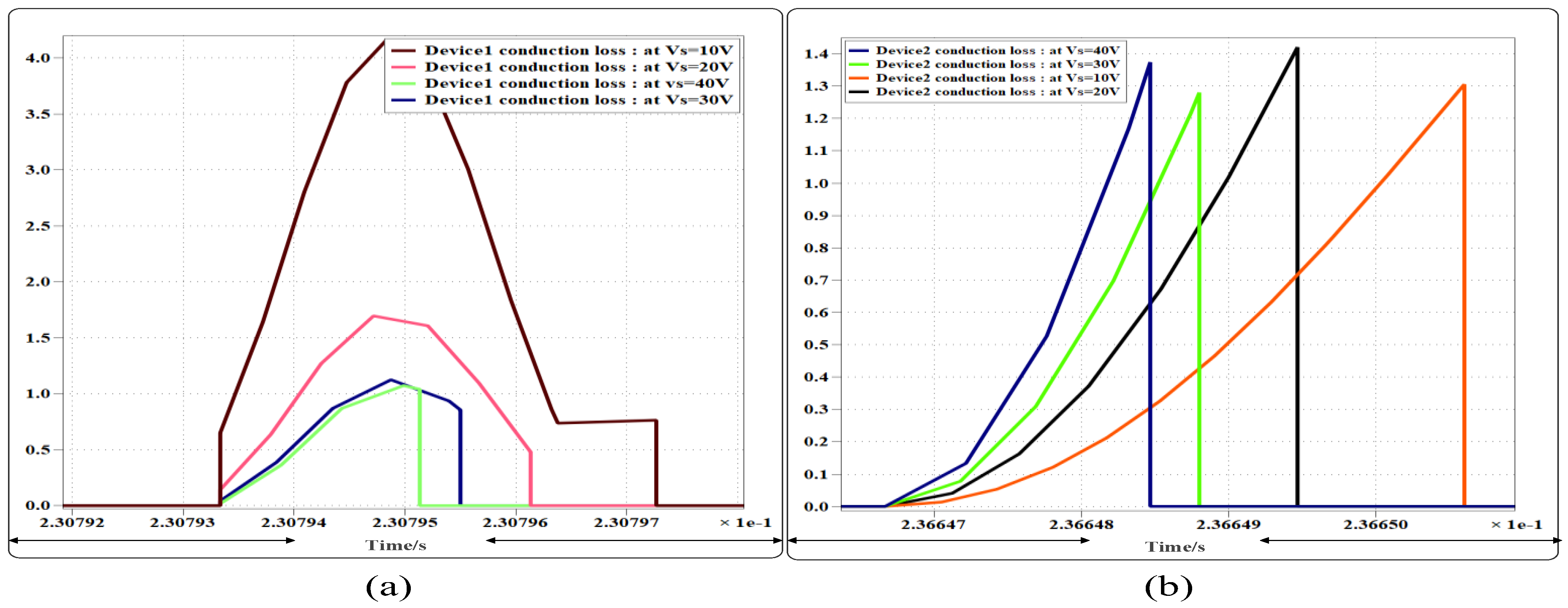

Figure 16a,b illustrates the conduction power losses of MOSFETs Sw

1 and Sw

2 at different input voltages. It can be observed that the conduction power losses for both MOSFET switches slightly increased as the input voltage rose from 10 V to 40 V. Additionally, the conduction losses showed a significant decrease as the duty cycle decreased.

This indicates that the SiC MOSFET utilized in the proposed converter exhibits very low power conduction losses, particularly at variable duty cycles. Consequently, the proposed converter achieves higher efficiency compared to previous DC-DC converters. By employing WBG (Wide Bandgap) MOSFETs, both conduction and switching losses can be substantially reduced, leading to a significant increase in the converter’s efficiency.

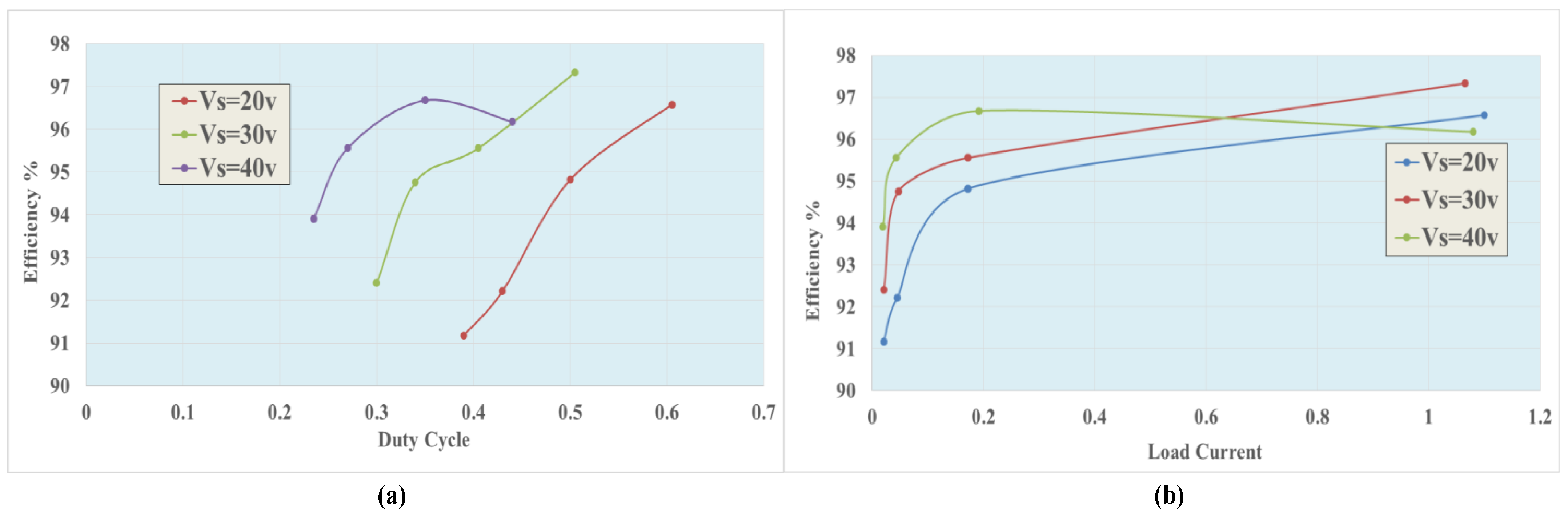

Figure 17a,b displays the efficiency of the proposed converter at various input voltages. The results indicate that at an input voltage of 30 V and a duty cycle of 50%, the converter achieves an efficiency of approximately 97.3% when operating at a power level of 200 W. This demonstrates that the proposed converter is capable of stepping up a low input voltage under light load current conditions, while also providing high load current at the maximum input voltage.

10. Conclusions

As a result, a new single-cell hybrid switched inductor DC-DC converter is proposed to demonstrate the verification of ultra-high voltage gain in photovoltaic applications. The modification in the proposed converter helps prevent the input current from pulsating to zero at very low duty cycles, making it more efficient for renewable energy applications. The single cell of the hybrid inductor is interleaved with the main switch to reduce current stress when the load current increases and the capacitor charge becomes zero. Moreover, the addition of a modified hybrid switch inductor with a capacitor, operating in dual boosting mode with a single switch, allows the converter to achieve ultra-high voltage gain.

The proposed converter offers several advantages, including ultra-high voltage gain, high efficiency, low voltage stress on power MOSFETs, diodes, inductors, and capacitors, as well as low switching and conduction losses. Furthermore, the proposed converter utilizes transformerless and non-coupled inductors. Additionally, the proposed converter’s efficiency is around 96.5% when the input voltage is 20 V with a duty cycle of 0.6. The increased flexibility in the duty cycle allows the proposed converter to operate at high power density and convert very low input voltage to high output voltage for renewable energy systems.

In addition, the output voltage of the proposed converter increases when the switching frequency is increased to boost low input to high output voltage at a low duty cycle. The voltage stress on the power devices has been reduced compared to existing DC-DC converters. Moreover, using a high switching frequency reduces the component values and circuit size, resulting in a significant reduction in the weight of the proposed converter. Passive components of the proposed converter are reduced when the converter operates in (DCM) and (CCM), which improves converter efficiency and performance.