A Design of a Dual Delay Line DLL with Wide Input Duty Cycle Range

Abstract

:1. Introduction

2. Research Methodology

3. Principle of DC-DL DLL Structure

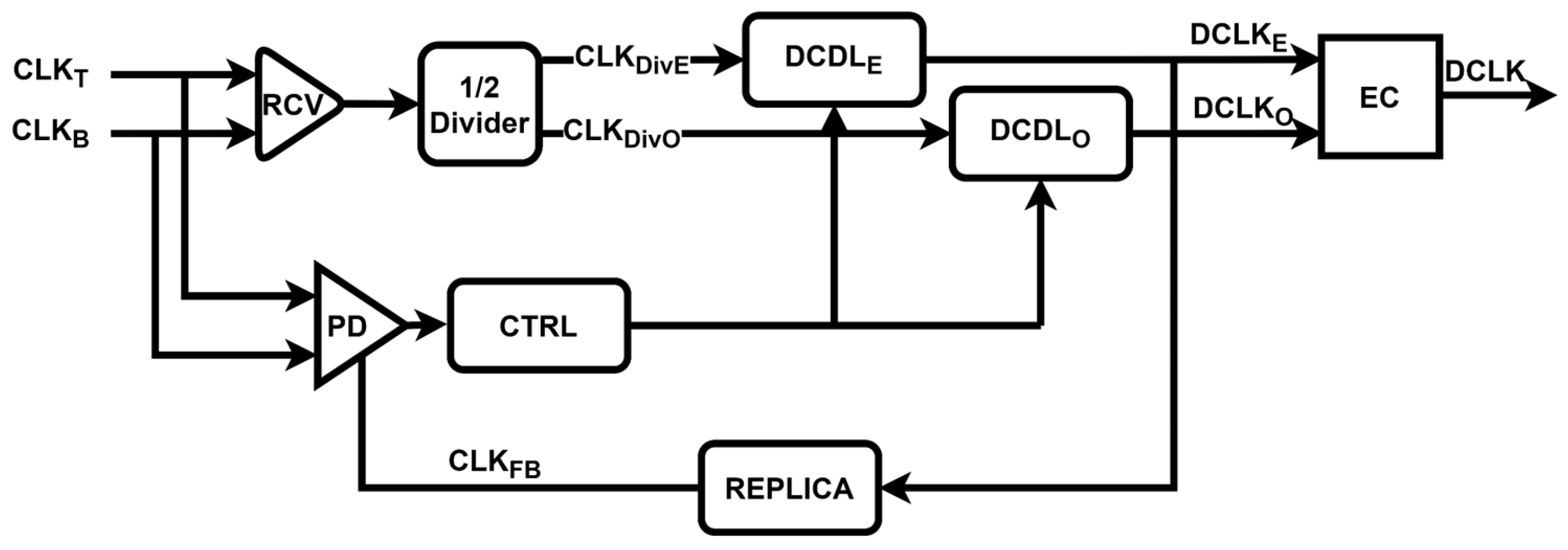

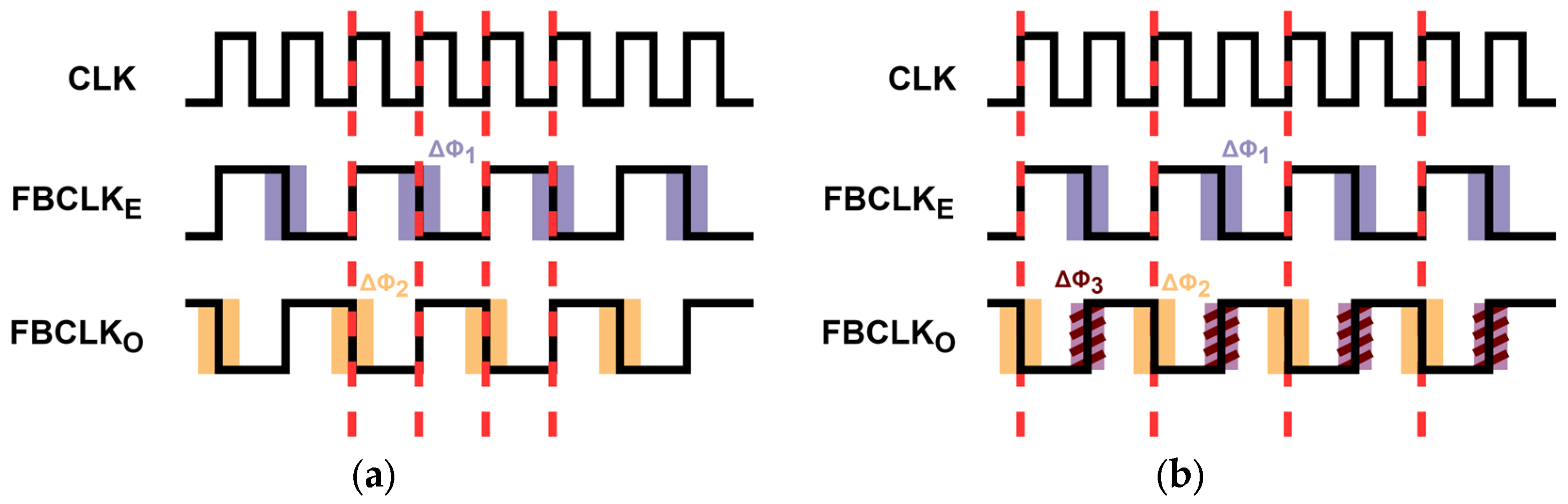

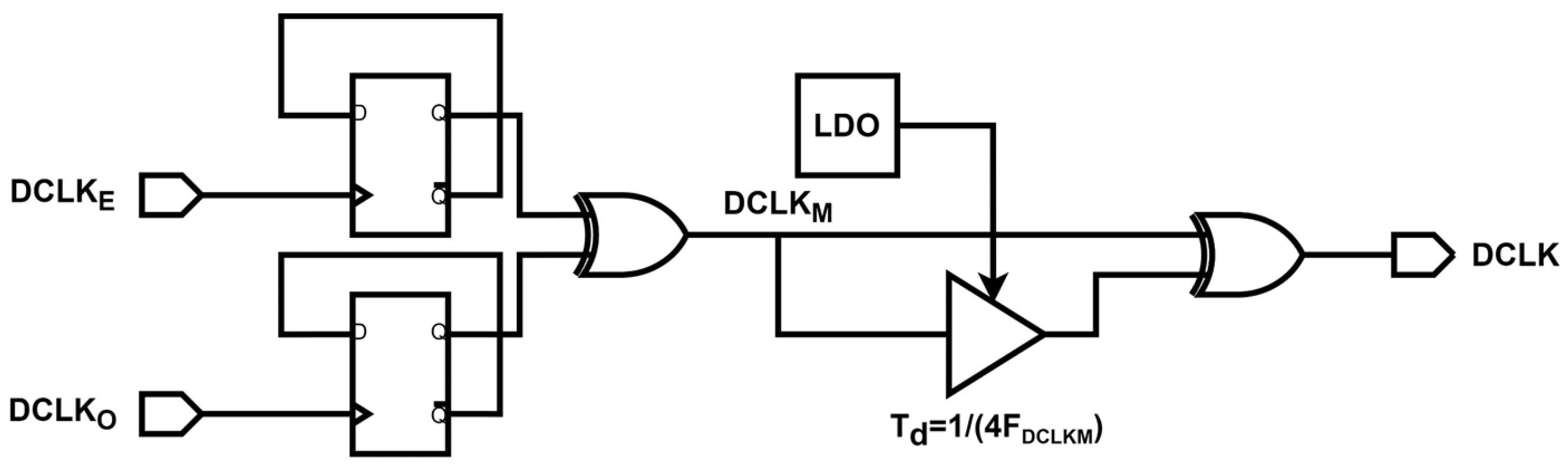

3.1. Proposed Structure

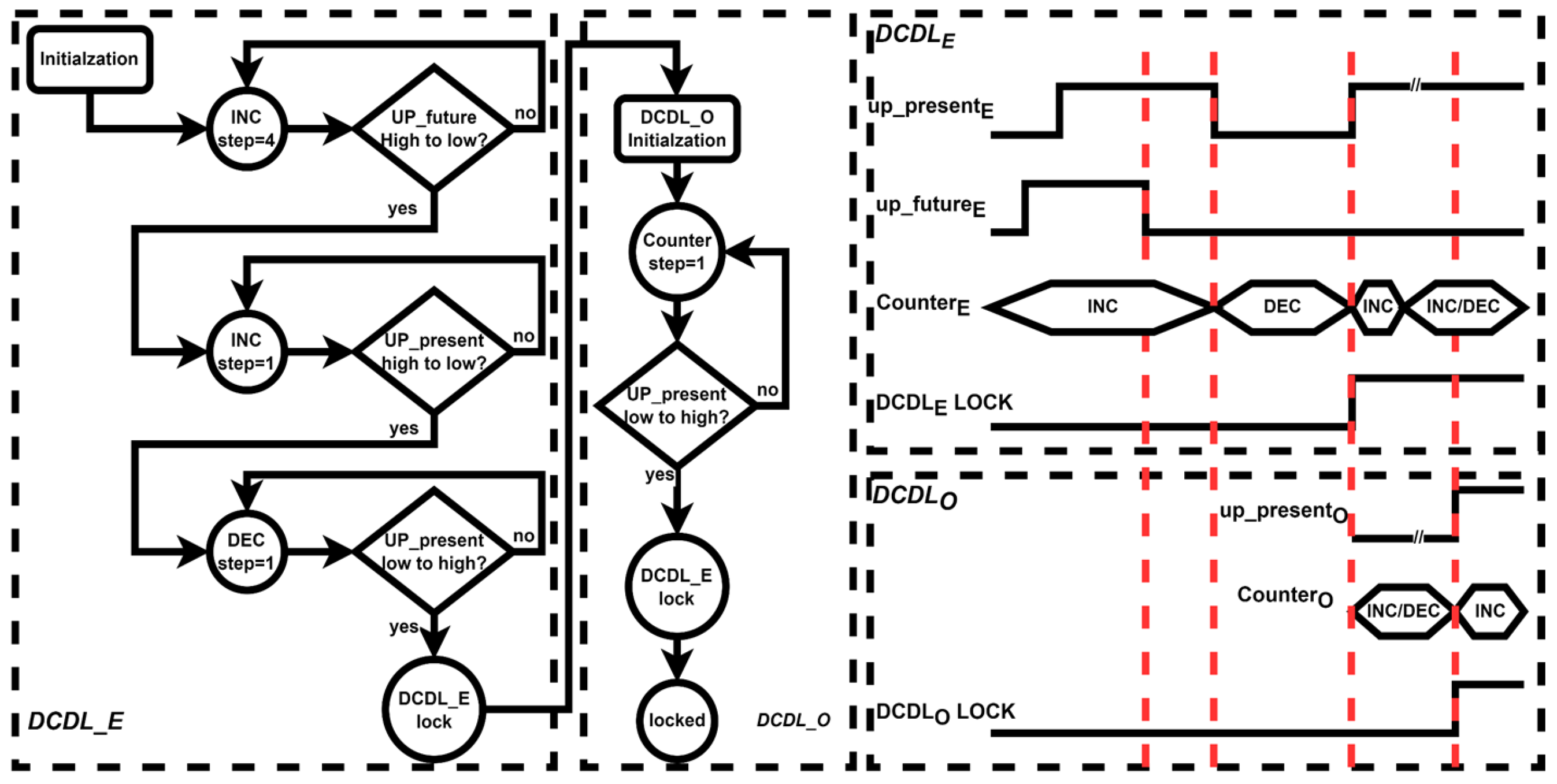

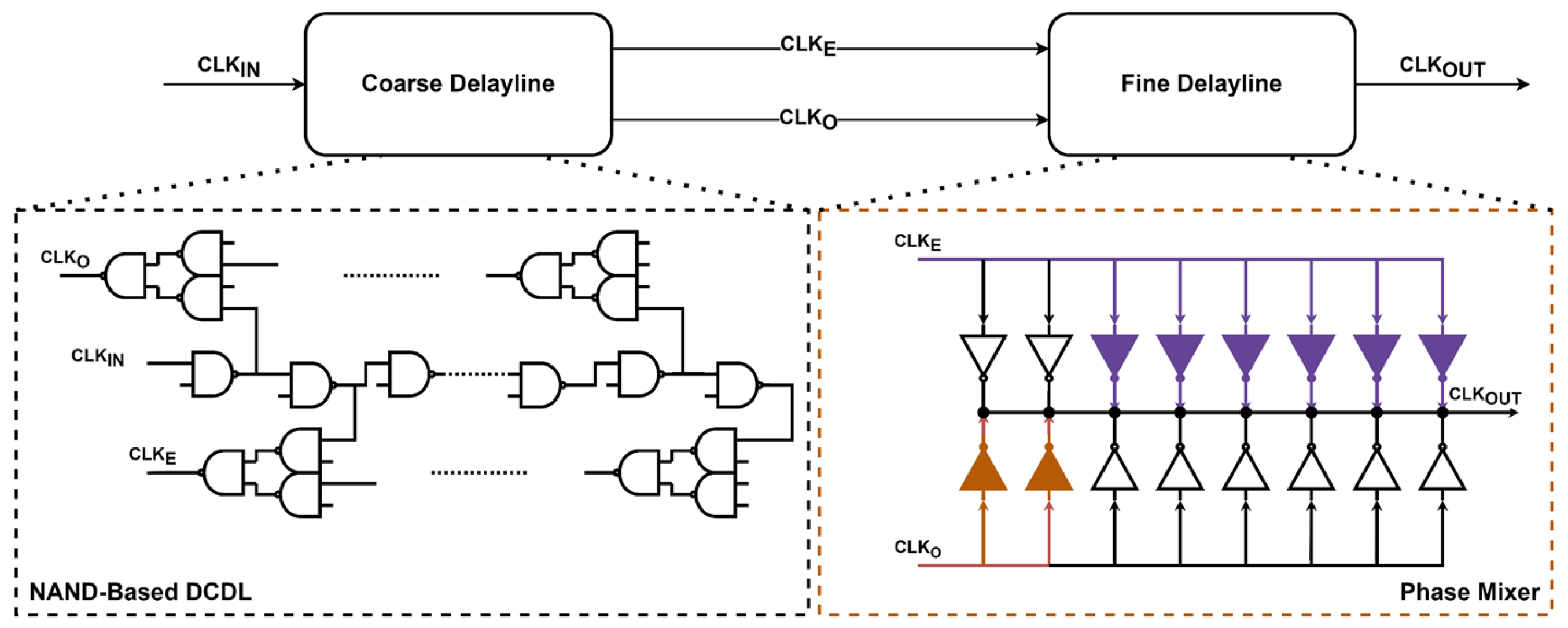

3.2. Detailed Composition Modules

4. Results

5. Discussion

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kim, S.Y.; Jin, X.; Chun, J.H.; Kwon, K.W. A Digital DLL with 4-Cycle Lock Time and 1/4 NAND-Delay Accuracy. In Proceedings of the 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), Xiamen, China, 9–11 November 2015; pp. 1–4. [Google Scholar]

- Yang, C.Y.; Li, M.S.; Chuang, A.J. A Wide-Range Folded-Tuned Dual-DLL-Based Clock-Deskewing Circuit for Core-to-Core Links. IEEE Trans. Very Large Scale Integr. Syst. 2021, 29, 883–894. [Google Scholar] [CrossRef]

- Zhang, D.; Yang, H.G.; Zhu, W.; Li, W.; Huang, Z.; Li, L.; Li, T. A Multiphase DLL with a Novel Fast-Locking Fine-Code Time-to-Digital Converter. IEEE Trans. Very Large Scale Integr. Syst. 2015, 23, 2680–2684. [Google Scholar] [CrossRef]

- Tsai, T.H.; Sheen, R.B.; Hsu, S.Y.; Chang, Y.T.; Chang, C.H.; Staszewski, R.B. A Cascaded PLL (LC-PLL + RO-PLL) with a Programmable Double Realignment Achieving 204fs Integrated Jitter (100 kHz to 100 MHz) and −72 dB Reference Spur. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 1–3. [Google Scholar]

- Yang, Z.; Chen, Y.; Yuan, J.; Mak, P.I.; Martins, R.P. A 3.3-GHz Integer N-Type-II Sub-Sampling PLL Using a BFSK-Suppressed Push–Pull SS-PD and a Fast-Locking FLL Achieving −82.2-dBc REF Spur and −255-dB FOM. IEEE Trans. Very Large Scale Integr. Syst. 2022, 30, 238–242. [Google Scholar] [CrossRef]

- Qian, Y.C.; Chao, Y.Y.; Liu, S.I. A Low-Jitter Sub-Sampling PLL with a Sub-Sampling DLL. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 269–273. [Google Scholar] [CrossRef]

- Lu, Y.R.; Liu, S.I.; Yang, Y.C.; Kang, H.C.; Chen, C.L.; Chan, K.U.; Lin, Y.H. A 2.4–3.0 GHz Process-Tolerant Sub-Sampling PLL with Loop Bandwidth Calibration. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 873–877. [Google Scholar]

- Park, D.; Kim, J. A 7-GHz Fast-Lock 2-Step TDC-based All-Digital DLL for Post-DDR4 SDRAMs. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar]

- Kim, T.; Kim, J. A 0.8–3.5 GHz Shared TDC-Based Fast-Lock All-Digital DLL with a Built-in DCC. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–4. [Google Scholar]

- Jung, D.H.; An, Y.J.; Ryu, K. All-digital fast-locking delay-locked loop using a cyclic-locking loop for DRAM. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 1023–1027. [Google Scholar] [CrossRef]

- Na, T.; Shim, Y.; Song, I.; Kim, J.K. A Heterogeneous Dual DLL and Quantization Error Minimized ZQ Calibration for 30 nm 1.2 V 4 Gb 3.2 Gb/s/pin DDR4 SDRAM. In Proceedings of the 2013 Symposium on VLSI Circuits, Kyoto, Japan, 12–14 June 2013; pp. C242–C243. [Google Scholar]

- Tsai, C.W.; Chiu, Y.T. A Wide-Range All-Digital Delay-Locked Loop for DDR1–DDR5 Applications. IEEE Trans. Very Large Scale Integr. Syst. 2021, 29, 1720–1729. [Google Scholar] [CrossRef]

- Kim, D.; Park, M. A 1.1-V 10-nm Class 6.4-Gb/s/Pin 16-Gb DDR5 SDRAM With a Phase Rotator-ILO DLL, High-Speed SerDes, and DFE/FFE Equalization Scheme for Rx/Tx. IEEE J. Solid-State Circuits 2020, 55, 167–177. [Google Scholar] [CrossRef]

- Park, H.; Sim, J. A 2.4–8 GHz Phase Rotator Delay-Locked Loop Using Cascading Structure for Direct Input–Output Phase Detection. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 794–798. [Google Scholar] [CrossRef]

- Yun, W.J.; Song, I.; Jeoung, H. 17.7 A Digital DLL with Hybrid DCC Using 2-Step Duty Error Extraction and 180° Phase Aligner for 2.67 Gb/S/pin 16 Gb 4-H Stack DDR4 SDRAM with TSVs. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Yoon, H.; Jung, W.; Park, J.; Byun, J.; Jin, H.; Cho, H.; Lee, S.H. A 3.2–12.8 Gb/s Duty-Cycle Compensating Quadrature Error Corrector for DRAM Interfaces, with Fast Locking and Low Power Characteristics. In Proceedings of the ESSCIRC 2021-IEEE 47th European Solid State Circuits Conference (ESSCIRC), Grenoble, France, 13–22 September 2021; pp. 463–466. [Google Scholar]

- SR, J.P.; Hiremath, S.S. Dual Loop Clock Duty Cycle Corrector for High Speed Serial Interface. In Proceedings of the 2017 International Conference on Smart Technologies for Smart Nation (SmartTechCon), Bengaluru, India, 17–19 August 2017; pp. 935–939. [Google Scholar]

- Jeong, C.H.; Abdullah, A.; Min, Y.J.; Hwang, I.C.; Kim, S.W. All-digital duty-cycle corrector with a wide duty correction range for DRAM applications. IEEE Trans. Very Large Scale Integr. Syst. 2015, 24, 363–367. [Google Scholar] [CrossRef]

- Ryu, K.; Jung, D.H.; Jung, S.O. Process-variation-calibrated multiphase delay locked loop with a loop-embedded duty cycle corrector. IEEE Trans. Circuits Syst. II Express Briefs 2013, 61, 6678577. [Google Scholar] [CrossRef]

- Chae, J.H.; Ko, H.; Park, J.; Kim, S. A quadrature clock corrector for DRAM interfaces, with a duty-cycle and quadrature phase detector based on a relaxation oscillator. IEEE Trans. Very Large Scale Integr. Syst. 2019, 27, 978–982. [Google Scholar] [CrossRef]

- Lim, J.H.; Bae, J.H. A Delay Locked Loop with a Feedback Edge Combiner of Duty-Cycle Corrector With a 20–80% Input Duty Cycle for SDRAMs. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 141–145. [Google Scholar] [CrossRef]

- Sim, J.; Park, H. A 1–3.2 GHz 0.6 mW/GHz Duty-Cycle-Corrector Using Bangbang Duty-Cyle-Detector. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–4. [Google Scholar]

- Kang, K.T.; Kim, S.Y.; Kim, S.J.; Lee, D.; Yoo, S.S.; Lee, K.Y. A 0.33–1 Ghz open-loop duty cycle corrector with digital falling edge modulator. IEEE Trans. Circuits Syst. II: Express Briefs 2018, 65, 1949–1953. [Google Scholar] [CrossRef]

- Chung, C.C.; Sheng, D.; Li, C.J. A wide-range low-cost all-digital duty-cycle corrector. IEEE Trans. Very Large Scale Integr. Syst. 2014, 23, 2487–2496. [Google Scholar] [CrossRef]

| This Work | VLSI [3] | IEEE T CIRCUITS-II [6] | ISCAS [22] | |

|---|---|---|---|---|

| Architecture | Divider + Dual delay line | ADDLL | Divider + DCC | BBDCD |

| Supply Voltage | 1.2 V | 1 V | 1.2 V | 1 V |

| Input Frequency Range | 1.6 GHz | 0.1–2.7 GHz | 1.6 GHz/2 GHz | 1–3.2 GHz |

| Input Clock Duty Cycle Range | 20–80% | N/A | 19.9–80.4% | 37–63% |

| MAX Duty Cycle Error | 1.3% | 1.9% | 0.9% | 1.5% |

| RMS/Peak to Peak Jitter | −/17.61 ps | 0.65 ps/5 ps | 2.7 ps/14 ps | −/12 ps |

| AREA | N/A | 0.089 mm2 | 0.099 mm2 | 0.001 mm2 |

| Power@Fmax | 10.06 mW | 49.4 mW | 6.6 mW | 1.92 mW |

| Technology | 25 nm | 90 nm | 65 nm | 28 nm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Qin, B.; Zhao, L.; Fang, C.; Poechmueller, P. A Design of a Dual Delay Line DLL with Wide Input Duty Cycle Range. Electronics 2023, 12, 2696. https://doi.org/10.3390/electronics12122696

Qin B, Zhao L, Fang C, Poechmueller P. A Design of a Dual Delay Line DLL with Wide Input Duty Cycle Range. Electronics. 2023; 12(12):2696. https://doi.org/10.3390/electronics12122696

Chicago/Turabian StyleQin, Binyu, Leilei Zhao, Chenyu Fang, and Peter Poechmueller. 2023. "A Design of a Dual Delay Line DLL with Wide Input Duty Cycle Range" Electronics 12, no. 12: 2696. https://doi.org/10.3390/electronics12122696

APA StyleQin, B., Zhao, L., Fang, C., & Poechmueller, P. (2023). A Design of a Dual Delay Line DLL with Wide Input Duty Cycle Range. Electronics, 12(12), 2696. https://doi.org/10.3390/electronics12122696